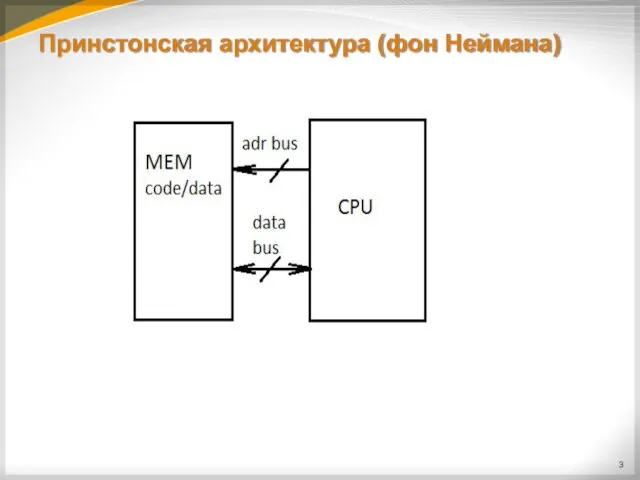

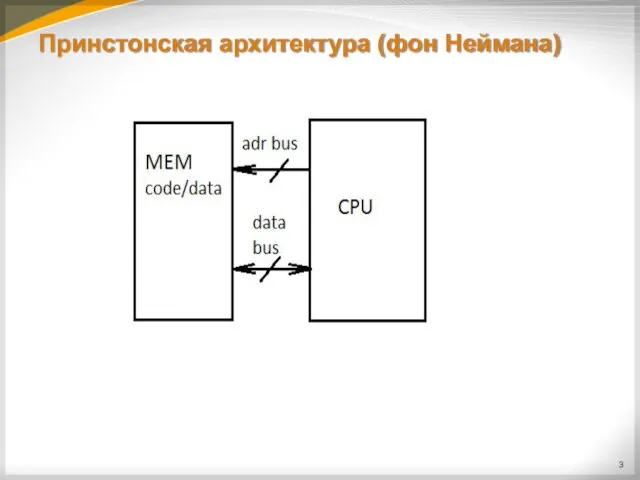

Слайд 3Принстонская архитектура (фон Неймана)

Слайд 5Базовые цифровые схемы

Комбинационные цифровые устройства (линейные схемы). Предназначены для преобразования информации и

направления потоков информации.

Последовательностные цифровые устройства (схемы, содержащие обратные связи). Предназначены для хранения информации.

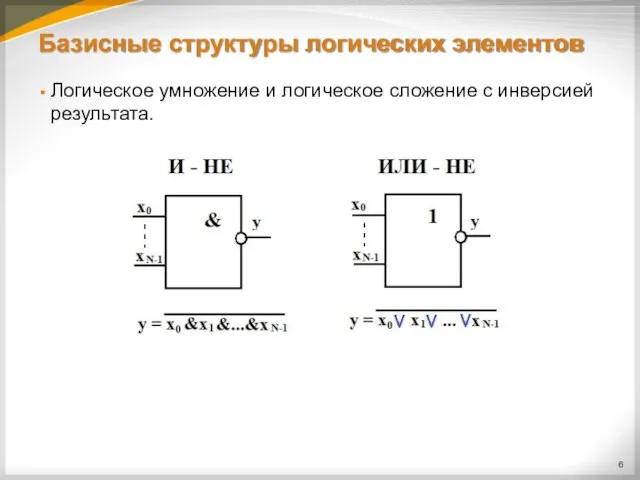

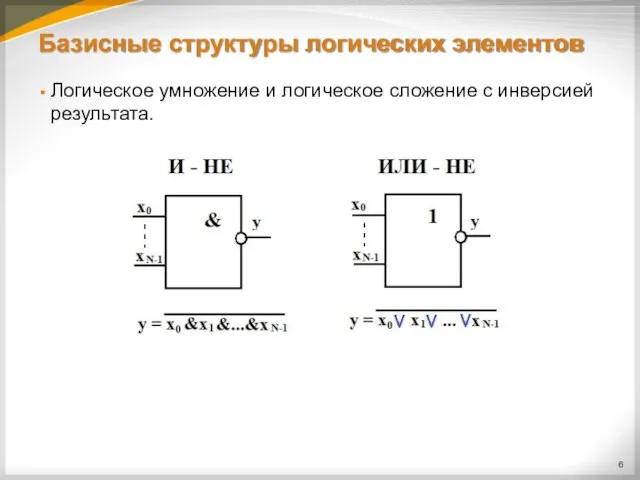

Слайд 6Базисные структуры логических элементов

Логическое умножение и логическое сложение с инверсией результата.

Слайд 7 Примеры КЦУ

Шифраторы, дешифраторы, сумматоры, кодопреобразователи, мультиплекоры, демультиплексоры.

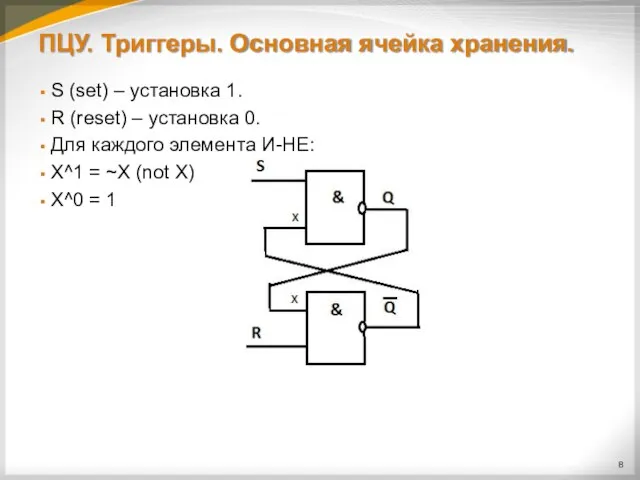

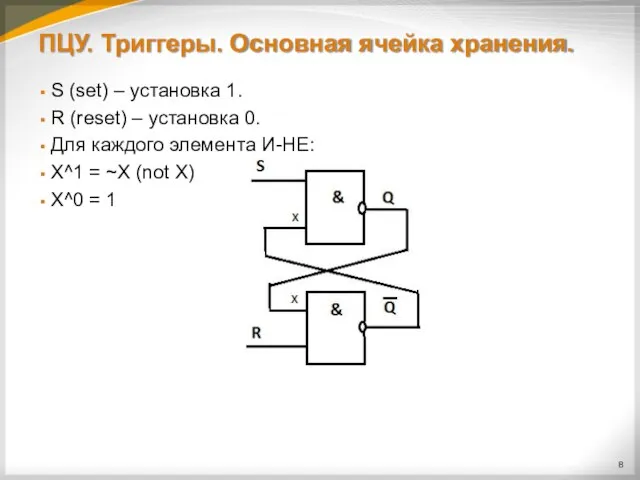

Слайд 8ПЦУ. Триггеры. Основная ячейка хранения.

S (set) – установка 1.

R (reset) – установка

0.

Для каждого элемента И-НЕ:

X^1 = ~X (not X)

X^0 = 1

Слайд 9ПЦУ. Триггеры. Таблица режимов RS-триггера.

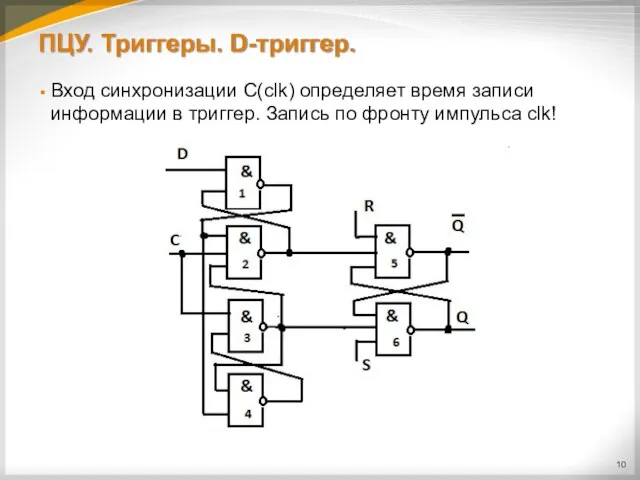

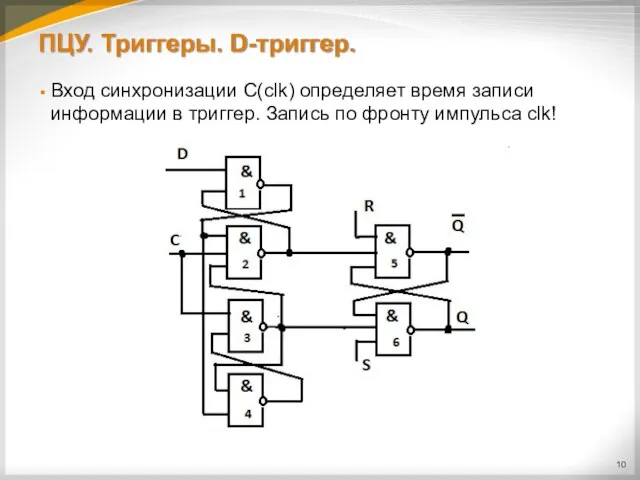

Слайд 10ПЦУ. Триггеры. D-триггер.

Вход синхронизации C(clk) определяет время записи информации в триггер. Запись

по фронту импульса clk!

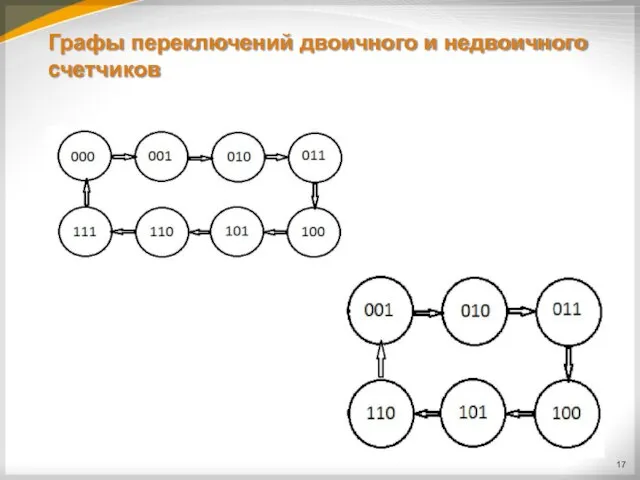

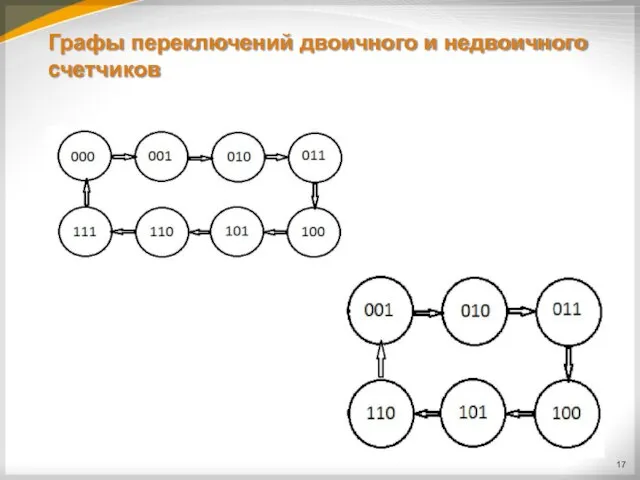

Слайд 17Графы переключений двоичного и недвоичного счетчиков

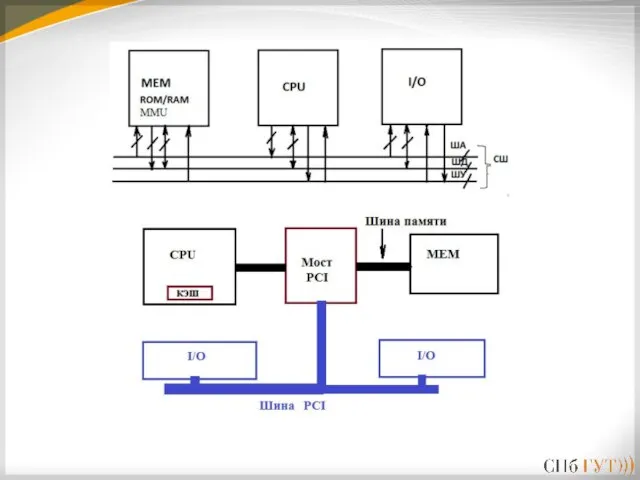

Слайд 20Структура микропроцессора (CortexA9)

Слайд 21Блочная структура ядра микропроцессора

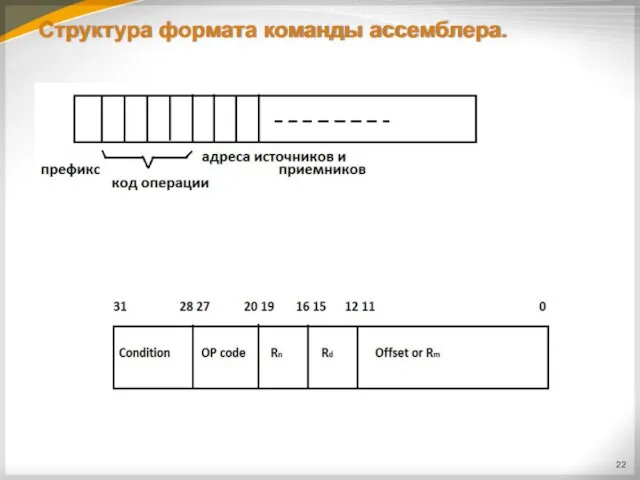

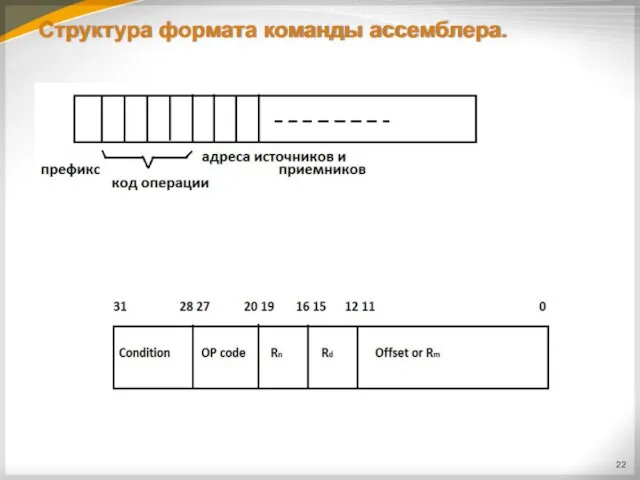

Слайд 22Структура формата команды ассемблера.

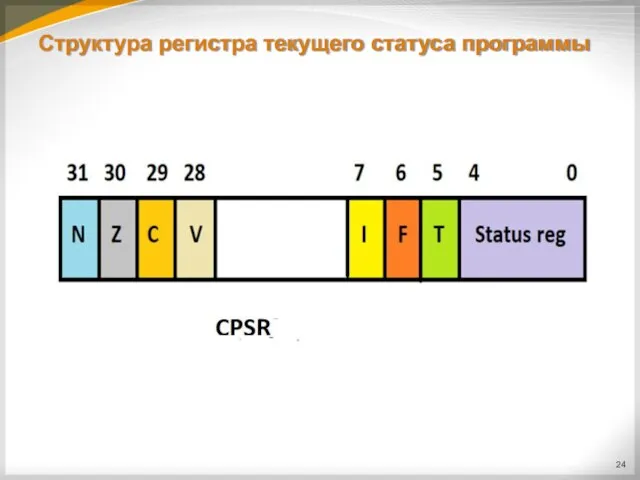

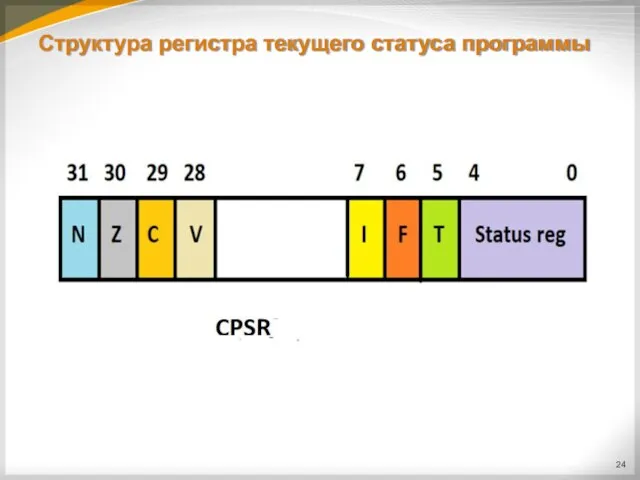

Слайд 24Структура регистра текущего статуса программы

Слайд 25 Флаги состояний.

N – флаг знака результата операции.

Z – флаг нулевого результата

операции.

C – флаг переноса.

V – флаг переполнения.

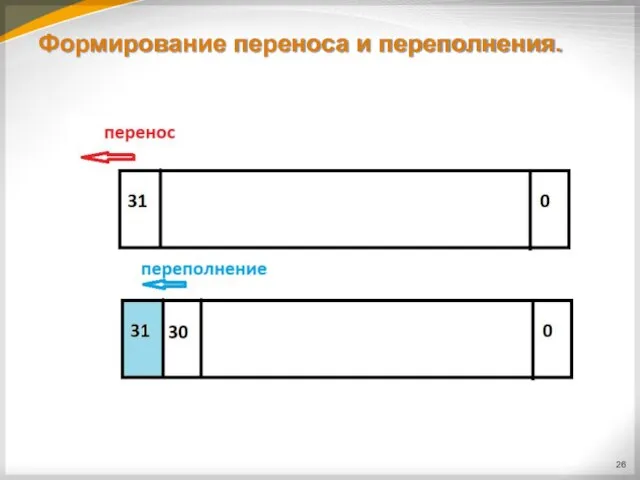

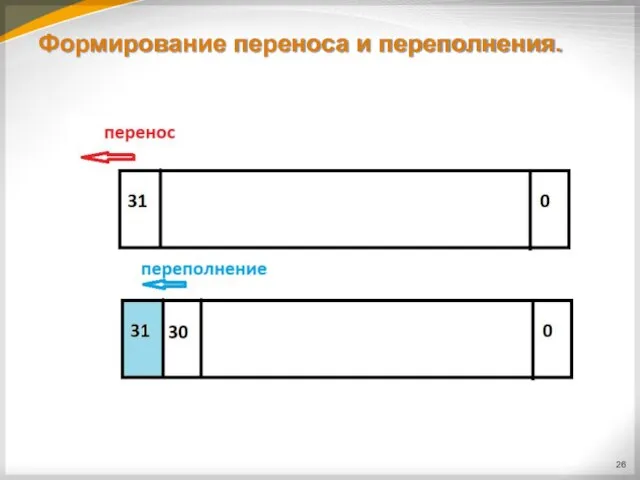

Слайд 26Формирование переноса и переполнения.

10 правил здорового образа жизни

10 правил здорового образа жизни Специфика олимпиадных заданий по этимологии

Специфика олимпиадных заданий по этимологии Мышление формирует нашу жизнь

Мышление формирует нашу жизнь Правоохранительные органы. Введение в дисциплину. (Тема 1)

Правоохранительные органы. Введение в дисциплину. (Тема 1) Урок-морское путешествие

Урок-морское путешествие Работа ШМО учителей русского языка и литературы МОУ «СОШ № 12» по подготовке учащихся к ЕГЭ и ГИА

Работа ШМО учителей русского языка и литературы МОУ «СОШ № 12» по подготовке учащихся к ЕГЭ и ГИА Семейный квест. Профилактика подростковых проблем средствами восстановления отношений подросток - родитель

Семейный квест. Профилактика подростковых проблем средствами восстановления отношений подросток - родитель Breslau europaeische Kulturhauptstadt

Breslau europaeische Kulturhauptstadt Презентация по английскому Idioms

Презентация по английскому Idioms  Технология перевозок по маршрутам

Технология перевозок по маршрутам Dental health education

Dental health education Что создавалось трудом крестьянина

Что создавалось трудом крестьянина ПОРТФОЛИО

ПОРТФОЛИО Классификация и устройство копировальных аппаратов

Классификация и устройство копировальных аппаратов Аренда недвижимого имущества по междисциплинарному курсу (учебной дисциплине)

Аренда недвижимого имущества по междисциплинарному курсу (учебной дисциплине) Животный мир Америки

Животный мир Америки Модуль числа (6 класс)

Модуль числа (6 класс) Реализация изъятого оборудованияООО «РМБ-лизинг»

Реализация изъятого оборудованияООО «РМБ-лизинг» Презентация на тему Растения и их классификация

Презентация на тему Растения и их классификация Использование анимации

Использование анимации Ислам. Пророк Мухаммед

Ислам. Пророк Мухаммед МЕДВЕДЬ — ЭТО ХИЩНИК?

МЕДВЕДЬ — ЭТО ХИЩНИК? Плоские черви 7 класс

Плоские черви 7 класс Страны Западной Европы

Страны Западной Европы Выборы губернатора Cанкт-Петербурга 8 сентрября 2019 г

Выборы губернатора Cанкт-Петербурга 8 сентрября 2019 г Генетика и медицина

Генетика и медицина Портфолио дошкольника странички

Портфолио дошкольника странички Моя малая родина. Природа, культура, этнос

Моя малая родина. Природа, культура, этнос