Содержание

- 2. Архитектура компьютера ( по Фон-Нейману)

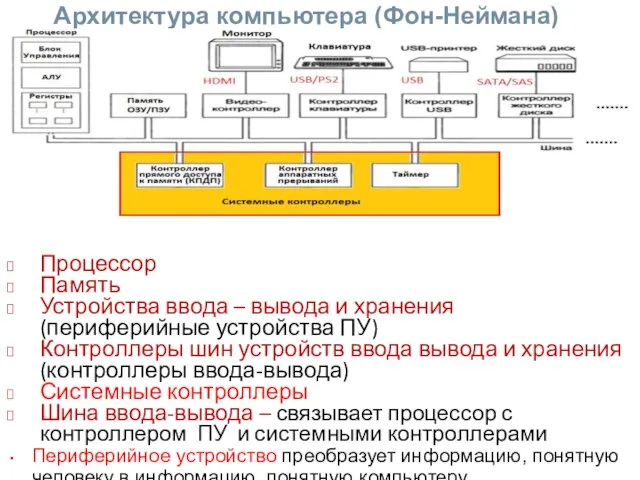

- 3. Архитектура компьютера (Фон-Неймана) Процессор Память Устройства ввода – вывода и хранения (периферийные устройства ПУ) Контроллеры шин

- 4. Обобщенная архитектура процессора

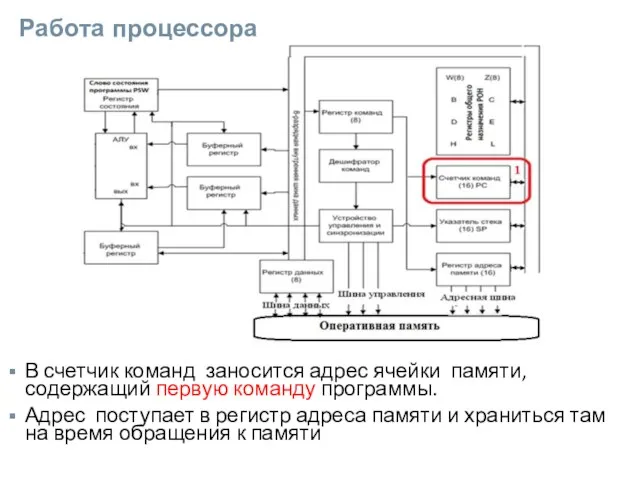

- 5. Работа процессора В счетчик команд заносится адрес ячейки памяти, содержащий первую команду программы. Адрес поступает в

- 6. Работа процессора Адрес команды через регистр адреса поступает на шину адреса памяти. По сигналу управления процессор

- 7. Работа процессора Из регистра данных текущая команда поступает в регистр команды. Там команда дешифруется и анализируется

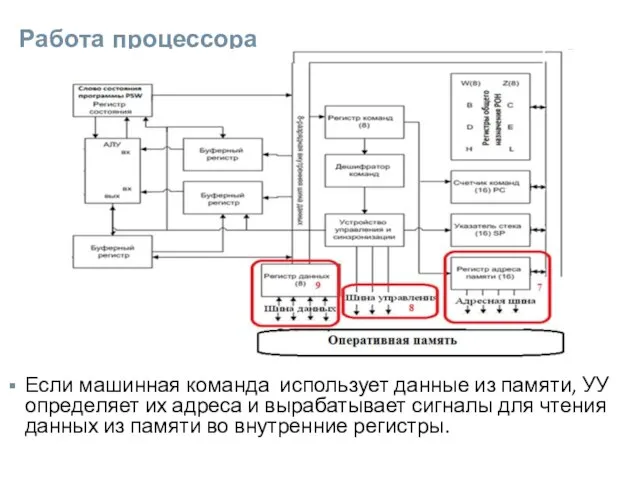

- 8. Работа процессора Если машинная команда использует данные из памяти, УУ определяет их адреса и вырабатывает сигналы

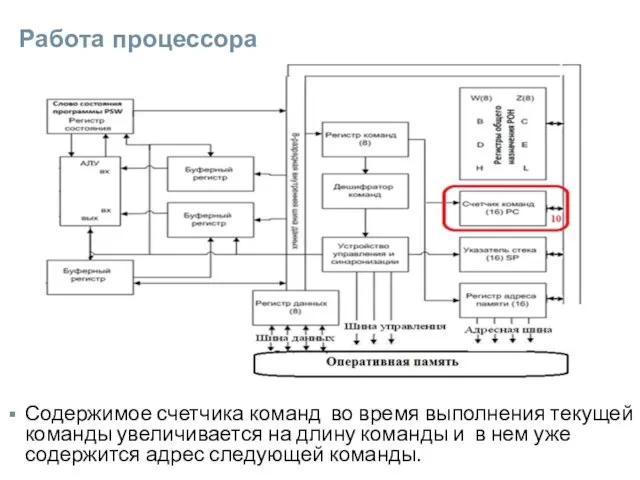

- 9. Работа процессора Содержимое счетчика команд во время выполнения текущей команды увеличивается на длину команды и в

- 10. Работа процессора АЛУ выполняет операцию над данными, находящимися в регистрах и сохраняет результат в аккумуляторе.

- 11. Работа процессора В регистре слова состояния программы устанавливаются признаки выполнения команды

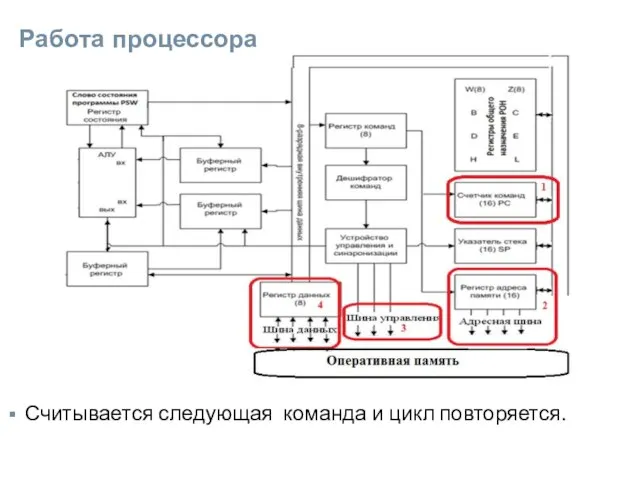

- 12. Работа процессора Считывается следующая команда и цикл повторяется.

- 13. Шина или аппаратный интерфейс Набор аппаратных средства и правила обмена (протоколов), обеспечивающих взаимосвязь устройств между собой

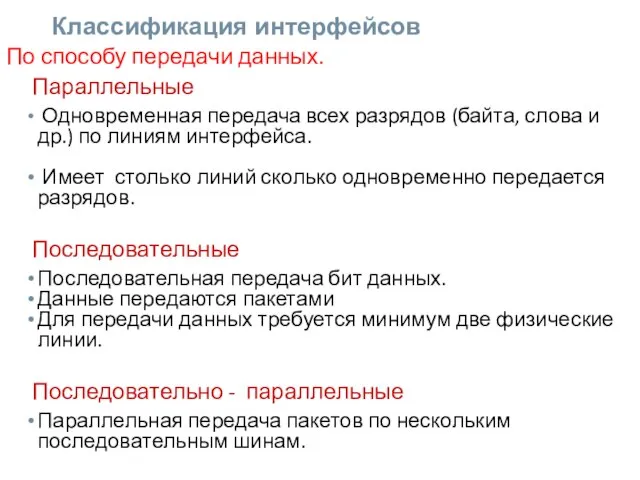

- 14. Классификация интерфейсов По способу передачи данных. Параллельные Одновременная передача всех разрядов (байта, слова и др.) по

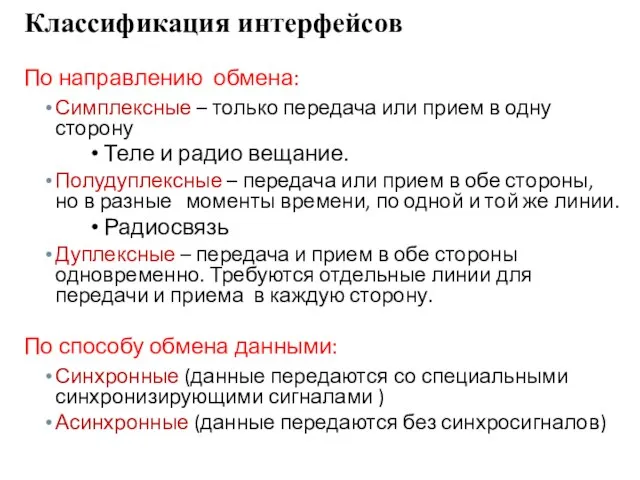

- 15. По направлению обмена: Симплексные – только передача или прием в одну сторону Теле и радио вещание.

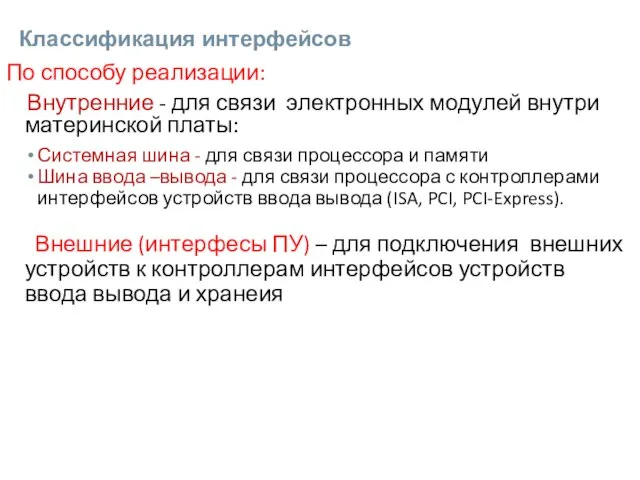

- 16. Классификация интерфейсов По способу реализации: Внутренние - для связи электронных модулей внутри материнской платы: Системная шина

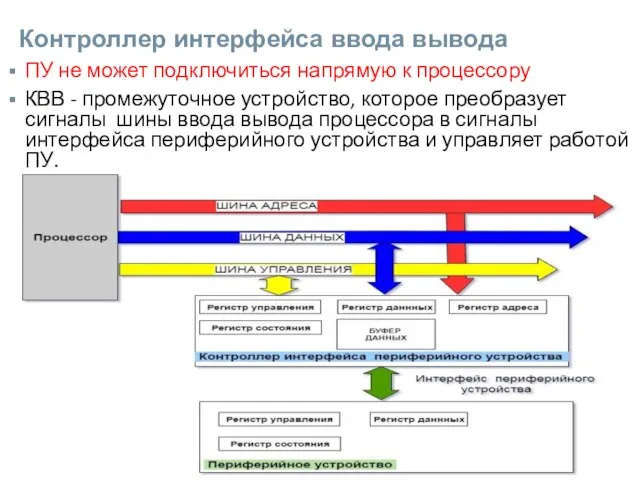

- 17. Контроллер интерфейса ввода вывода ПУ не может подключиться напрямую к процессору КВВ - промежуточное устройство, которое

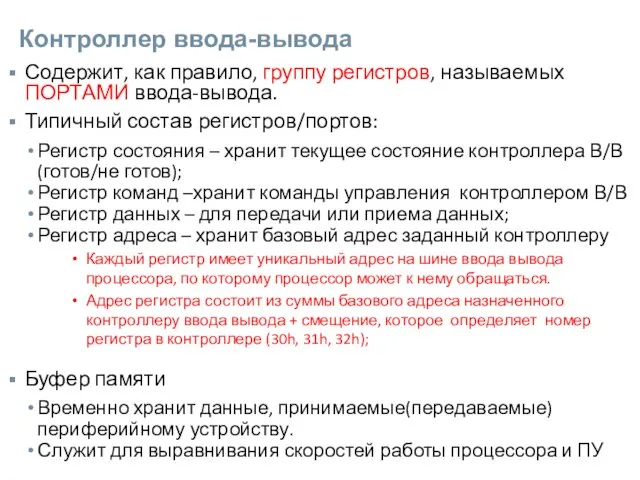

- 18. Контроллер ввода-вывода Содержит, как правило, группу регистров, называемых ПОРТАМИ ввода-вывода. Типичный состав регистров/портов: Регистр состояния –

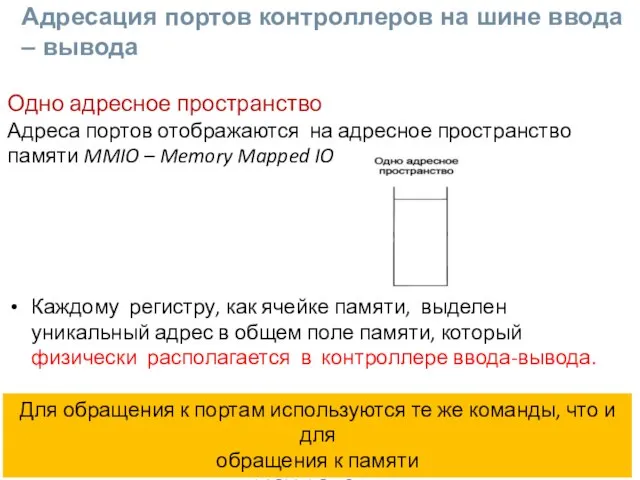

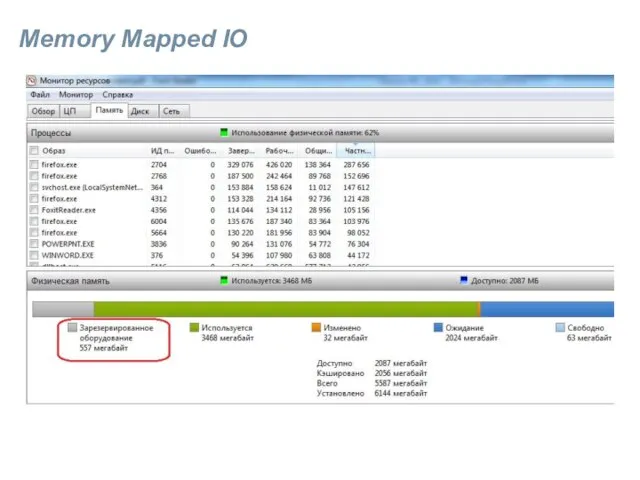

- 19. Одно адресное пространство Адреса портов отображаются на адресное пространство памяти MMIO – Memory Mapped IO Каждому

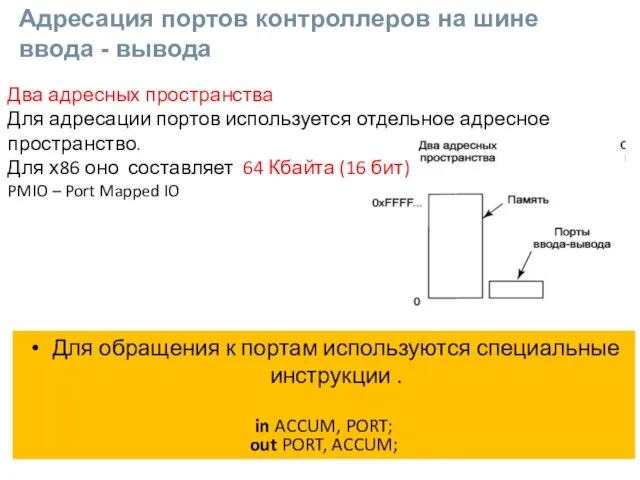

- 20. Для обращения к портам используются специальные инструкции . in ACCUM, PORT; out PORT, ACCUM; Адресация портов

- 21. Используется в х86; Внутренняя память (буфер) контроллера (если имеется) , находится в адресном пространстве памяти, а

- 22. Memory Mapped IO

- 23. ОРГАНИЗАЦИЯ КОМПЬЮТЕРНОЙ АРХИТЕКТУРЫ НА БАЗЕ ПРОЦЕССОРА Х8086

- 24. Intel 8008 Intel 8008 (апрель 1972 ) первый 8-битный процессор, для продвинутых калькуляторов, терминалов ввода-вывода; Тактовая

- 25. Intel 8080 Intel 8080 (апрель 1974 года ) — 8-битный микропроцессор Количество регистров: 7 Разрядность регистров:

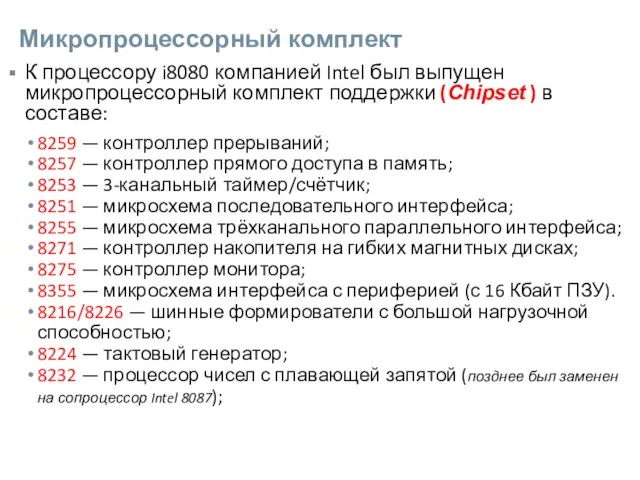

- 26. Микропроцессорный комплект К процессору i8080 компанией Intel был выпущен микропроцессорный комплект поддержки (Сhipset ) в составе:

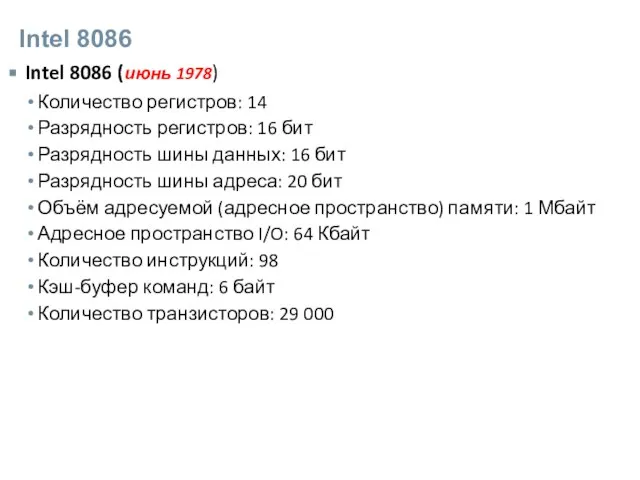

- 27. Intel 8086 Intel 8086 (июнь 1978) Количество регистров: 14 Разрядность регистров: 16 бит Разрядность шины данных:

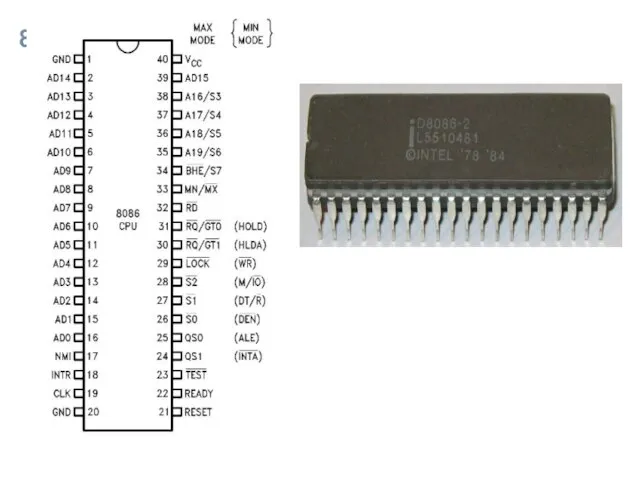

- 28. 8086

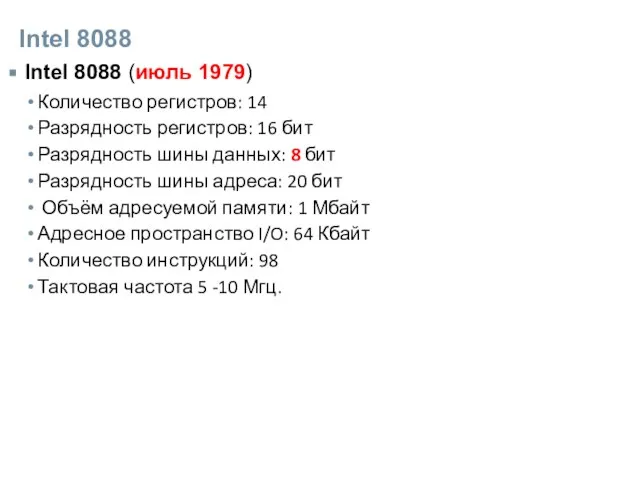

- 29. Intel 8088 Intel 8088 (июль 1979) Количество регистров: 14 Разрядность регистров: 16 бит Разрядность шины данных:

- 30. Структурная схема i8086

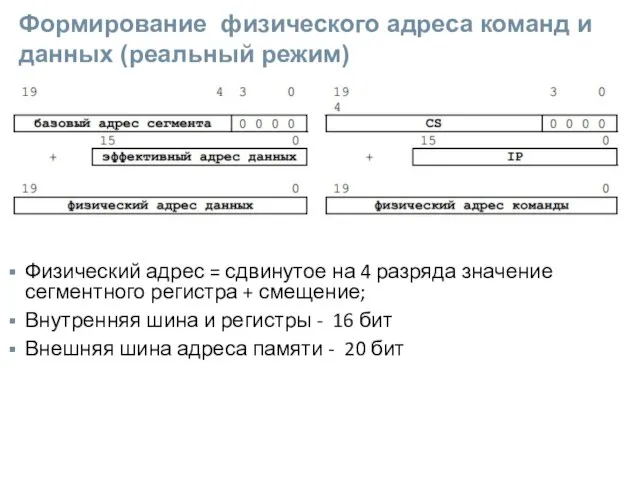

- 31. Формирование физического адреса команд и данных (реальный режим) Физический адрес = сдвинутое на 4 разряда значение

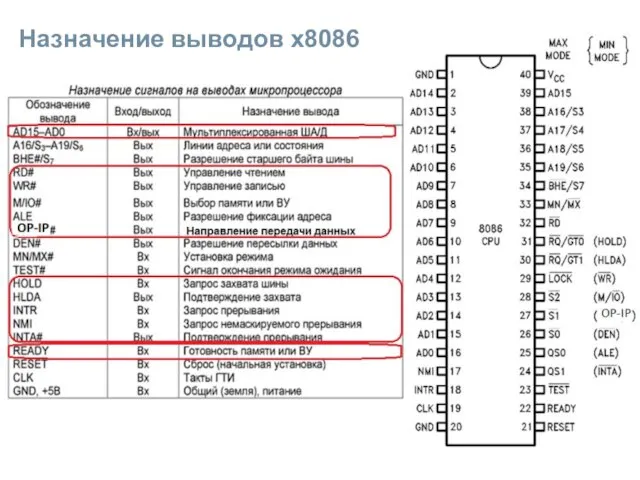

- 32. Назначение выводов х8086

- 33. Машинный цикл процессора (чтение/запись ) Машинный цикл чтения / записи занимает четыре такта генератора Частота тактового

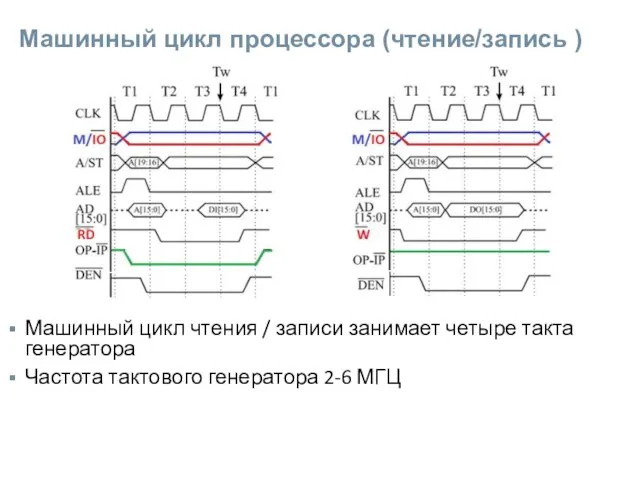

- 34. Минимальный режим Минимальный – сигналы управления внешней шиной вырабатывает один процессор

- 35. Максимальный режим Мультипроцессорный режим - для подключения нескольких процессоров (сопроцессора) к общей шине . Сигналы управления

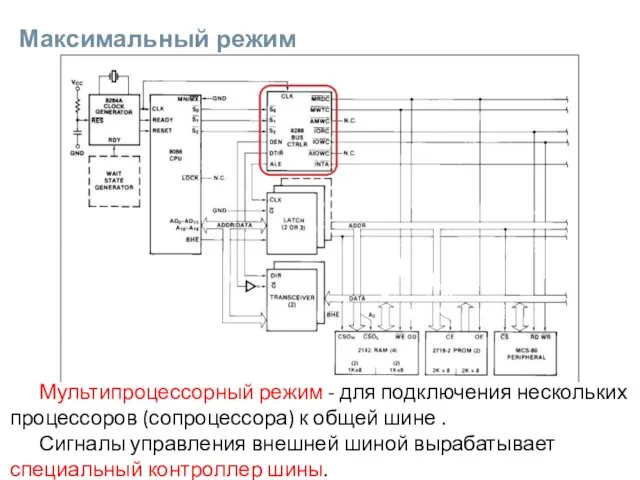

- 36. Структурная схема IBM PC XT Сигнал CS =0 переводит выходы соответствующего контроллера из третьего состояния (выводит

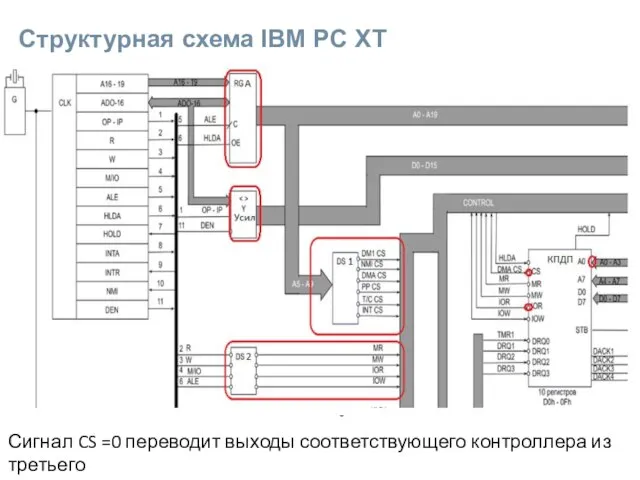

- 37. Схема включения процессора RGA – регистр адреса Служит для хранения адреса памяти или порта В/В на

- 38. Обобщенная схема

- 39. Контроллер прямого доступа к памяти КПДП запись в регистры

- 40. Контроллер прерываний и трехканальный таймер

- 41. Программируемы параллельный интерфейс ROM, RAM

- 42. Слоты расширения

- 43. Контроллер прямого доступа Контроллер прямого доступа к памяти (DMA - Direct Memory Access) обеспечивает высокоскоростной обмен

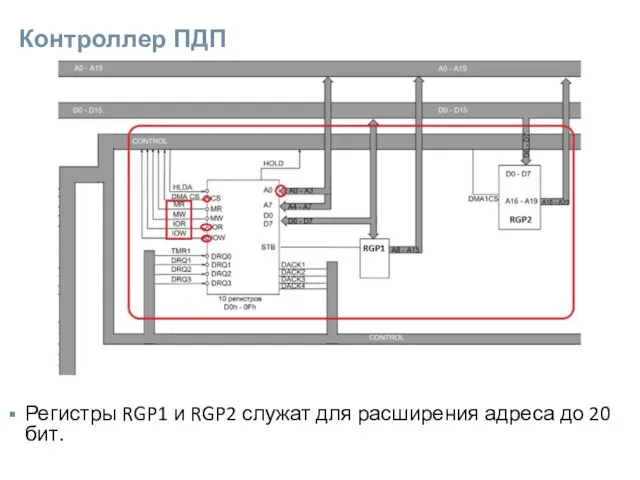

- 44. Контроллер ПДП Регистры RGP1 и RGP2 служат для расширения адреса до 20 бит.

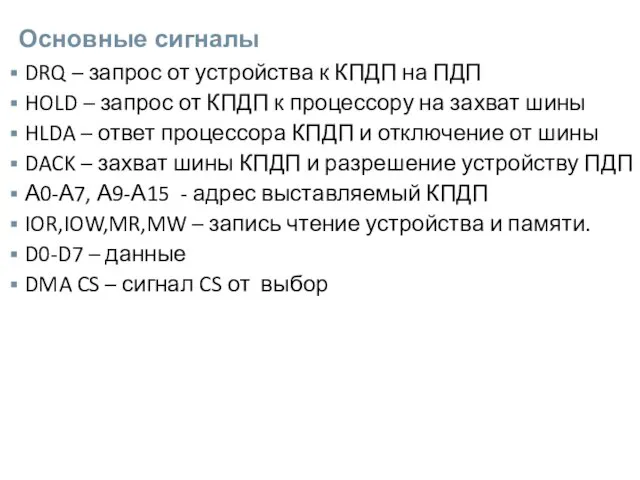

- 45. Основные сигналы DRQ – запрос от устройства к КПДП на ПДП HOLD – запрос от КПДП

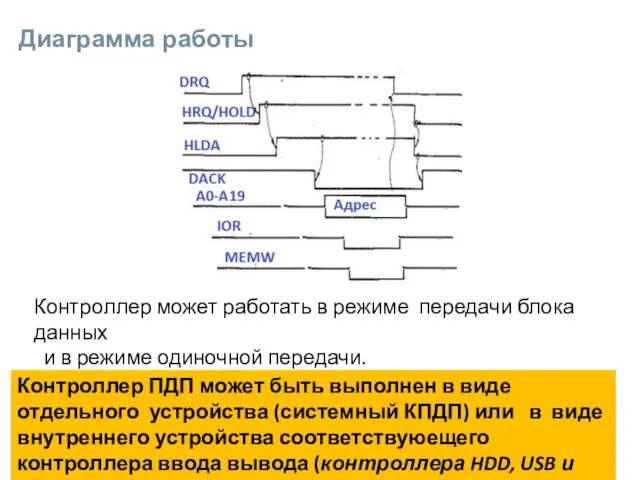

- 46. Диаграмма работы Контроллер может работать в режиме передачи блока данных и в режиме одиночной передачи. Контроллер

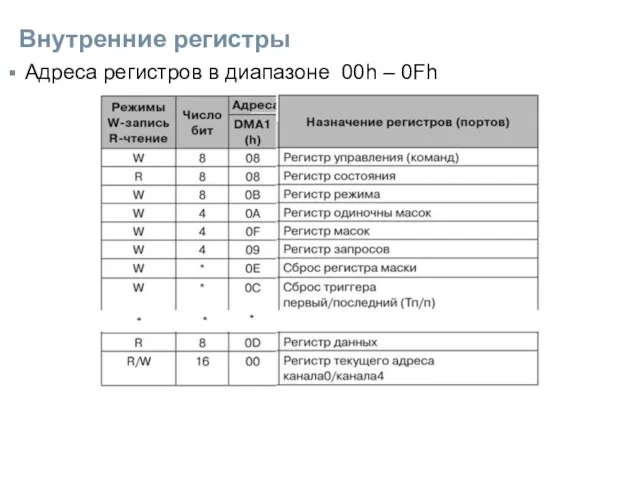

- 47. Внутренние регистры Адреса регистров в диапазоне 00h – 0Fh

- 48. Последовательность передачи при ПДП на примере контроллера HDD

- 49. Инициализация контроллера DMA Процессор «знает» с какой областью памяти работает внешнее устройство (начальный адрес области памяти

- 50. Последовательность операций при ПДП 1. Инициализация контроллера 2. Принять Запрос (DRЕQ) на ПДП от контроллера HDD

- 51. Внутренняя структура

- 52. Каскадирование контроллеров ПДП

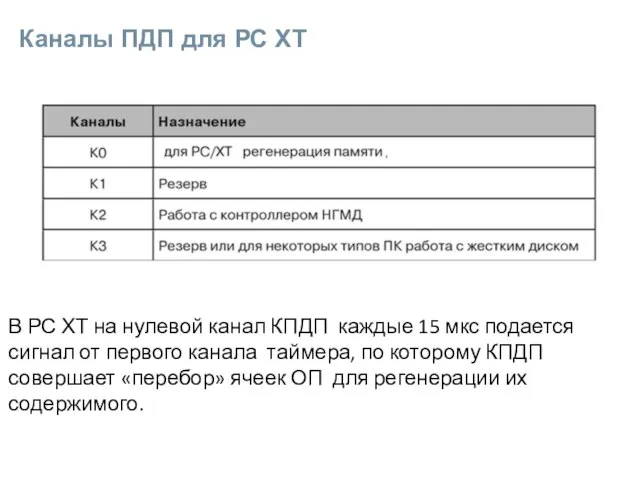

- 53. Каналы ПДП для РС ХТ В РС ХТ на нулевой канал КПДП каждые 15 мкс подается

- 54. Контроллер прерываний i8259 IRQ0-IRQ7 входы запросов на прерывание INTCS – выбор чипа контроллера прерываний от дешифратора

- 55. Контроллер прерываний i8259

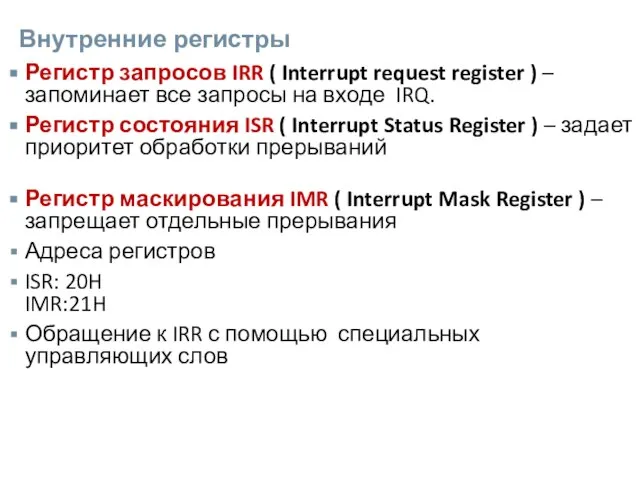

- 56. Внутренние регистры Регистр запросов IRR ( Interrupt request register ) – запоминает все запросы на входе

- 57. Временная диаграмма

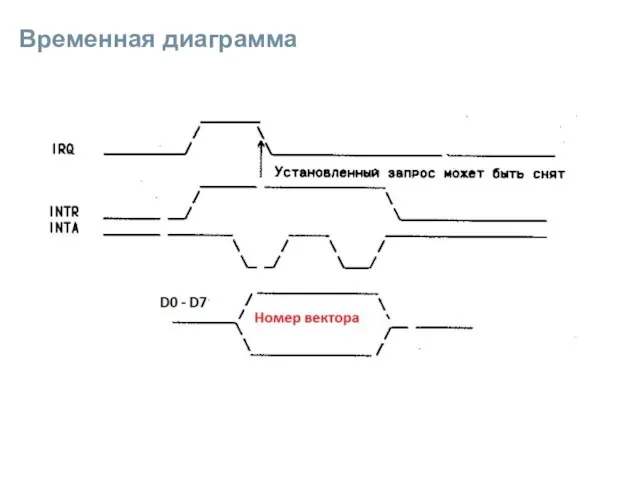

- 58. Порядок операций при прерывании 1. Инициализация контроллера 2. Контроллер устройства В/В вырабатывает сигнал запроса на прерывание,

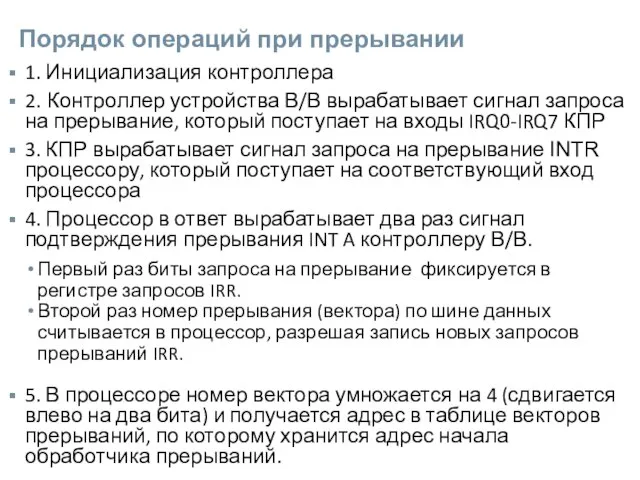

- 59. Приоритеты прерываний IRQ# Номер вектора Устройство 0 08h Системный таймер 1 09h Клавиатура 2 0Ah Зарезервировано(2-ой

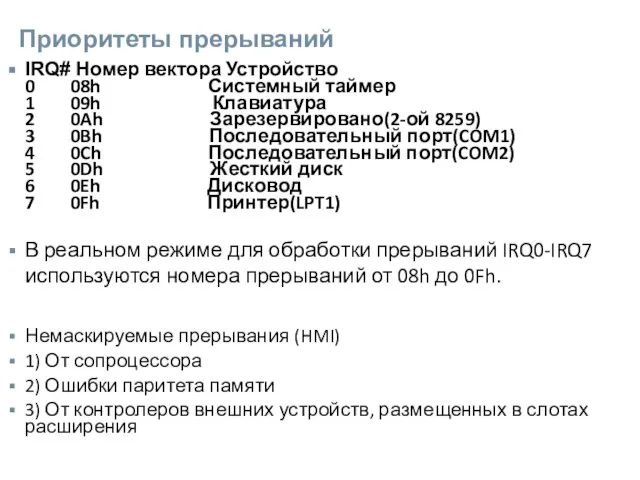

- 60. Инициализация контроллера Программирование i8259 осуществляется двумя типами управляющих слов: Командные слова инициализации ICW (Initialization Command Word)

- 61. Каскадирование контроллеров

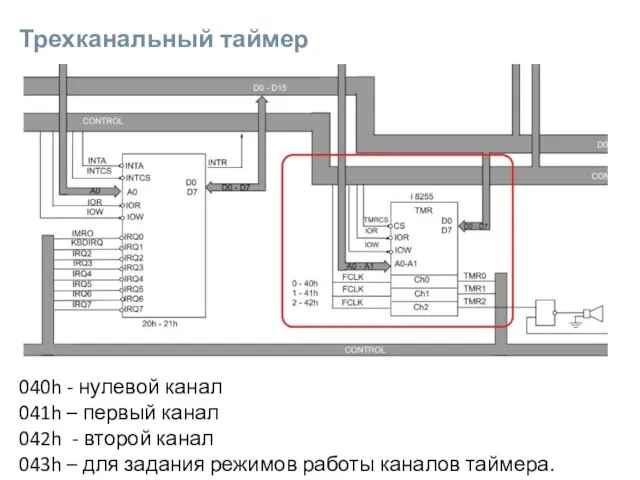

- 62. Трехканальный таймер 040h - нулевой канал 041h – первый канал 042h - второй канал 043h –

- 63. Таймер i8253 Каждый канал представляет собой независимый счетчик с программно-управляемым коэффициентом пересчета, который может работать в

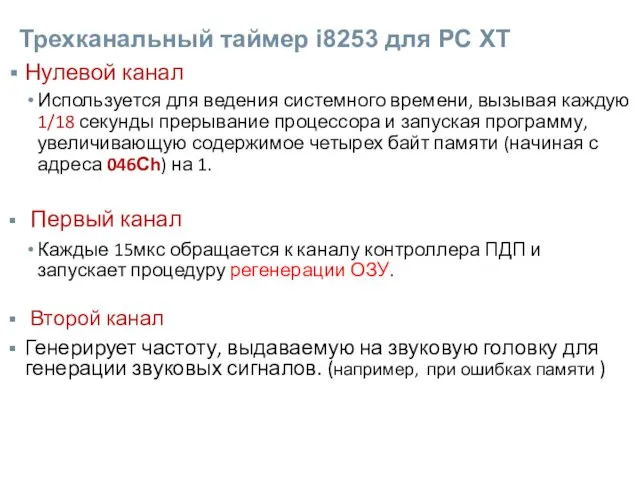

- 64. Трехканальный таймер i8253 для РС ХТ Нулевой канал Используется для ведения системного времени, вызывая каждую 1/18

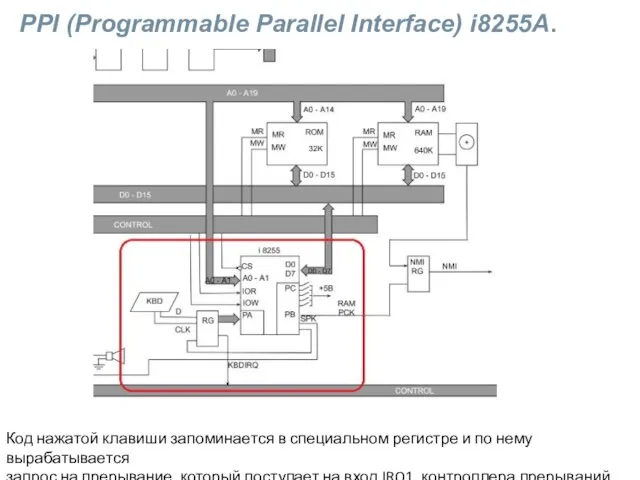

- 65. PPI (Programmable Parallel Interface) i8255A. Код нажатой клавиши запоминается в специальном регистре и по нему вырабатывается

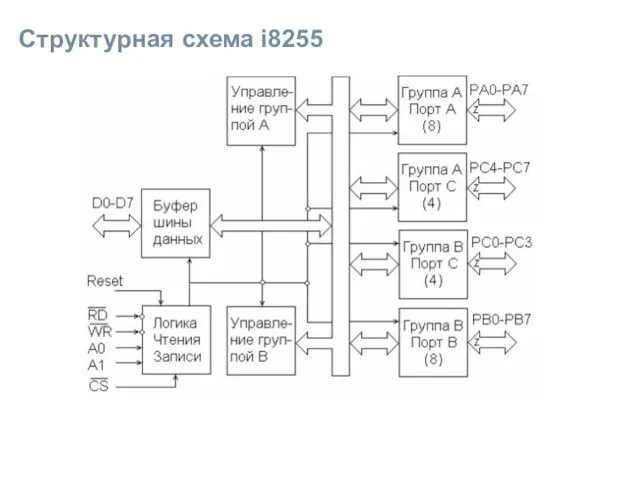

- 66. Структурная схема i8255

- 67. Программируемый параллельный интерфейс PPI (Programmable Parallel Interface) i8255A. Включает три двунаправленных байтовых порта (А, В и

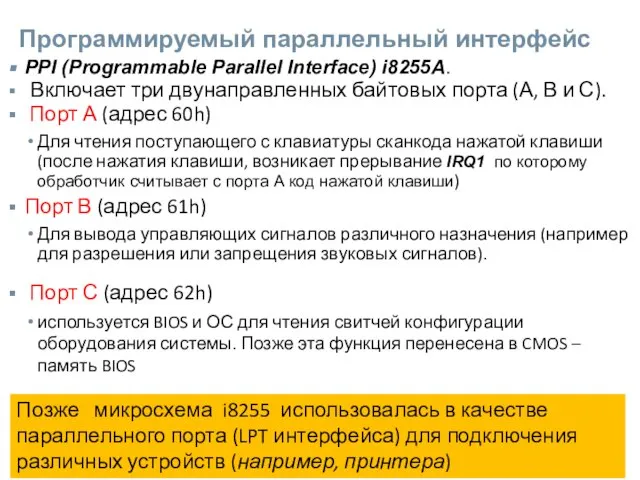

- 68. Универсальный последовательный синхронно-асинхронный приемо-передатчик i8251 (COM порт) USART – Universal Synchronous/Asynchronous Resiver/Тransmitter Реализует синхронно-асинхронными канал последовательной

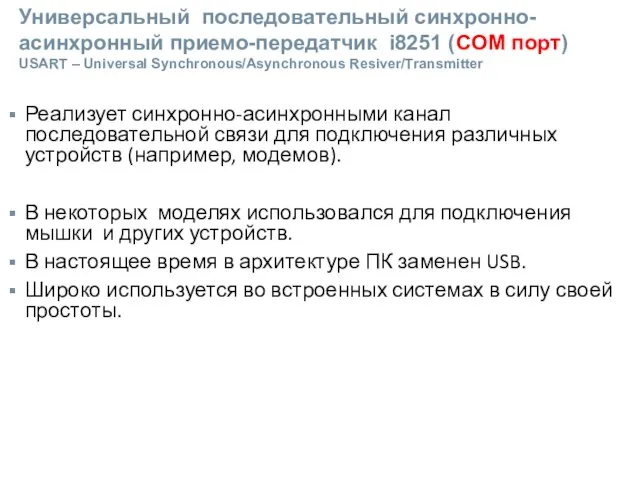

- 69. Структурная схема В состав входят передатчик, приемник, буфер шины данных и схемы управления передатчиком, приемником

- 70. Cтруктура шина ISA Проц. ОЗУ Сист. К Кон. Пр. К П Д П Кон.В-В Кон.В-В ISA

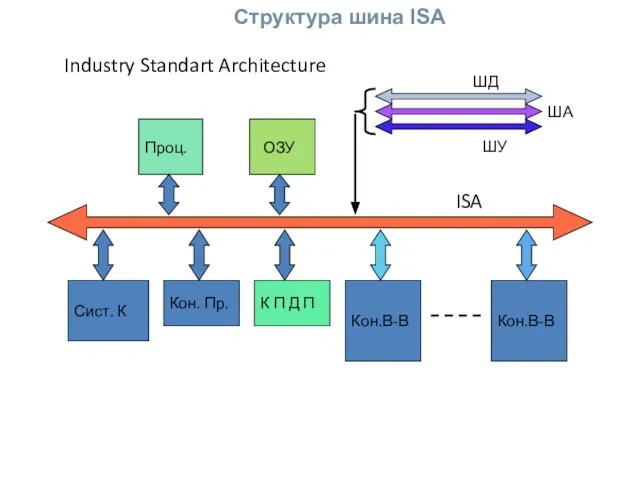

- 72. Скачать презентацию

Процессы тепловлажностной обработки воздуха при контакте с водой

Процессы тепловлажностной обработки воздуха при контакте с водой  1

1 Дробные числа

Дробные числа Герберт Спенсер

Герберт Спенсер В мастерской художника-графика

В мастерской художника-графика Калинина Татьяна Васильевна

Калинина Татьяна Васильевна ТЕОРИЯ ВЕРОЯТНОСТЕЙ НА ЕГЭ ПО МАТЕМАТИКЕ

ТЕОРИЯ ВЕРОЯТНОСТЕЙ НА ЕГЭ ПО МАТЕМАТИКЕ Технология установки дверного замка

Технология установки дверного замка 6-8 классы

6-8 классы Будни и праздники начальной школы 2014-2018

Будни и праздники начальной школы 2014-2018 Виды искусств. Искусство слова, звука, изображения. Храм искусств

Виды искусств. Искусство слова, звука, изображения. Храм искусств Свойства корня n-й степени

Свойства корня n-й степени Презентация на тему орган вкуса

Презентация на тему орган вкуса  Meet and assist service

Meet and assist service Язык неразрывно связан с культурой и традициями народа

Язык неразрывно связан с культурой и традициями народа Бизнес-кейс от компании SUN InBev

Бизнес-кейс от компании SUN InBev Здоровый образ жизни

Здоровый образ жизни Какво е Twitter и има ли почва у нас?. Еволюция или революция... Какво е Twitter?

Какво е Twitter и има ли почва у нас?. Еволюция или революция... Какво е Twitter? Шайдуллина Ю.Р. Требования к ДОУ

Шайдуллина Ю.Р. Требования к ДОУ Урок алгебры и начал анализа

Урок алгебры и начал анализа Отдел Опеки, попечительства и патронажа

Отдел Опеки, попечительства и патронажа Stefani Joanne Angelina Germanotta

Stefani Joanne Angelina Germanotta Интернет-эквайриг

Интернет-эквайриг Детский сад будущего

Детский сад будущего Презентация новинки в ассортименте тм Test

Презентация новинки в ассортименте тм Test Презентация на тему Жан Батист Пьер Антуан де Моне Ламарк

Презентация на тему Жан Батист Пьер Антуан де Моне Ламарк Влияние комнатных растений на человека

Влияние комнатных растений на человека CASE-средство IBM Rational Rose

CASE-средство IBM Rational Rose