Содержание

- 2. Цели и задачи Получение навыков создания моделей при помощи языка VHDL Описание цифровых систем при помощи

- 3. Структура курса Введение Основные элементы языка VHDL Методы моделирования на VHDL Синтез цифровых систем Иерархический дизайн

- 4. Основы языка VHDL Введение

- 5. Основы VHDL Язык VHDL утвержден на уровне отраслевых стандартов (IEEE) как программное средство для описания аппаратных

- 6. Основные определения HDL – Hardware description language, язык описания аппаратных средств Поведенческое моделирование: (Behavior modeling) –

- 7. Register Transfer Layer (RTL) – Уровень проектирования (Уровень регистрового обмена) Синтез – трансляция с уровня описания

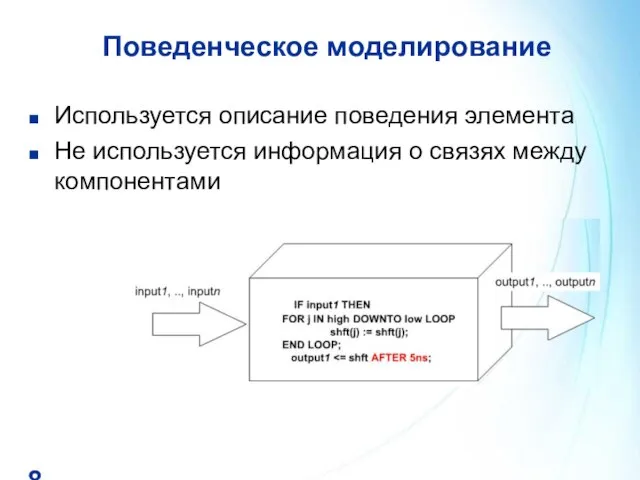

- 8. Поведенческое моделирование Используется описание поведения элемента Не используется информация о связях между компонентами

- 9. Структурное моделирование Функциональное и структурное описание объекта моделирования Возможно использование аппаратно зависимых ресурсов

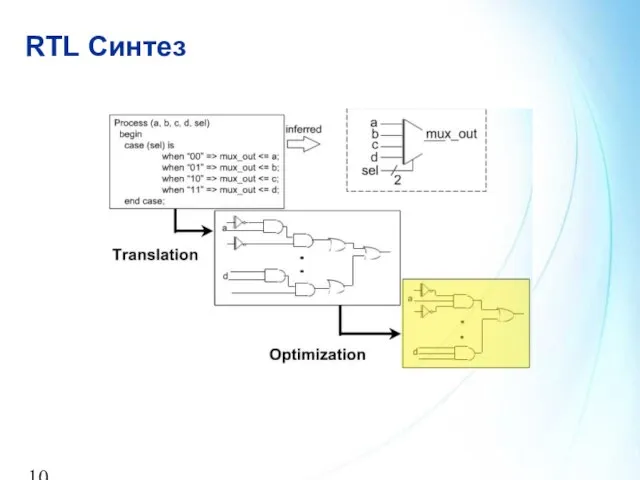

- 10. RTL Синтез

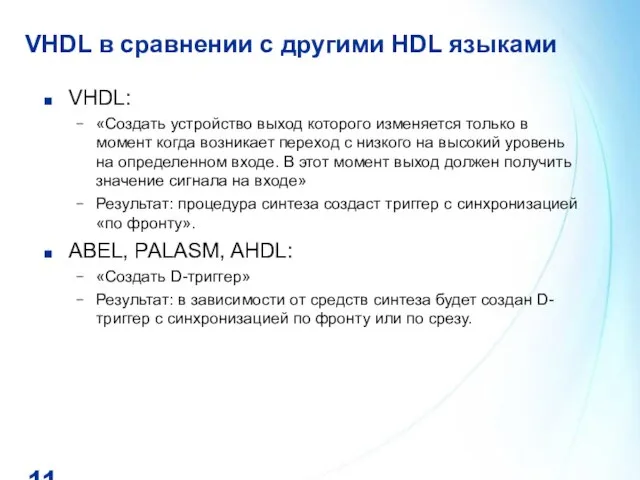

- 11. VHDL в сравнении с другими HDL языками VHDL: «Создать устройство выход которого изменяется только в момент

- 12. Некоторые особенности VHDL Два подмножества конструкций языка: Синтезируемые конструкции Конструкции для моделирования Язык VHDL нечувствителен к

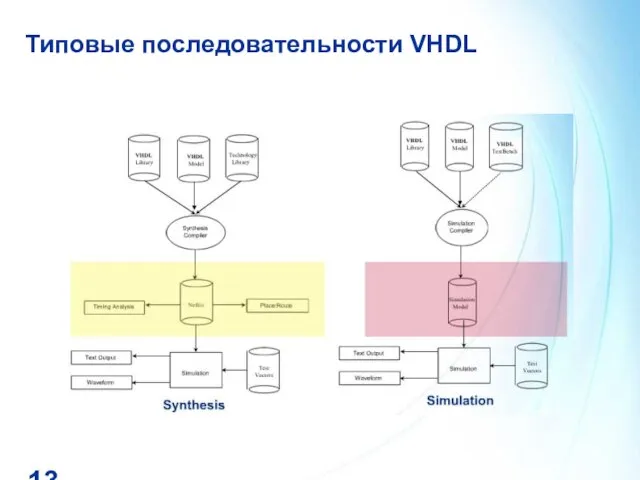

- 13. Типовые последовательности VHDL

- 14. Основы языка VHDL Основные конструкции VHDL

- 15. Основные элементы языка VHDL Entity Используется для описания интерфейса модели. Architecture Используется для описания поведения модели.

- 16. Объявление ENTITY ENTITY IS Generic declarations Port declarations END ; (Версия 1076-1987) END ENTITY ; (Версия

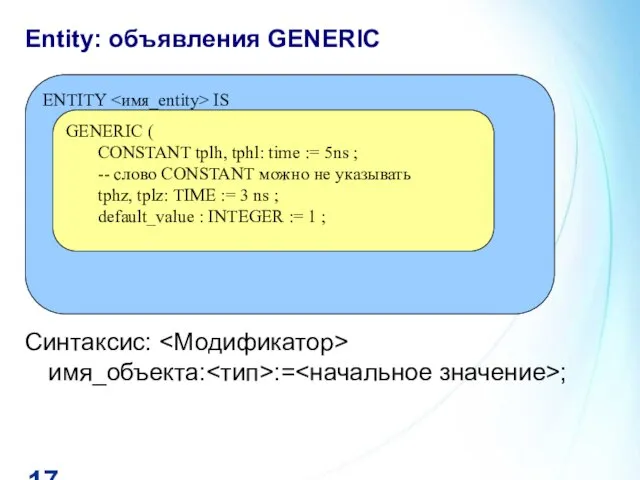

- 17. Entity: объявления GENERIC Синтаксис: имя_объекта: := ; ENTITY IS GENERIC ( CONSTANT tplh, tphl: time :=

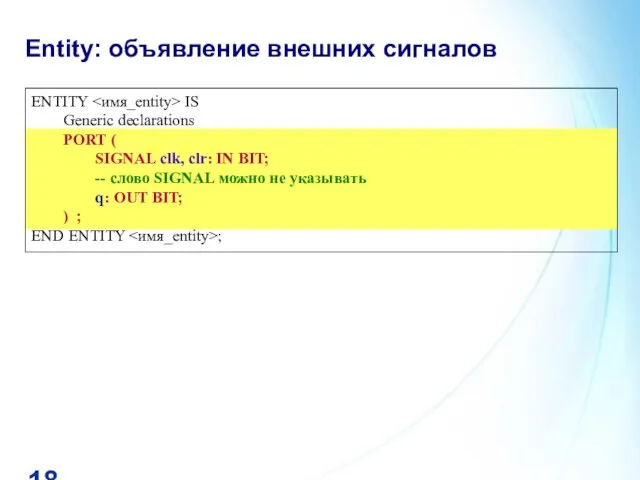

- 18. Entity: объявление внешних сигналов ENTITY IS Generic declarations PORT ( SIGNAL clk, clr: IN BIT; --

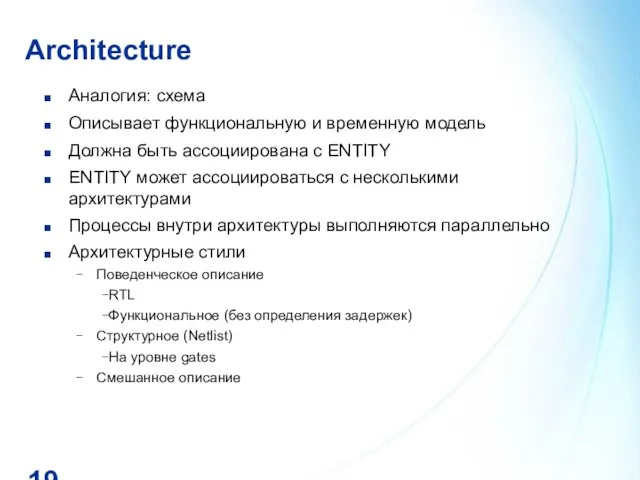

- 19. Architecture Аналогия: схема Описывает функциональную и временную модель Должна быть ассоциирована с ENTITY ENTITY может ассоциироваться

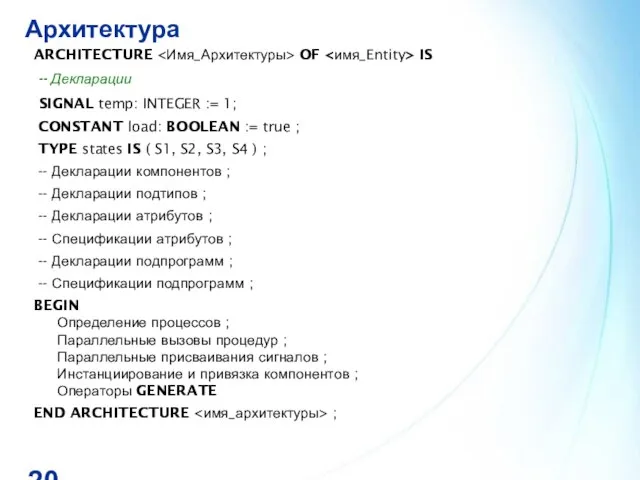

- 20. Архитектура ARCHITECTURE OF IS -- Декларации SIGNAL temp: INTEGER := 1; CONSTANT load: BOOLEAN := true

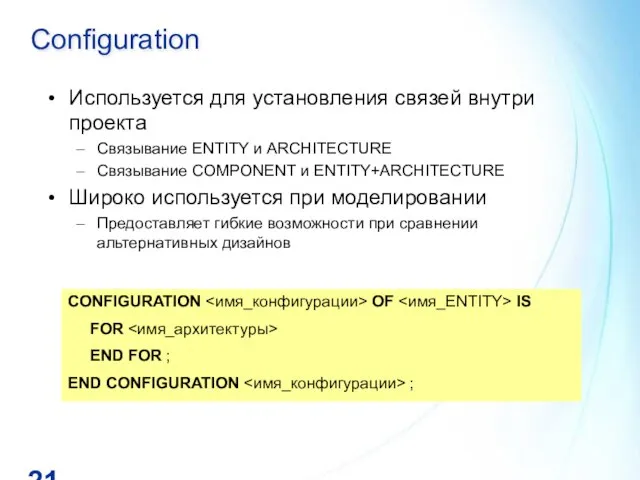

- 21. Configuration Используется для установления связей внутри проекта Связывание ENTITY и ARCHITECTURE Связывание COMPONENT и ENTITY+ARCHITECTURE Широко

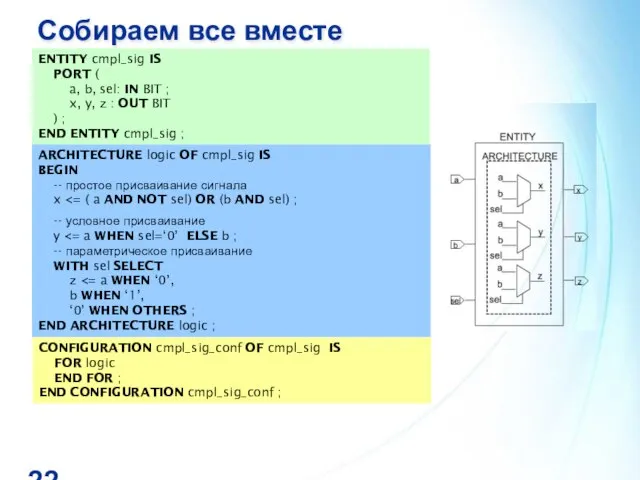

- 22. Собираем все вместе ENTITY cmpl_sig IS PORT ( a, b, sel: IN BIT ; x, y,

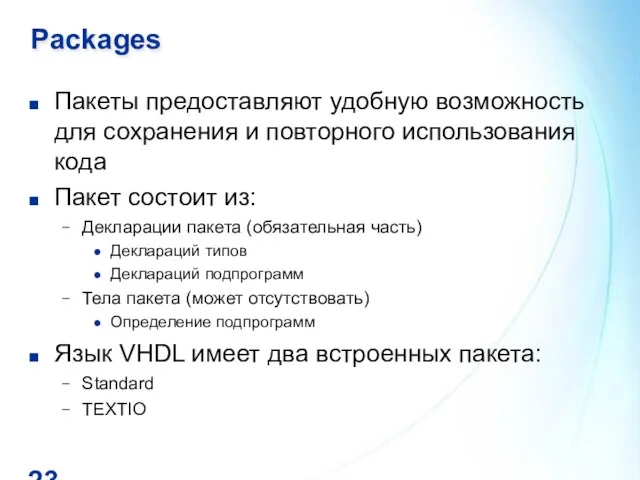

- 23. Packages Пакеты предоставляют удобную возможность для сохранения и повторного использования кода Пакет состоит из: Декларации пакета

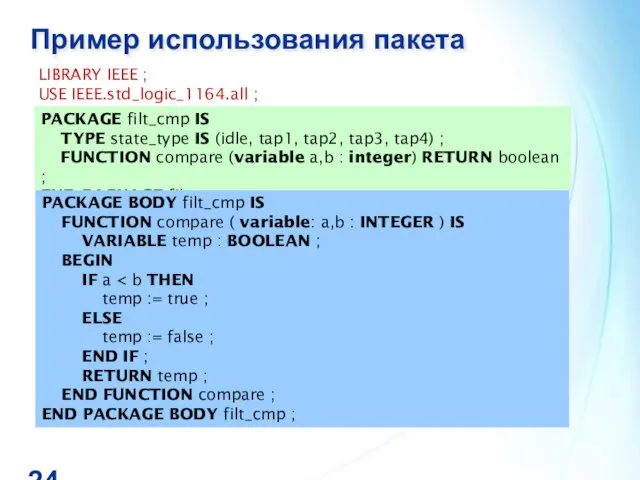

- 24. Пример использования пакета LIBRARY IEEE ; USE IEEE.std_logic_1164.all ; PACKAGE filt_cmp IS TYPE state_type IS (idle,

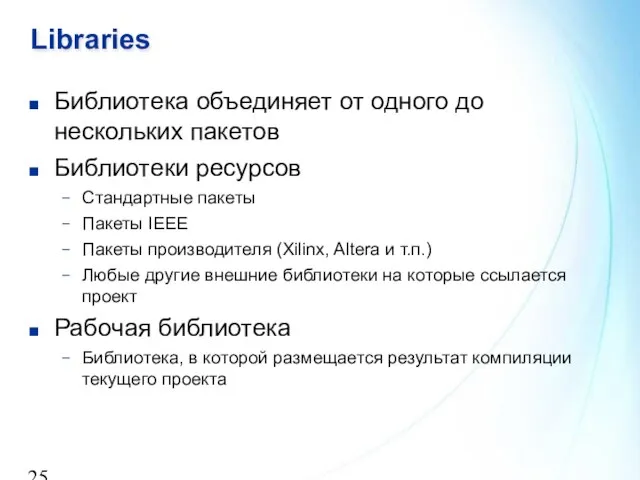

- 25. Libraries Библиотека объединяет от одного до нескольких пакетов Библиотеки ресурсов Стандартные пакеты Пакеты IEEE Пакеты производителя

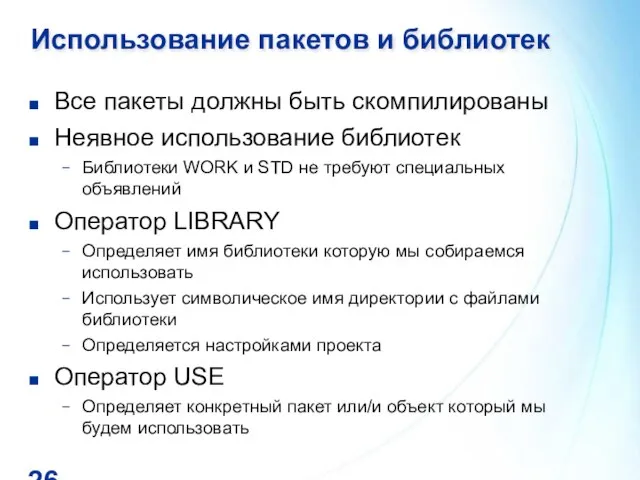

- 26. Использование пакетов и библиотек Все пакеты должны быть скомпилированы Неявное использование библиотек Библиотеки WORK и STD

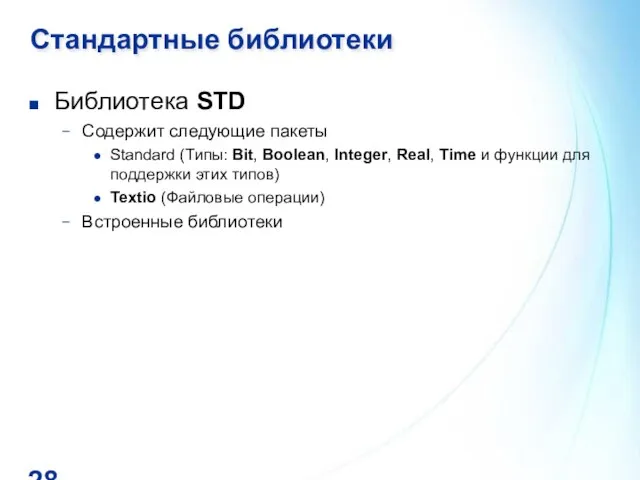

- 28. Стандартные библиотеки Библиотека STD Содержит следующие пакеты Standard (Типы: Bit, Boolean, Integer, Real, Time и функции

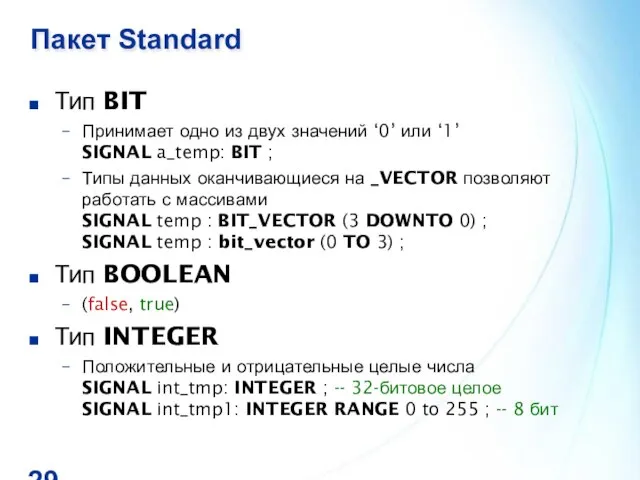

- 29. Пакет Standard Тип BIT Принимает одно из двух значений ‘0’ или ‘1’ SIGNAL a_temp: BIT ;

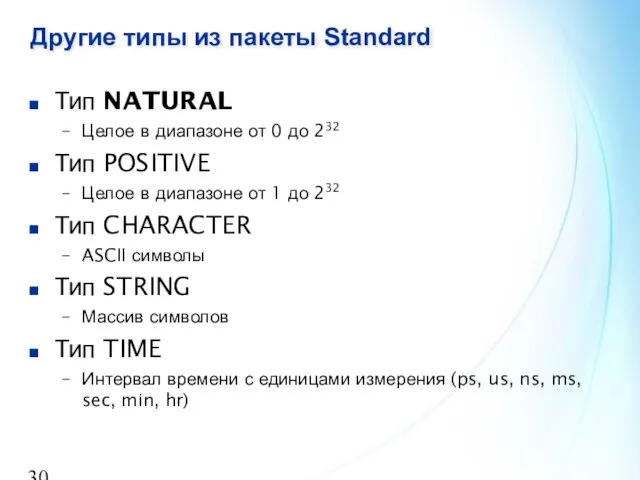

- 30. Другие типы из пакеты Standard Тип NATURAL Целое в диапазоне от 0 до 232 Тип POSITIVE

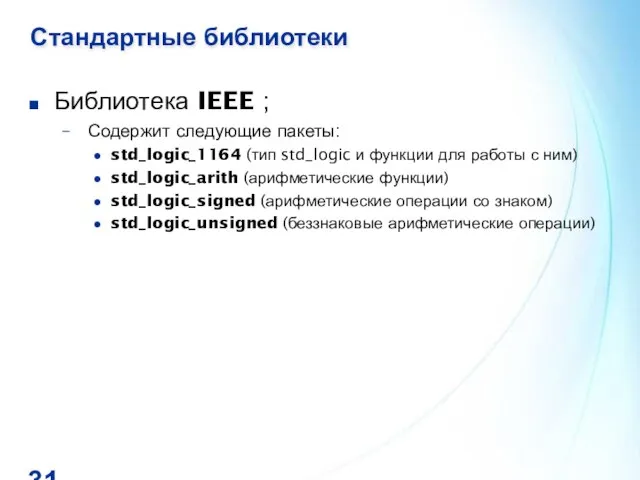

- 31. Стандартные библиотеки Библиотека IEEE ; Содержит следующие пакеты: std_logic_1164 (тип std_logic и функции для работы с

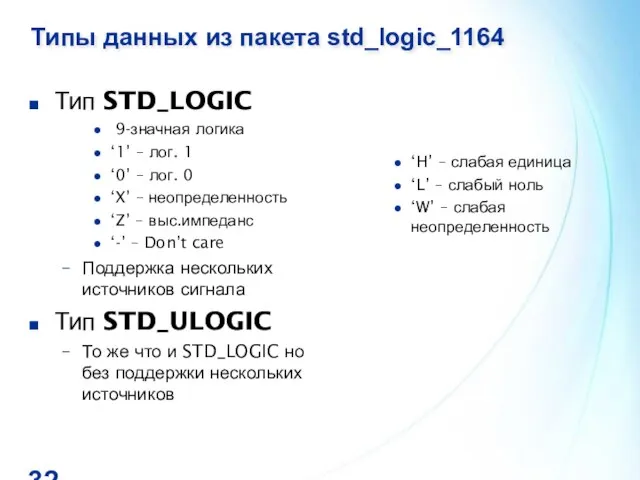

- 32. Типы данных из пакета std_logic_1164 Тип STD_LOGIC 9-значная логика ‘1’ – лог. 1 ‘0’ – лог.

- 34. Основы языка VHDL Моделирование цифровых систем

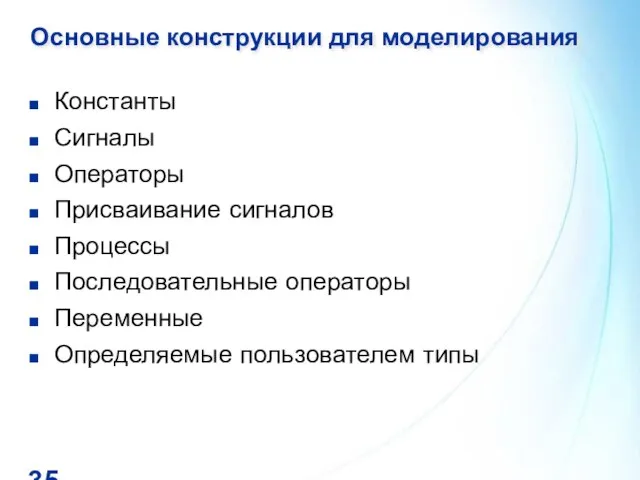

- 35. Основные конструкции для моделирования Константы Сигналы Операторы Присваивание сигналов Процессы Последовательные операторы Переменные Определяемые пользователем типы

- 36. Константы Присваивают имя константе Объявление константы CONSTANT : := ; Константа не может изменять свое значение

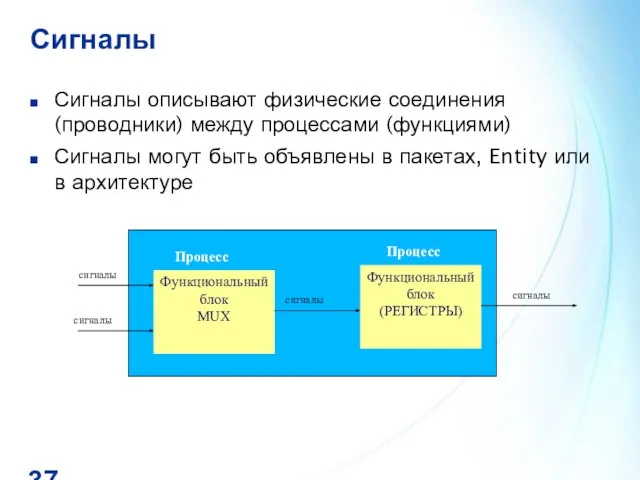

- 37. Сигналы Сигналы описывают физические соединения (проводники) между процессами (функциями) Сигналы могут быть объявлены в пакетах, Entity

- 38. Присваивание значение сигналам SIGNAL temp: std_logic_vector (7 DOWNTO 0) Присваивание всех битов: temp temp Один бит:

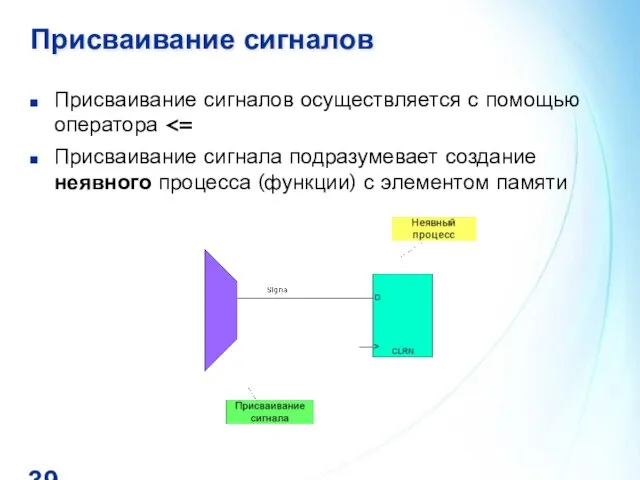

- 39. Присваивание сигналов Присваивание сигналов осуществляется с помощью оператора Присваивание сигнала подразумевает создание неявного процесса (функции) с

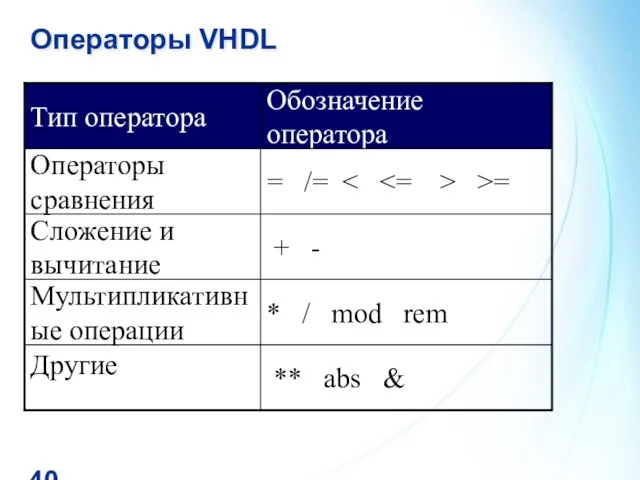

- 40. Операторы VHDL

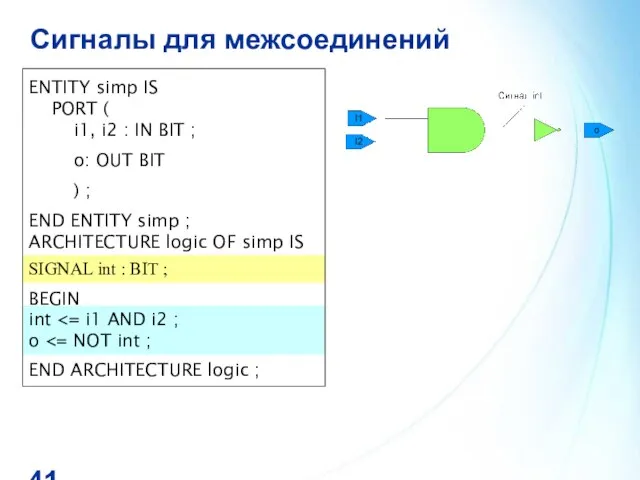

- 41. Сигналы для межсоединений ENTITY simp IS PORT ( i1, i2 : IN BIT ; o: OUT

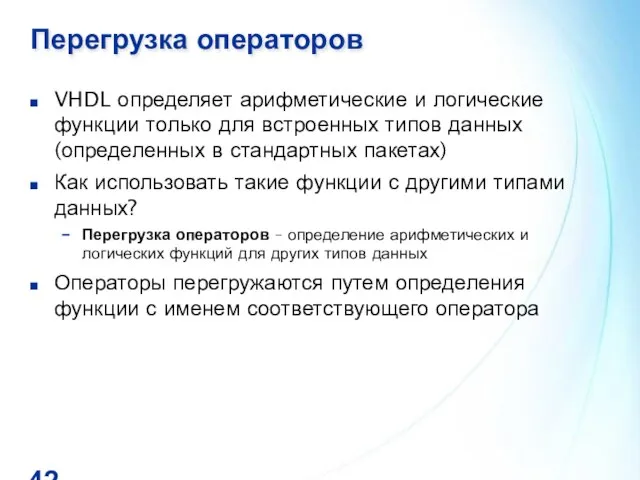

- 42. Перегрузка операторов VHDL определяет арифметические и логические функции только для встроенных типов данных (определенных в стандартных

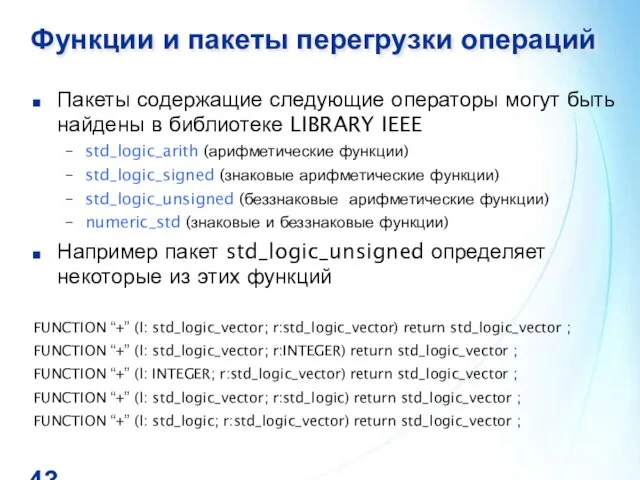

- 43. Функции и пакеты перегрузки операций Пакеты содержащие следующие операторы могут быть найдены в библиотеке LIBRARY IEEE

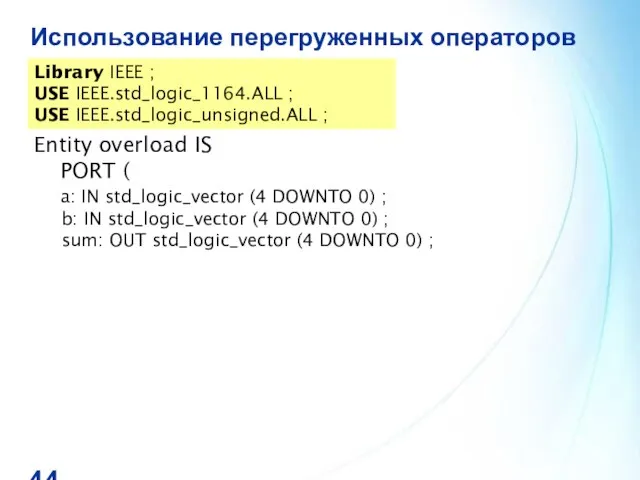

- 44. Использование перегруженных операторов Library IEEE ; USE IEEE.std_logic_1164.ALL ; USE IEEE.std_logic_unsigned.ALL ; Entity overload IS PORT

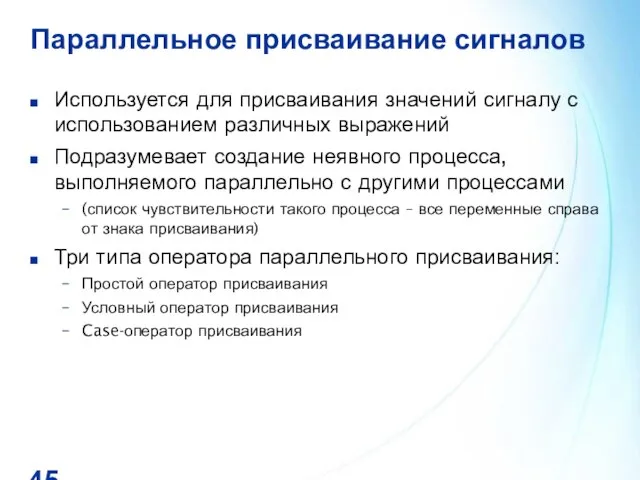

- 45. Параллельное присваивание сигналов Используется для присваивания значений сигналу с использованием различных выражений Подразумевает создание неявного процесса,

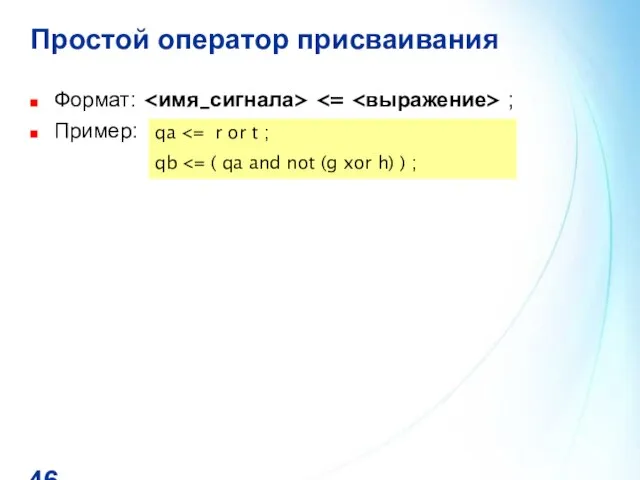

- 46. Простой оператор присваивания Формат: ; Пример: qa qb

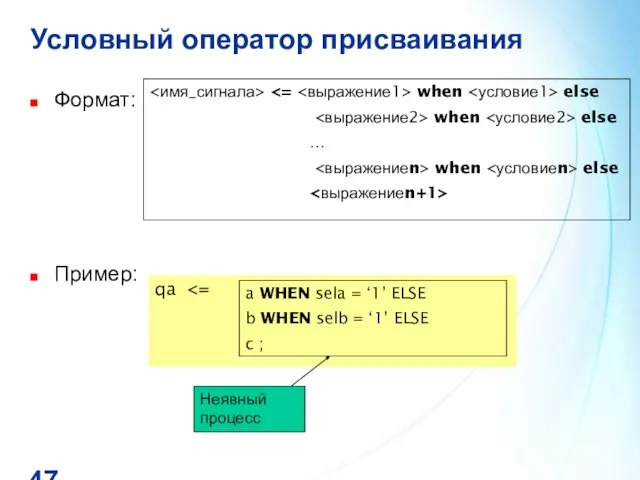

- 47. Условный оператор присваивания Формат: Пример: qa when else when else … when else a WHEN sela

- 48. Оператор присваивания WITH Формат: Пример: WITH sel SELECT q b WHEN “01”, c WHEN “10”, d

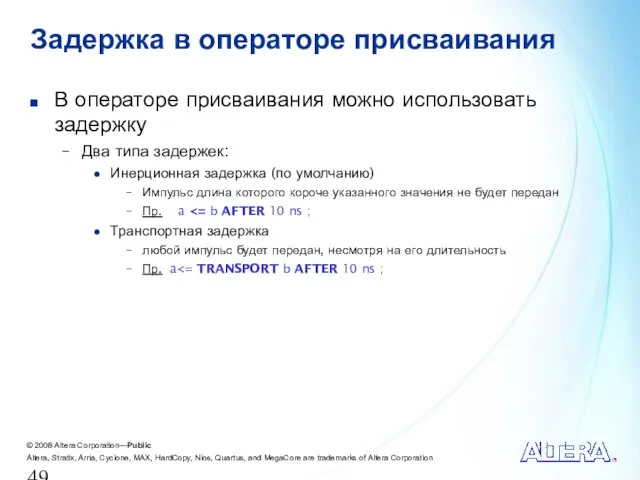

- 49. Задержка в операторе присваивания В операторе присваивания можно использовать задержку Два типа задержек: Инерционная задержка (по

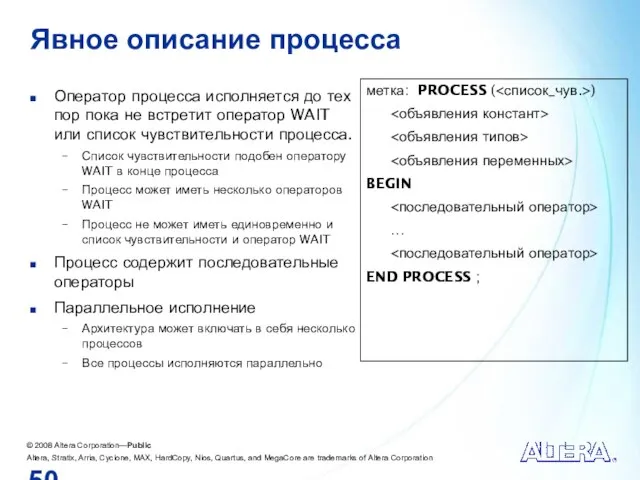

- 50. Явное описание процесса Оператор процесса исполняется до тех пор пока не встретит оператор WAIT или список

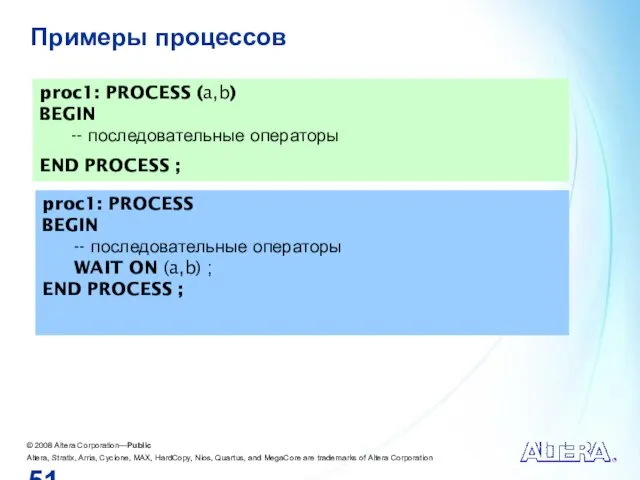

- 51. Примеры процессов proc1: PROCESS (a,b) BEGIN -- последовательные операторы END PROCESS ; proc1: PROCESS BEGIN --

- 52. Последовательные операторы Последовательные операторы Простое присваивание сигнала Оператор IF-THEN Оператор CASE Оператор цикла Оператор WAIT

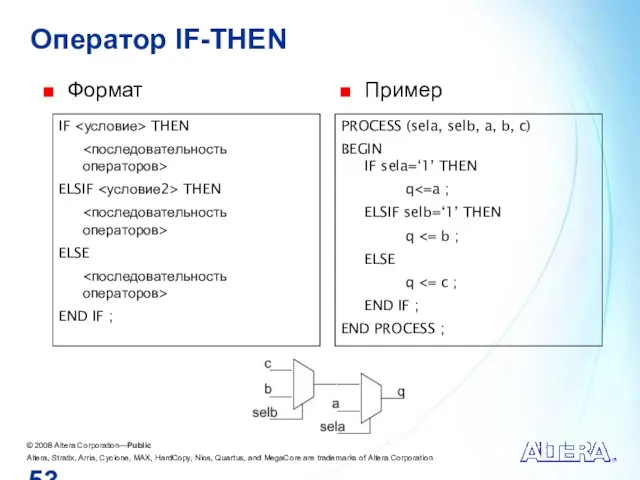

- 53. Оператор IF-THEN Формат IF THEN ELSIF THEN ELSE END IF ; PROCESS (sela, selb, a, b,

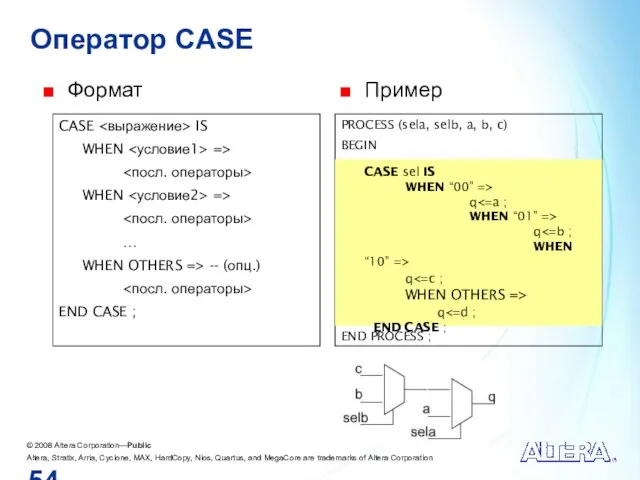

- 54. Оператор CASE Формат CASE IS WHEN => WHEN => … WHEN OTHERS => -- (опц.) END

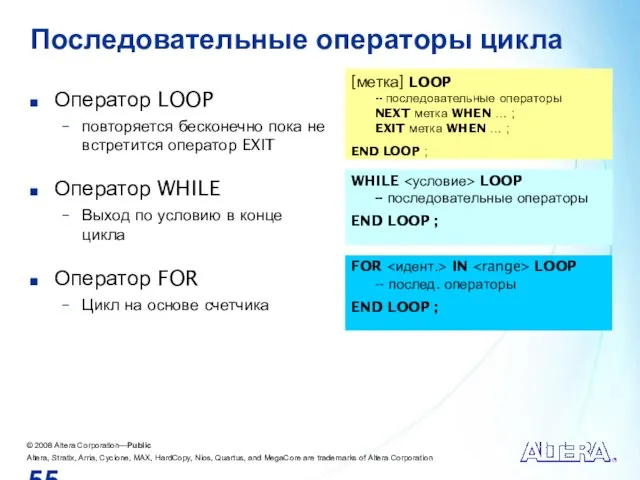

- 55. Последовательные операторы цикла Оператор LOOP повторяется бесконечно пока не встретится оператор EXIT Оператор WHILE Выход по

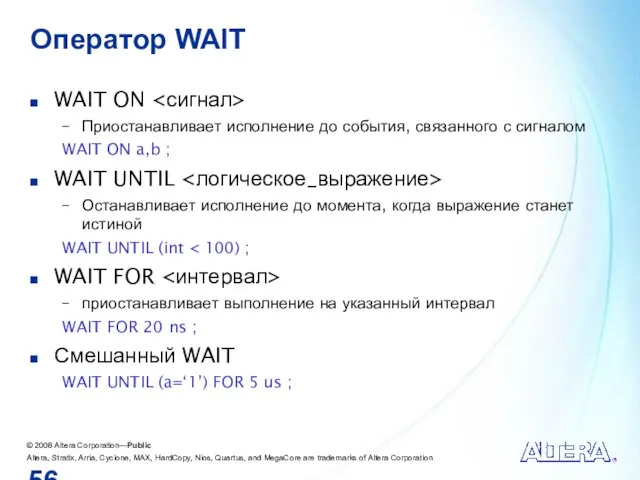

- 56. Оператор WAIT WAIT ON Приостанавливает исполнение до события, связанного с сигналом WAIT ON a,b ; WAIT

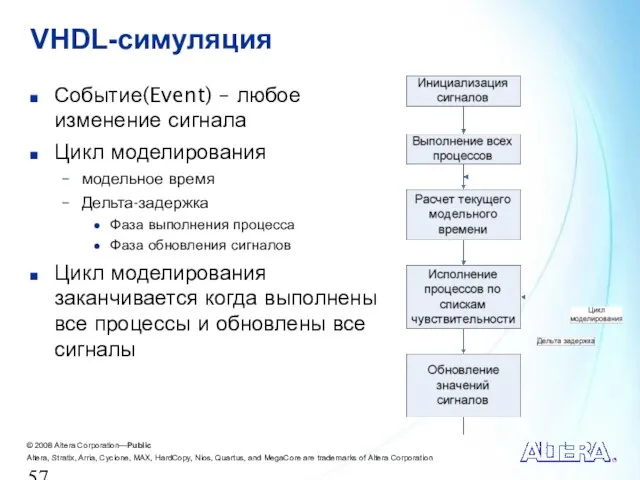

- 57. Событие(Event) – любое изменение сигнала Цикл моделирования модельное время Дельта-задержка Фаза выполнения процесса Фаза обновления сигналов

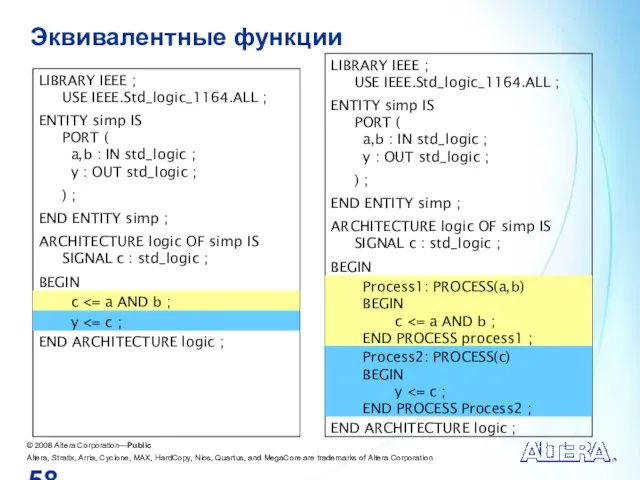

- 58. Эквивалентные функции LIBRARY IEEE ; USE IEEE.Std_logic_1164.ALL ; ENTITY simp IS PORT ( a,b : IN

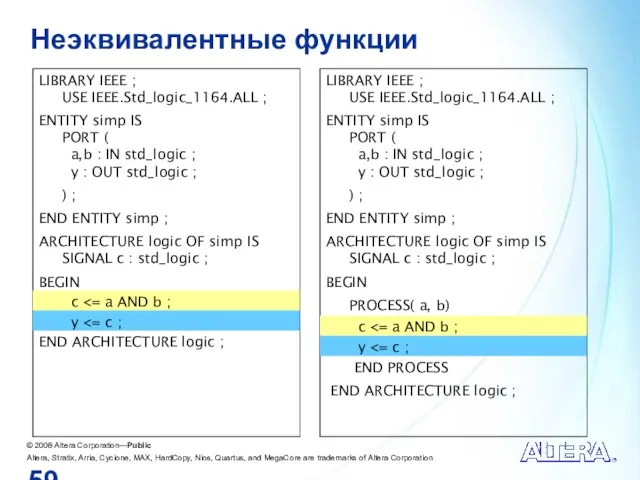

- 59. Неэквивалентные функции LIBRARY IEEE ; USE IEEE.Std_logic_1164.ALL ; ENTITY simp IS PORT ( a,b : IN

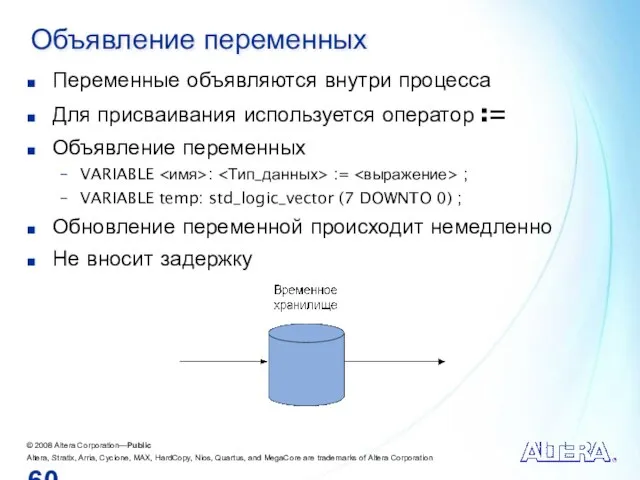

- 60. Объявление переменных Переменные объявляются внутри процесса Для присваивания используется оператор := Объявление переменных VARIABLE : :=

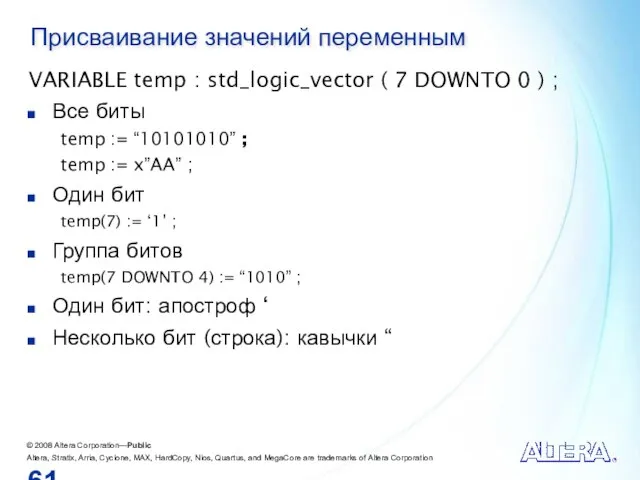

- 61. Присваивание значений переменным VARIABLE temp : std_logic_vector ( 7 DOWNTO 0 ) ; Все биты temp

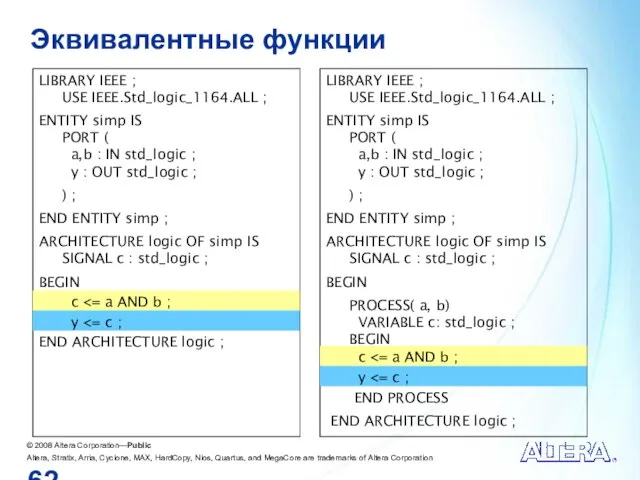

- 62. Эквивалентные функции LIBRARY IEEE ; USE IEEE.Std_logic_1164.ALL ; ENTITY simp IS PORT ( a,b : IN

- 63. Сигналы против переменных

- 64. Определяемые пользователем типы Массивы Arrays Перечислимые типы данных

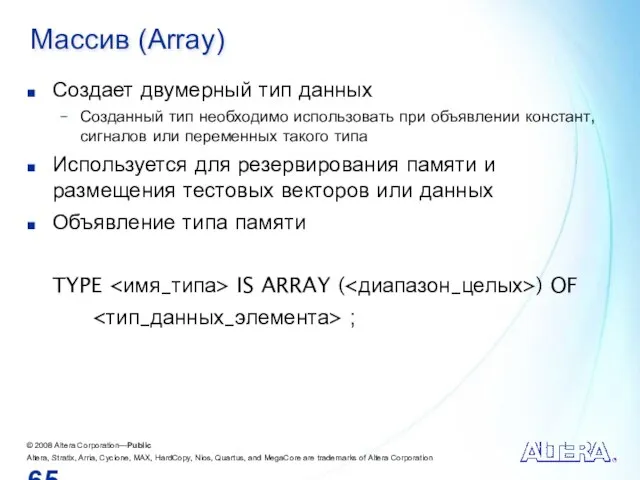

- 65. Массив (Array) Создает двумерный тип данных Созданный тип необходимо использовать при объявлении констант, сигналов или переменных

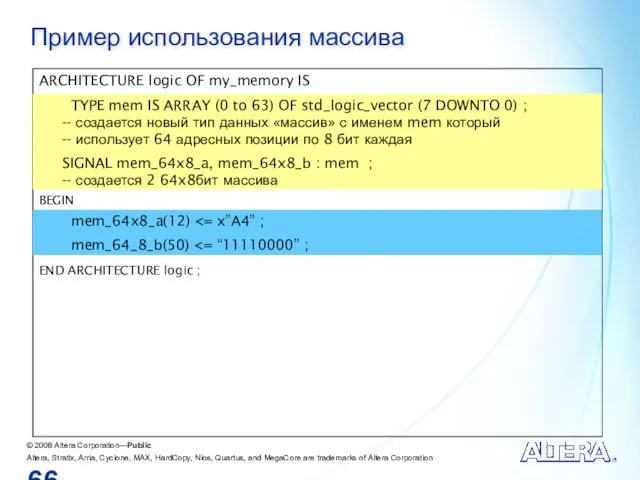

- 66. Пример использования массива ARCHITECTURE logic OF my_memory IS TYPE mem IS ARRAY (0 to 63) OF

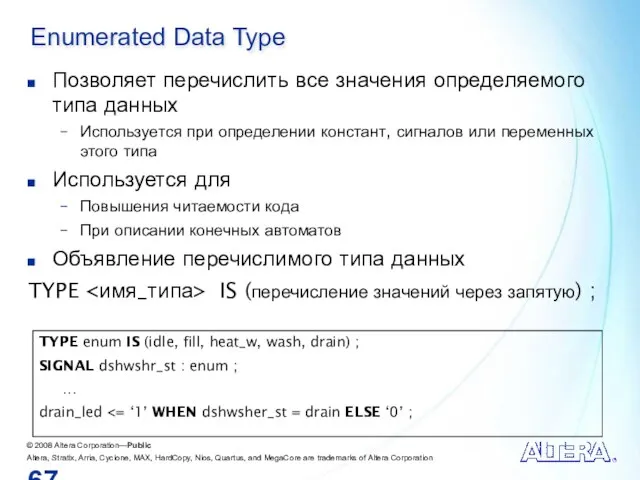

- 67. Enumerated Data Type Позволяет перечислить все значения определяемого типа данных Используется при определении констант, сигналов или

- 68. Основы языка VHDL Синтез цифровых систем

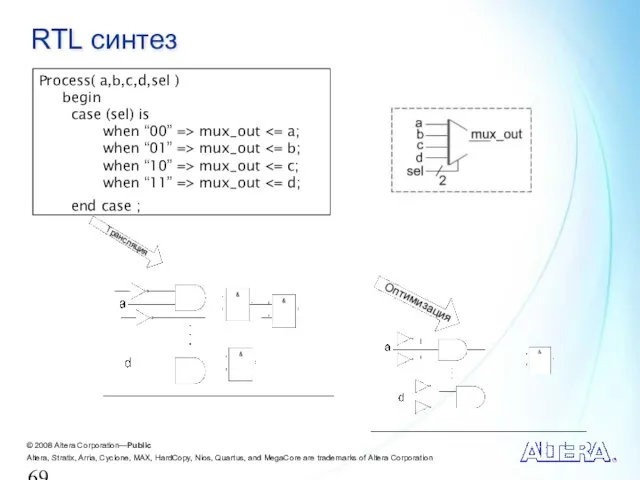

- 69. RTL синтез Process( a,b,c,d,sel ) begin case (sel) is when “00” => mux_out mux_out mux_out mux_out

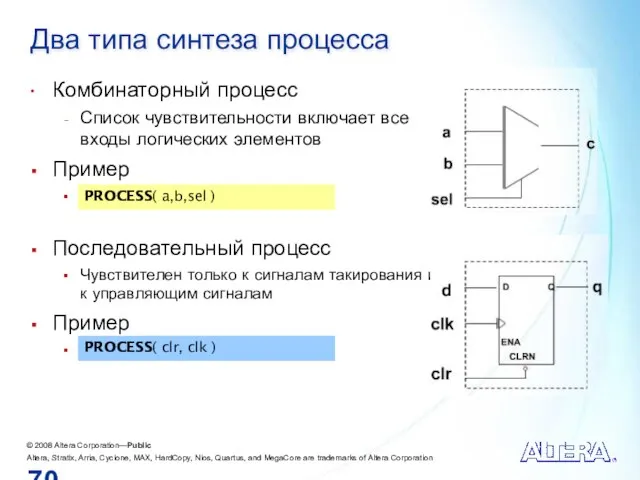

- 70. Два типа синтеза процесса Комбинаторный процесс Список чувствительности включает все входы логических элементов Пример Последовательный процесс

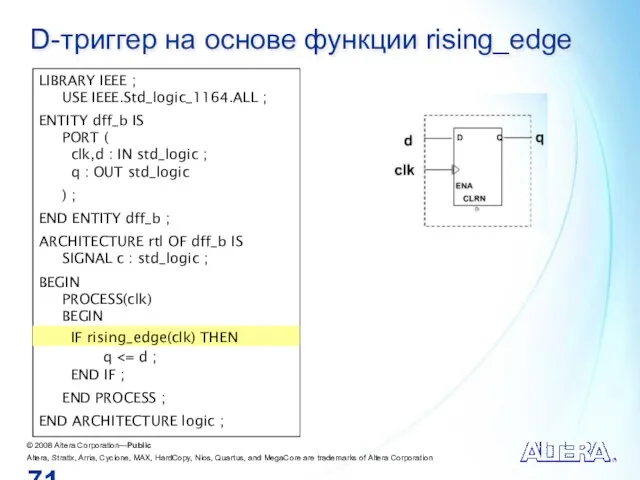

- 71. D-триггер на основе функции rising_edge LIBRARY IEEE ; USE IEEE.Std_logic_1164.ALL ; ENTITY dff_b IS PORT (

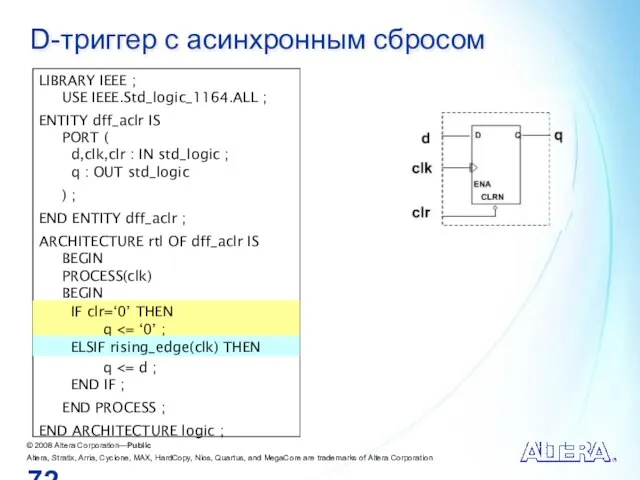

- 72. D-триггер с асинхронным сбросом LIBRARY IEEE ; USE IEEE.Std_logic_1164.ALL ; ENTITY dff_aclr IS PORT ( d,clk,clr

- 73. D-триггер с синхронным сбросом LIBRARY IEEE ; USE IEEE.Std_logic_1164.ALL ; ENTITY dff_aclr IS PORT ( d,clk,clr

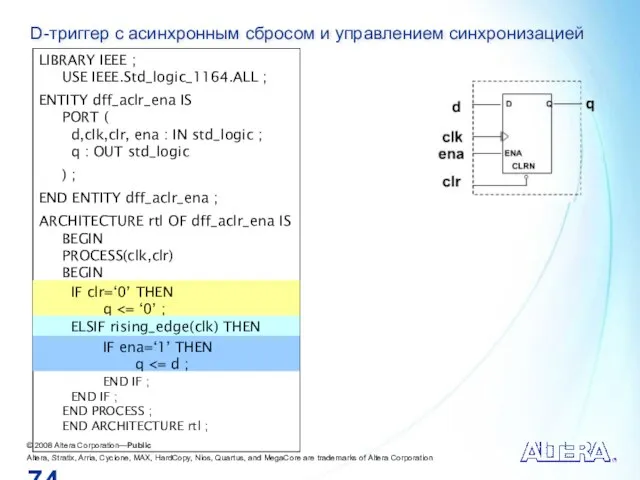

- 74. D-триггер с асинхронным сбросом и управлением синхронизацией LIBRARY IEEE ; USE IEEE.Std_logic_1164.ALL ; ENTITY dff_aclr_ena IS

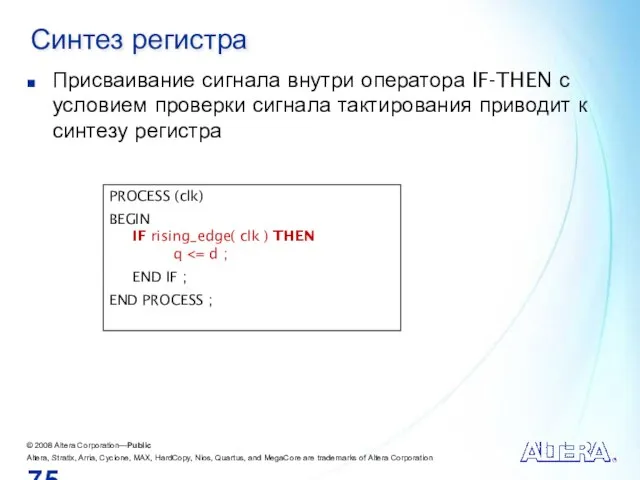

- 75. Синтез регистра Присваивание сигнала внутри оператора IF-THEN с условием проверки сигнала тактирования приводит к синтезу регистра

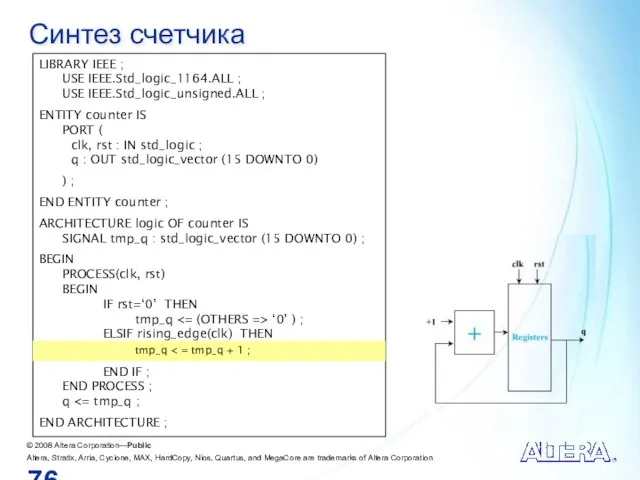

- 76. Синтез счетчика LIBRARY IEEE ; USE IEEE.Std_logic_1164.ALL ; USE IEEE.Std_logic_unsigned.ALL ; ENTITY counter IS PORT (

- 77. Основы языка VHDL Структурное описание

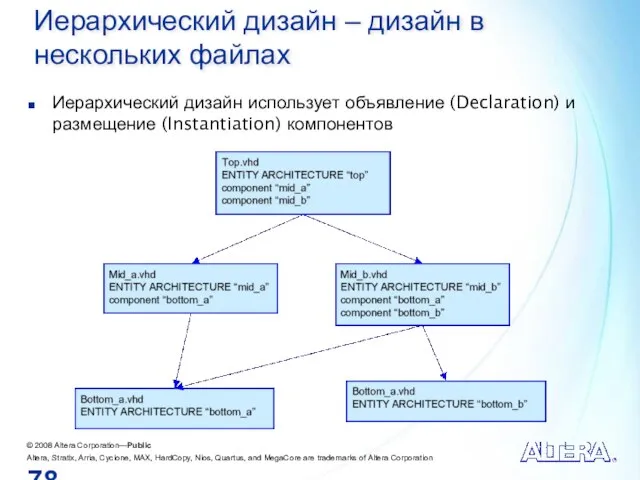

- 78. Иерархический дизайн – дизайн в нескольких файлах Иерархический дизайн использует объявление (Declaration) и размещение (Instantiation) компонентов

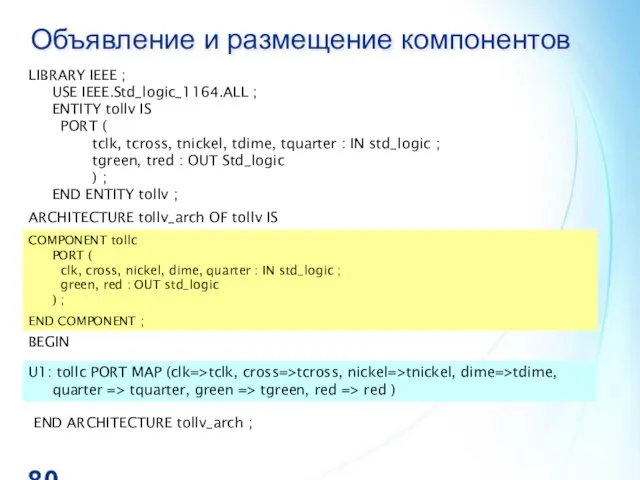

- 79. Объявление и размещение компонентов Объявление компонента используется для указания типов данных и портов другого ENTITY COMPONENT

- 80. Объявление и размещение компонентов LIBRARY IEEE ; USE IEEE.Std_logic_1164.ALL ; ENTITY tollv IS PORT ( tclk,

- 81. Основы языка VHDL Дополнительные операторы языка VHDL

- 82. Оператор GENERATE : FOR IN GENERATE : [ PORT MAP ] END GENERATE ; COMPONENT register_4

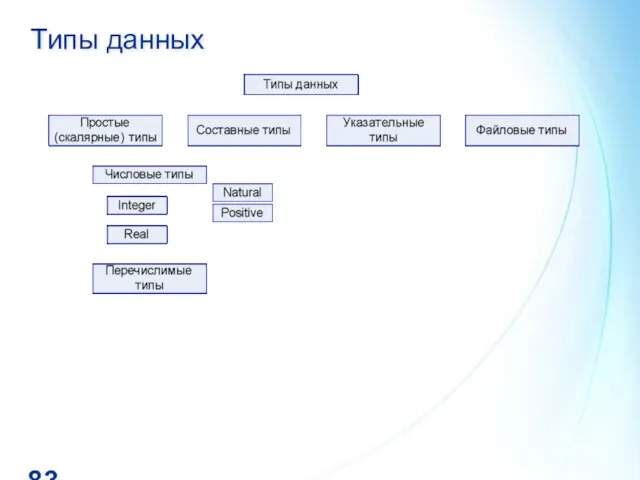

- 83. Типы данных

- 85. Скачать презентацию

![Оператор GENERATE : FOR IN GENERATE : [ PORT MAP ] END](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/420495/slide-81.jpg)

ЧС в быту

ЧС в быту Пустыни

Пустыни Проект группы “Б”

Проект группы “Б” Древние люди Забайкалья

Древние люди Забайкалья 1816 г. Рене-Теофиль Лаэннек изобрёл стетоскоп

1816 г. Рене-Теофиль Лаэннек изобрёл стетоскоп Образовательная программа по вопросам ценообразования и государственного регулирования отраслей экономики РФ

Образовательная программа по вопросам ценообразования и государственного регулирования отраслей экономики РФ СОДЕРЖАНИЕ: Краткая информация………………………………………33 Партнеры………………..……………………………………44 Стадии процесса…..………………

СОДЕРЖАНИЕ: Краткая информация………………………………………33 Партнеры………………..……………………………………44 Стадии процесса…..……………… Инфекции — Туляремия

Инфекции — Туляремия Презентация на тему Автомеханик

Презентация на тему Автомеханик Организация проектной деятельности на уроках

Организация проектной деятельности на уроках Однокомнатная квартира. Тип 1

Однокомнатная квартира. Тип 1 «Учителя – в годы Великой Отечественной войны» Экспозиция школьного музеявыполнена зам. директора по ВР Мельниченко В.В.С.Нарв

«Учителя – в годы Великой Отечественной войны» Экспозиция школьного музеявыполнена зам. директора по ВР Мельниченко В.В.С.Нарв Растительный мир тундры

Растительный мир тундры Строительный подряд

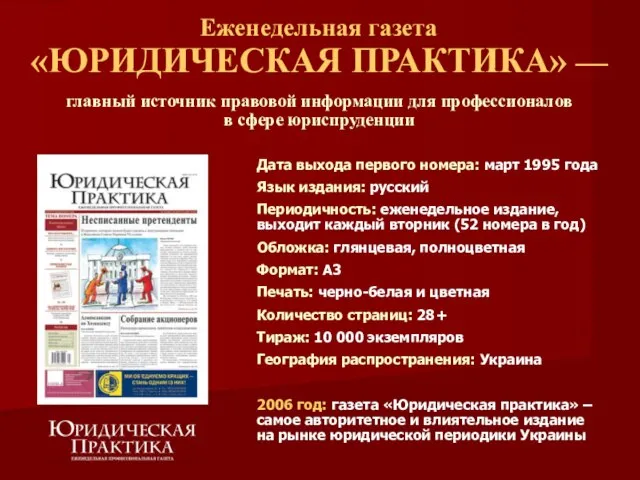

Строительный подряд Еженедельная газета «ЮРИДИЧЕСКАЯ ПРАКТИКА» —главный источник правовой информации для профессионалов в сфере юриспруденции

Еженедельная газета «ЮРИДИЧЕСКАЯ ПРАКТИКА» —главный источник правовой информации для профессионалов в сфере юриспруденции Презентация на тему Аркадий Кирсанов в произведение Ивана сергеевича тургенева «отцы и дети»

Презентация на тему Аркадий Кирсанов в произведение Ивана сергеевича тургенева «отцы и дети» Загрязнение окружающей среды.Проблема мусора

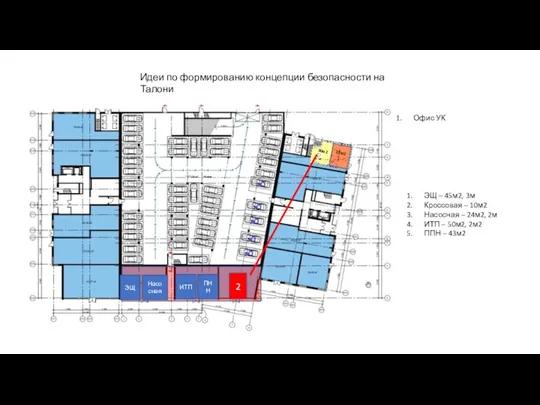

Загрязнение окружающей среды.Проблема мусора Идеи по формированию концепции безопасности на Талони

Идеи по формированию концепции безопасности на Талони Вводный урок по русскому языку

Вводный урок по русскому языку Апаратты кодтау жне сатау. СРС

Апаратты кодтау жне сатау. СРС Творческий проект "Мой друг Кеша"

Творческий проект "Мой друг Кеша" The Blending of Genres

The Blending of Genres  Программируем в Windows Forms

Программируем в Windows Forms  Биосинтез белков

Биосинтез белков Конструирование балки

Конструирование балки Министерство сельского хозяйства Ульяновской области МЯСНЫЕ ПОРОДЫКРУПНОГО РОГАТОГО СКОТА

Министерство сельского хозяйства Ульяновской области МЯСНЫЕ ПОРОДЫКРУПНОГО РОГАТОГО СКОТА Презентация на тему Нравственный поступок

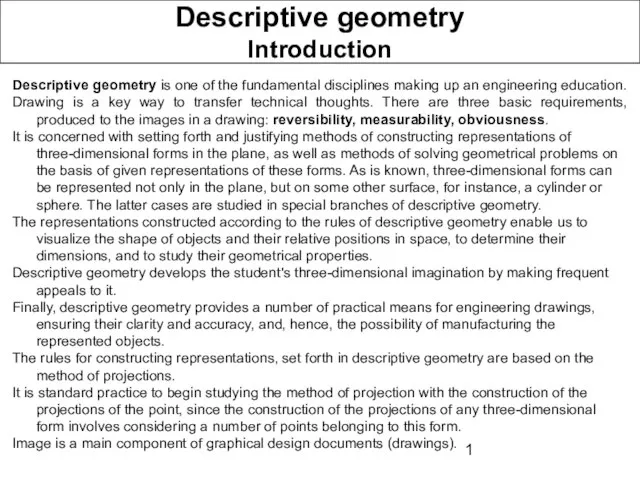

Презентация на тему Нравственный поступок  1 Descriptive geometry Introduction

1 Descriptive geometry Introduction