Содержание

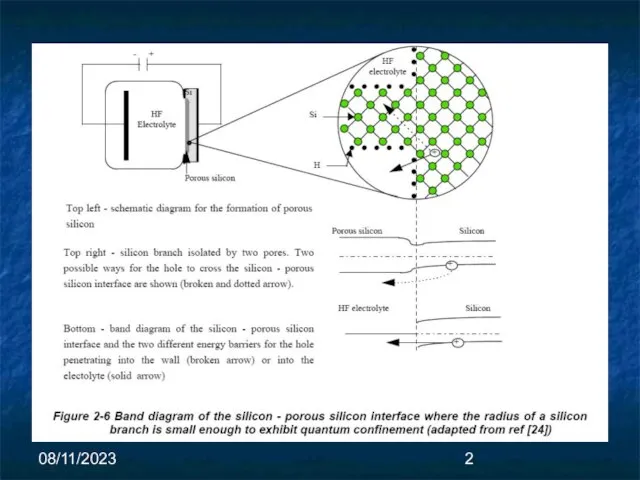

- 2. 08/11/2023

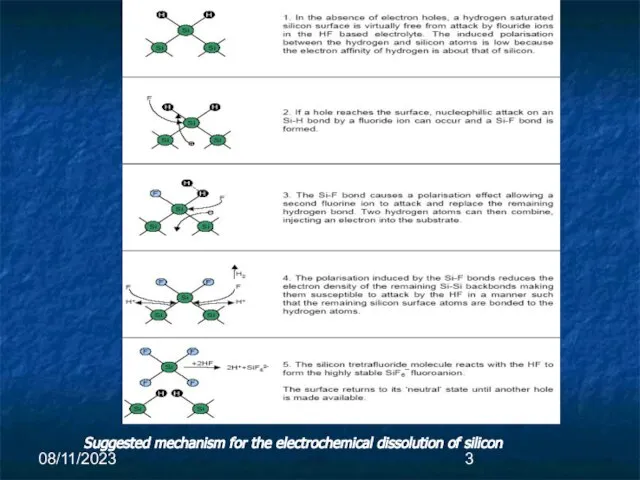

- 3. 08/11/2023 Suggested mechanism for the electrochemical dissolution of silicon

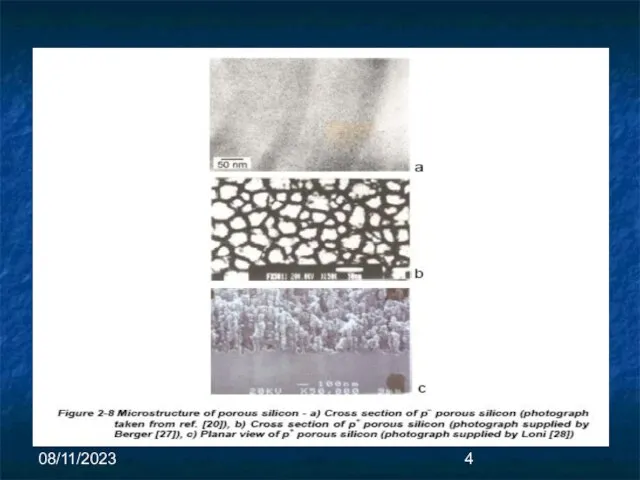

- 4. 08/11/2023

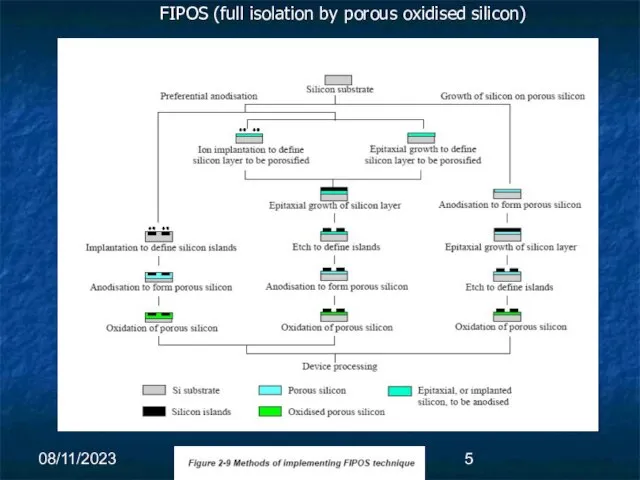

- 5. 08/11/2023 FIPOS (full isolation by porous oxidised silicon)

- 6. 08/11/2023

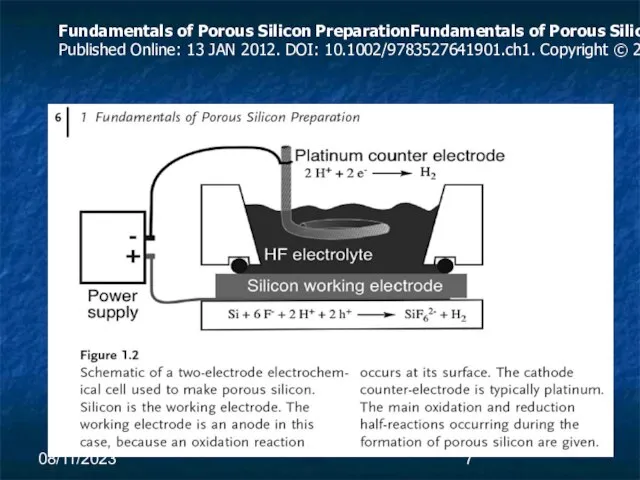

- 7. 08/11/2023 Fundamentals of Porous Silicon PreparationFundamentals of Porous Silicon Preparation. Prof. Dr. Michael J. Sailor. Published

- 8. 08/11/2023 The techniques employed for dielectric isolation using porous silicon can also be used for micromachining

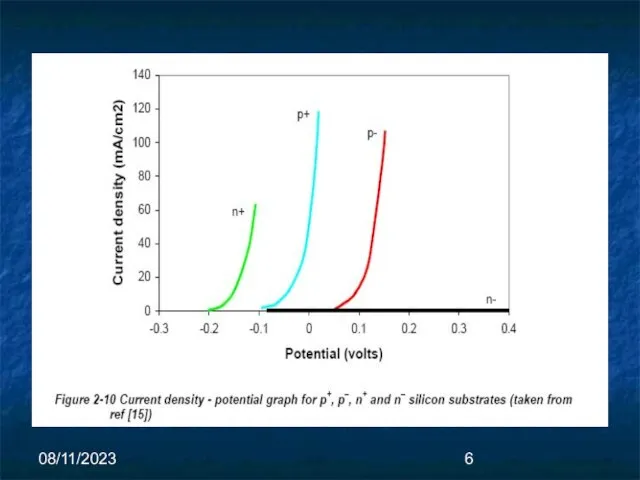

- 9. 08/11/2023 For high current densities, the density of holes is high and the etched surface is

- 10. 08/11/2023 The large surface-to-volume ratios make porous Si attractive for gaseous and liquid applications, including filter

- 11. 08/11/2023 A third application uses porous Si as a sacrificial layer for polysilicon and single crystalline

- 12. 08/11/2023 Silicon Dioxide Silicon dioxide (SiO2) is one of the most widely used materials in the

- 13. 08/11/2023 The most common processes used to produce SiO2 films for polysilicon surface micromachining are thermal

- 14. 08/11/2023 SiO2 films can be deposited on a wide variety of substrate materials by LPCVD. LPCVD

- 15. 08/11/2023 Phosphosilicate glass (PSG) can be formed using nearly the same deposition process as LTO by

- 16. 08/11/2023 PSG and LTO films are deposited in hot-wall, low pressure, fused silica furnaces in systems

- 17. 08/11/2023 The low deposition temperatures result in LTO and PSG films that are slightly less dense

- 18. 08/11/2023 Thermal SiO2 and LTO are electrical insulators used in numerous MEMS applications. The dielectric constants

- 19. 08/11/2023 For LTO the as-deposited residual stress is tensile, with a magnitude of about 100 MPa

- 20. 08/11/2023 Plasma-enhanced chemical vapor deposition (PECVD) is another common method to produce oxides of silicon. Using

- 21. 08/11/2023 Quartz is the crystalline form of SiO2 and has interesting properties for MEMS. Quartz is

- 22. 08/11/2023 Another SiO2-related material that has recently found uses in MEMS is spin-on-glass (SOG). SOG is

- 23. 08/11/2023 The thick SOG films were patterned into molds and filled with 10 micron-thick LPCVD polysilicon

- 24. 08/11/2023 In the second example, Liu et al. fabricated high-aspect ratio channel plate microstructures from SOG.

- 25. 08/11/2023 Thick (5–100 µm) spin-on glass (SOG) has the ability to uniformly coat surfaces and smooth

- 26. 08/11/2023 Spin-on glass is commercially available in different forms, commonly siloxane- or silicate-based. The latter type

- 27. 08/11/2023 Spin on glass (SOG) is a mixture of SiO2 and dopants (either boron or phosphorous)

- 28. 08/11/2023 A siloxane A siloxane is any chemical compound composed of units of the form R2SiSiOSiO,

- 29. 08/11/2023 An examples are: [SiO(CH3)2]n (polydimethylsiloxane) and [SiO(C6H5)2]n (polydiphenylsiloxane).

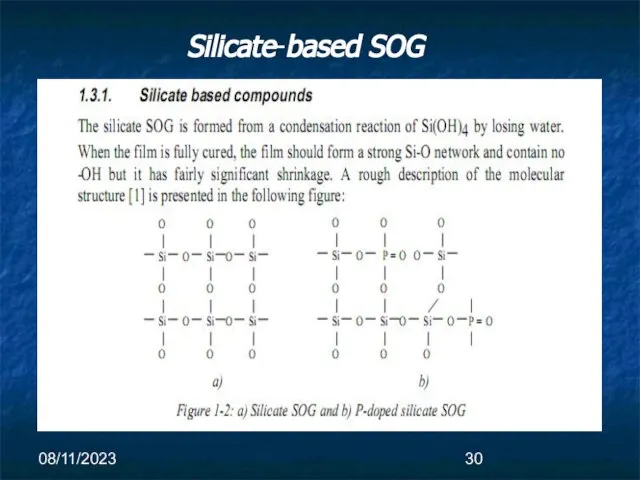

- 30. 08/11/2023 Silicate-based SOG

- 31. 08/11/2023 Silicon Nitride Silicon nitride (Si3N4) is widely used in MEMS for electrical isolation, surface passivation,

- 32. 08/11/2023 PECVD silicon nitride is generally nonstoichiometric (sometimes denoted as SixNy : H) and may contain

- 33. 08/11/2023 Unlike its PECVD counterpart, LPCVD Si3N4 is extremely resistant to chemical attack, making it the

- 34. 08/11/2023 Typical deposition temperatures and pressures range between 700 ◦C to 900 ◦C and 200 mtorr

- 35. 08/11/2023 The residual stress in stoichiometric Si3N4 is large and tensile, with a magnitude of about

- 36. 08/11/2023 Стехиометрия (от др.-греч. (от др.-греч. στοιχεῖον «элемент» + μετρέω «измерять») — раздел химии (от др.-греч.

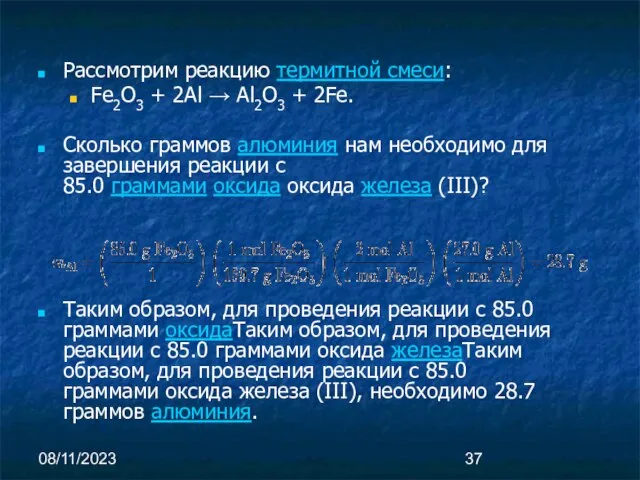

- 37. 08/11/2023 Рассмотрим реакцию термитной смеси: Fe2O3 + 2Al → Al2O3 + 2Fe. Сколько граммов алюминия нам

- 38. 08/11/2023 To enable the use of Si3N4 films for applications that require micron thick, durable (прочные),

- 39. 08/11/2023 Nearly stress-free films can be deposited using a NH3 to SiH2Cl2 ratio of 1 :

- 40. 08/11/2023 Germanium-Based Materials Like Si, Ge has a long history as a semiconductor device material, dating

- 41. 08/11/2023 Polycrystalline Ge Thin polycrystalline Ge (poly-Ge) films can be deposited by LPCVD at temperatures as

- 42. 08/11/2023 Poly-Ge is essentially impervious (невосприимчивый) to KOH, TMAH, and BOE, enabling the fabrication of Ge

- 43. 08/11/2023 Mixtures of HNO3, H2O, and HCl and H2O, H2O2, and HCl, as well as the

- 44. 08/11/2023 Werner KernWerner Kern developed the basic procedure in 1965 while working for RCA, the Radio

- 45. 08/11/2023 The wafers are prepared by soaking them in DI waterThe wafers are prepared by soaking

- 46. 08/11/2023 Using these techniques, devices such as poly-Ge-based thermistors and Si3N4 membrane-based pressure sensors, made using

- 47. 08/11/2023 Polycrystalline SiGe Like poly-Ge, polycrystalline SiGe (poly-SiGe) is a material that can be deposited at

- 48. 08/11/2023 In general, the deposition temperature is related to the concentration of Ge in the films,

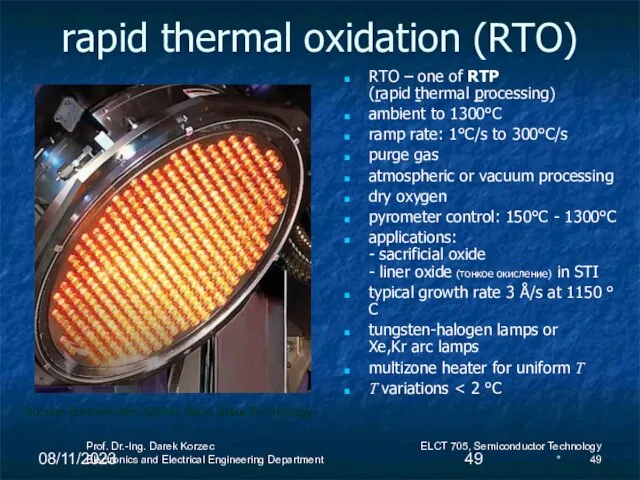

- 49. 08/11/2023 Prof. Dr.-Ing. Darek Korzec Electronics and Electrical Engineering Department ELCT 705, Semiconductor Technology * rapid

- 50. 08/11/2023 Like polysilicon, poly-SiGe can be doped with boron and phosphorus to modify its conductivity. In

- 51. 08/11/2023 Unlike poly-Ge, poly-SiGe can be deposited on a number of sacrificial substrates, including SiO2, PSG,

- 52. 08/11/2023 For instance, etching of poly-SiGe by H2O2 becomes significant for Ge concentrations over 70%. Sedky

- 53. 08/11/2023 The poly-SiGe, poly-Ge material system is particularly attractive for surface micromachining since H2O2 can be

- 54. 08/11/2023 Due to the conformal nature of LPCVD processing, poly-SiGe structural elements, such as gimbal-based microactuator

- 55. 08/11/2023 In this process, CMOS structures are first fabricated on Si wafers. Poly-SiGe mechanical structures are

- 56. 08/11/2023 Use of H2O2 as the sacrificial etchant means that no special protective layers are required

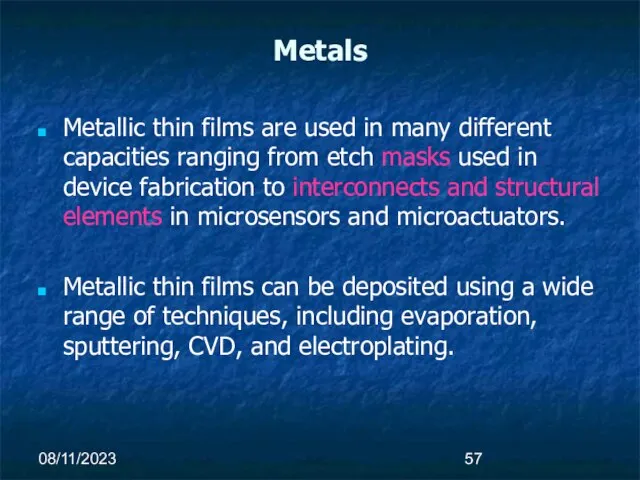

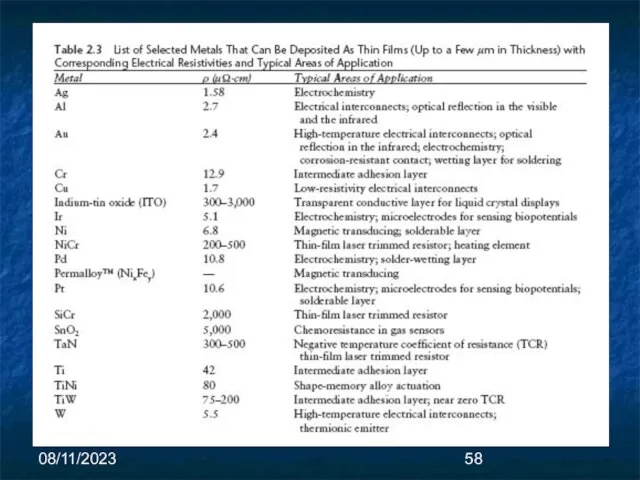

- 57. 08/11/2023 Metals Metallic thin films are used in many different capacities ranging from etch masks used

- 58. 08/11/2023

- 59. 08/11/2023 Polysilicon Silicides Aluminum alloy Titanium Titanium Nitride Tungsten Copper Tantalum Conducting Thin Films

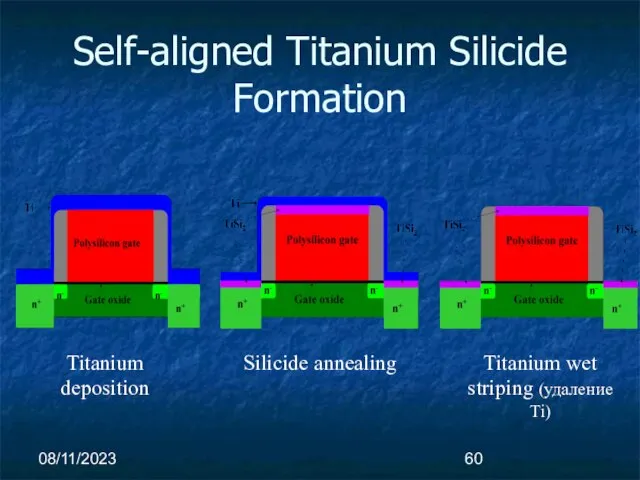

- 60. 08/11/2023 Self-aligned Titanium Silicide Formation

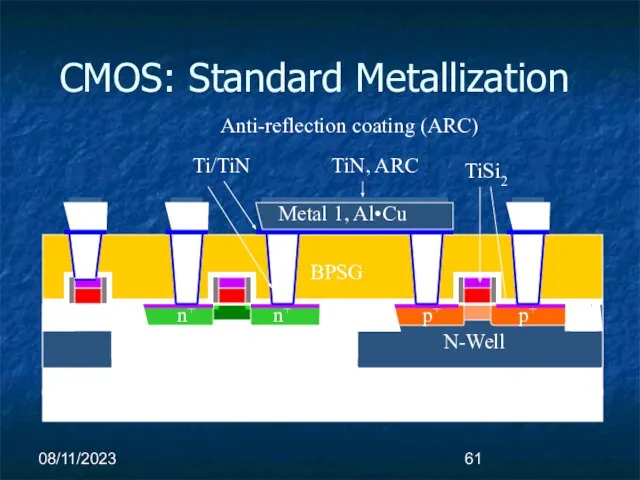

- 61. 08/11/2023 CMOS: Standard Metallization P-wafer N-Well P-Well STI n+ n+ USG p+ p+ Metal 1, Al•Cu

- 62. 08/11/2023 Fluorosilicate glass (FSG) is a low-k dielectric (FSG) is a low-k dielectric used in between

- 63. 08/11/2023 Shallow trench isolation (STI), also known as Box Isolation Technique, is an integrated circuit, is

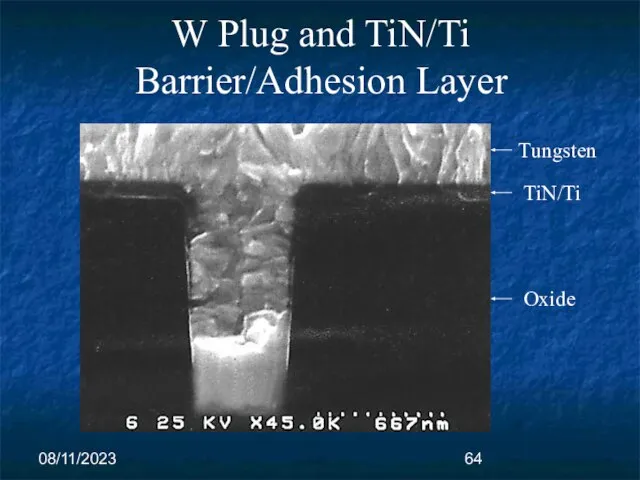

- 64. 08/11/2023 W Plug and TiN/Ti Barrier/Adhesion Layer

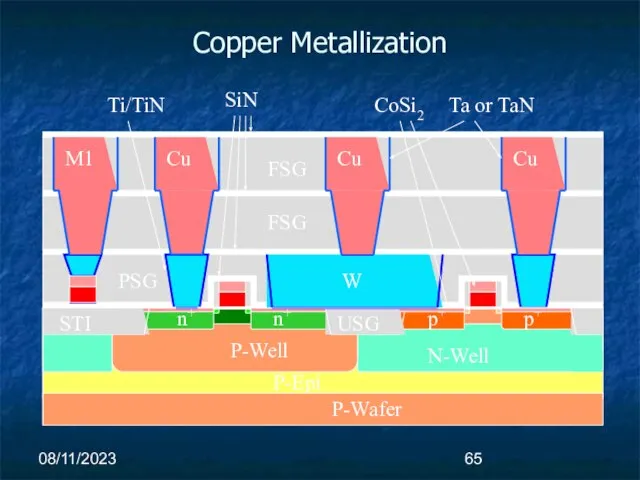

- 65. 08/11/2023 Copper Metallization

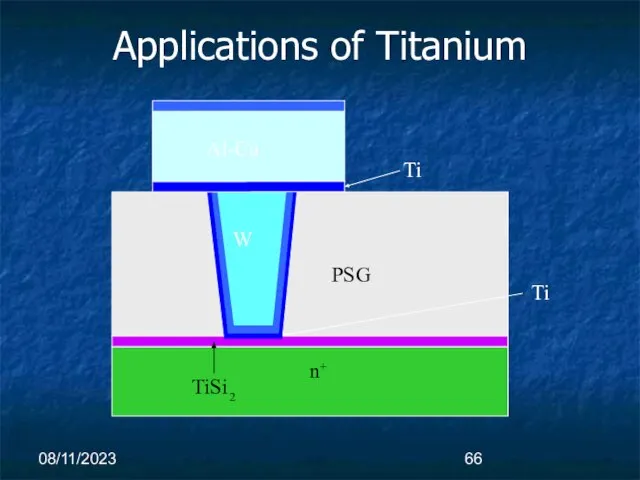

- 66. 08/11/2023 Applications of Titanium Ti PSG TiSi 2 n + Ti W Al-Cu

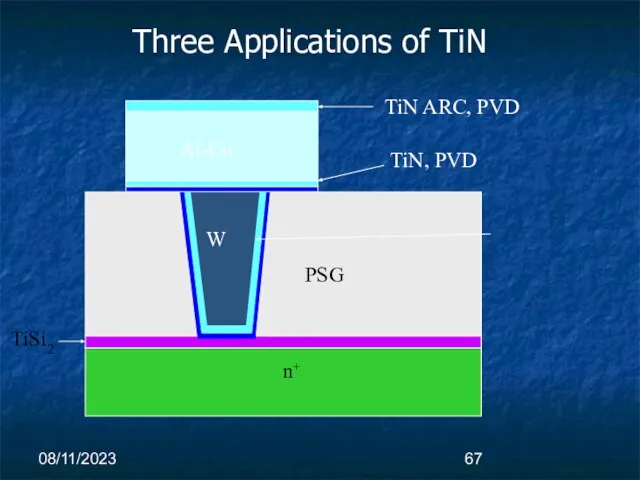

- 67. 08/11/2023 PSG TiSi2 n + TiN, PVD W Al-Cu TiN ARC, PVD Three Applications of TiN

- 68. 08/11/2023 Aluminum (Al) and gold (Au) are among the most widely employed metals in microfabricated electronic

- 69. 08/11/2023 One such example is the use of Au micromechanical switches for RF MEMS. For conventional

- 70. 08/11/2023 http://airccse.com/eeij/papers/1114eeij03.pdf Electrical Engineering: An International Journal (EEIJ), Vol. 1, No. 1, June 2014 A NOVEL

- 71. 08/11/2023 Unfortunately, these devices suffer (страдают) from insertion losses and poor electrical solation. In an effort

- 72. 08/11/2023 The trilayer cantilever structure was chosen to minimize the deleterious effects of thermal and process-related

- 73. 08/11/2023 The processing steps proved to be completely compatible with GaAs substrates. The released cantilevers demonstrated

- 74. 08/11/2023 In a second example from RF MEMS, Chang et al. reported the fabrication of an

- 75. 08/11/2023 Each switch is comprised of a series of linked bimorph cantilevers designed in such a

- 76. 08/11/2023 The released switches were relatively slow, at 10ms, but an actuation voltage of only 26V

- 77. 08/11/2023 The reversible phase change allows the shape-memory effect to be used as an actuation mechanism,

- 78. 08/11/2023 Titanium-nickel (TiNi) is among the most popular of the shape-memory alloys, owing to its high

- 79. 08/11/2023 In this study, TiNi films were deposited by co-sputtering elemental Ti and Ni targets, and

- 81. Скачать презентацию

![08/11/2023 An examples are: [SiO(CH3)2]n (polydimethylsiloxane) and [SiO(C6H5)2]n (polydiphenylsiloxane).](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/373792/slide-28.jpg)

«Технологии обработки числовой информации»

«Технологии обработки числовой информации» Психотехнологии корпоративной символики

Психотехнологии корпоративной символики Дни краеведения

Дни краеведения Проблемы компьютерной безопасности: тактика и контрмеры

Проблемы компьютерной безопасности: тактика и контрмеры Муниципальная программа "Одаренные дети"

Муниципальная программа "Одаренные дети" Неделя театра

Неделя театра Проектирование технологической оснастки для восстановления деталей кривошипно-шатунного механизма

Проектирование технологической оснастки для восстановления деталей кривошипно-шатунного механизма Презентация на тему Пищеварительная система у позвоночных животных

Презентация на тему Пищеварительная система у позвоночных животных  Характеристика фрустрации

Характеристика фрустрации Истоки кинематографа

Истоки кинематографа Афродита - богиня любви и красоты

Афродита - богиня любви и красоты ФЕДЕРАЛЬНЫЙ ЗАКОНN 293-ФЗ 8 ноября 2010 г.

ФЕДЕРАЛЬНЫЙ ЗАКОНN 293-ФЗ 8 ноября 2010 г. Презентация на тему Игровая зависимость

Презентация на тему Игровая зависимость  Решение задач на проценты. Юрий Алексеевич Гагарин 9 марта 1934 - 27 марта 1968

Решение задач на проценты. Юрий Алексеевич Гагарин 9 марта 1934 - 27 марта 1968 Jack London 1876 -1916

Jack London 1876 -1916 Международное сотрудничество МГТУ

Международное сотрудничество МГТУ Доклад

Доклад Ancient city

Ancient city Madrid: 4-days tour. SWOT

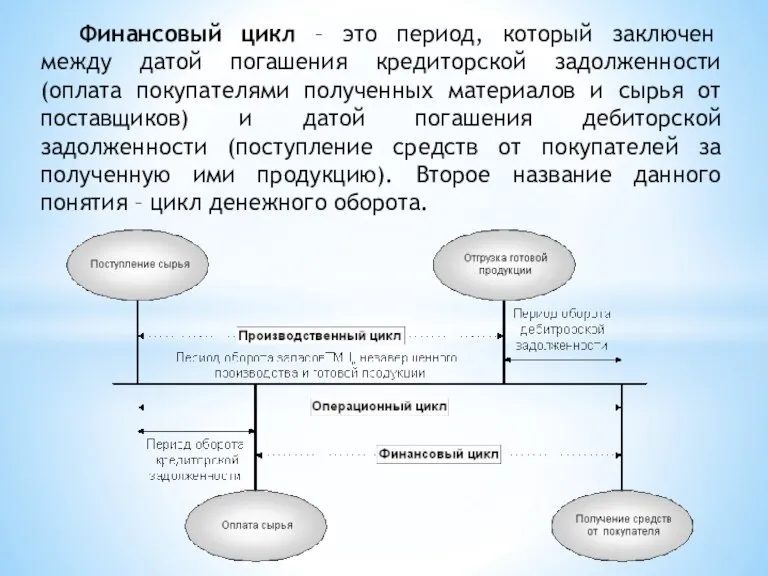

Madrid: 4-days tour. SWOT Цикл денежного оборота

Цикл денежного оборота Семейный праздник Новый Год

Семейный праздник Новый Год Эскизы

Эскизы Актуарная оценка перспектив развития ПФР

Актуарная оценка перспектив развития ПФР Мобильный интернет для бизнеса: альтернатива или достойная замена?

Мобильный интернет для бизнеса: альтернатива или достойная замена? Презентация на тему телевидение

Презентация на тему телевидение  Презентация по английскому Sights of London

Презентация по английскому Sights of London  Народные праздники Вятского края

Народные праздники Вятского края ALL COLORS family

ALL COLORS family