Содержание

- 2. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Системы на кристалле: типы SoC, структура, основные характеристики

- 3. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. SOPC делятся на однородные и блочные. В однородных

- 4. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Блочные SOPC делятся на 2 группы: 1. имеющие

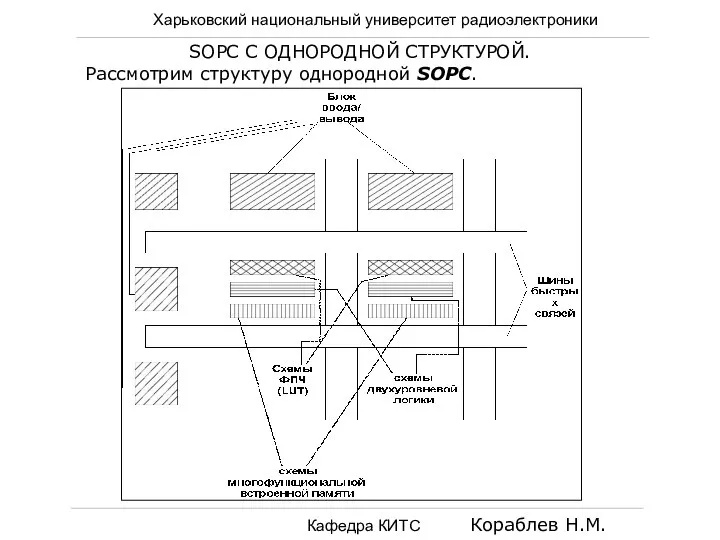

- 5. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. SOPC С ОДНОРОДНОЙ СТРУКТУРОЙ. Рассмотрим структуру однородной SOPC.

- 6. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Архитектура таких SOPC.называется multicore. В ней сочетаются ФБ

- 7. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. 10 логических элементов объединяются в логический блок, имеющий

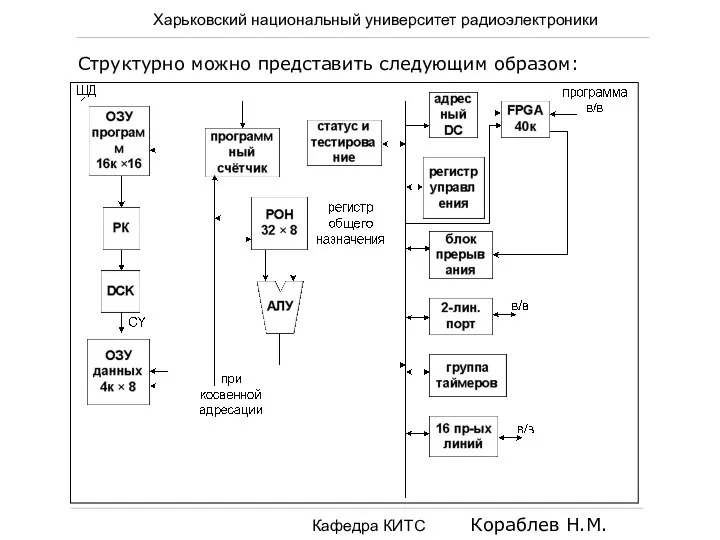

- 8. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. SOPC С БЛОЧНЫМИ СТРУКТУРАМИ. В составе блока SOPC

- 9. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Структурно можно представить следующим образом:

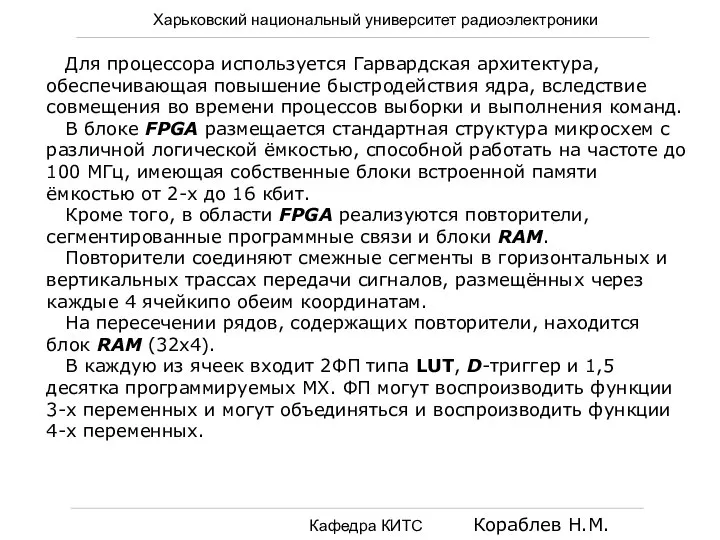

- 10. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Для процессора используется Гарвардская архитектура, обеспечивающая повышение быстродействия

- 11. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Логические ячейки имеют несколько стандартных конфигураций: 1) для

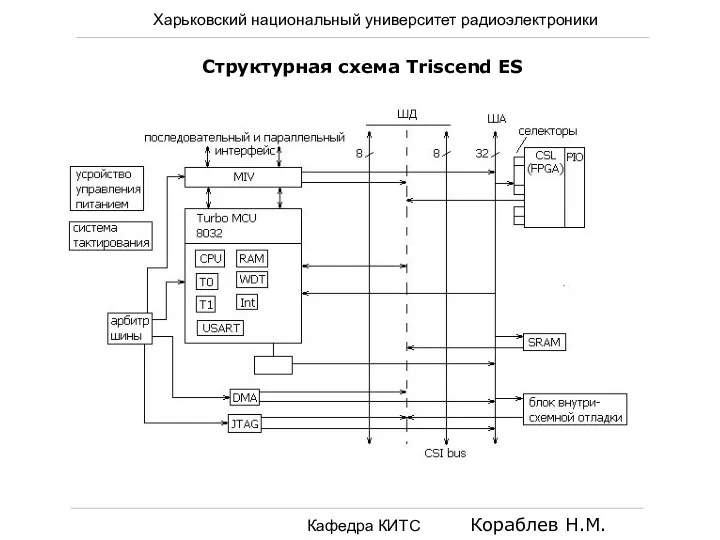

- 12. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Структурная схема Triscend ES

- 13. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Структурная схема Triscend ES MCU – микропроцессорное устройство.

- 14. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. 32-разрядные микроконтроллеры на основе ядра ARM7TDMI Основные характеристики:

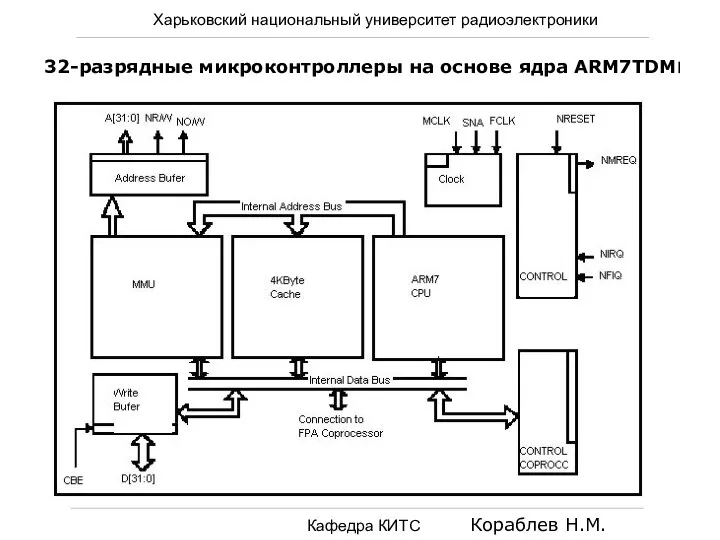

- 15. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. 32-разрядные микроконтроллеры на основе ядра ARM7TDMI

- 16. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. 32-разрядные микроконтроллеры на основе ядра ARM7TDMI 32-разрядная система

- 17. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. 32-разрядные микроконтроллеры на основе ядра ARM7TDMI Интерфейс с

- 19. Скачать презентацию

О РЕЗУЛЬТАТАХ ОЦЕНКИ ЭФФЕКТИВНОСТИ ДЕЯТЕЛЬНОСТИ И ОСНОВНЫХ НАПРАВЛЕНИЯХ РАБОТЫ ОРГАНОВ МЕСТНОГО САМОУПРАВЛЕНИЯ МУНИЦИПАЛЬНЫХ О

О РЕЗУЛЬТАТАХ ОЦЕНКИ ЭФФЕКТИВНОСТИ ДЕЯТЕЛЬНОСТИ И ОСНОВНЫХ НАПРАВЛЕНИЯХ РАБОТЫ ОРГАНОВ МЕСТНОГО САМОУПРАВЛЕНИЯ МУНИЦИПАЛЬНЫХ О Стресс. Разновидности стресса

Стресс. Разновидности стресса Фирма Акра. Производство и офис:

Фирма Акра. Производство и офис: Audio-Production.ru Профессиональная студия озвучки

Audio-Production.ru Профессиональная студия озвучки Памятник князю Владимиру в г. Белгороде

Памятник князю Владимиру в г. Белгороде Семена огородных культур

Семена огородных культур Этика бизнеса

Этика бизнеса В гостях у самовара

В гостях у самовара Приказ Министерства образования и науки РФ от 11.10.2011 № 2451 «Об утверждении порядка проведения ЕГЭ»

Приказ Министерства образования и науки РФ от 11.10.2011 № 2451 «Об утверждении порядка проведения ЕГЭ» Формирование доказательной базы технических регламентов и системы оценки соответствия в рамках Единого экономического простр

Формирование доказательной базы технических регламентов и системы оценки соответствия в рамках Единого экономического простр Виды технического обслуживания автомобилей

Виды технического обслуживания автомобилей Высокие технологии

Высокие технологии Иоганн Вольфганг Гете

Иоганн Вольфганг Гете Ф ГОУ СОШ № 155 МО РФ Августовские педагогические чтения Здоровьесбережение как базовая составляющая процесса гуманизации начал

Ф ГОУ СОШ № 155 МО РФ Августовские педагогические чтения Здоровьесбережение как базовая составляющая процесса гуманизации начал Развивающие упражнения на уроках географии 6 класс

Развивающие упражнения на уроках географии 6 класс Лекция ПТМ - 2

Лекция ПТМ - 2 Prezentatsia_2

Prezentatsia_2 Приказ Министерства образования и науки РФ № 209 от 24 марта 2010 г.

Приказ Министерства образования и науки РФ № 209 от 24 марта 2010 г. У Ч Е Т А Р Е Н Д Ы

У Ч Е Т А Р Е Н Д Ы Outdoor cafe - test

Outdoor cafe - test Презентация на тему День юного героя - антифашиста

Презентация на тему День юного героя - антифашиста  Понятие греха , раскаяния и воздаяния

Понятие греха , раскаяния и воздаяния Обобщение опыта работы:

Обобщение опыта работы: Презентация на тему Теоремы синусов и косинусов 9 КЛАСС

Презентация на тему Теоремы синусов и косинусов 9 КЛАСС Сними меня, фотограф. Работа к 3 семинару по предмету Фотодело Нестеренко Данил

Сними меня, фотограф. Работа к 3 семинару по предмету Фотодело Нестеренко Данил Теория и история социологии второй половины 20 века

Теория и история социологии второй половины 20 века Гимнастика

Гимнастика Презентация на тему Диалог. Правильно говорим по телефону

Презентация на тему Диалог. Правильно говорим по телефону