Содержание

- 2. Сумматор двоичных чисел Полусумматор. При сложении двух двоичных цифр образуется сумма в данном разряде и при

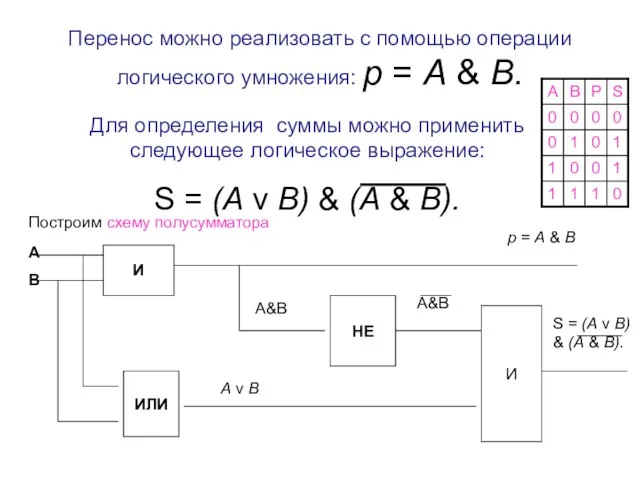

- 3. Перенос можно реализовать с помощью операции логического умножения: р = А & В. Для определения суммы

- 4. Полный одноразрядный сумматор 11111 10101 11111 110100 + pipi-1 an………aiai-1…a0 bn………bibi-1…b0 Sn+1Sn…SiSi-1…S0 + P=(A&B)+(A&P0)+(B&P0) S=(A+B+P0)&P S=(A+B+P0)&P0+(A&B&P0)

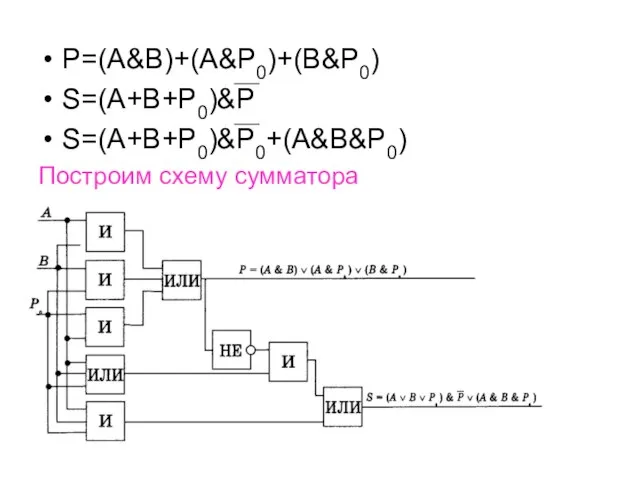

- 5. P=(A&B)+(A&P0)+(B&P0) S=(A+B+P0)&P S=(A+B+P0)&P0+(A&B&P0) Построим схему сумматора

- 6. Многоразрядный сумматор процессора состоит из полных одноразрядных сумматоров. На каждый разряд ставится одноразрядный сумматор причем выход

- 7. Триггер. Важнейшей структурной единицей оперативной памяти компьютер, а также внутренних регистров процессора является триггер. Триггер может

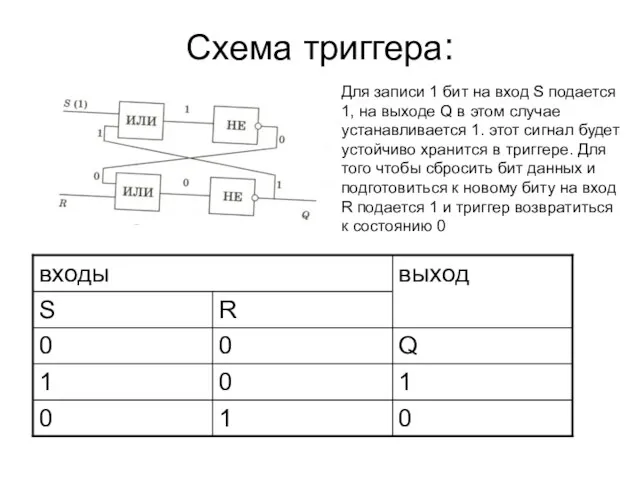

- 8. Схема триггера: Для записи 1 бит на вход S подается 1, на выходе Q в этом

- 10. Скачать презентацию

Тема: «Спортивные игры зимой»

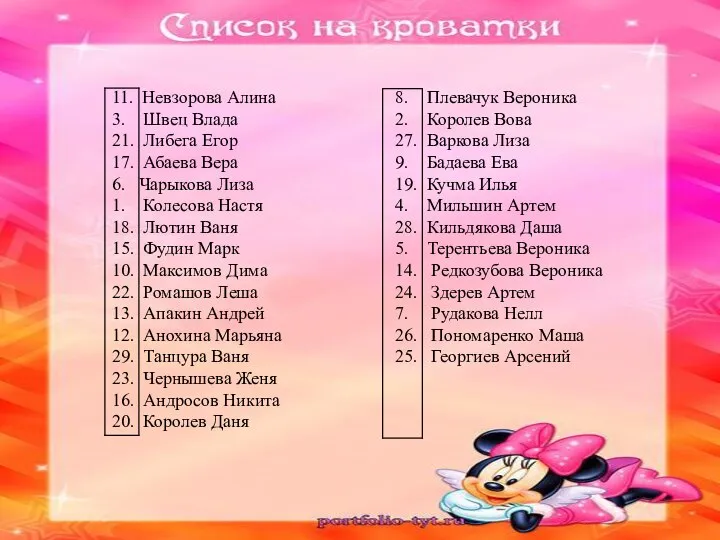

Тема: «Спортивные игры зимой» Список детей на получение кроватей и полотенец

Список детей на получение кроватей и полотенец Тепловые двигатели. Паровая турбина.

Тепловые двигатели. Паровая турбина. Система образования в Англии

Система образования в Англии Геометрические паркеты

Геометрические паркеты Подходы к системному целеполаганию. Лекция 2

Подходы к системному целеполаганию. Лекция 2 Конституция РФ

Конституция РФ Проект "Задачи на смеси и сплавы"

Проект "Задачи на смеси и сплавы" Раздел #. Дизайн интерьера

Раздел #. Дизайн интерьера Основы научных исследований

Основы научных исследований 000834aa-f5be4922

000834aa-f5be4922 Погружение

Погружение Невербальное общение

Невербальное общение Однородность керамзита

Однородность керамзита Презентация на тему Длина и меры ее измерения

Презентация на тему Длина и меры ее измерения Презентация на тему Экономика как наука

Презентация на тему Экономика как наука Кофемашина Yamaguchi CoffeeMann

Кофемашина Yamaguchi CoffeeMann Танковая викторина

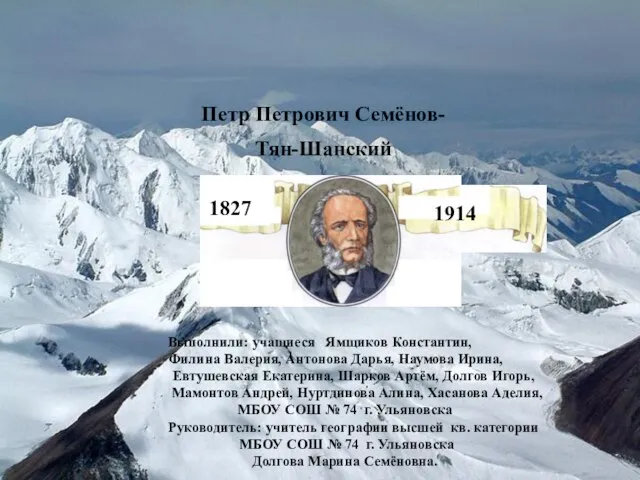

Танковая викторина Петр Петрович Семёнов-Тян-Шанский

Петр Петрович Семёнов-Тян-Шанский Александр

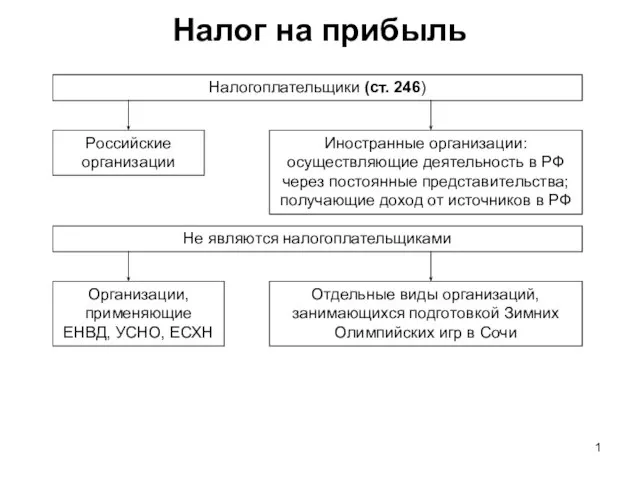

Александр Налог на прибыль

Налог на прибыль SPORTS in Our Life

SPORTS in Our Life  Аудирование —цель и средство обучения

Аудирование —цель и средство обучения Отношения мужчины и женщины. Женская психология

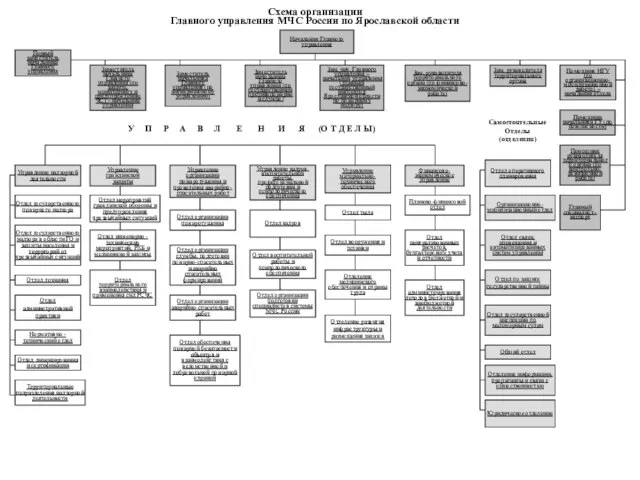

Отношения мужчины и женщины. Женская психология Схема организации Главного управления МЧС России по Ярославской области

Схема организации Главного управления МЧС России по Ярославской области Презентация на тему Афанасий Афанасьевич Фет (4 класс)

Презентация на тему Афанасий Афанасьевич Фет (4 класс) муниципальное образовательное учреждениеОбходская основная общеобразовательная школаУренского муниципального районаНижегор

муниципальное образовательное учреждениеОбходская основная общеобразовательная школаУренского муниципального районаНижегор куликовская битва

куликовская битва