Слайд 2Шина

Шина – группа проводников (сигналов), соединяющих различные устройства.

Шина позволяет осуществлять обмен данными

между устройствами.

Обычно, шина содержит сигналы адреса, данных и управляющие сигналы.

Слайд 3Протокол Шины

Соглашения о порядке обмена данными и правилах использования сигналов называются протоколом

шины.

По шине передаются дискретные сигналы.

Состояние шины меняется дискретно во времени.

Слайд 4Разновидности Сигналов

Устройства, подключенные к шине наблюдают за состоянием сигналов.

В соответствии с протоколом,

устройство управляет сигналами:

Активно

Только одно устройство может управлять данным сигналом

Через выход с тремя состояниями

В каждый момент времени сигналом управляет одно из устройств

Через выход с открытым коллектором

Несколько устройств управляют сигналом («монтажное ИЛИ»)

Слайд 5Мультиплексирование Адреса и Данных

Адрес и данные могут передаваться по одним линиям. Состояние

шины определяет, что передают эти линии в данный момент.

Слайд 6Разрядность

Разрядность определяет количество бит адреса и данных, передаваемых по шине.

Разрядность адреса и

данных может различаться.

Бывают 1-разрядные (последовательные) шины.

Слайд 7Синхронные Шины

Изменения состояния синхронной шины привязаны к периодам тактового сигнала.

Большинство шин –

синхронные.

Слайд 8Временная Диаграмма

Временная диаграмма специфицирует и иллюстрирует протокол шины. Временная диаграмма показывает последовательность

изменений состояний во времени.

Слайд 9Master/Slave

Master (инициатор) – устройство, инициирующее транзакцию на шине.

Slave – устройство, отвечающее на

транзакцию.

Архитектура шины может допускать наличие одного или нескольких инициаторов.

Слайд 10Арбитр

Нескольким инициаторам может потребоваться начать обмен одновременно.

Протокол шины должен позволить принять решение:

какому мастеру отдать приоритет.

Арбитр – специальное устройство, принимающее это решение.

Слайд 11Примеры Шинных Архитектур - PCI

PCI – Peripheral Component Interconnect

шина используется для подключения

периферийных устройств

синхронная (33/66MHz)

с мультиплексированием адреса и данных

Разрядность – 32/64 бита

Внешний арбитр

3 адресных пространства:

Конфигурационное

Ввода/вывода

Памяти

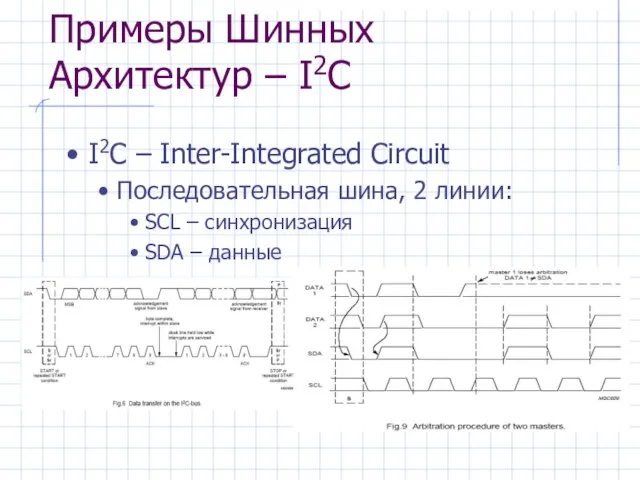

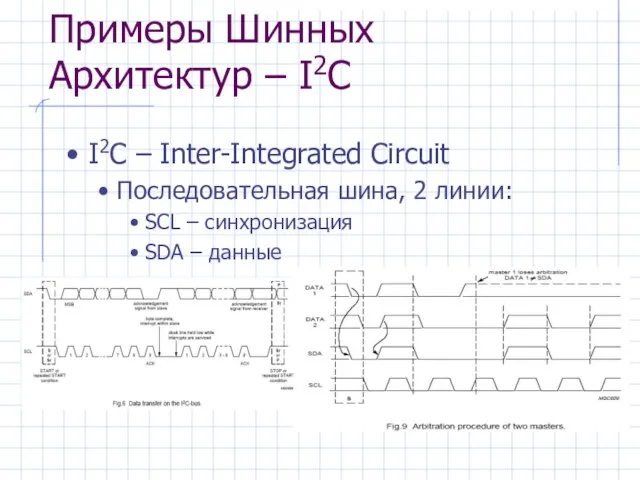

Слайд 12Примеры Шинных Архитектур – I2C

I2C – Inter-Integrated Circuit

Последовательная шина, 2 линии:

SCL –

синхронизация

SDA – данные

Слайд 13Примеры Шинных Архитектур

VME bus

Multibus, Multibus II

ISA

AMBA

Wishbone

Other…

1-Wire

SCSI

IDE/ATA

USB

AC’97

UTOPIA

MII

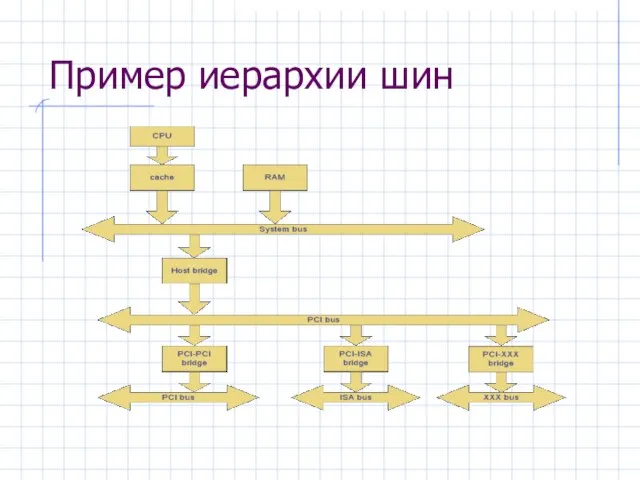

Слайд 14Мост (bridge)

Мост – устройство, которое транслирует транзакции между шинами (имеющими одинаковую, родственные

или различные архитектуры).

Мосты позволяют иерархически организовывать шины.

Слайд 16Зачем Нужны Мосты

Интеграция разнородных шин

Масштабирование

Преодоление физических ограничений

Оптимизация потоков данных

Замечание: периферийное устройство может

быть встроенной системой и являться предметом нашего рассмотрения!

Слайд 17DMA – прямой доступ к памяти

Устройство, осуществляющее DMA, способно производить пересылки данных

между устройством и памятью без вмешательства процессора.

Слайд 18Чтение и Запись

Концептуальное различие между операциями чтения и записи в память:

Операция чтения

– блокирующая. Выполняя операцию чтения, необходимо дождаться результата.

При записи в память, ожидание окончания записи не является обязательным (при условии сохранения последовательности операций).

Операции записи можно откладывать.

Местонахождение буферов влияет на производительность!

Слайд 19Кэш-память

Быстродействующая память, находящаяся между процессором и основной памятью.

В кэш-памяти хранятся часто используемые

данные (принцип локальности).

Позволяет существенно улучшить производительность системы.

Время работы программного кода становится фактически непредсказуемым.

Слайд 21Рассогласование

При осуществлении DMA доступа, содержимое кэш-памяти и основной памяти может стать рассогласованным:

Процессор

работает с данными

Устройство пишет в память по тому же адресу.

За этим надо строго следить!

СРАВНИТЬ и ВЫБРАТЬ Презентация Maanimo.com – портала объективного сравнения финансовых услуг для рекламных и медиа-агентств Киев, 05.02.09

СРАВНИТЬ и ВЫБРАТЬ Презентация Maanimo.com – портала объективного сравнения финансовых услуг для рекламных и медиа-агентств Киев, 05.02.09 Красный, жёлтый, зелёный.

Красный, жёлтый, зелёный. «Конструирование рукава» 9 класс

«Конструирование рукава» 9 класс Презентация на тему Предмет физики и ее связь с другими науками

Презентация на тему Предмет физики и ее связь с другими науками Устный счет

Устный счет Правила поведения в классе

Правила поведения в классе Мой 8 гуманитарный класс (информация к размышлению)

Мой 8 гуманитарный класс (информация к размышлению) Лобовой щит СДПМ

Лобовой щит СДПМ Правление Ярослава Мудрого

Правление Ярослава Мудрого Конфликт. Пути предотвращения и разрешения

Конфликт. Пути предотвращения и разрешения For Вікторія Костецька

For Вікторія Костецька Русское искусство второй половины XIX века

Русское искусство второй половины XIX века Баскетбол. История

Баскетбол. История Презентация«Стандарт качества организации работы по управлению бизнес-процессами в кредитных организациях»

Презентация«Стандарт качества организации работы по управлению бизнес-процессами в кредитных организациях» Бритва. Сказка от Леонардо да Винчи

Бритва. Сказка от Леонардо да Винчи Создавай Будущее Легко. Инстант Инвест

Создавай Будущее Легко. Инстант Инвест КАБИНЕТ КОМПЛЕКСНОЙ БЕЗОПАСНОСТИ ГОУ СОШ №426 Ответственный за кабинет: Семин Дмитрий Владимирович

КАБИНЕТ КОМПЛЕКСНОЙ БЕЗОПАСНОСТИ ГОУ СОШ №426 Ответственный за кабинет: Семин Дмитрий Владимирович Мой девиз Где обитаю

Мой девиз Где обитаю СРЕДСТВА И МЕТОДЫ РАЗВИТИЯ СКОРОСТНЫХ СПОСОБНОСТЕЙ БОРЦОВ

СРЕДСТВА И МЕТОДЫ РАЗВИТИЯ СКОРОСТНЫХ СПОСОБНОСТЕЙ БОРЦОВ Метапредметный подход, что это такое и зачем?

Метапредметный подход, что это такое и зачем? Проигрыватели компакт - дисков

Проигрыватели компакт - дисков Мы - граждане Российской Федерации. 12 декабря – День Конституции РФ

Мы - граждане Российской Федерации. 12 декабря – День Конституции РФ Построение федеральной сети мебели и товаров для дома в России

Построение федеральной сети мебели и товаров для дома в России Знаки зодиака (1 класс)

Знаки зодиака (1 класс) Портфолио. Тулуш Сылдыс Олегович

Портфолио. Тулуш Сылдыс Олегович Розовый цвет в рекламе

Розовый цвет в рекламе «Российская грамматика» М.В.Ломоносова

«Российская грамматика» М.В.Ломоносова Системно-целостный подход

Системно-целостный подход