Слайд 22

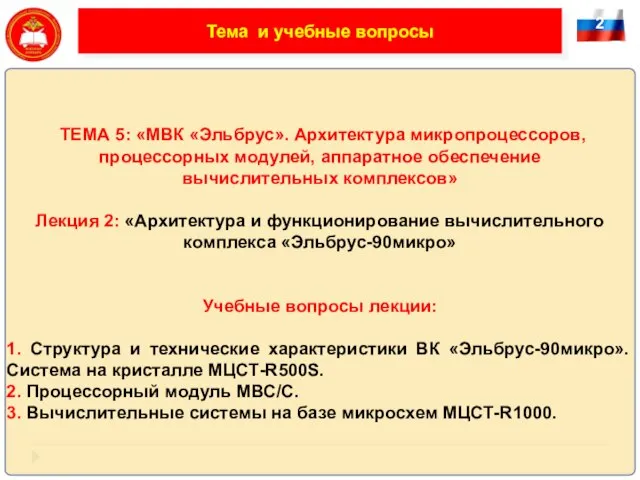

Тема и учебные вопросы

ТЕМА 5: «МВК «Эльбрус». Архитектура микропроцессоров, процессорных модулей,

аппаратное обеспечение

вычислительных комплексов»

Лекция 2: «Архитектура и функционирование вычислительного комплекса «Эльбрус-90микро»

Учебные вопросы лекции:

1. Структура и технические характеристики ВК «Эльбрус-90микро». Система на кристалле МЦСТ-R500S.

2. Процессорный модуль МВС/C.

3. Вычислительные системы на базе микросхем МЦСТ-R1000.

Слайд 33

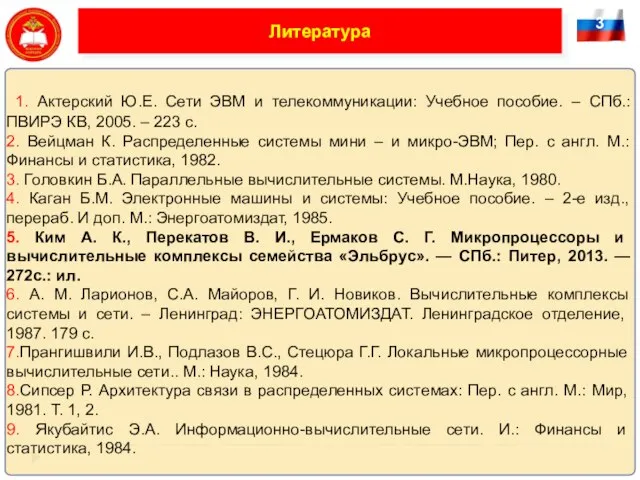

Литература

1. Актерский Ю.Е. Сети ЭВМ и телекоммуникации: Учебное пособие. – СПб.:

ПВИРЭ КВ, 2005. – 223 с.

2. Вейцман К. Распределенные системы мини – и микро-ЭВМ; Пер. с англ. М.: Финансы и статистика, 1982.

3. Головкин Б.А. Параллельные вычислительные системы. М.Наука, 1980.

4. Каган Б.М. Электронные машины и системы: Учебное пособие. – 2-е изд., перераб. И доп. М.: Энергоатомиздат, 1985.

5. Ким А. К., Перекатов В. И., Ермаков С. Г. Микропроцессоры и вычислительные комплексы семейства «Эльбрус». — СПб.: Питер, 2013. — 272с.: ил.

6. А. М. Ларионов, С.А. Майоров, Г. И. Новиков. Вычислительные комплексы системы и сети. – Ленинград: ЭНЕРГОАТОМИЗДАТ. Ленинградское отделение, 1987. 179 с.

7.Прангишвили И.В., Подлазов В.С., Стецюра Г.Г. Локальные микропроцессорные вычислительные сети.. М.: Наука, 1984.

8.Сипсер Р. Архитектура связи в распределенных системах: Пер. с англ. М.: Мир, 1981. Т. 1, 2.

9. Якубайтис Э.А. Информационно-вычислительные сети. И.: Финансы и статистика, 1984.

Слайд 44

Учебный вопрос №1

Структура и технические характеристики ВК

«Эльбрус-90микро». Система на кристалле МЦСТ-R500S

Слайд 55

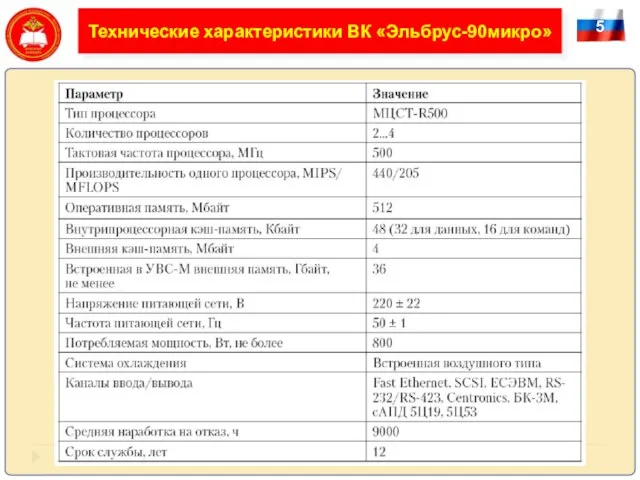

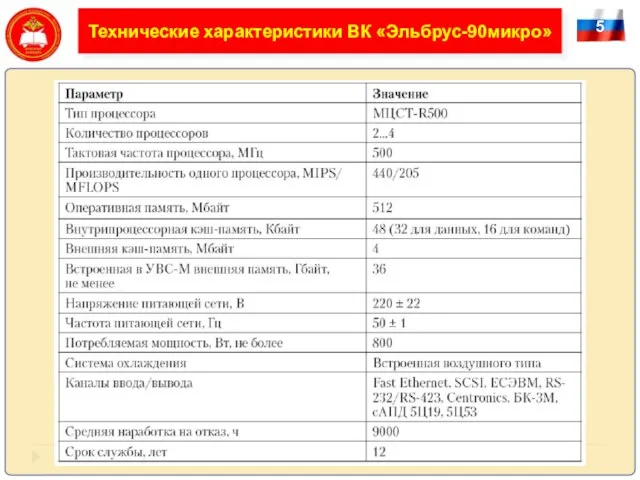

Технические характеристики ВК «Эльбрус-90микро»

Архитектура МВК “Эльбрус-2”

Слайд 66

Структурная схема ВК «Эльбрус-90микро»

Архитектура МВК “Эльбрус-2”

Слайд 77

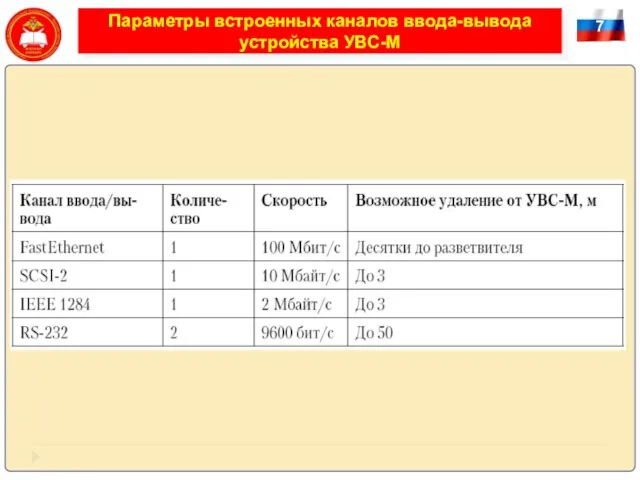

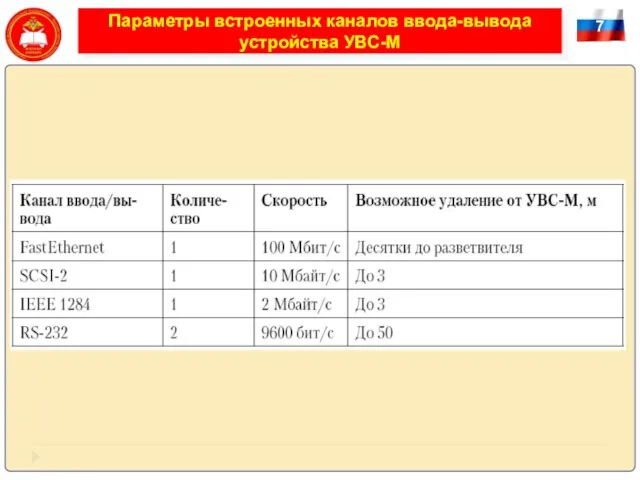

Параметры встроенных каналов ввода-вывода устройства УВС-М

Слайд 88

Учебный вопрос №1

Система на кристалле МЦСТ-R500S

Слайд 99

Внешний вид системы на кристалле МЦСТ-R500S

Слайд 1010

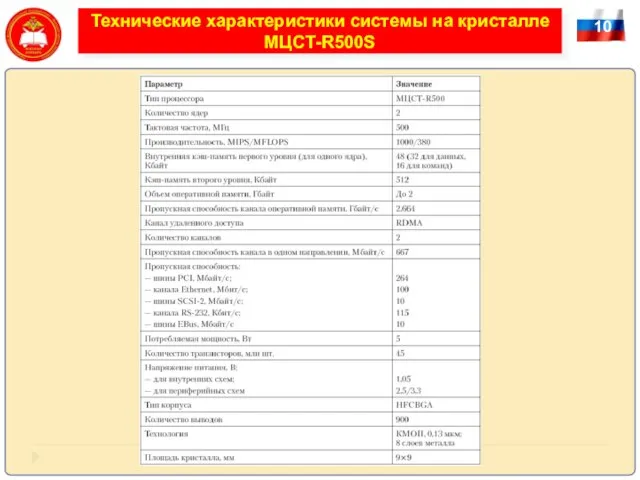

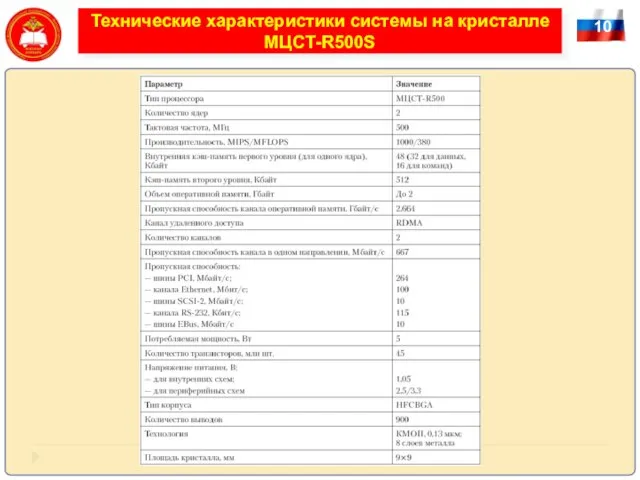

Технические характеристики системы на кристалле МЦСТ-R500S

Слайд 1111

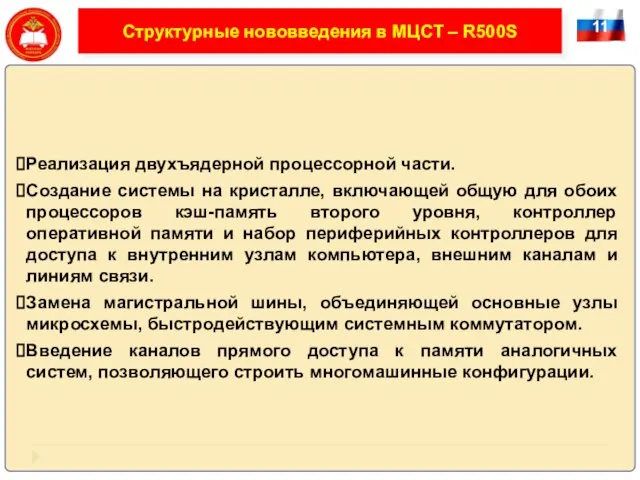

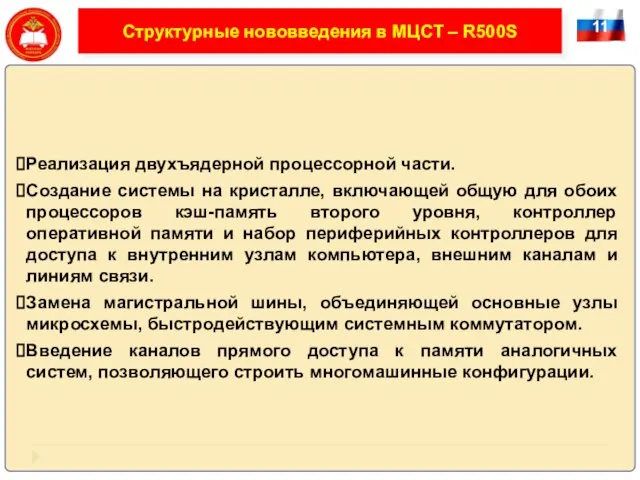

Структурные нововведения в МЦСТ – R500S

Реализация двухъядерной процессорной части.

Создание системы на кристалле,

включающей общую для обоих процессоров кэш-память второго уровня, контроллер оперативной памяти и набор периферийных контроллеров для доступа к внутренним узлам компьютера, внешним каналам и линиям связи.

Замена магистральной шины, объединяющей основные узлы микросхемы, быстродействующим системным коммутатором.

Введение каналов прямого доступа к памяти аналогичных систем, позволяющего строить многомашинные конфигурации.

Слайд 1212

Структурная схема системы на кристалле

МЦСТ-R500S

Слайд 1313

Учебный вопрос № 2

Процессорный модуль МВС/C

Слайд 1414

Внешний вид процессорного модуля МВС/С

Слайд 1515

Структурная схема процессорного модуля МВС/С

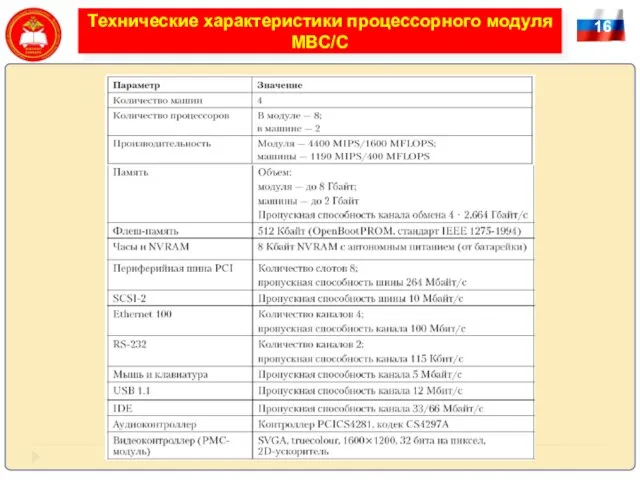

Слайд 1616

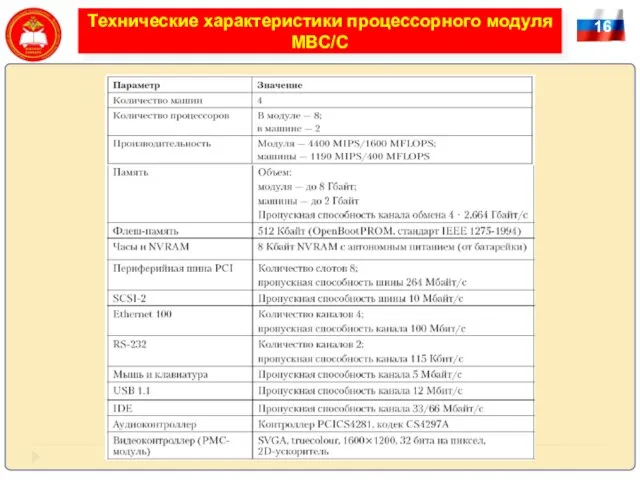

Технические характеристики процессорного модуля МВС/С

Слайд 1717

Учебный вопрос № 3

Вычислительные системы на базе микросхем

МЦСТ-R1000

Слайд 1818

Структурная схема системы на кристалле

МЦСТ-R1000

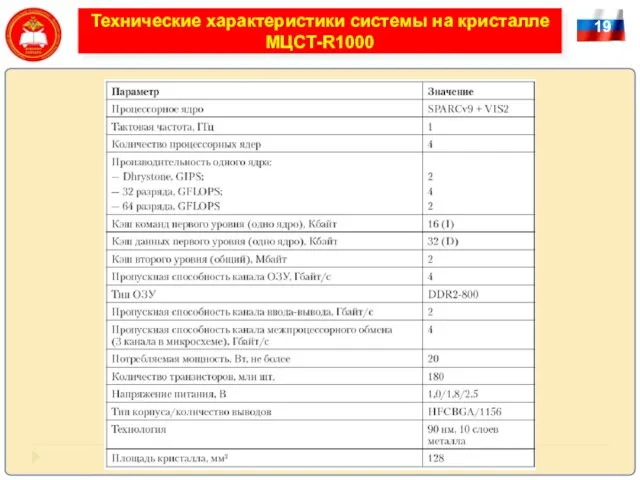

Слайд 1919

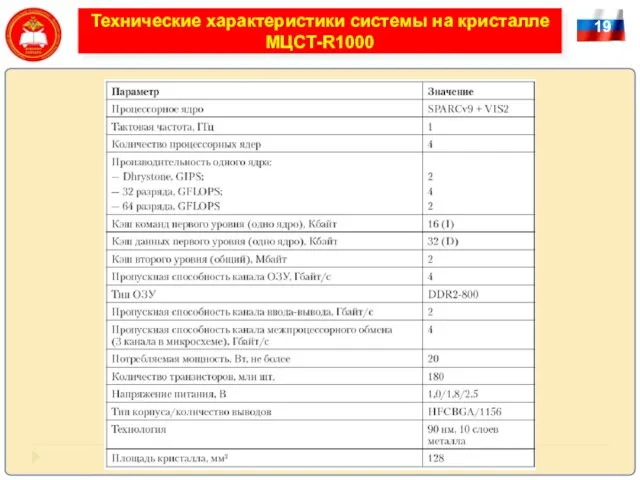

Технические характеристики системы на кристалле МЦСТ-R1000

Слайд 2020

Учебный вопрос № 3

Вычислительные системы на базе микросхем

МЦСТ-R1000

Слайд 2121

Вычислительная система на базе микросхем

МЦСТ-R1000

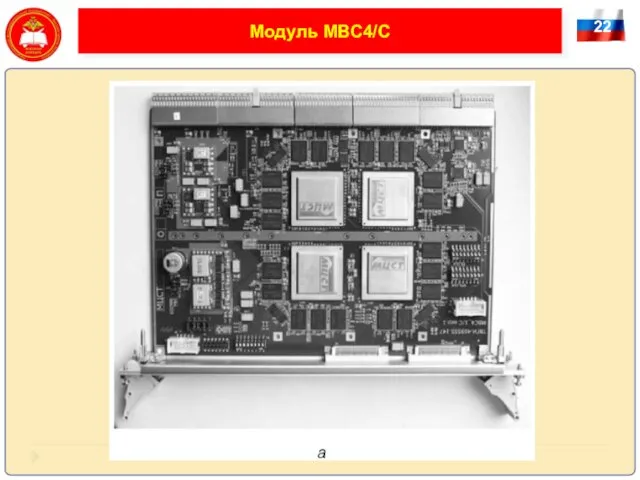

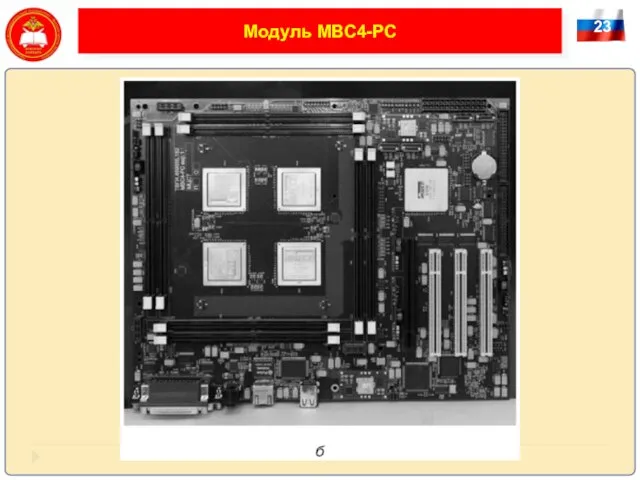

Слайд 2424

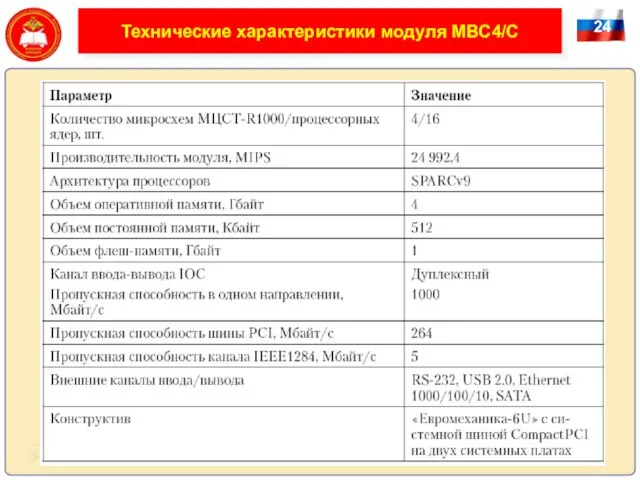

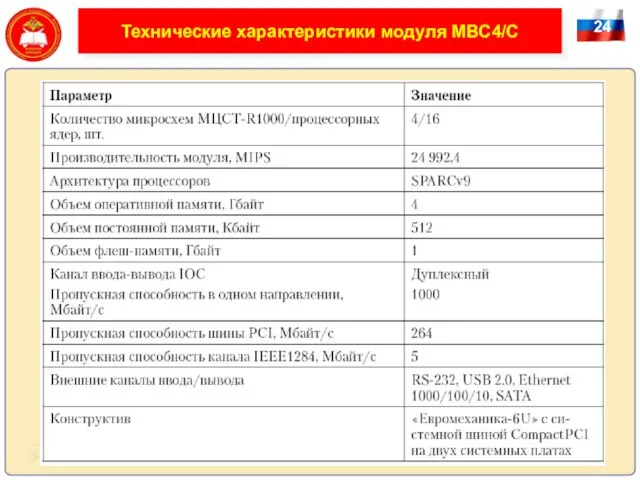

Технические характеристики модуля МВС4/С

Слайд 2525

Технические характеристики модуля МВС4-PC

Слайд 2626

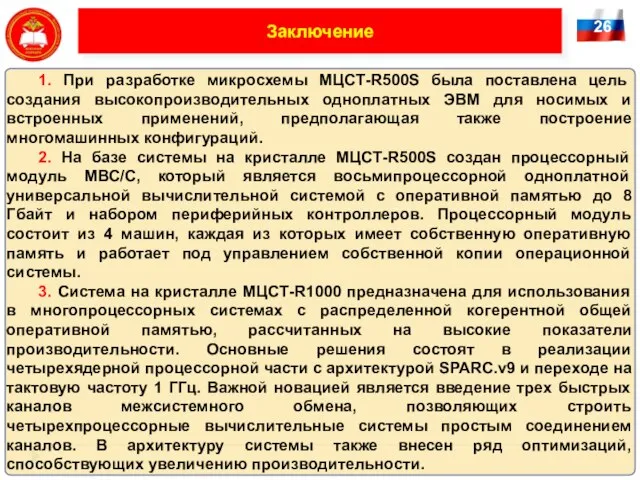

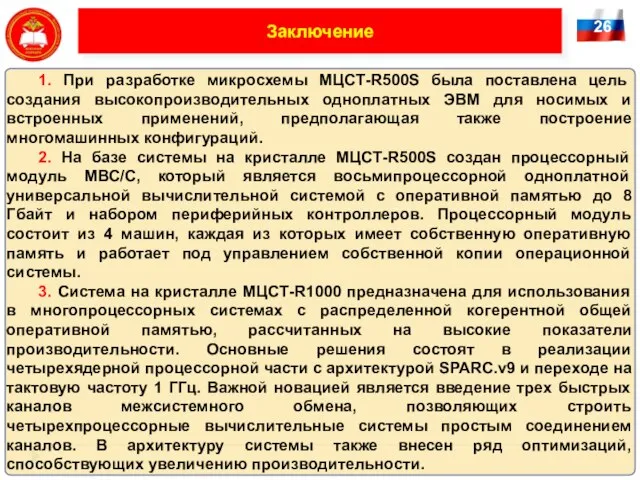

Заключение

1. При разработке микросхемы МЦСТ-R500S была поставлена цель создания высокопроизводительных одноплатных ЭВМ

для носимых и встроенных применений, предполагающая также построение многомашинных конфигураций.

2. На базе системы на кристалле МЦСТ-R500S создан процессорный модуль МВС/С, который является восьмипроцессорной одноплатной универсальной вычислительной системой с оперативной памятью до 8 Гбайт и набором периферийных контроллеров. Процессорный модуль состоит из 4 машин, каждая из которых имеет собственную оперативную память и работает под управлением собственной копии операционной системы.

3. Система на кристалле МЦСТ-R1000 предназначена для использования в многопроцессорных системах с распределенной когерентной общей оперативной памятью, рассчитанных на высокие показатели производительности. Основные решения состоят в реализации четырехядерной процессорной части с архитектурой SPARC.v9 и переходе на тактовую частоту 1 ГГц. Важной новацией является введение трех быстрых каналов межсистемного обмена, позволяющих строить четырехпроцессорные вычислительные системы простым соединением каналов. В архитектуру системы также внесен ряд оптимизаций, способствующих увеличению производительности.

Слайд 2727

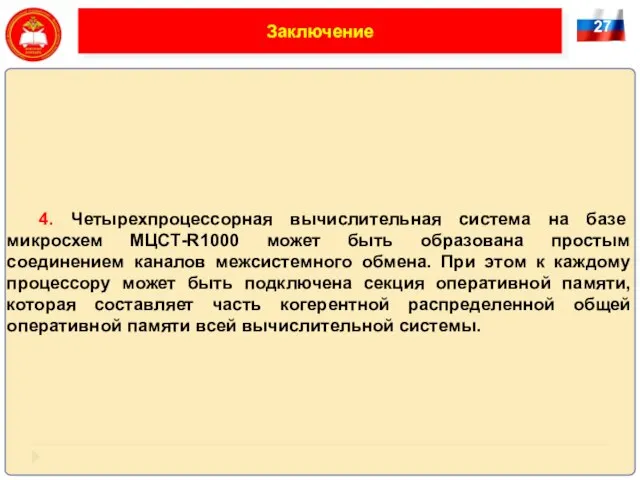

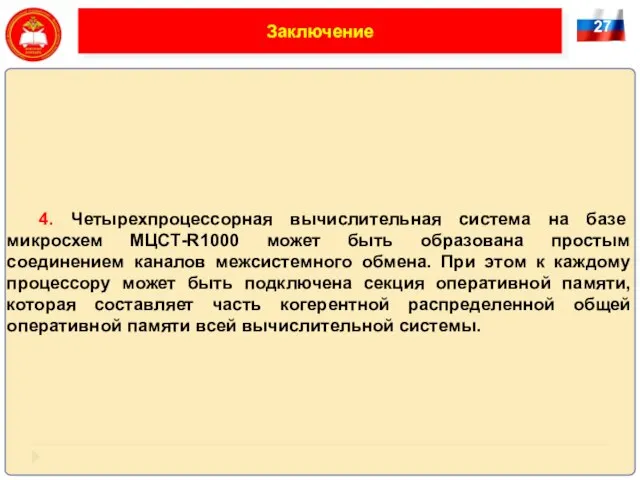

Заключение

4. Четырехпроцессорная вычислительная система на базе микросхем МЦСТ-R1000 может быть образована простым

соединением каналов межсистемного обмена. При этом к каждому процессору может быть подключена секция оперативной памяти, которая составляет часть когерентной распределенной общей оперативной памяти всей вычислительной системы.

Тизерная кухня. (День 5)

Тизерная кухня. (День 5) Знакомство с библиотекой

Знакомство с библиотекой Решение логических задач

Решение логических задач Графический редактор Paint

Графический редактор Paint Что такое пиксель? Видеомонтаж

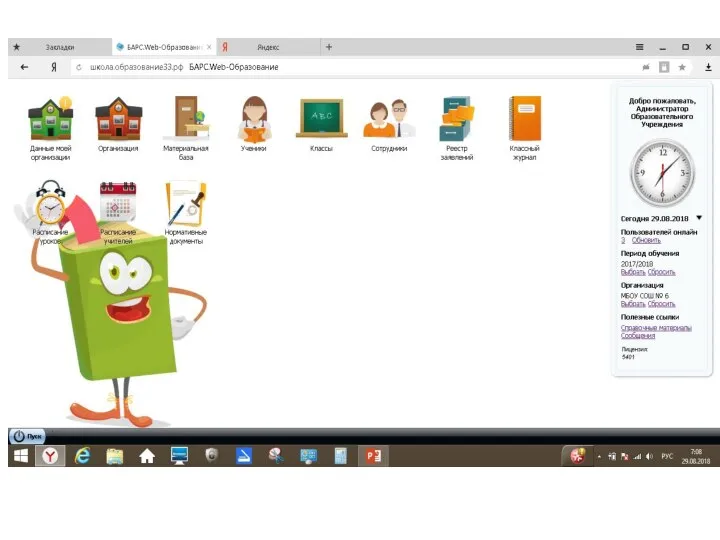

Что такое пиксель? Видеомонтаж БАРС. Web-образование

БАРС. Web-образование Информационные ресурсы и сервисы Интернета

Информационные ресурсы и сервисы Интернета Профилактика киберпреступлений и борьба с ними

Профилактика киберпреступлений и борьба с ними Анимация “Колобок”

Анимация “Колобок” Информационная система аптеки кассира

Информационная система аптеки кассира Базы данных и системы управления ими

Базы данных и системы управления ими Як регіструватись на сайті “Навчальна платформа”

Як регіструватись на сайті “Навчальна платформа” Новая онлайн-версия КонсультантПлюс: Студент

Новая онлайн-версия КонсультантПлюс: Студент Классификация прикладного программного обеспечения. Лекция 5

Классификация прикладного программного обеспечения. Лекция 5 goCoworking. Система бронирования коворкингов

goCoworking. Система бронирования коворкингов Алфавитный подход к определению количества информации

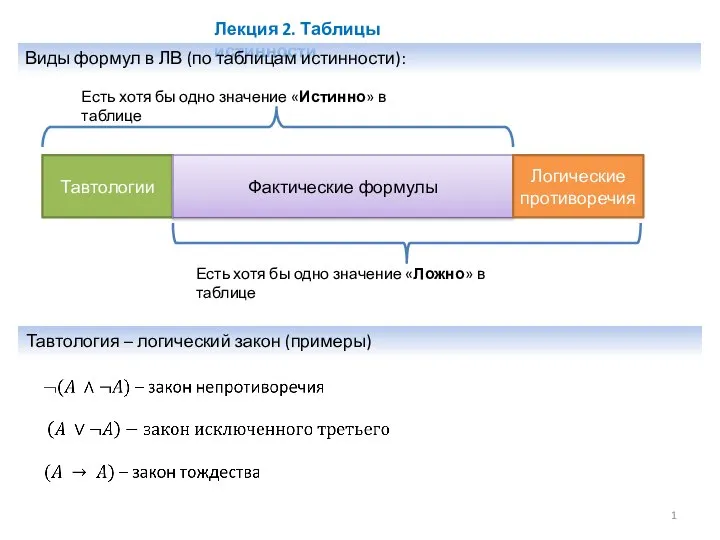

Алфавитный подход к определению количества информации Urok_12_Elementy_algebry_logiki

Urok_12_Elementy_algebry_logiki Плакаты по Word

Плакаты по Word Основы тестирования

Основы тестирования Автоматизированная система сбора данных о качестве сборочных операций

Автоматизированная система сбора данных о качестве сборочных операций Таблицы истинности

Таблицы истинности Презентация на тему Адресация в сети интернет

Презентация на тему Адресация в сети интернет  Информационные технологии в профессиональной деятельности

Информационные технологии в профессиональной деятельности Что такое Google

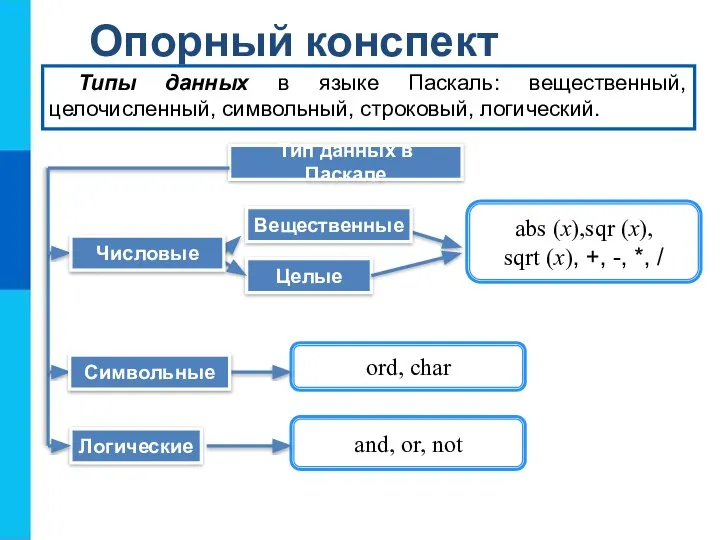

Что такое Google Типы данных в языке Паскаль: вещественный, целочисленный, символьный, строковый, логический

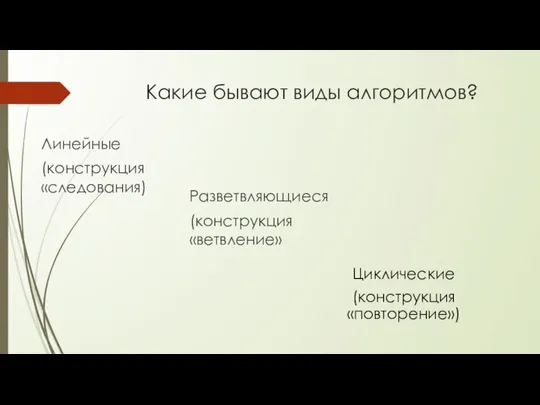

Типы данных в языке Паскаль: вещественный, целочисленный, символьный, строковый, логический Виды алгоритмов

Виды алгоритмов С прием на работу при наличии программного обеспечения 1С

С прием на работу при наличии программного обеспечения 1С Безопасность в интернете

Безопасность в интернете