Содержание

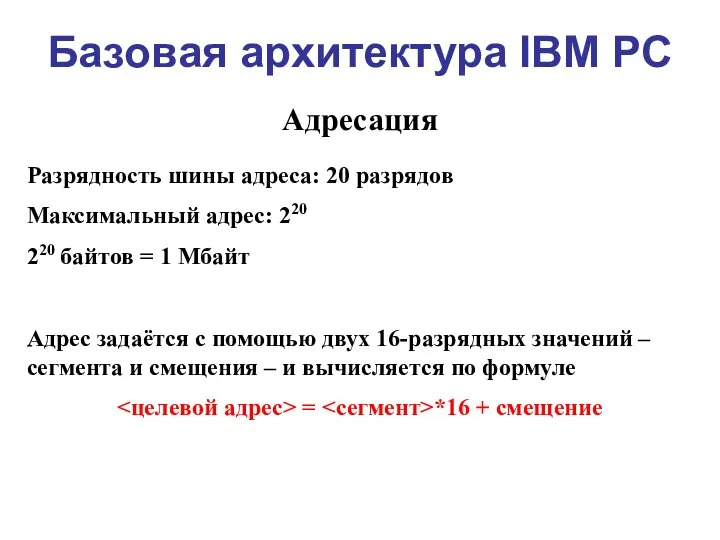

- 2. Базовая архитектура IBM PC Адресация Разрядность шины адреса: 20 разрядов Максимальный адрес: 220 220 байтов =

- 3. Базовая архитектура IBM PC Система команд Команды пересылки: а) между регистрами и памятью; б) между регистрами

- 4. Базовая архитектура IBM PC Организация вычислительного процесса Вычислительный процесс организован в полном соответствии с принципами фон

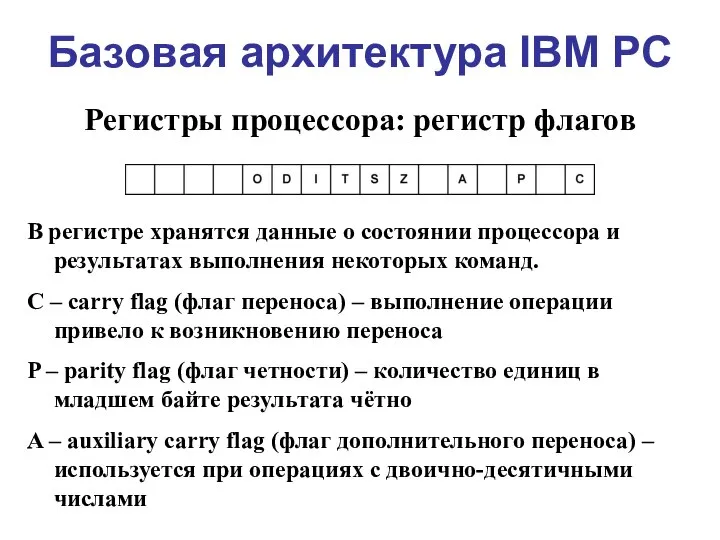

- 5. Базовая архитектура IBM PC Регистры процессора: регистр флагов В регистре хранятся данные о состоянии процессора и

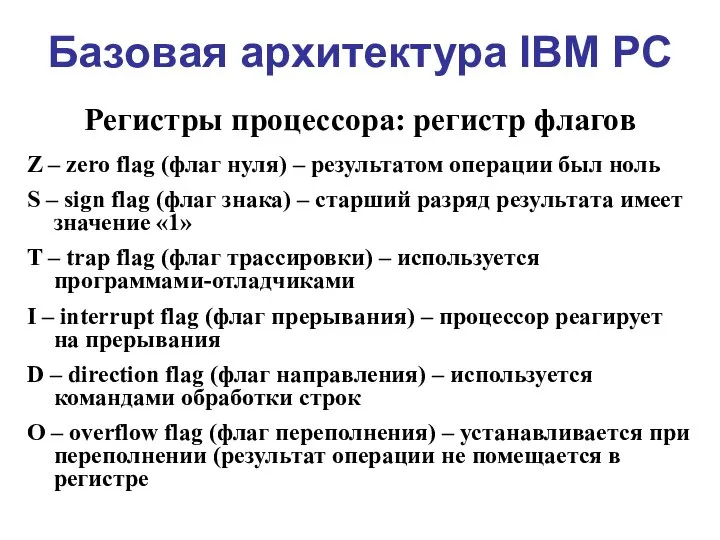

- 6. Базовая архитектура IBM PC Регистры процессора: регистр флагов Z – zero flag (флаг нуля) – результатом

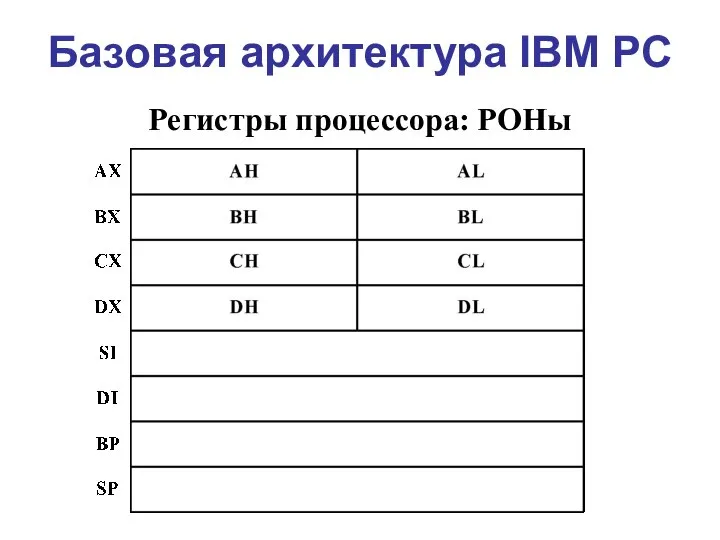

- 7. Базовая архитектура IBM PC Регистры процессора: РОНы

- 8. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр AX (accumulator, аккумулятор) Это регистр-накопитель. Наиболее эффективно его

- 9. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр BX (base, базовый регистр) В некоторых операциях этот

- 10. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр CX (counter, счётчик) Обычно этот регистр используется как

- 11. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр DX (data, регистр данных) Этот регистр используется в

- 12. Базовая архитектура IBM PC Регистры процессора: РОНы Регистры SI, DI Индексные регистры источника (SI, source index)

- 13. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр BP Базовый регистр, в котором содержится смещение относительно

- 14. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр SP (stack pointer, указатель стека) В SP содержится

- 15. Базовая архитектура IBM PC Регистры процессора: РОНы Регистр IP (instruction pointer, счётчик команд) Регистр содержит адрес

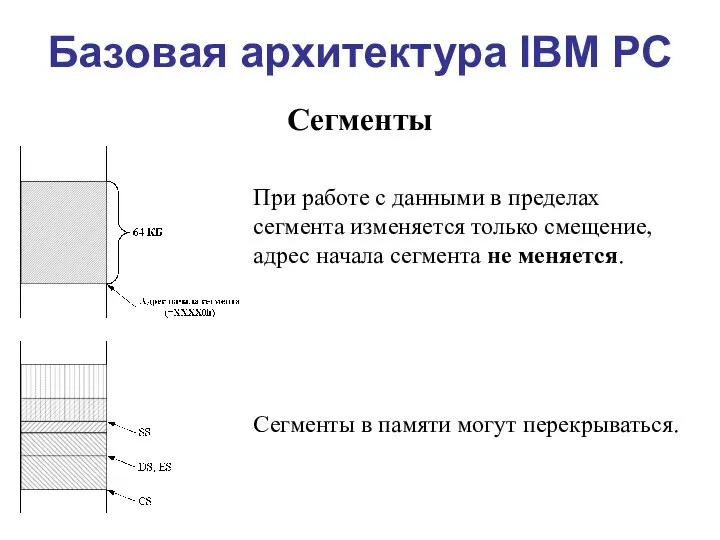

- 16. Базовая архитектура IBM PC Сегменты При работе с данными в пределах сегмента изменяется только смещение, адрес

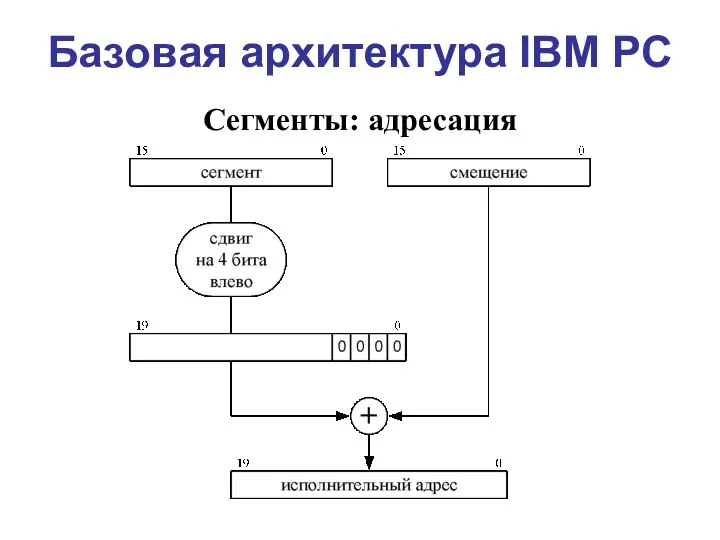

- 17. Базовая архитектура IBM PC Сегменты: адресация

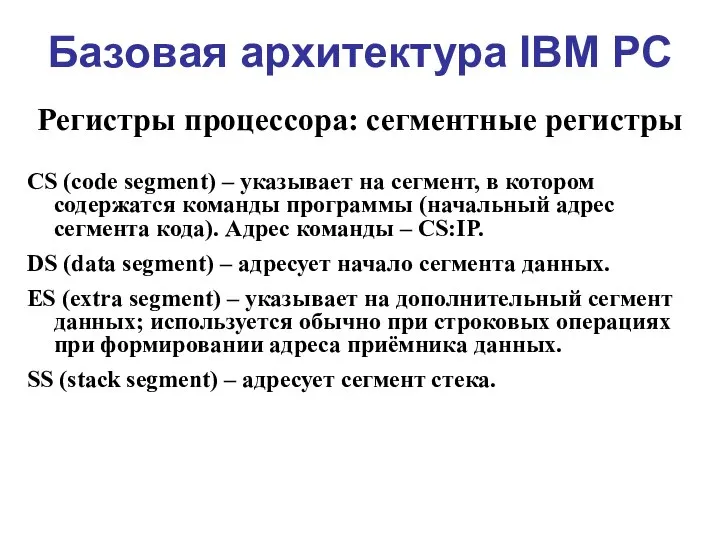

- 18. Базовая архитектура IBM PC Регистры процессора: сегментные регистры CS (code segment) – указывает на сегмент, в

- 19. Базовая архитектура IBM PC Система прерываний Предусмотрены прерывания аппаратные и программные. Всего в системе может быть

- 21. Скачать презентацию

Операции с целыми числами. Программирование на языке Python

Операции с целыми числами. Программирование на языке Python Использование образовательных платформ как средство повышения качества обучения

Использование образовательных платформ как средство повышения качества обучения Библиотека Requests API

Библиотека Requests API Презентация на тему Информатика для начинающих

Презентация на тему Информатика для начинающих  Диаграммы взаимодействия

Диаграммы взаимодействия Конфигурирование операционной системы

Конфигурирование операционной системы Технология программирования

Технология программирования Лаборатория высоких технологий

Лаборатория высоких технологий Основные устройства персонального компьютера

Основные устройства персонального компьютера OASIS DDB децентрализованная база данных. Преимущества и выгоды простым и понятным языком

OASIS DDB децентрализованная база данных. Преимущества и выгоды простым и понятным языком Информационная система для профессионального образования Бугульминский машиностроительный техникум

Информационная система для профессионального образования Бугульминский машиностроительный техникум Основы языка JavaScript

Основы языка JavaScript Язык программирования Pascal Повторение А. Жидков

Язык программирования Pascal Повторение А. Жидков Преобразование библиотеки

Преобразование библиотеки Autodesk inventor работа в режиме Модель. Конструкционные операции. Стратегия построения

Autodesk inventor работа в режиме Модель. Конструкционные операции. Стратегия построения Иду в ИТ

Иду в ИТ Приватность в цифровом мире. Урок Цифры № 3

Приватность в цифровом мире. Урок Цифры № 3 Оформление исследовательской работы

Оформление исследовательской работы Элементы цифровой среды, связанные с ЭБС

Элементы цифровой среды, связанные с ЭБС Функции и модули (1)

Функции и модули (1) Интерактивная система помощи иностранным студентам

Интерактивная система помощи иностранным студентам Операционная система Windows

Операционная система Windows Внедрение ИИ – ботов в инфраструктуру городов

Внедрение ИИ – ботов в инфраструктуру городов Презентация на тему Звуковые карты

Презентация на тему Звуковые карты  Персональный компьютер

Персональный компьютер Машинное обучение. Лекция №4

Машинное обучение. Лекция №4 Компьютерная графика

Компьютерная графика Презентация на тему Современные носители информации

Презентация на тему Современные носители информации