Слайд 3Структурные единицы ЭВМ

В ЭВМ различают структурные единицы (с точки зрения электроники):

Элементы –

обработка одной единицы электронных сигналов (битов информации). Часть электронной схемы, которая реализует элементарную логическую функцию, называется логический элемент компьютера.

Узлы – одновременная обработка группы электронных сигналов (информационных слов)

Блоки – некоторая последовательность в обработке информационных слов

Устройства – выполнение отдельных машинных операций и их последовательности

Слайд 4Цифровые схемы

Цифровой сигнал — это сигнал, принимающий только два логических значения,

которые можно закодировать цифрами 0 и 1.

Цифровая схема – это схема, в которой циркулируют цифровые сигналы.

Обычно электрический сигнал с напряжением от 0 до 1 В представляет одно значение (например, 0), а сигнал с напряжением от 2 до 5 В — другое значение (например, 1).

Напряжение за пределами указанных величин недопустимо.

Цифровые схемы конструируются из небольшого числа простых элементов, называемых вентилями, путем сочетания этих элементов в различных комбинациях.

Слайд 5Вентили

Вентили - крошечные электронные устройства, позволяющие получать различные функции от этих двузначных

сигналов. Лежат в основе аппаратного обеспечения, на котором строятся все цифровые компьютеры.

Логически вентиль - цифровая схема, в которой есть только два логических значения.

У каждого вентиля есть одно или несколько цифровых входных данных (сигналов, представляющих 0 или 1).

Вентиль вычисляет простые функции этих сигналов, такие как логические И или ИЛИ.

Каждый вентиль формируется из нескольких транзисторов.

Несколько вентилей формируют 1 бит памяти, который может содержать 0 или 1.

Биты памяти, объединенные в группы, например, по 16, 32 или 64, формируют регистры (элементы процессора).

Из вентилей также может строиться само ядро вычислительной системы.

Слайд 7Логические операции и базовые элементы компьютера

Понятие булевой (логической) функции

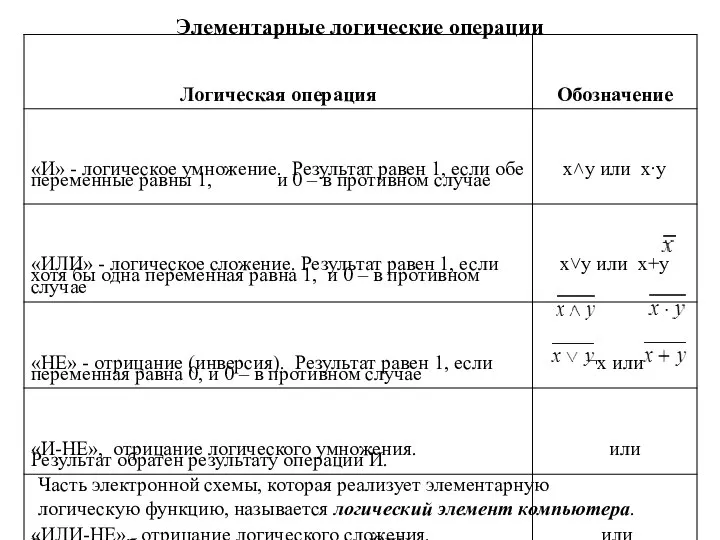

Элементарные логические операции

Способы задания

булевой функции. Понятие таблицы истинности

Реализация булевых функций в виде электронных схем

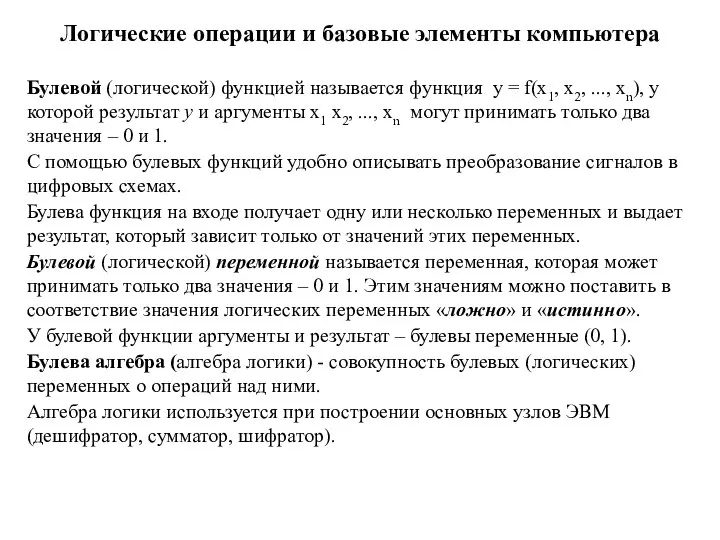

Слайд 8Логические операции и базовые элементы компьютера

Булевой (логической) функцией называется функция y =

f(х1, х2, ..., хn), у которой результат у и аргументы х1 х2, ..., хn могут принимать только два значения – 0 и 1.

С помощью булевых функций удобно описывать преобразование сигналов в цифровых схемах.

Булева функция на входе получает одну или несколько переменных и выдает результат, который зависит только от значений этих переменных.

Булевой (логической) переменной называется переменная, которая может принимать только два значения – 0 и 1. Этим значениям можно поставить в соответствие значения логических переменных «ложно» и «истинно».

У булевой функции аргументы и результат – булевы переменные (0, 1).

Булева алгебра (алгебра логики) - совокупность булевых (логических) переменных о операций над ними.

Алгебра логики используется при построении основных узлов ЭВМ (дешифратор, сумматор, шифратор).

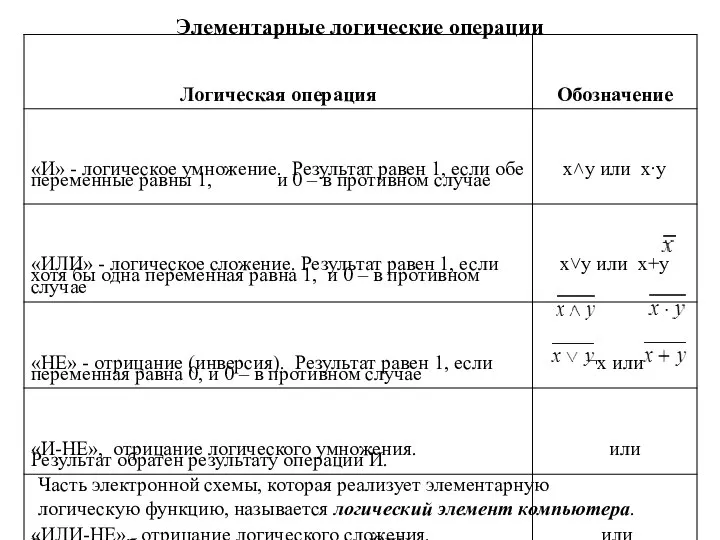

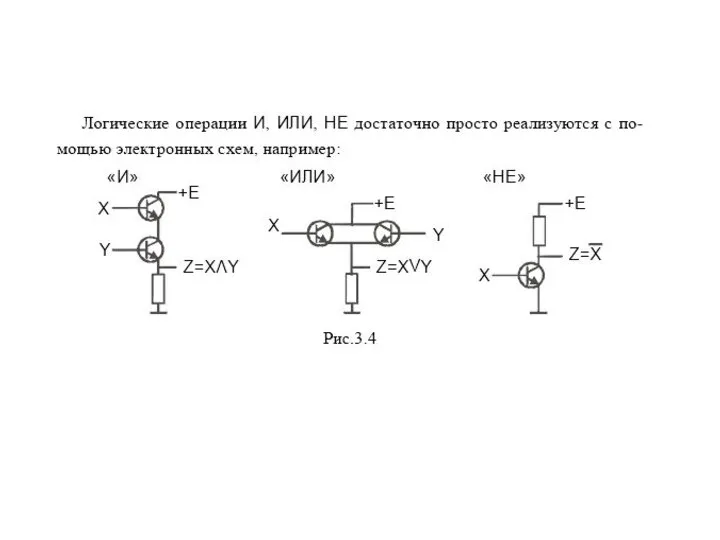

Слайд 9Элементарные логические операции

Часть электронной схемы, которая реализует элементарную логическую функцию, называется логический

элемент компьютера.

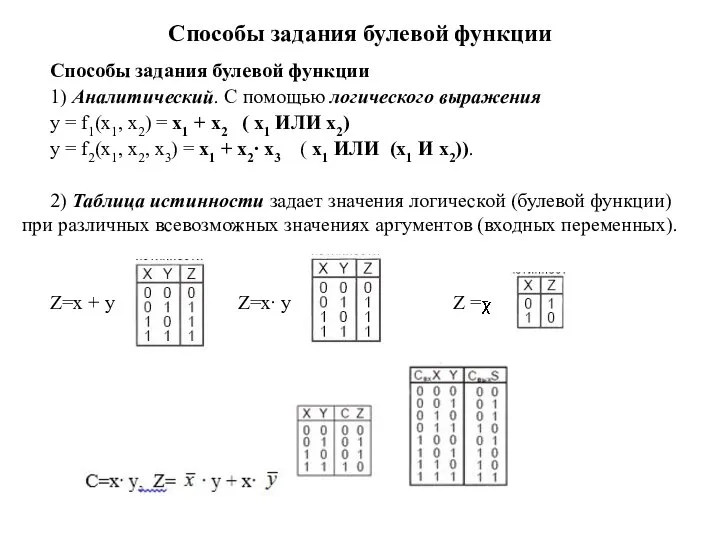

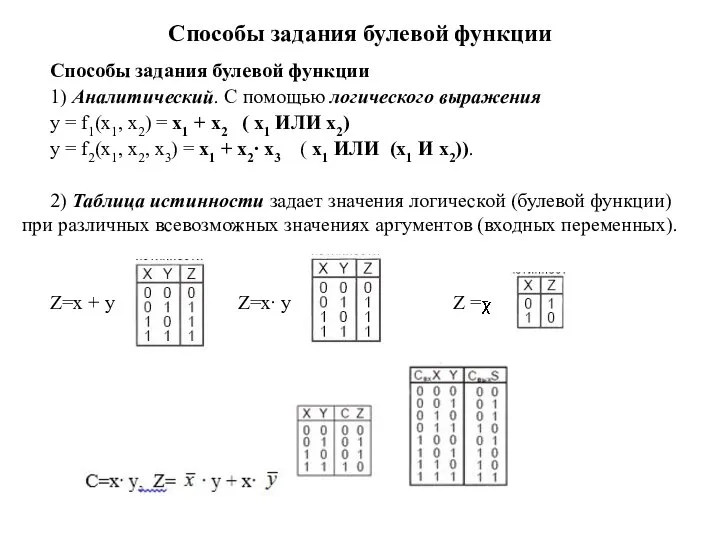

Слайд 11Способы задания булевой функции

Способы задания булевой функции

1) Аналитический. С помощью логического выражения

y = f1(х1, х2) = х1 + х2 ( х1 ИЛИ х2)

y = f2(х1, х2, х3) = х1 + х2∙ х3 ( х1 ИЛИ (х1 И х2)).

2) Таблица истинности задает значения логической (булевой функции) при различных всевозможных значениях аргументов (входных переменных).

Z=х + y Z=х∙ y Z =

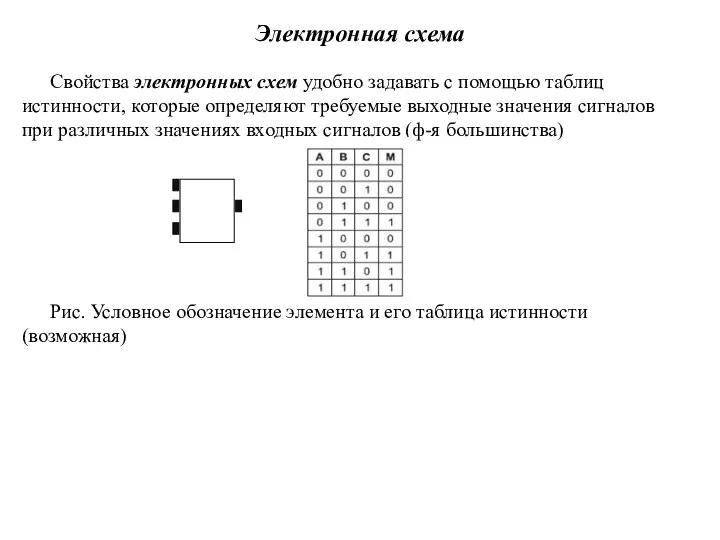

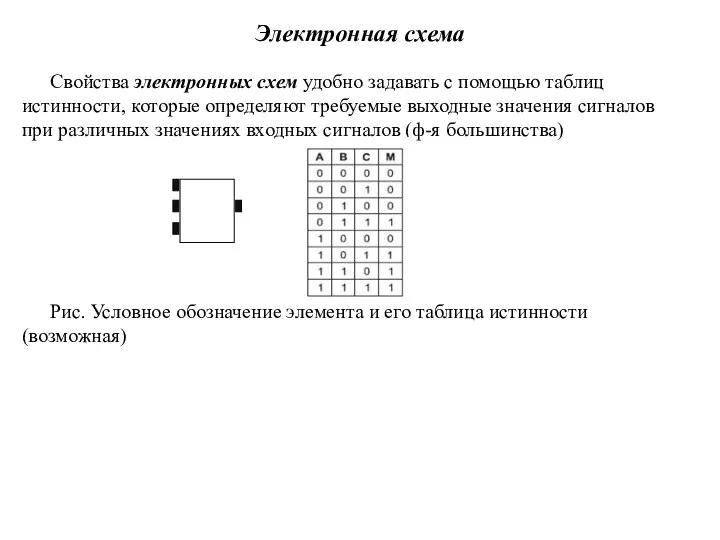

Слайд 12Электронная схема

Свойства электронных схем удобно задавать с помощью таблиц истинности, которые определяют

требуемые выходные значения сигналов при различных значениях входных сигналов (ф-я большинства)

Рис. Условное обозначение элемента и его таблица истинности (возможная)

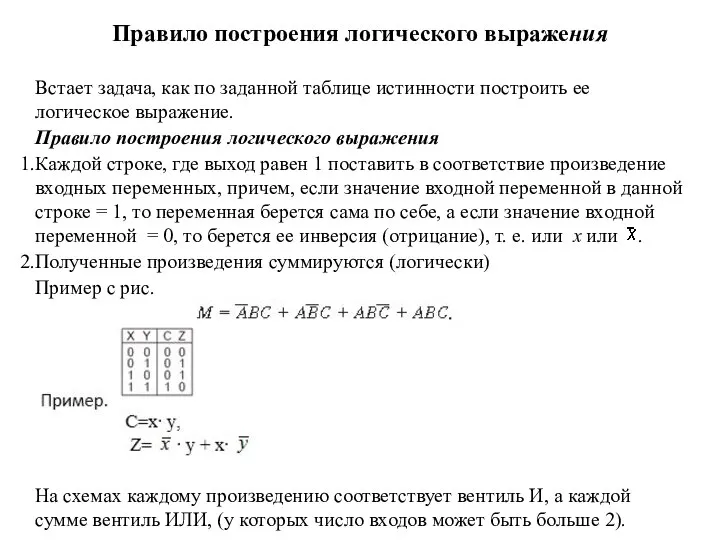

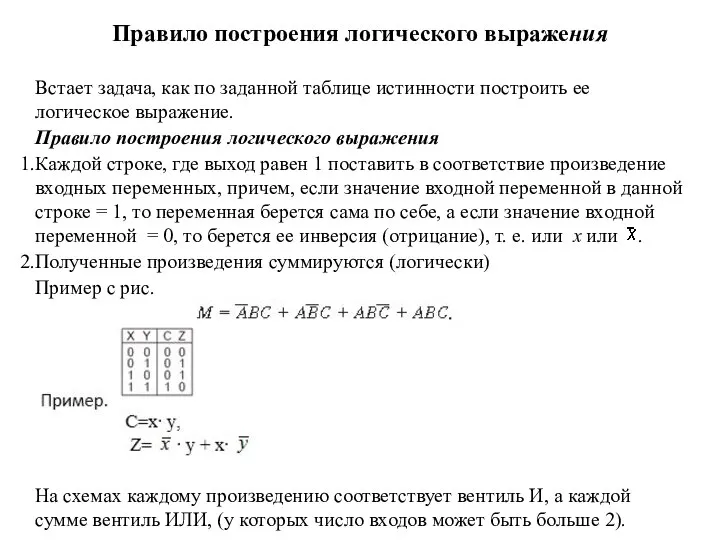

Слайд 13Правило построения логического выражения

Встает задача, как по заданной таблице истинности построить ее

логическое выражение.

Правило построения логического выражения

Каждой строке, где выход равен 1 поставить в соответствие произведение входных переменных, причем, если значение входной переменной в данной строке = 1, то переменная берется сама по себе, а если значение входной переменной = 0, то берется ее инверсия (отрицание), т. е. или х или .

Полученные произведения суммируются (логически)

Пример с рис.

На схемах каждому произведению соответствует вентиль И, а каждой сумме вентиль ИЛИ, (у которых число входов может быть больше 2).

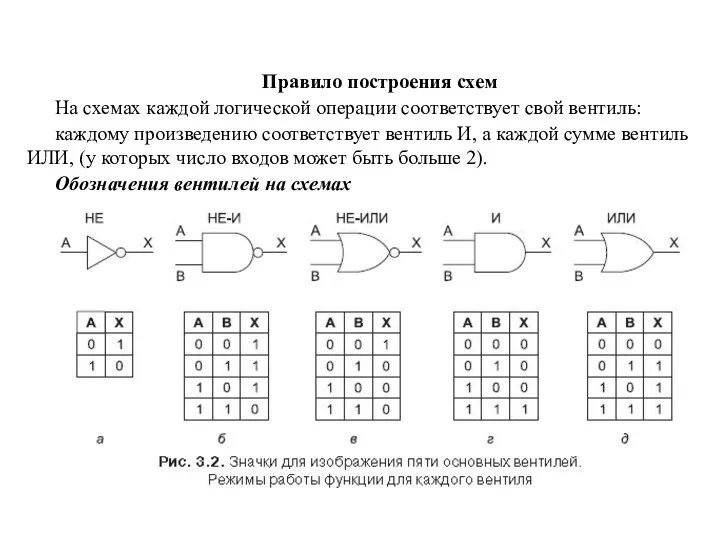

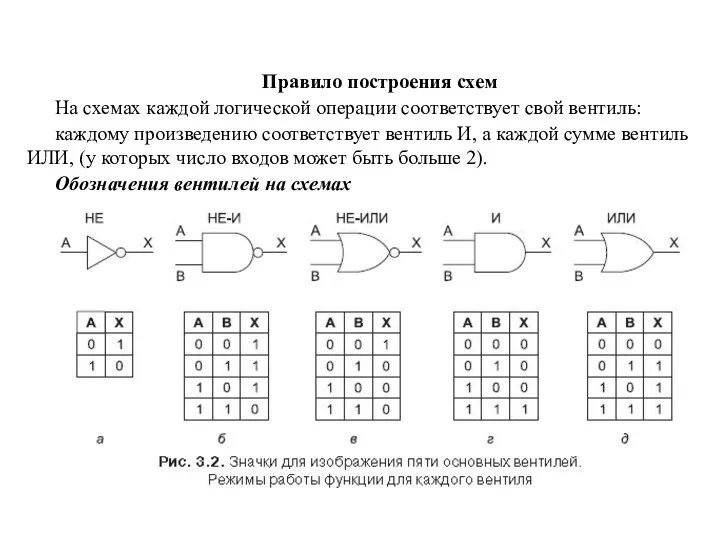

Слайд 14Правило построения схем

На схемах каждой логической операции соответствует свой вентиль:

каждому произведению соответствует

вентиль И, а каждой сумме вентиль ИЛИ, (у которых число входов может быть больше 2).

Обозначения вентилей на схемах

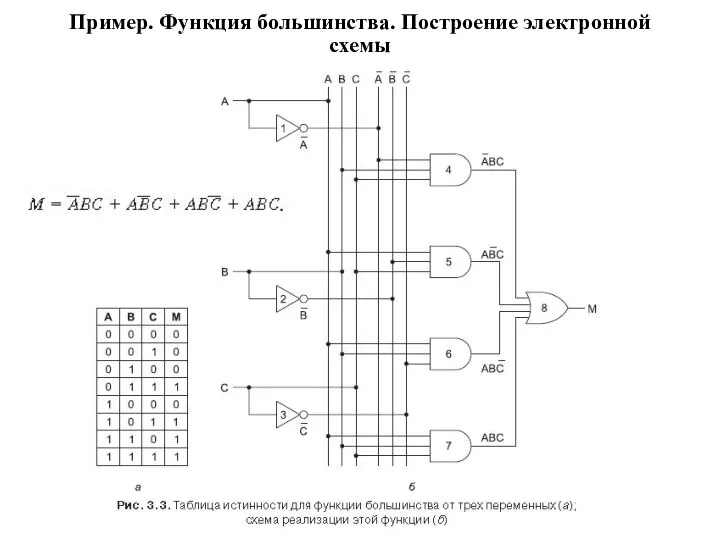

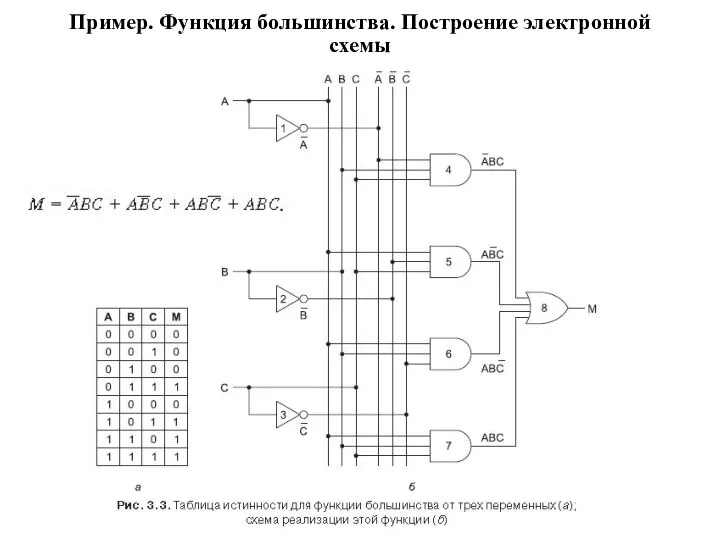

Слайд 15Пример. Функция большинства. Построение электронной схемы

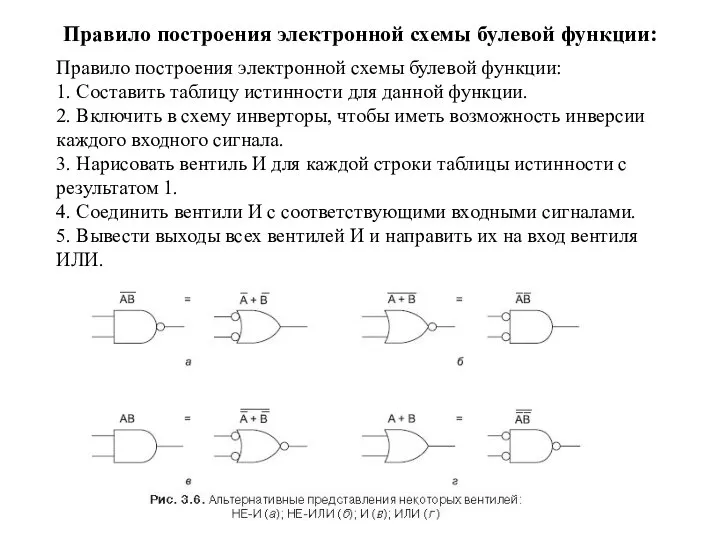

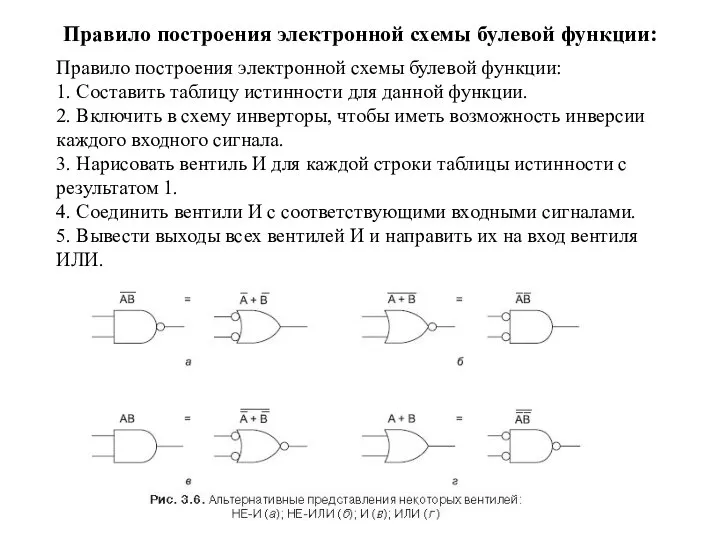

Слайд 16Правило построения электронной схемы булевой функции:

Правило построения электронной схемы булевой функции:

1. Составить

таблицу истинности для данной функции.

2. Включить в схему инверторы, чтобы иметь возможность инверсии каждого входного сигнала.

3. Нарисовать вентиль И для каждой строки таблицы истинности с результатом 1.

4. Соединить вентили И с соответствующими входными сигналами.

5. Вывести выходы всех вентилей И и направить их на вход вентиля ИЛИ.

Слайд 17Основные цифровые логические схемы

Комбинаторные схемы: мультиплексоры, декодеры, компараторы

Арифметические схемы: схемы сдвига, сумматоры

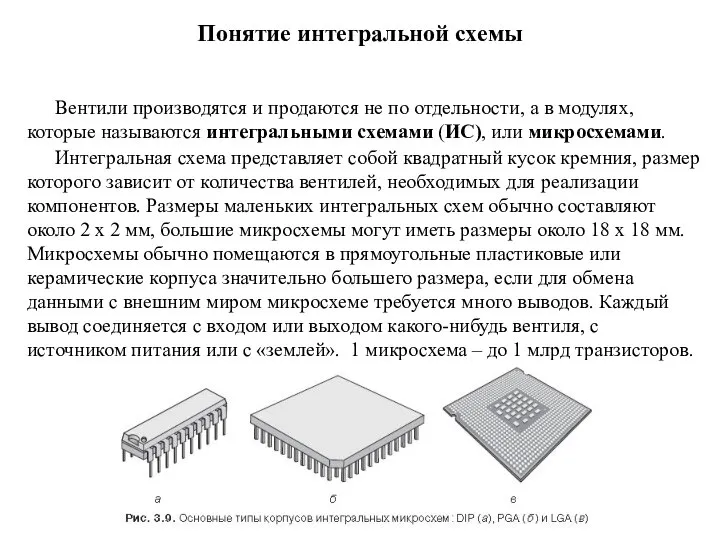

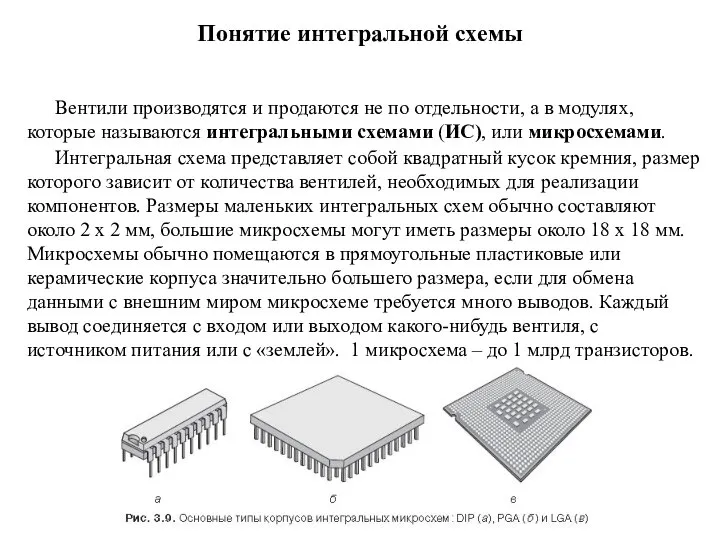

Слайд 18Понятие интегральной схемы

Вентили производятся и продаются не по отдельности, а в модулях,

которые называются интегральными схемами (ИС), или микросхемами.

Интегральная схема представляет собой квадратный кусок кремния, размер которого зависит от количества вентилей, необходимых для реализации компонентов. Размеры маленьких интегральных схем обычно составляют около 2 х 2 мм, большие микросхемы могут иметь размеры около 18 х 18 мм. Микросхемы обычно помещаются в прямоугольные пластиковые или керамические корпуса значительно большего размера, если для обмена данными с внешним миром микросхеме требуется много выводов. Каждый вывод соединяется с входом или выходом какого-нибудь вентиля, с источником питания или с «землей». 1 микросхема – до 1 млрд транзисторов.

Слайд 19Комбинаторные схемы

Многие применения цифровой логики требуют наличия схем с несколькими входами и

несколькими выходами, в которых выходные сигналы определяются текущими входными сигналами. Такая схема называется комбинаторной.

Слайд 20Мультиплексоры

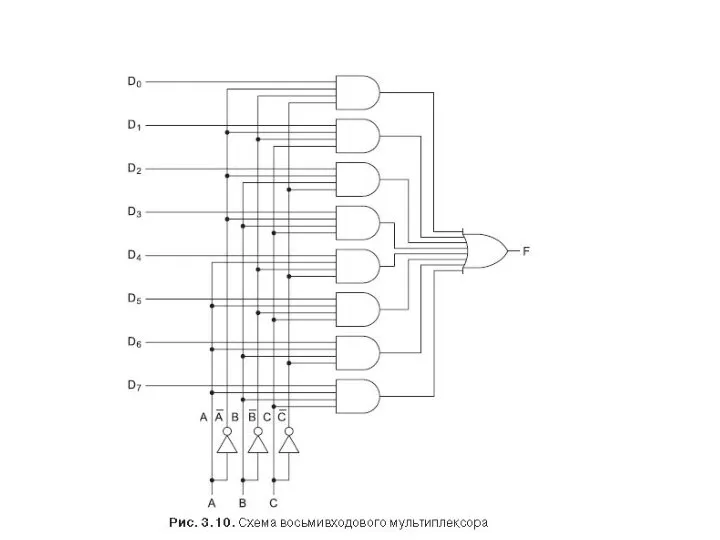

На цифровом логическом уровне мультиплексор представляет собой схему с 2n входами, одним

выходом и n линиями управления, которые позволяют выбрать один из входов. Выбранный вход соединяется с выходом.

На рис. 3.10 изображена схема восьмивходового мультиплексора. Три линии управления A, B и C кодируют 3-разрядное число, которое указывает, какая из восьми входных линий должна соединяться с вентилем ИЛИ и, следовательно, с выходом.

Вне зависимости от того, какое значение окажется на линиях управления, семь вентилей И всегда будут выдавать на выходе 0, а оставшийся может выдавать 0 или 1 в зависимости от значения выбранной линии входа. Каждый вентиль И запускается определенной комбинацией сигналов на линиях управления. Схема мультиплексора показана на рис. 3.10.

Противоположностью мультиплексора является демультиплексор, который соединяет единственный входной сигнал с одним из 2n выходов в зависимости от значений сигналов в n линиях управления. Если бинарное значение линий управления равно k, то выбирается выход k.

Слайд 22Декодеры

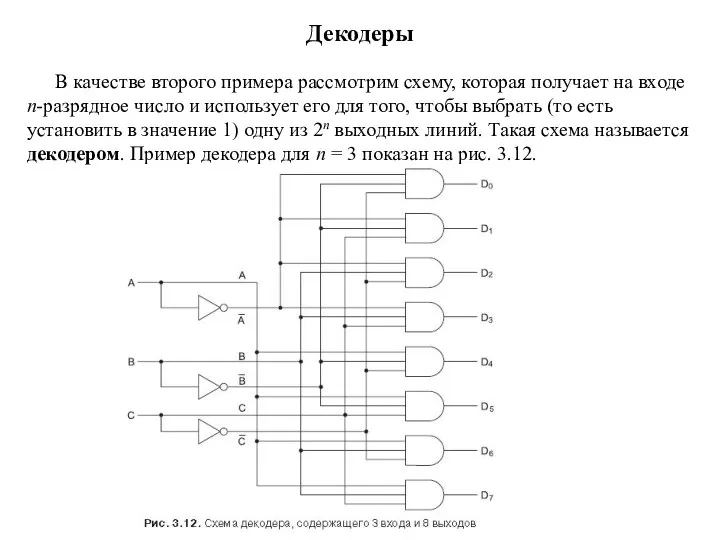

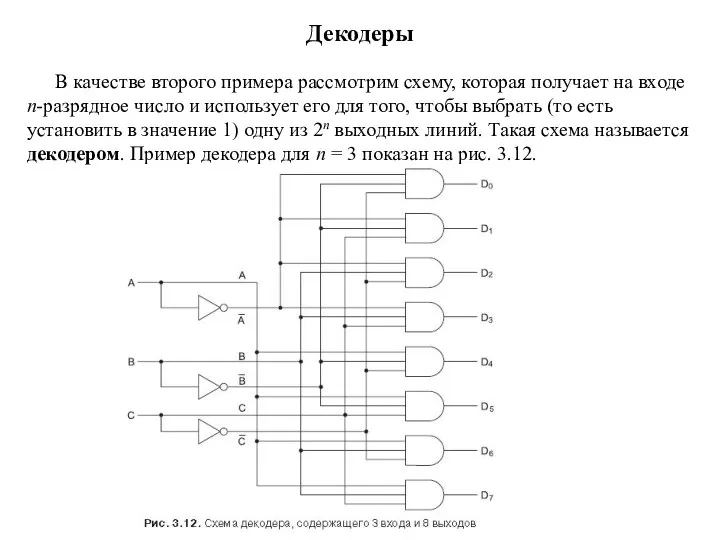

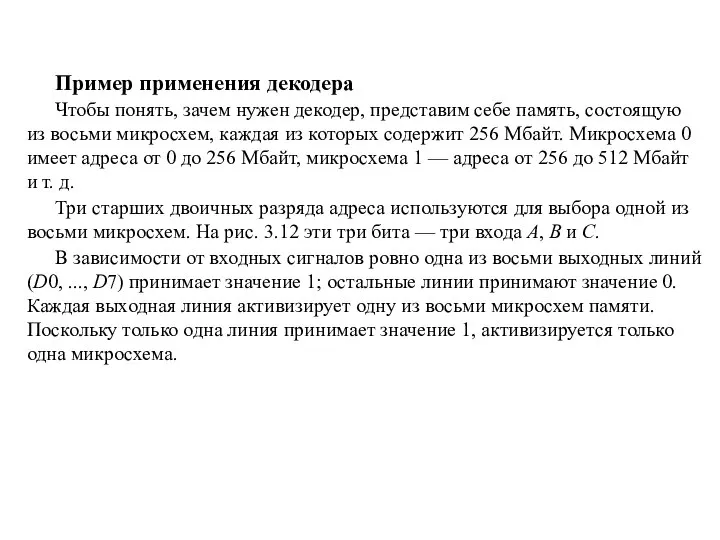

В качестве второго примера рассмотрим схему, которая получает на входе n-разрядное число

и использует его для того, чтобы выбрать (то есть установить в значение 1) одну из 2n выходных линий. Такая схема называется декодером. Пример декодера для n = 3 показан на рис. 3.12.

Слайд 23Пример применения декодера

Чтобы понять, зачем нужен декодер, представим себе память, состоящую из

восьми микросхем, каждая из которых содержит 256 Мбайт. Микросхема 0 имеет адреса от 0 до 256 Мбайт, микросхема 1 — адреса от 256 до 512 Мбайт и т. д.

Три старших двоичных разряда адреса используются для выбора одной из восьми микросхем. На рис. 3.12 эти три бита — три входа A, B и С.

В зависимости от входных сигналов ровно одна из восьми выходных линий (D0, ..., D7) принимает значение 1; остальные линии принимают значение 0. Каждая выходная линия активизирует одну из восьми микросхем памяти. Поскольку только одна линия принимает значение 1, активизируется только одна микросхема.

Слайд 24Компараторы

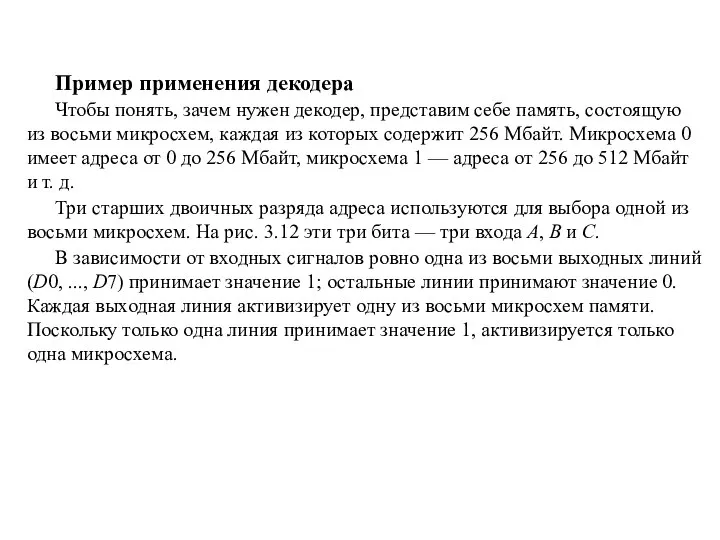

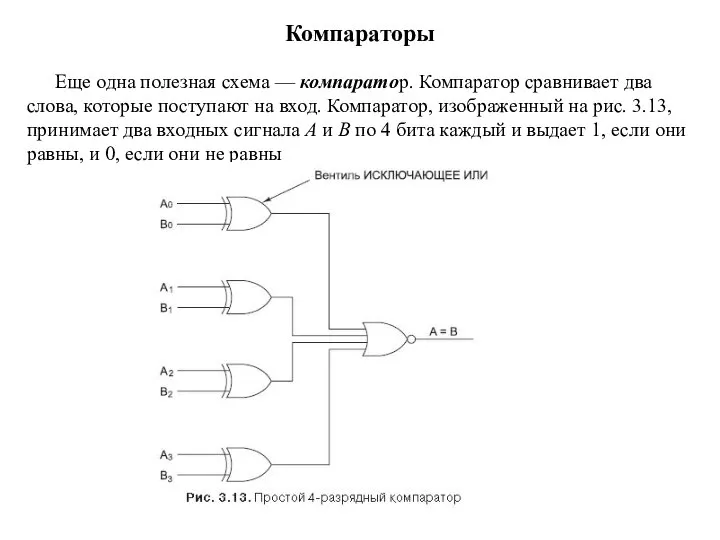

Еще одна полезная схема — компаратор. Компаратор сравнивает два слова, которые поступают

на вход. Компаратор, изображенный на рис. 3.13, принимает два входных сигнала A и B по 4 бита каждый и выдает 1, если они равны, и 0, если они не равны

Слайд 25Арифметические схемы

Схемы, используемые для выполнения арифметических операций не является функцией состояния только

входных сигналов

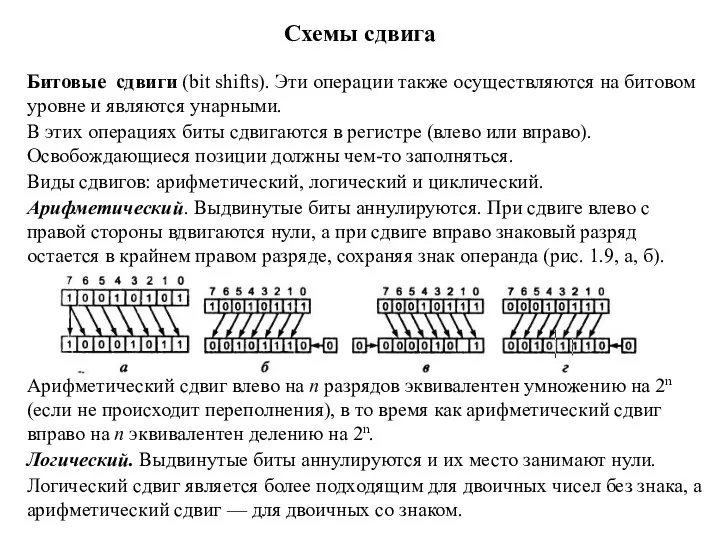

Слайд 26Схемы сдвига

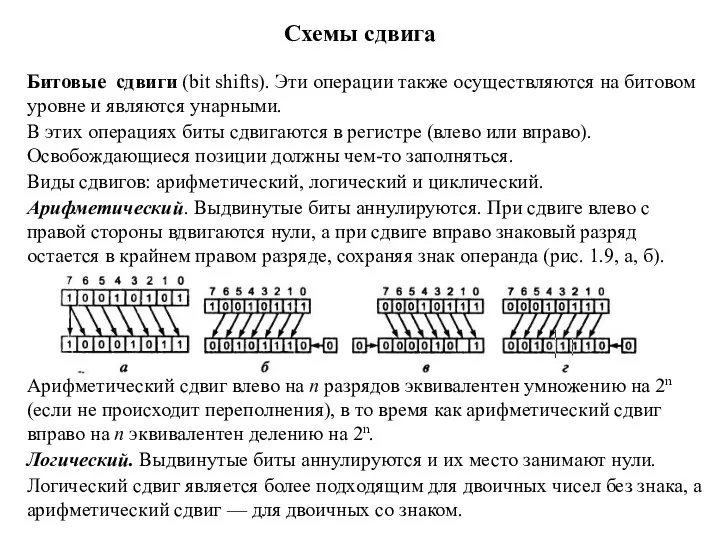

Битовые сдвиги (bit shifts). Эти операции также осуществляются на битовом уровне

и являются унарными.

В этих операциях биты сдвигаются в регистре (влево или вправо). Освобождающиеся позиции должны чем-то заполняться.

Виды сдвигов: арифметический, логический и циклический.

Арифметический. Выдвинутые биты аннулируются. При сдвиге влево с правой стороны вдвигаются нули, а при сдвиге вправо знаковый разряд остается в крайнем правом разряде, сохраняя знак операнда (рис. 1.9, а, б).

Арифметический сдвиг влево на n разрядов эквивалентен умножению на 2n (если не происходит переполнения), в то время как арифметический сдвиг вправо на n эквивалентен делению на 2n.

Логический. Выдвинутые биты аннулируются и их место занимают нули.

Логический сдвиг является более подходящим для двоичных чисел без знака, а арифметический сдвиг — для двоичных со знаком.

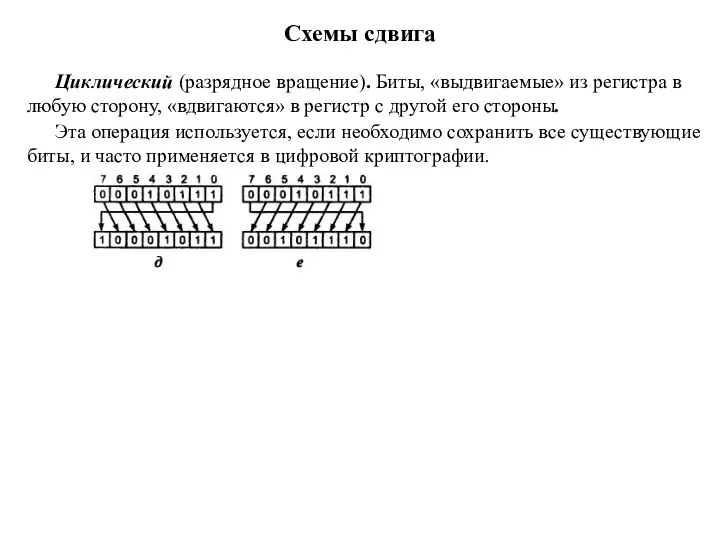

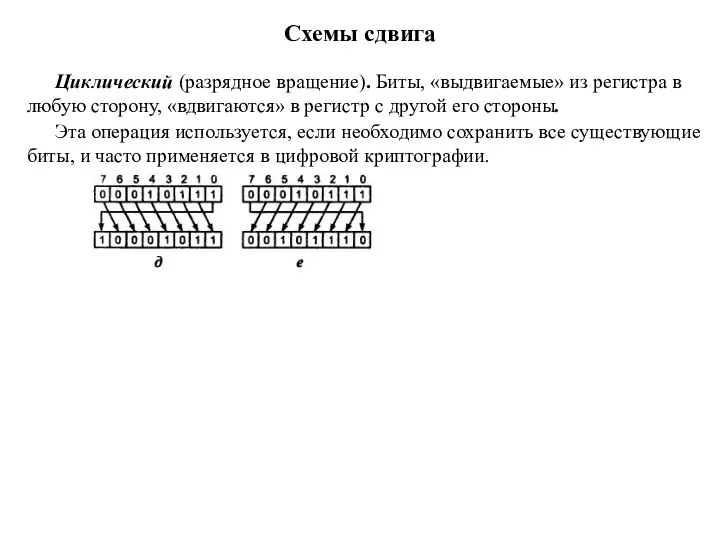

Слайд 27Схемы сдвига

Циклический (разрядное вращение). Биты, «выдвигаемые» из регистра в любую сторону, «вдвигаются»

в регистр с другой его стороны.

Эта операция используется, если необходимо сохранить все существующие биты, и часто применяется в цифровой криптографии.

Слайд 28

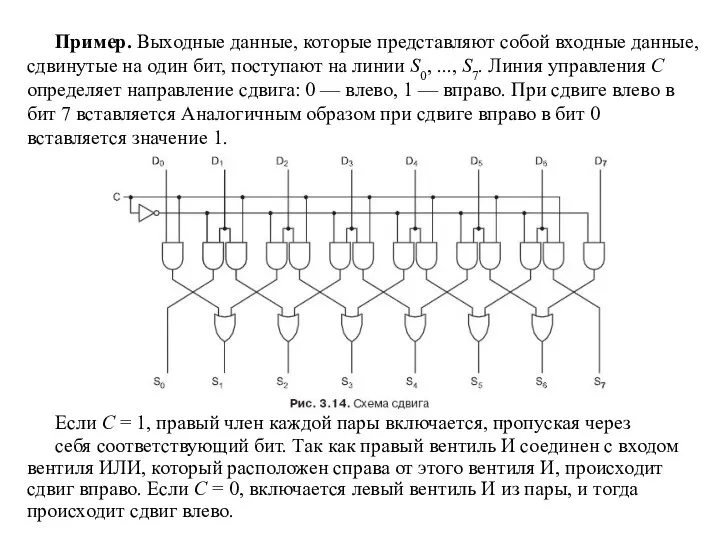

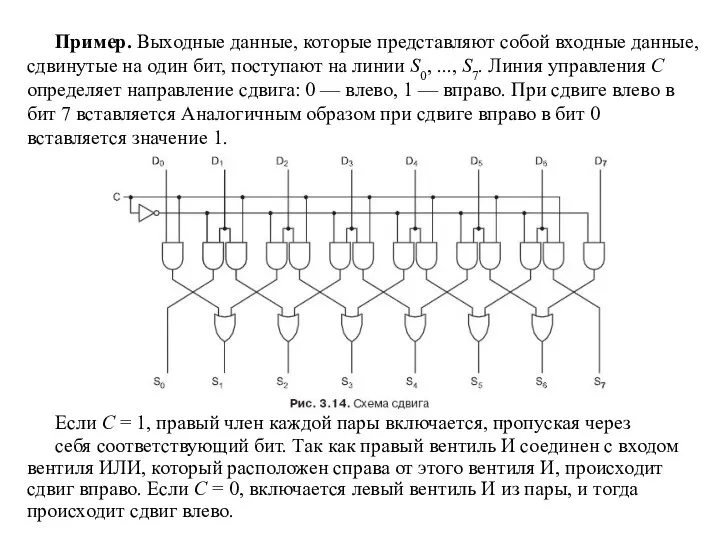

Пример. Выходные данные, которые представляют собой входные данные, сдвинутые на один

бит, поступают на линии S0, ..., S7. Линия управления С определяет направление сдвига: 0 — влево, 1 — вправо. При сдвиге влево в бит 7 вставляется Аналогичным образом при сдвиге вправо в бит 0 вставляется значение 1.

Если С = 1, правый член каждой пары включается, пропуская через

себя соответствующий бит. Так как правый вентиль И соединен с входом вентиля ИЛИ, который расположен справа от этого вентиля И, происходит сдвиг вправо. Если С = 0, включается левый вентиль И из пары, и тогда происходит сдвиг влево.

Слайд 29Сумматоры. Полусумматор

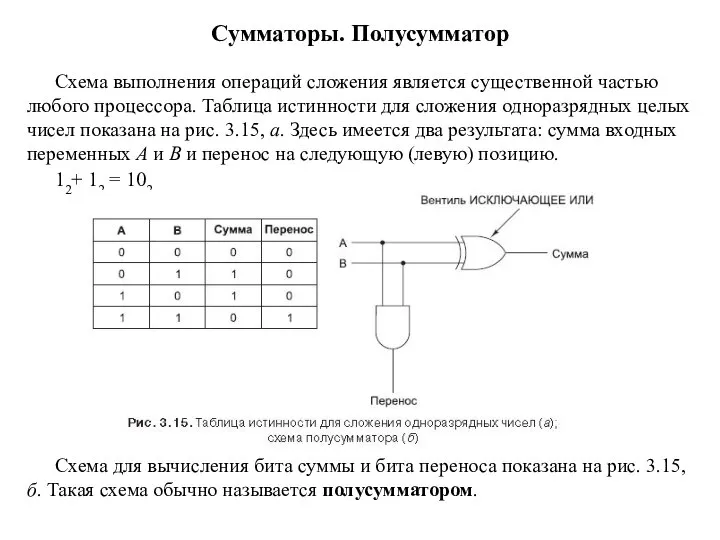

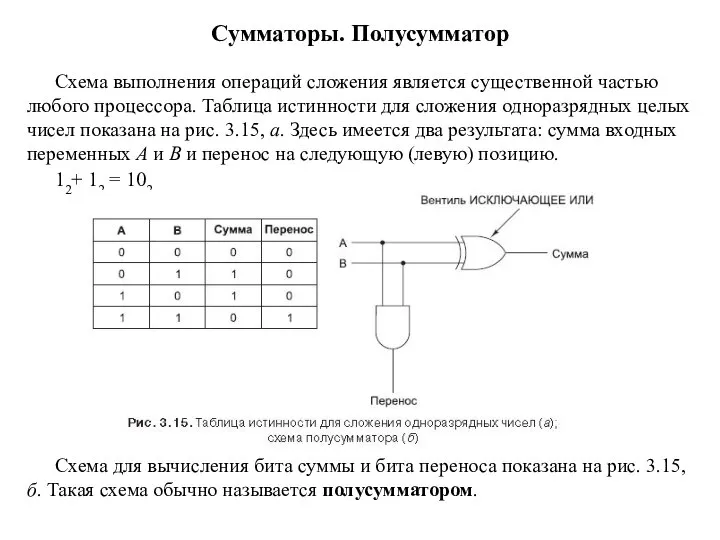

Схема выполнения операций сложения является существенной частью любого процессора. Таблица истинности

для сложения одноразрядных целых чисел показана на рис. 3.15, а. Здесь имеется два результата: сумма входных переменных A и B и перенос на следующую (левую) позицию.

12+ 12 = 102

Схема для вычисления бита суммы и бита переноса показана на рис. 3.15, б. Такая схема обычно называется полусумматором.

Слайд 30Полный сумматор

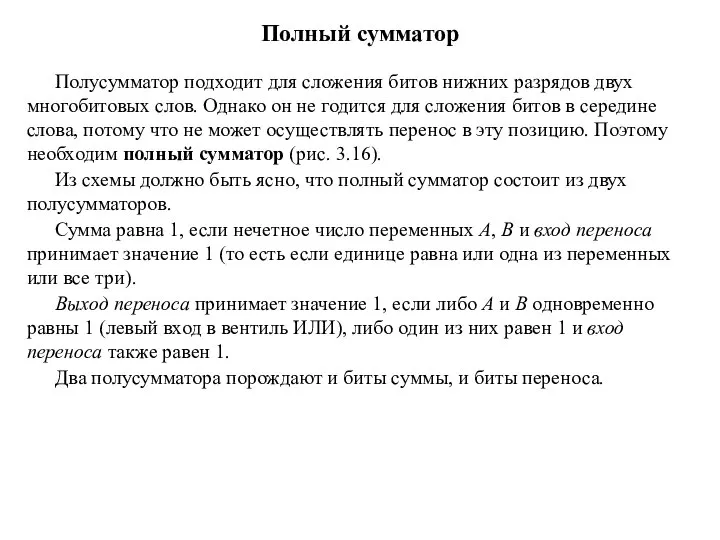

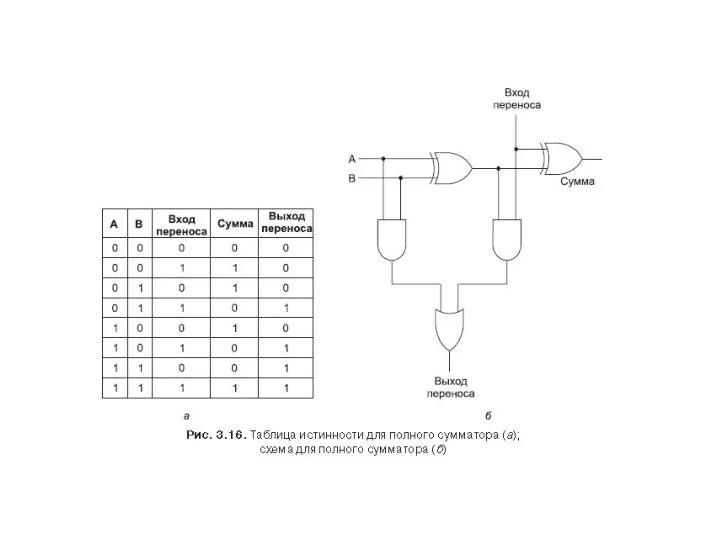

Полусумматор подходит для сложения битов нижних разрядов двух многобитовых слов. Однако

он не годится для сложения битов в середине слова, потому что не может осуществлять перенос в эту позицию. Поэтому необходим полный сумматор (рис. 3.16).

Из схемы должно быть ясно, что полный сумматор состоит из двух полусумматоров.

Сумма равна 1, если нечетное число переменных A, B и вход переноса принимает значение 1 (то есть если единице равна или одна из переменных или все три).

Выход переноса принимает значение 1, если либо А и B одновременно равны 1 (левый вход в вентиль ИЛИ), либо один из них равен 1 и вход переноса также равен 1.

Два полусумматора порождают и биты суммы, и биты переноса.

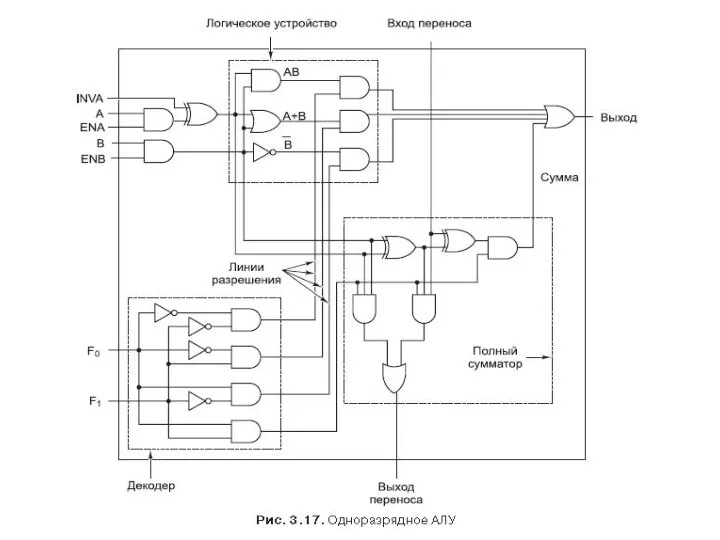

Слайд 32Арифметико-логические устройства

Слайд 33Арифметико-логические устройства

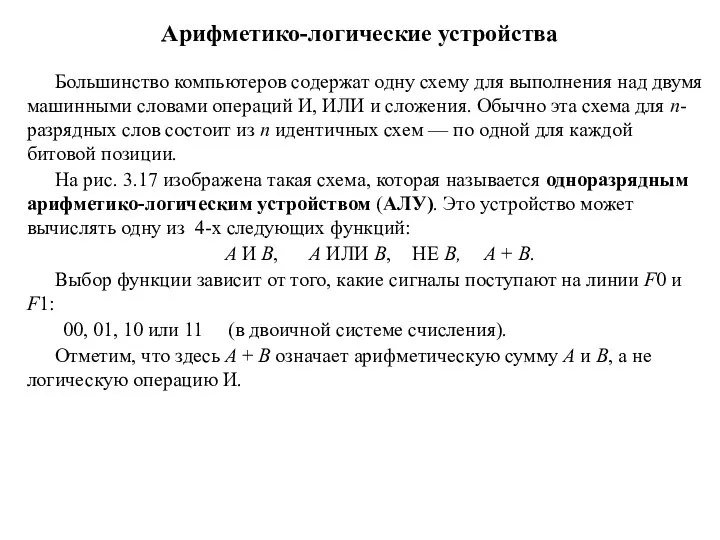

Большинство компьютеров содержат одну схему для выполнения над двумя машинными словами

операций И, ИЛИ и сложения. Обычно эта схема для n-разрядных слов состоит из n идентичных схем — по одной для каждой битовой позиции.

На рис. 3.17 изображена такая схема, которая называется одноразрядным арифметико-логическим устройством (АЛУ). Это устройство может вычислять одну из 4-х следующих функций:

A И B, A ИЛИ B, НЕ B, A + B.

Выбор функции зависит от того, какие сигналы поступают на линии F0 и F1:

00, 01, 10 или 11 (в двоичной системе счисления).

Отметим, что здесь A + B означает арифметическую сумму A и B, а не логическую операцию И.

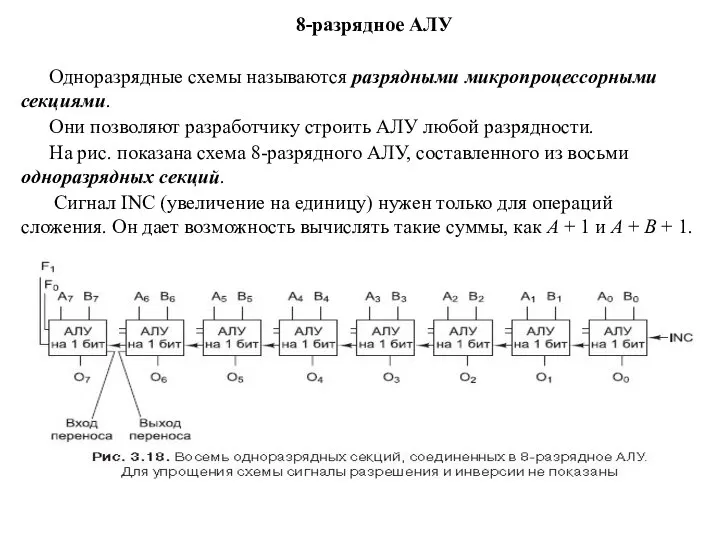

Слайд 358-разрядное АЛУ

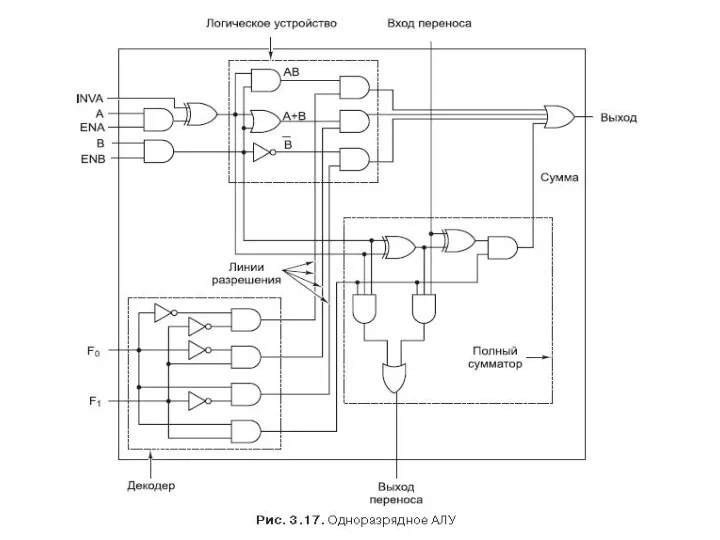

Одноразрядные схемы называются разрядными микропроцессорными секциями.

Они позволяют разработчику строить АЛУ

любой разрядности.

На рис. показана схема 8-разрядного АЛУ, составленного из восьми одноразрядных секций.

Сигнал INC (увеличение на единицу) нужен только для операций сложения. Он дает возможность вычислять такие суммы, как А + 1 и А + В + 1.

Слайд 37Тактовые генераторы

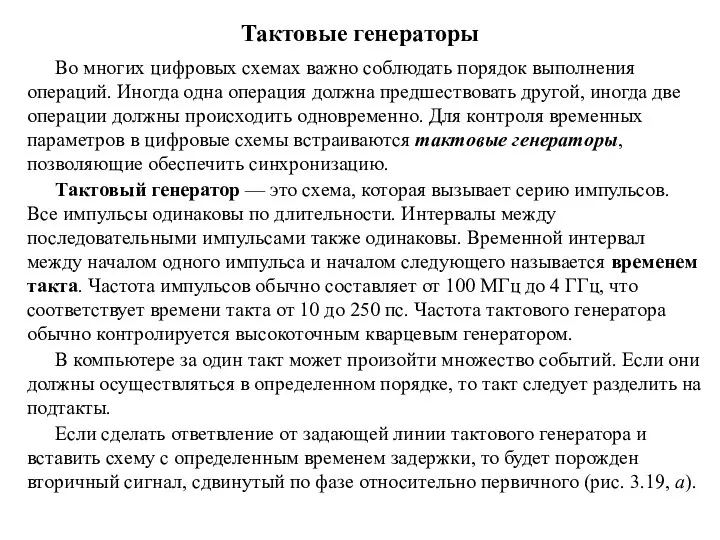

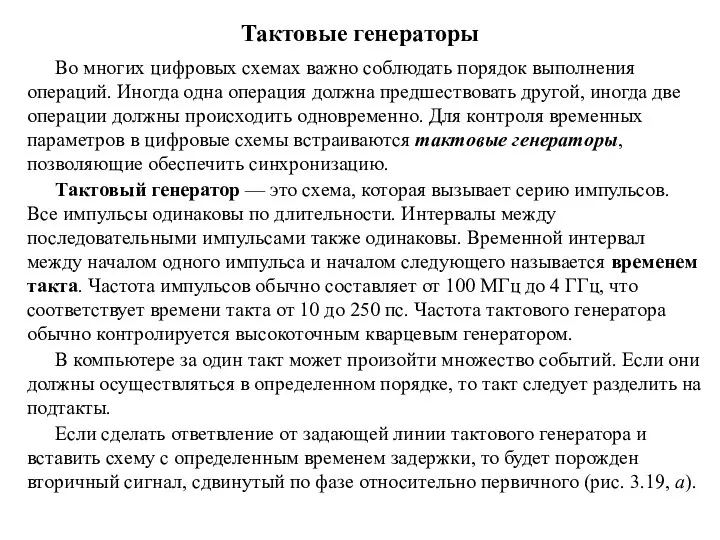

Во многих цифровых схемах важно соблюдать порядок выполнения операций. Иногда одна

операция должна предшествовать другой, иногда две операции должны происходить одновременно. Для контроля временных параметров в цифровые схемы встраиваются тактовые генераторы, позволяющие обеспечить синхронизацию.

Тактовый генератор — это схема, которая вызывает серию импульсов. Все импульсы одинаковы по длительности. Интервалы между последовательными импульсами также одинаковы. Временной интервал между началом одного импульса и началом следующего называется временем такта. Частота импульсов обычно составляет от 100 МГц до 4 ГГц, что соответствует времени такта от 10 до 250 пс. Частота тактового генератора обычно контролируется высокоточным кварцевым генератором.

В компьютере за один такт может произойти множество событий. Если они должны осуществляться в определенном порядке, то такт следует разделить на подтакты.

Если сделать ответвление от задающей линии тактового генератора и вставить схему с определенным временем задержки, то будет порожден вторичный сигнал, сдвинутый по фазе относительно первичного (рис. 3.19, а).

Слайд 38

Временная диаграмма, показанная на рис. 3.19, б, предлагает четыре точки начала отсчета

времени для дискретных событий:

1. Фронт С1.

2. Спад С1.

3. Фронт С2.

4. Спад С2.

Связав различные события с разными перепадами (фронтами и спадами), можно достичь требуемой последовательности выполнения действий.

Слайд 39Память

Память является необходимым компонентом любого компьютера. Без памяти не было бы компьютеров,

по крайней мере таких, какие есть сейчас. Память используется для хранения как команд, так и данных.

Память строится на таких элементах, как защелки и триггеры.

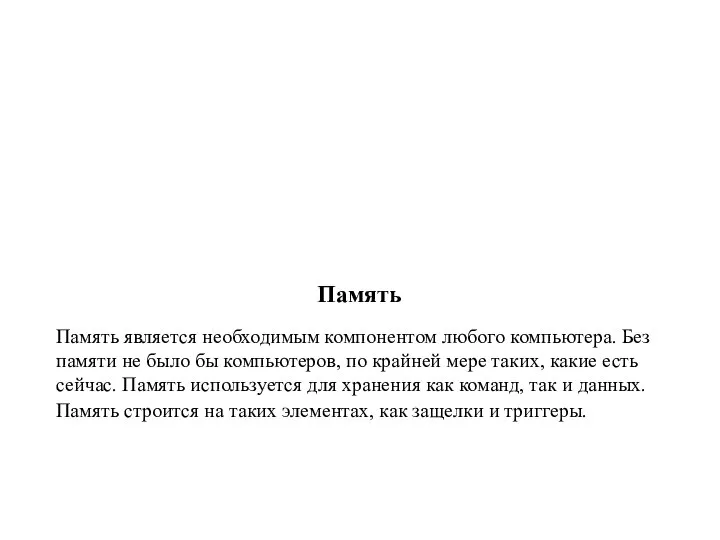

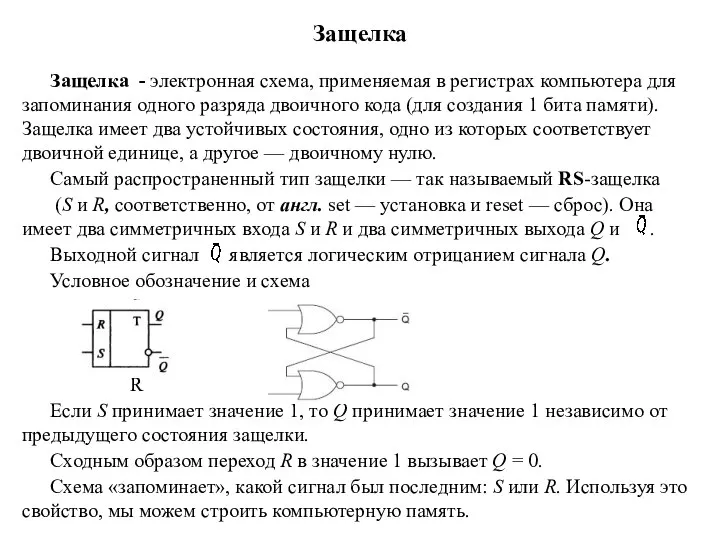

Слайд 40Защелка

Защелка - электронная схема, применяемая в регистрах компьютера для запоминания одного разряда

двоичного кода (для создания 1 бита памяти). Защелка имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю.

Самый распространенный тип защелки — так называемый RS-защелка

(S и R, соответственно, от англ. set — установка и reset — сброс). Она имеет два симметричных входа S и R и два симметричных выхода Q и .

Выходной сигнал является логическим отрицанием сигнала Q.

Условное обозначение и схема

S

R

Если S принимает значение 1, то Q принимает значение 1 независимо от предыдущего состояния защелки.

Сходным образом переход R в значение 1 вызывает Q = 0.

Схема «запоминает», какой сигнал был последним: S или R. Используя это свойство, мы можем строить компьютерную память.

Слайд 41Синхронные SR-защелки

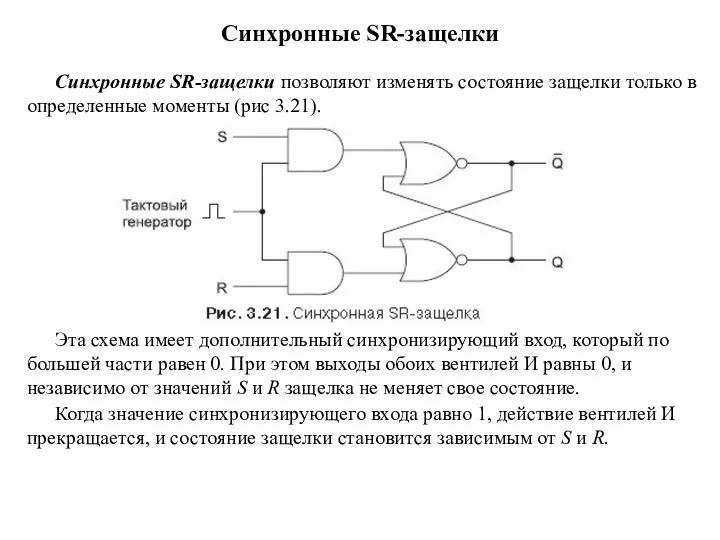

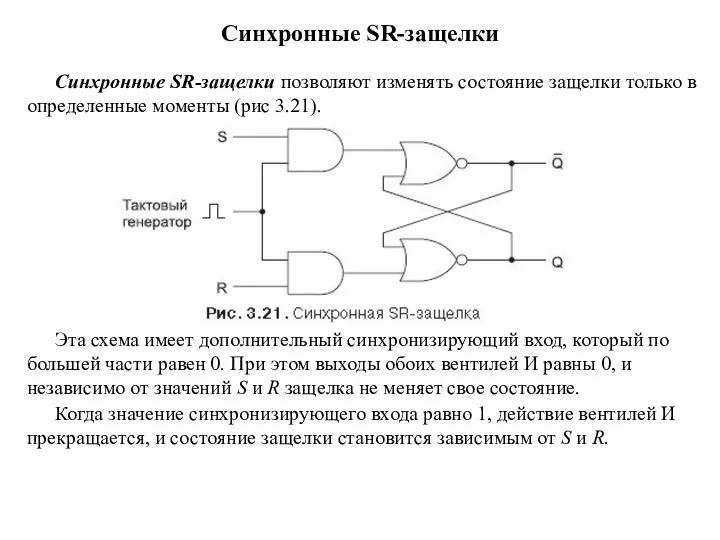

Синхронные SR-защелки позволяют изменять состояние защелки только в определенные моменты (рис

3.21).

Эта схема имеет дополнительный синхронизирующий вход, который по большей части равен 0. При этом выходы обоих вентилей И равны 0, и независимо от значений S и R защелка не меняет свое состояние.

Когда значение синхронизирующего входа равно 1, действие вентилей И прекращается, и состояние защелки становится зависимым от S и R.

Слайд 42Синхронные D-защелки

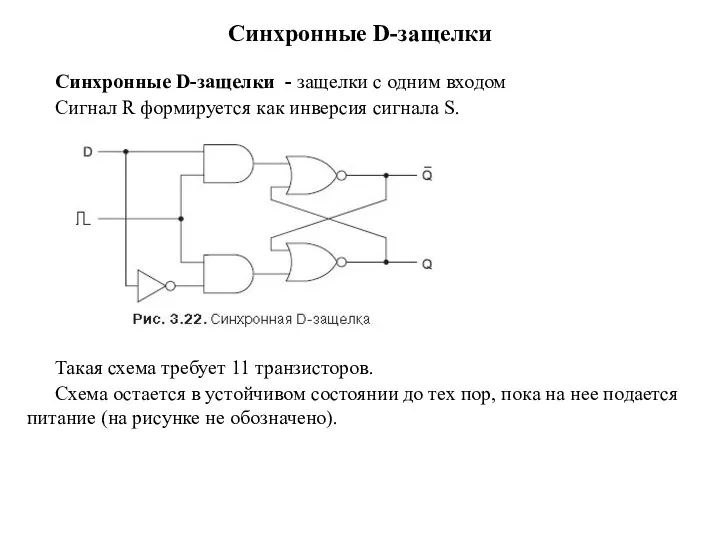

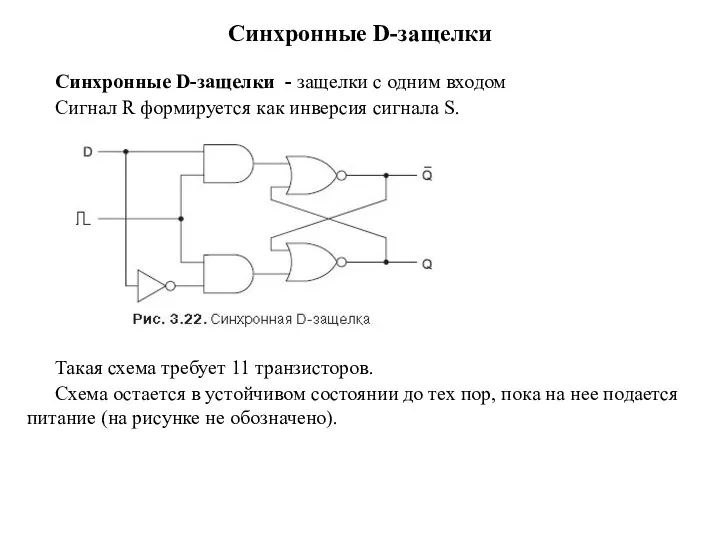

Синхронные D-защелки - защелки с одним входом

Сигнал R формируется как инверсия

сигнала S.

Такая схема требует 11 транзисторов.

Схема остается в устойчивом состоянии до тех пор, пока на нее подается питание (на рисунке не обозначено).

Слайд 43Триггеры

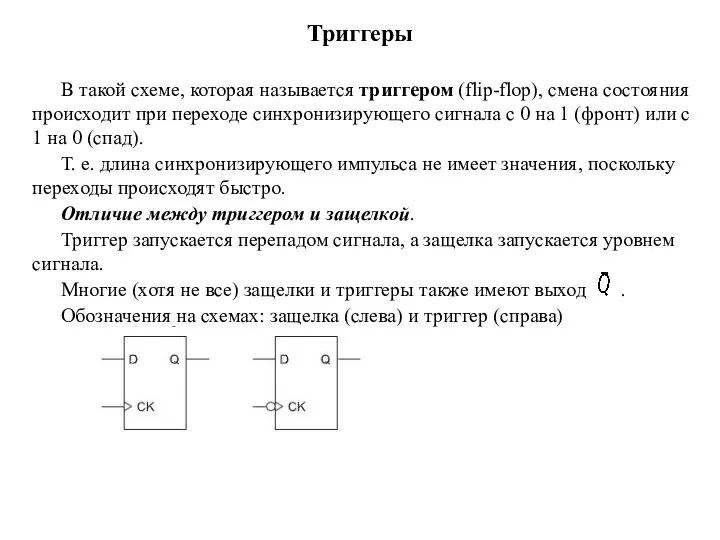

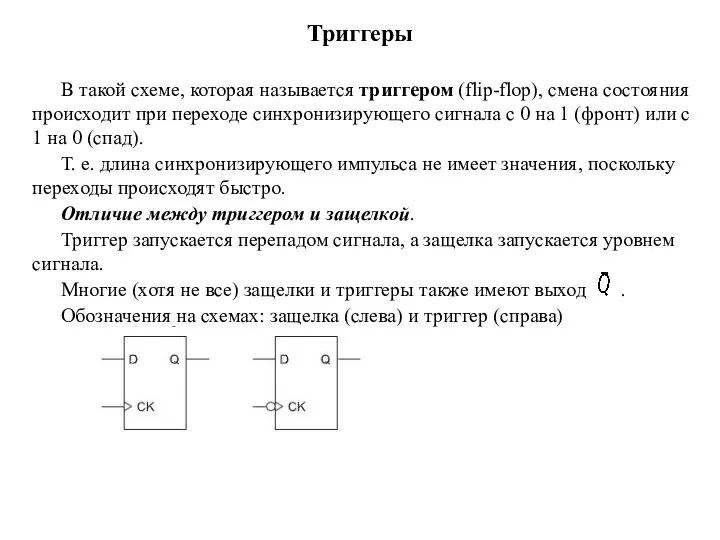

В такой схеме, которая называется триггером (flip-flop), смена состояния происходит при переходе

синхронизирующего сигнала с 0 на 1 (фронт) или с 1 на 0 (спад).

Т. е. длина синхронизирующего импульса не имеет значения, поскольку переходы происходят быстро.

Отличие между триггером и защелкой.

Триггер запускается перепадом сигнала, а защелка запускается уровнем сигнала.

Многие (хотя не все) защелки и триггеры также имеют выход .

Обозначения на схемах: защелка (слева) и триггер (справа)

Слайд 44Регистры

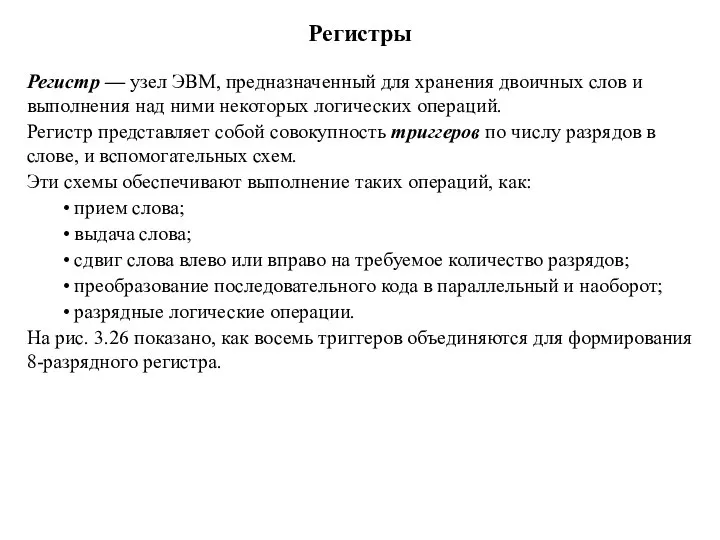

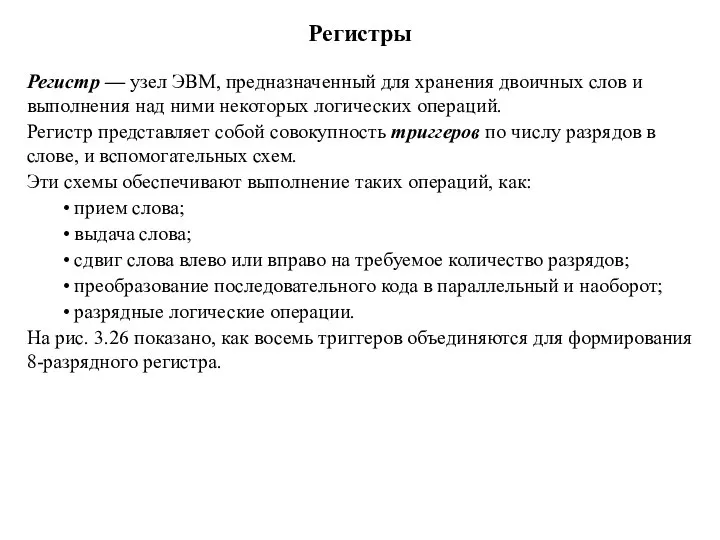

Регистр — узел ЭВМ, предназначенный для хранения двоичных слов и выполнения над

ними некоторых логических операций.

Регистр представляет собой совокупность триггеров по числу разрядов в слове, и вспомогательных схем.

Эти схемы обеспечивают выполнение таких операций, как:

• прием слова;

• выдача слова;

• сдвиг слова влево или вправо на требуемое количество разрядов;

• преобразование последовательного кода в параллельный и наоборот;

• разрядные логические операции.

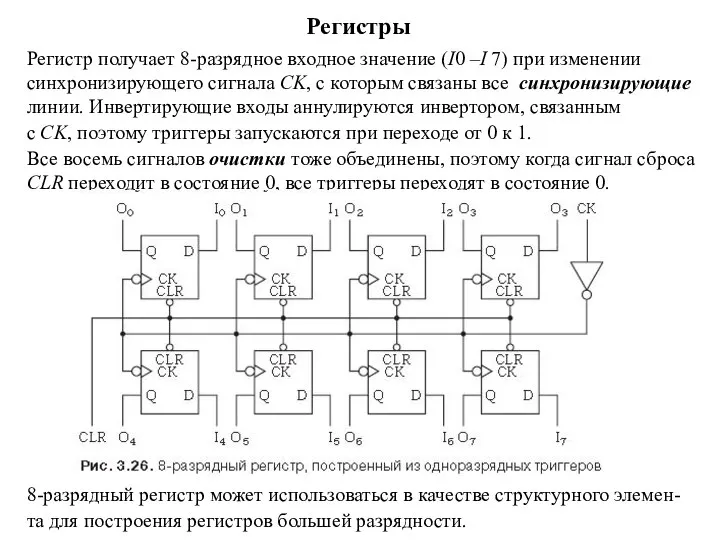

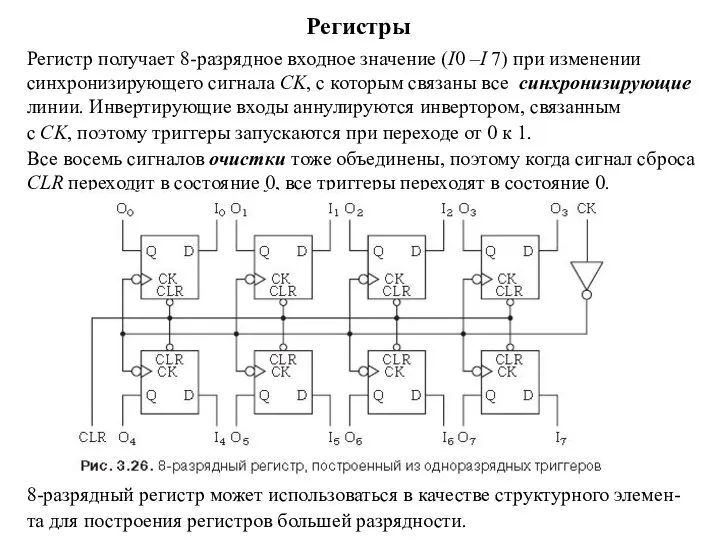

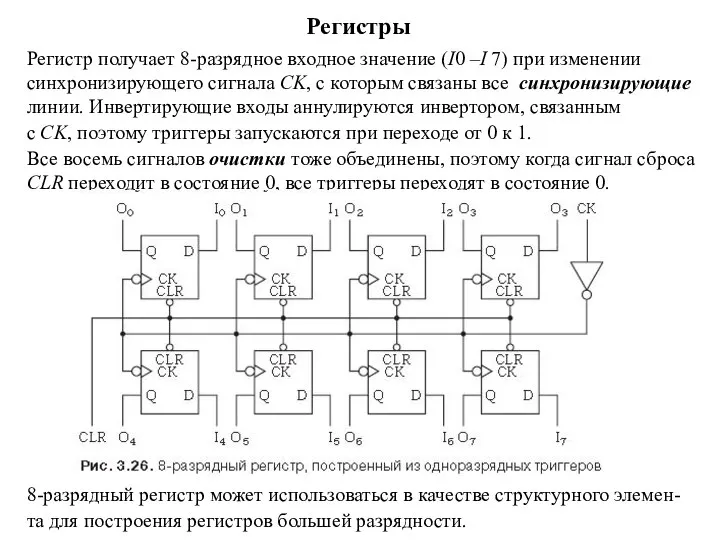

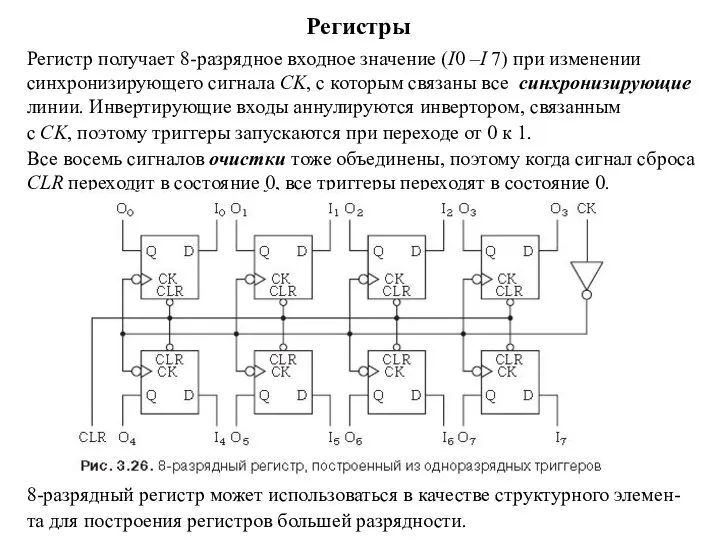

На рис. 3.26 показано, как восемь триггеров объединяются для формирования 8-разрядного регистра.

Слайд 45Регистры

Регистр получает 8-разрядное входное значение (I0 –I 7) при изменении синхронизирующего сигнала

CK, с которым связаны все синхронизирующие линии. Инвертирующие входы аннулируются инвертором, связанным

с CK, поэтому триггеры запускаются при переходе от 0 к 1.

Все восемь сигналов очистки тоже объединены, поэтому когда сигнал сброса CLR переходит в состояние 0, все триггеры переходят в состояние 0.

8-разрядный регистр может использоваться в качестве структурного элемен-

та для построения регистров большей разрядности.

Слайд 46Регистры

Регистр получает 8-разрядное входное значение (I0 –I 7) при изменении синхронизирующего сигнала

CK, с которым связаны все синхронизирующие линии. Инвертирующие входы аннулируются инвертором, связанным

с CK, поэтому триггеры запускаются при переходе от 0 к 1.

Все восемь сигналов очистки тоже объединены, поэтому когда сигнал сброса CLR переходит в состояние 0, все триггеры переходят в состояние 0.

8-разрядный регистр может использоваться в качестве структурного элемен-

та для построения регистров большей разрядности.

Слайд 47Виды памяти компьютера

Непосредственно в компьютере используются два вида электронной памяти ОЗУ и

ПЗУ.

Память ОЗУ (оперативное запоминающее устройство), или RAM (Random Access Memory — оперативная память) позволяет и записывать, и считывать информацию. Ее назначение хранить программу и данные в процессе выполнения программы.

ПЗУ (постоянное запоминающее устройство), или ROM (Read-Only Memory — постоянная память).

Существует два типа ОЗУ: статическое и динамическое.

Слайд 48ОЗУ

Существует два типа ОЗУ: статическое и динамическое.

Статическое ОЗУ (Static RAM, SRAM)

конструируется с использованием D-триггеров. Информация в ОЗУ сохраняется на протяжении всего времени, пока к нему подается питание: секунды, минуты, часы и даже дни. Статическое ОЗУ работает очень быстро. Обычно время доступа составляет несколько наносекунд. По этой причине статическое ОЗУ часто используется в качестве кэш-памяти второго уровня.

В динамическом ОЗУ (Dynamic RAM, DRAM), напротив, триггеры не используются. Динамическое ОЗУ представляет собой массив ячеек, каждая из которых содержит транзистор и крошечный конденсатор. Конденсаторы могут быть заряженными и разряженными, что позволяет хранить нули и единицы. Поскольку электрический заряд имеет тенденцию исчезать, каждый бит в динамическом ОЗУ должен обновляться (перезаряжаться) каждые несколько миллисекунд, чтобы предотвратить утечку данных.

В современных компьютерах сочетание кэшпамяти на основе статического ОЗУ и основной памяти на основе динамического ОЗУ соединяет в себе преимущества обоих устройств.

Слайд 49ПЗУ

Первоначально ПЗУ не позволяли изменять и стирать хранящуюся в них информацию (ни

умышленно, ни случайно). Данные записываются в ПЗУ в процессе производства. Для этого изготавливается трафарет с определенным набором битов, который накладывается на фоточувствительный материал, а затем открытые (или закрытые) части поверхности вытравливаются.

Единственный способ изменить программу в ПЗУ — поменять всю микросхему.

Слайд 50 Флэш-память

Флэш-память - современный тип электронно перепрограммируемого ПЗУ.

Флэш-память образуется из множества твердотельных

ячеек, состоящих из одного специального флэш-транзистора.

Флэш-память стирается и записывается блоками.

Они используются для хранения изображений в цифровых камерах и для других целей.

В настоящее время флэш-память начинает вытеснять магнитные диски в качестве внешнего накопителя, учитывая время доступа в 50 нс.

Флэш-память обеспечивает лучшее время доступа при более низком энергопотреблении; с другой стороны, стоимость одного бита флэш-памяти существенно выше, чем у дисков.

Слайд 51Резюме

Компьютеры собираются из интегральных схем, содержащих крошечные переключатели, которые называются вентилями. Обычно

используются вентили И, ИЛИ, НЕ-И, НЕ-ИЛИ и НЕ. Комбинируя отдельные вентили, можно строить простые схемы.

Более сложными схемами являются мультиплексоры, демультиплексоры, кодеры, декодеры, схемы сдвига и АЛУ. С помощью программируемой вентильной матрицы (FPGA) можно запрограммировать произвольные булевы функции. Если требуется много булевых функций, программируемые логические матрицы обычно более эффективны, чем другие средства. Для преобразования схем из одной формы в другую используются законы булевой алгебры. Во многих случаях это позволяет создать более экономичные схемы.

Арифметические действия в компьютерах осуществляются сумматорами. Одноразрядный полный сумматор можно сконструировать из двух полусумматоров. Чтобы построить сумматор для многоразрядных слов, полные сумматоры соединяются таким образом, чтобы выходной сигнал переноса каждого сумматора передавался его левому соседу.

Слайд 52Резюме

Статическая память состоит из защелок и триггеров, каждый из которых может хранить

один бит информации. Их можно объединять, получая восьмиразрядные триггеры и защелки или готовую память для хранения слов. Существуют различные типы памяти: ОЗУ, ПЗУ, флэш-память.

Статическое ОЗУ не нужно обновлять: оно хранит информацию, пока включен компьютер. Динамическое ОЗУ, напротив, нужно периодически обновлять, чтобы предотвратить потерю информации.

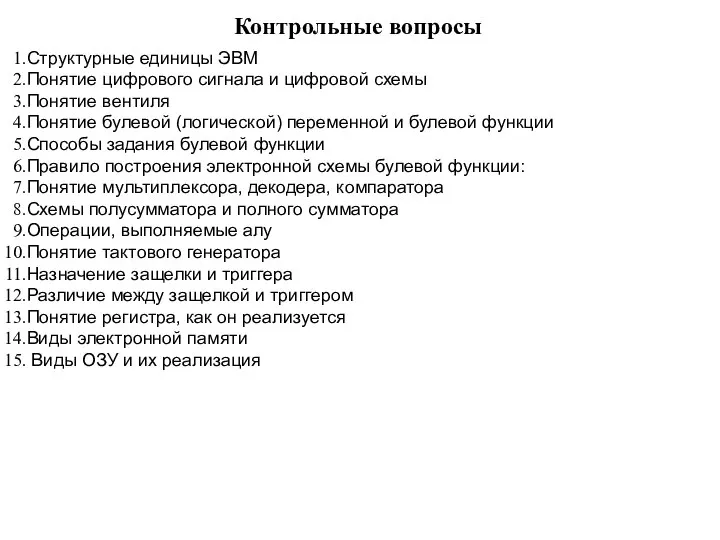

Слайд 53Контрольные вопросы

Структурные единицы ЭВМ

Понятие цифрового сигнала и цифровой схемы

Понятие вентиля

Понятие булевой (логической)

переменной и булевой функции

Способы задания булевой функции

Правило построения электронной схемы булевой функции:

Понятие мультиплексора, декодера, компаратора

Схемы полусумматора и полного сумматора

Операции, выполняемые алу

Понятие тактового генератора

Назначение защелки и триггера

Различие между защелкой и триггером

Понятие регистра, как он реализуется

Виды электронной памяти

Виды ОЗУ и их реализация

Разделение и предварительный просмотр чеков

Разделение и предварительный просмотр чеков Screenshots for wc lp

Screenshots for wc lp Создание презентации к урокам

Создание презентации к урокам Задание Access

Задание Access Комп'ютерні віруси та антивірусний захист

Комп'ютерні віруси та антивірусний захист Структура как пользовательский тип и совокупность данных

Структура как пользовательский тип и совокупность данных Технология хранения, обработки числовой информации

Технология хранения, обработки числовой информации Создание с помощью компьютера схем для вязания

Создание с помощью компьютера схем для вязания Системы счисления

Системы счисления Классификация компьютерной графики. Сравнительные характеристики различных графических сред

Классификация компьютерной графики. Сравнительные характеристики различных графических сред Драйвер. Общая схема взаимодействия пользователя с компьютером

Драйвер. Общая схема взаимодействия пользователя с компьютером Поиск записей в табличной базе данных с помощью фильтров

Поиск записей в табличной базе данных с помощью фильтров Отчет о профессионально-творческой практике в Первичной профсоюзной организации

Отчет о профессионально-творческой практике в Первичной профсоюзной организации Оформление списка источников и литературы в исследовательской работе

Оформление списка источников и литературы в исследовательской работе Этапы решения задач на компьютере

Этапы решения задач на компьютере Сортировка массивов

Сортировка массивов Использование компьютера в сфере Торговля

Использование компьютера в сфере Торговля Собчак. Выборы 2018

Собчак. Выборы 2018 Язык разметки гипертекста HTML

Язык разметки гипертекста HTML Оформление проектов

Оформление проектов Архитектура компьютера. Своя игра

Архитектура компьютера. Своя игра Канал https://www.youtube.com/wat ch?v=FhMOcFGyQas&t=20s

Канал https://www.youtube.com/wat ch?v=FhMOcFGyQas&t=20s Презентация на тему Суперкомпьютеры

Презентация на тему Суперкомпьютеры  Sist_schislen_perevody_8_klass_urok_6_prezentats_18_10_22 (2)

Sist_schislen_perevody_8_klass_urok_6_prezentats_18_10_22 (2) Деректер қоры

Деректер қоры Метаданные. Базы данных Встреча 10

Метаданные. Базы данных Встреча 10 Текстовый процессор Writer

Текстовый процессор Writer Кодирование и шифрование данных

Кодирование и шифрование данных