Содержание

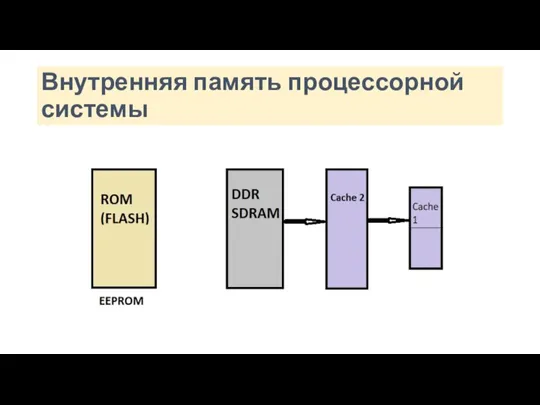

- 2. Внутренняя память процессорной системы

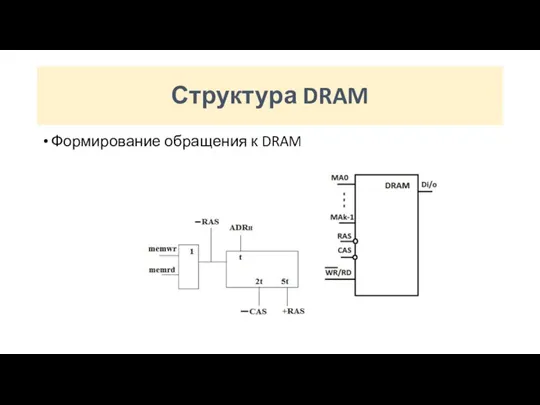

- 3. Структура DRAM Формирование обращения к DRAM

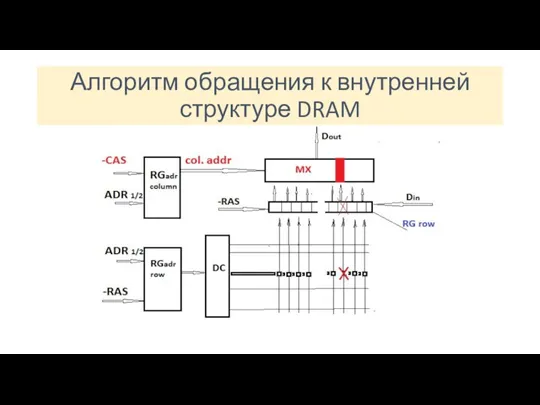

- 4. Алгоритм обращения к внутренней структуре DRAM

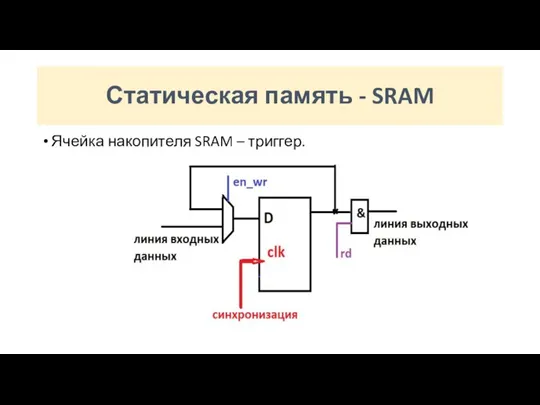

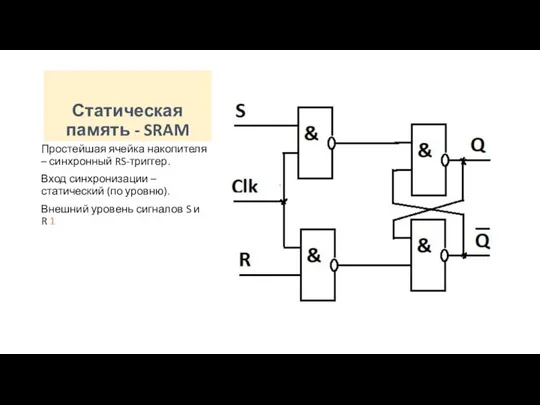

- 5. Статическая память - SRAM Ячейка накопителя SRAM – триггер.

- 6. Простейшая ячейка накопителя – синхронный RS-триггер. Вход синхронизации – статический (по уровню). Внешний уровень сигналов S

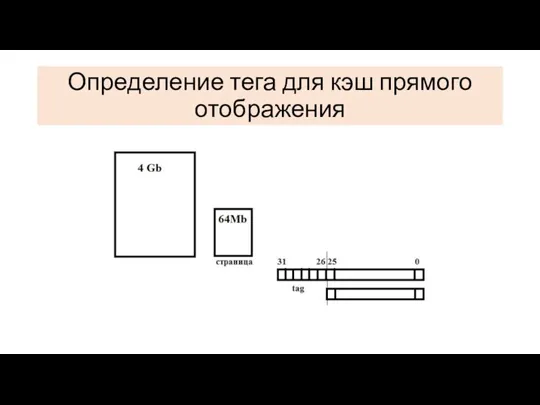

- 7. Определение тега для кэш прямого отображения

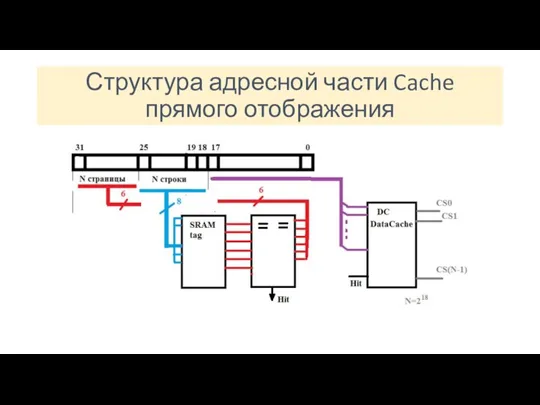

- 8. Структура адресной части Cache прямого отображения

- 9. Преобразование памяти

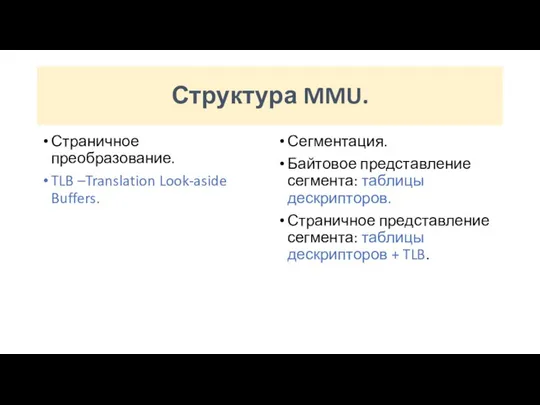

- 10. Структура MMU. Страничное преобразование. TLB –Translation Look-aside Buffers. Сегментация. Байтовое представление сегмента: таблицы дескрипторов. Страничное представление

- 12. Скачать презентацию

О компании НПО Криста

О компании НПО Криста Презентация на тему Блок питания ПК

Презентация на тему Блок питания ПК  Школа::Кода Основы программирования на языке Python. 7 занятие

Школа::Кода Основы программирования на языке Python. 7 занятие Электронная цифровая подпись

Электронная цифровая подпись Формирование комплекса целей в информационном менеджменте. (Тема 2)

Формирование комплекса целей в информационном менеджменте. (Тема 2) Бинарные деревья

Бинарные деревья Логическое проектирование

Логическое проектирование Владение информационными технологиями – путь к успеху

Владение информационными технологиями – путь к успеху Проектирование структуры БД. Методические указания к курсовой работе Разработка и эксплуатация АИС Часть 1

Проектирование структуры БД. Методические указания к курсовой работе Разработка и эксплуатация АИС Часть 1 Оформление библиографического описания

Оформление библиографического описания 2 современные методы

2 современные методы Файлы и папки

Файлы и папки Требования к программному обеспечению

Требования к программному обеспечению Расширения алгоритмов LLE, Isomap, MDS, Eigenmaps, и Spectral Clustering для точек вне обучающей выборки

Расширения алгоритмов LLE, Isomap, MDS, Eigenmaps, и Spectral Clustering для точек вне обучающей выборки Прикладное программное обеспечение (ППО)специального назначения

Прикладное программное обеспечение (ППО)специального назначения Исследование проблемной области на наличие аналогичных разработок программного обеспечения

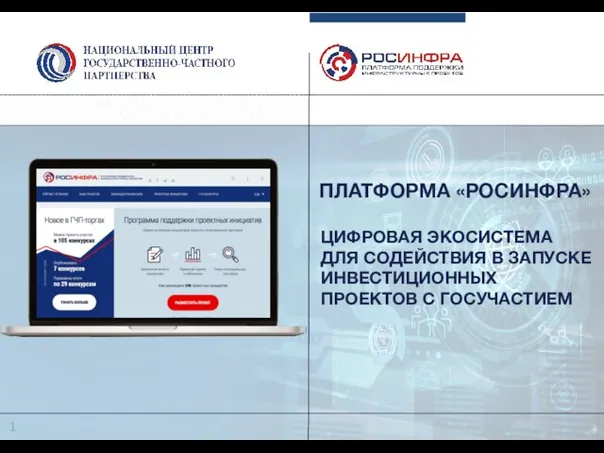

Исследование проблемной области на наличие аналогичных разработок программного обеспечения Платформа Росинфра. Цифровая экосистема для содействия в запуске инвестиционных проектов с госучастием

Платформа Росинфра. Цифровая экосистема для содействия в запуске инвестиционных проектов с госучастием Ретушь

Ретушь ВПД 2020. Тема2. Информационные системы и технологии

ВПД 2020. Тема2. Информационные системы и технологии Рамки для аватарок

Рамки для аватарок Алгоритм. Задания для 2 класса

Алгоритм. Задания для 2 класса Der Rfid oder NFC Chip

Der Rfid oder NFC Chip Современные online сервисы в образовании (1)

Современные online сервисы в образовании (1) Обработка потока данных. Цикл с параметром

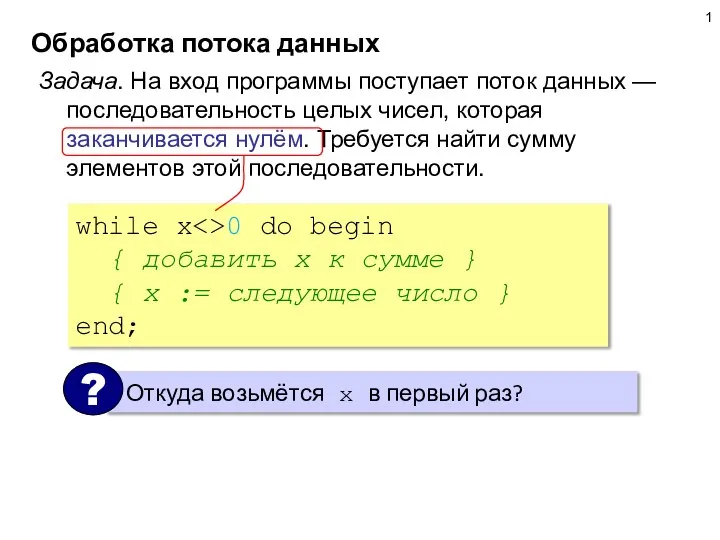

Обработка потока данных. Цикл с параметром Мультимедиа. Классификация

Мультимедиа. Классификация Objektorientierte. Modul 24

Objektorientierte. Modul 24 С++. Отличия

С++. Отличия Конвергент от Ростелеком

Конвергент от Ростелеком