Содержание

- 2. Узлом ЭВМ называется совокупность функционально связанных элементов, предназначенных для выполнения определенных операций над двоичными словами. Узлы

- 3. Регистр — узел ЭВМ, предназначенный для хранения двоичных слов и выполнения над ними некоторых логических операций.

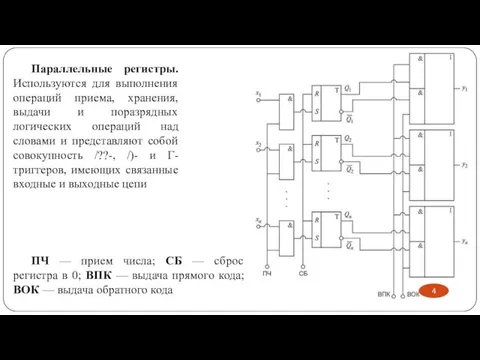

- 4. Параллельные регистры. Используются для выполнения операций приема, хранения, выдачи и поразрядных логических операций над словами и

- 5. Сдвиговые регистры. Используются для выполнения следующих операций: 1) умножение на 2^к, если сдвиг осуществляется на к

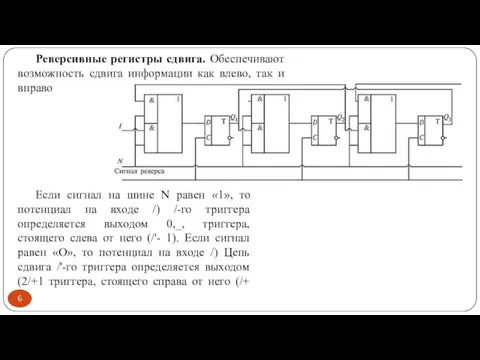

- 6. Реверсивные регистры сдвига. Обеспечивают возможность сдвига информации как влево, так и вправо Если сигнал на шине

- 7. Счетчик — накопительный узел ЭВМ, предназначенный для подсчета числа импульсов, поступивших на его вход. По структуре

- 8. К характеристикам счетчиков относят: • коэффициент пересчета (число состояний счетчика) М (количество импульсов, поступивших на вход

- 9. Счетчик с последовательным переносом cтроится на основе Г-триггеров. Счетчик со сквозным переносом. Увеличить быстродействие счетчика можно

- 10. Счетчик с групповым переносом. Из-за конечности коэффициентов объединения элементов «И» число разрядов в счетчике с параллельным

- 11. Сумматор — узел ЭВМ, выполняющий суммирование двоичных кодов чисел. Он является узлом преобразования информации. Различают комбинационные

- 12. В зависимости от способов обработки разрядов слагаемых различают сумматоры: • последовательного действия (разряды обрабатываются последовательно один

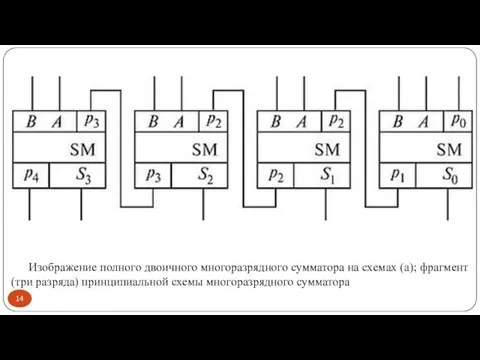

- 13. Многоразрядные сумматоры строятся как совокупность одноразрядных. Комбинационный сумматор параллельного действия с последовательным переносом. Такие сумматоры строятся

- 14. Изображение полного двоичного многоразрядного сумматора на схемах (а); фрагмент (три разряда) принципиальной схемы многоразрядного сумматора

- 15. Комбинационный сумматор параллельного действия с параллельным переносом. Применяется схема параллельного переноса (СПП), формирующая перенос каждого разряда

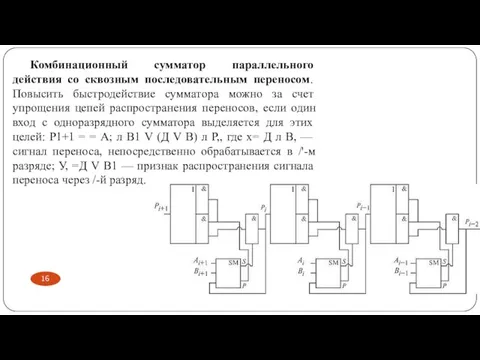

- 16. Комбинационный сумматор параллельного действия со сквозным последовательным переносом. Повысить быстродействие сумматора можно за счет упрощения цепей

- 17. Комбинационный n-разрядный сумматор с групповым переносом. В такой сумматор вводят обходные цепи распространения сигнала переноса, для

- 18. Дешифратор — комбинационный узел, который предназначен для преобразования двоичного кода (х) на входе в управляющий сигнал

- 19. Виды дешифраторов По структурному построению дешифраторы делятся на линейные и многокаскадные. У линейных дешифраторов все переменные

- 20. Простейший линейный дешифратор можно построить на диодной матрице. В этой схеме используется тельная логика. При подаче

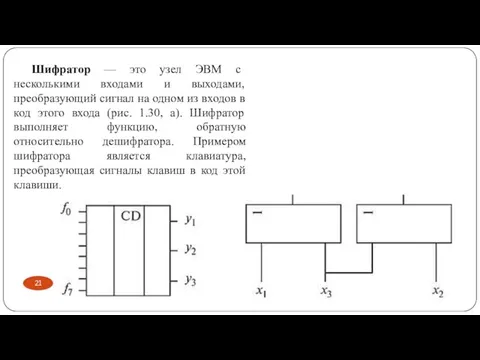

- 21. Шифратор — это узел ЭВМ с несколькими входами и выходами, преобразующий сигнал на одном из входов

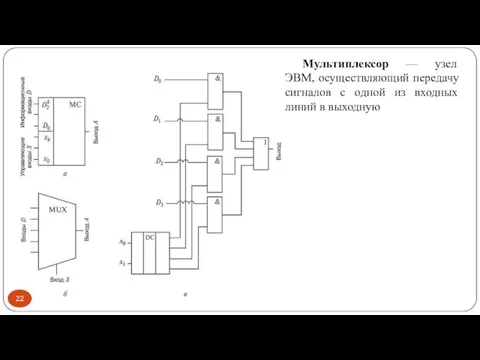

- 22. Мультиплексор — узел ЭВМ, осуществляющий передачу сигналов с одной из входных линий в выходную

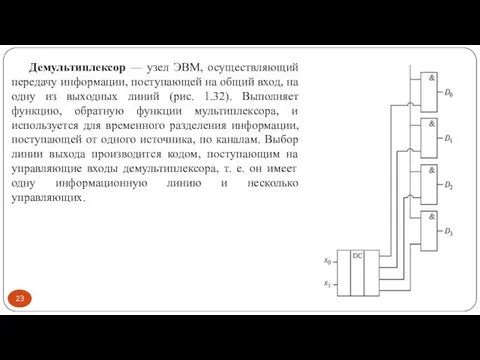

- 23. Демультиплексор — узел ЭВМ, осуществляющий передачу информации, поступающей на общий вход, на одну из выходных линий

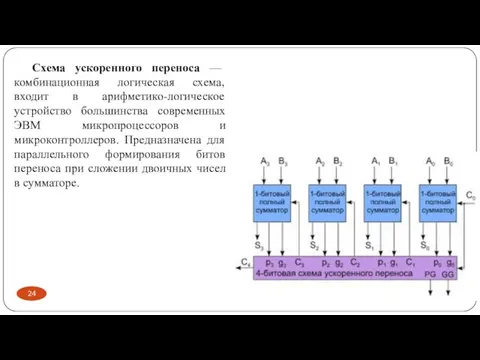

- 24. Схема ускоренного переноса — комбинационная логическая схема, входит в арифметико-логическое устройство большинства современных ЭВМ микропроцессоров и

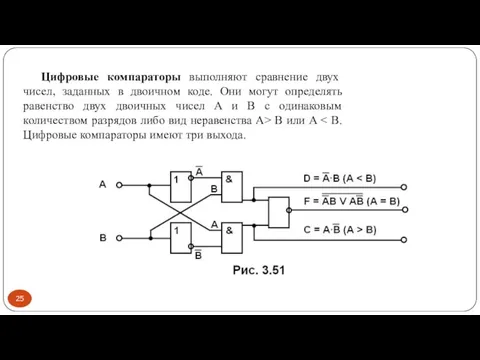

- 25. Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных

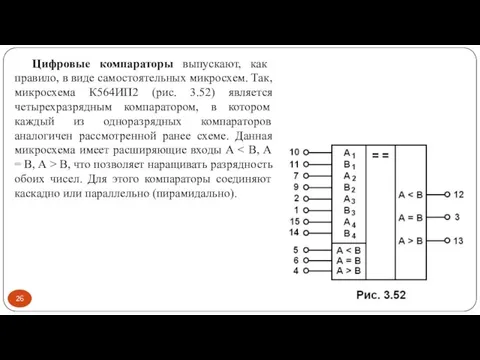

- 26. Цифровые компараторы выпускают, как правило, в виде самостоятельных микросхем. Так, микросхема К564ИП2 (рис. 3.52) является четырехразрядным

- 27. Цифро-аналоговый преобразователь (ЦАП) — устройство для преобразования цифрового (обычно двоичного) кода в аналоговый сигнал (ток, напряжение

- 28. Аналого-цифровой преобразователь (АЦП, англ. Analog-to-digital converter, ADC) — устройство, преобразующее входной аналоговый сигнал в дискретный код

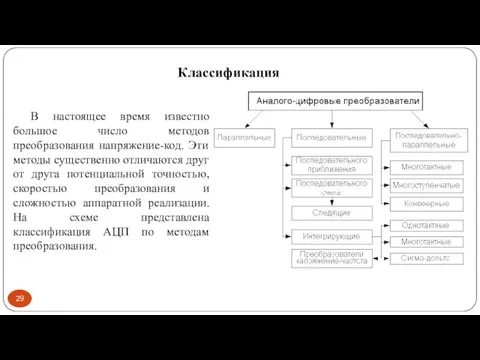

- 29. Классификация В настоящее время известно большое число методов преобразования напряжение-код. Эти методы существенно отличаются друг от

- 30. 1. АЦП параллельного преобразования. Обладают низкой разрядностью и высоким быстродействием. Принцип действия заключается в поступлении входного

- 32. Скачать презентацию

Афинский Акрополь

Афинский Акрополь Электрическая цепь и её составные части

Электрическая цепь и её составные части Атмосфера. Ветер

Атмосфера. Ветер Анимации и рисунки для облегчения понимания выбранных изменений правил волейбола в 2021г. (презентация ERC)

Анимации и рисунки для облегчения понимания выбранных изменений правил волейбола в 2021г. (презентация ERC) Царева Алина Александровна Кинематическое и динамическое моделирование плоских механизмов в системе Mathematica Руководитель: канд

Царева Алина Александровна Кинематическое и динамическое моделирование плоских механизмов в системе Mathematica Руководитель: канд Введение в Микробиологию

Введение в Микробиологию Презентация на тему Нептун 8 класс

Презентация на тему Нептун 8 класс Близорукость. Профилактика близорукости

Близорукость. Профилактика близорукости Музеи

Музеи Креатив в eventах: рутина и творчество

Креатив в eventах: рутина и творчество Фотоальбом

Фотоальбом Математика в архитектуре и живописи

Математика в архитектуре и живописи Социальное обеспечение и защита военнослужащих и членов их семей

Социальное обеспечение и защита военнослужащих и членов их семей Презентация на тему ДОБРЫХ РУК МАСТЕРСТВО

Презентация на тему ДОБРЫХ РУК МАСТЕРСТВО  Презентация на тему Правила поведения во время зимних каникул

Презентация на тему Правила поведения во время зимних каникул What time is it

What time is it Вопросы теории государства и права. Урок 1-2. Государство, его признаки и формы

Вопросы теории государства и права. Урок 1-2. Государство, его признаки и формы Иван Андреевич Крылов

Иван Андреевич Крылов Проведение Нового года в разных странах мира

Проведение Нового года в разных странах мира Экономика недвижимости (2)

Экономика недвижимости (2) Путешествие по "Стране Законии"

Путешествие по "Стране Законии" Натюрморт

Натюрморт Развитие творческого потенциала воспитанников учреждения дополнительного образования

Развитие творческого потенциала воспитанников учреждения дополнительного образования Как технологии изменят нашу жизнь?

Как технологии изменят нашу жизнь? Правила поведения в библиотеке

Правила поведения в библиотеке Я-концепция как основа жизненного стиля

Я-концепция как основа жизненного стиля Самоучитель английский для взрослых

Самоучитель английский для взрослых Политико-экономические детерминанты развития БеларусиДипломная работа

Политико-экономические детерминанты развития БеларусиДипломная работа