Содержание

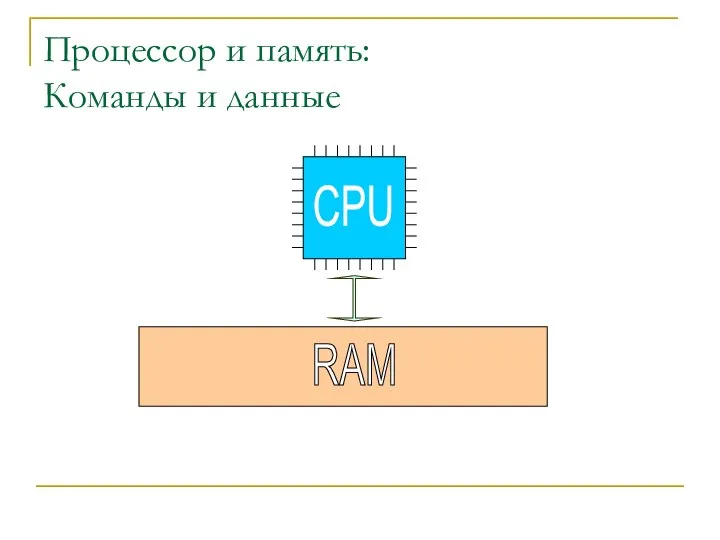

- 2. Процессор и память: Команды и данные CPU RAM

- 3. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора

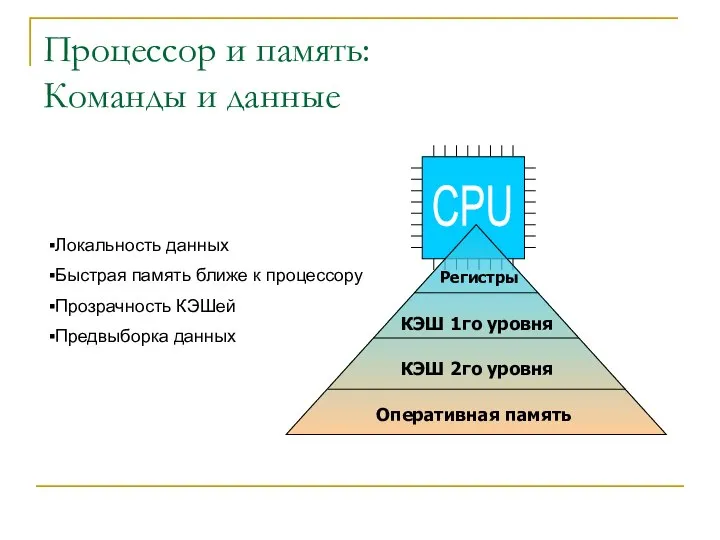

- 4. Процессор и память: Команды и данные CPU Регистры КЭШ 1го уровня КЭШ 2го уровня Оперативная память

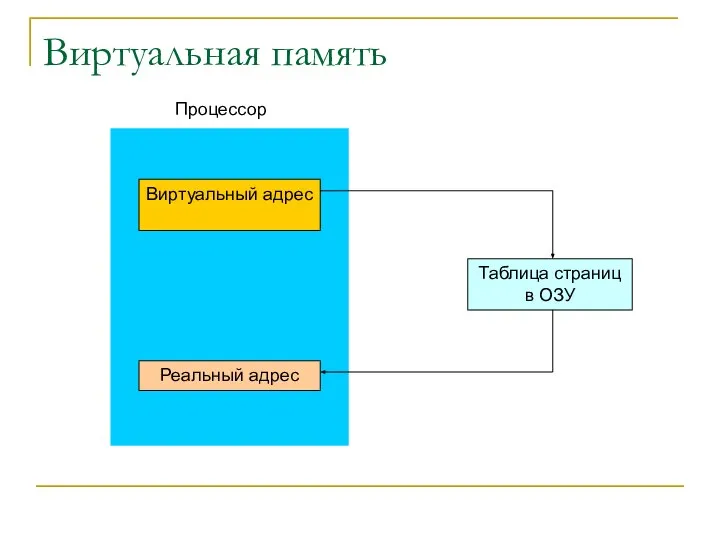

- 5. Виртуальная память Виртуальный адрес Реальный адрес Таблица страниц в ОЗУ Процессор

- 6. Виртуальная память Виртуальный адрес Реальный адрес Таблица страниц в ОЗУ Процессор TLB

- 7. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора

- 8. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора Дополнительные устройства Конвейеризация Упрощение команд Параллелизм

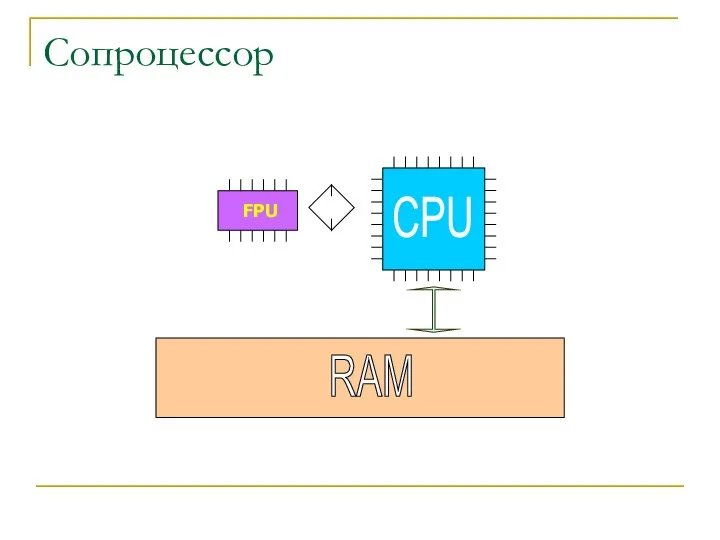

- 9. Сопроцессор FPU CPU RAM

- 10. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора Дополнительные устройства Конвейеризация Упрощение команд Параллелизм

- 11. Конвейер команд 1 2 1 2 1 2 1 2 1 2 Ступени Выборка команды Декодирование

- 12. Конвейер команд 1 2 3 4 5 6 1 2 3 4 5 6 1 2

- 13. Конвейер: Условные ветвления Конвейер ? Проблема: Условные переходы

- 14. Конвейер: Условные ветвления Конвейер ?* Проблема: Условные переходы Решения: Спекулятивное исполнение с предсказанием переходов Использование условных

- 15. Конвейер: Условные ветвления Конвейер Проблема: Условные переходы Решения: Спекулятивное исполнение с предсказанием переходов Использование условных команд

- 16. Конвейер: Условные ветвления Конвейер Проблема: Условные переходы Решения: Спекулятивное исполнение с предсказанием переходов Использование условных команд

- 17. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора Дополнительные устройства Конвейеризация Упрощение команд Параллелизм

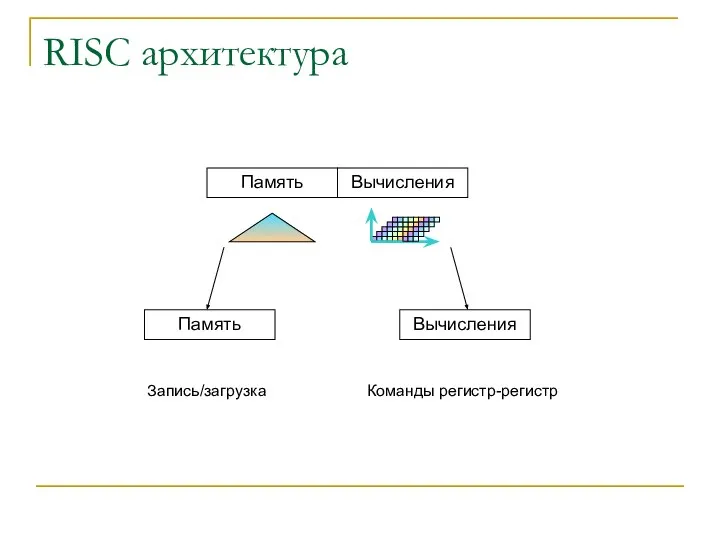

- 18. RISC архитектура Память Вычисления Память Вычисления Запись/загрузка Команды регистр-регистр

- 19. CISC Большое количество команд Много типов данных Различная длина инструкций Небольшое количество регистров Ориентация на процессор

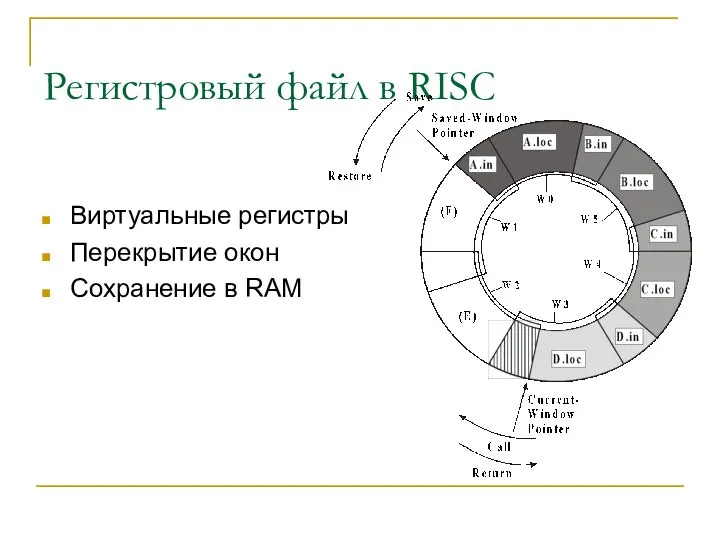

- 20. Регистровый файл в RISC Виртуальные регистры Перекрытие окон Сохранение в RAM

- 21. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора Дополнительные устройства Конвейеризация Упрощение команд Параллелизм

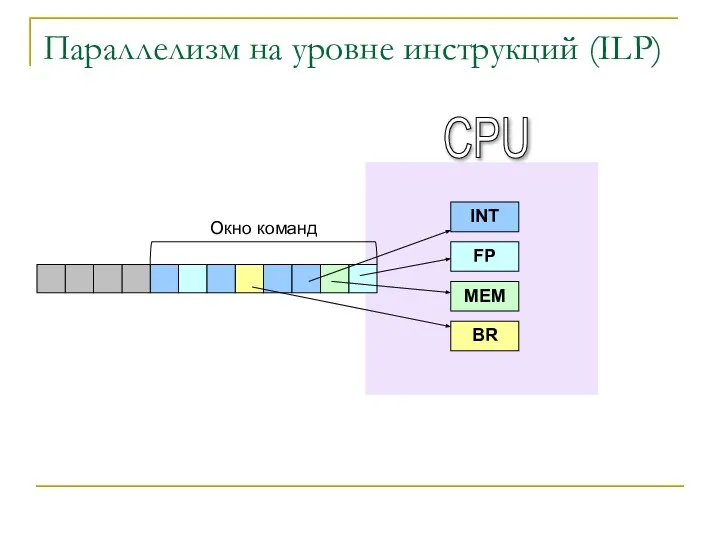

- 22. Параллелизм на уровне инструкций (ILP) INT FP MEM BR Окно команд CPU

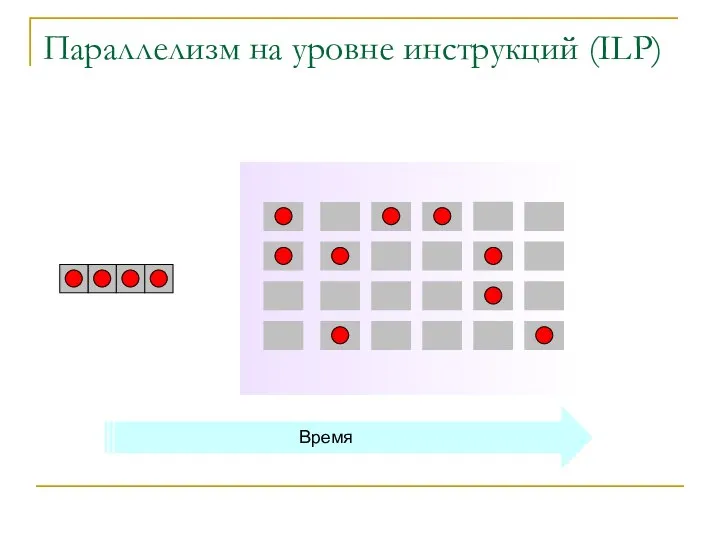

- 23. Параллелизм на уровне инструкций (ILP) Время

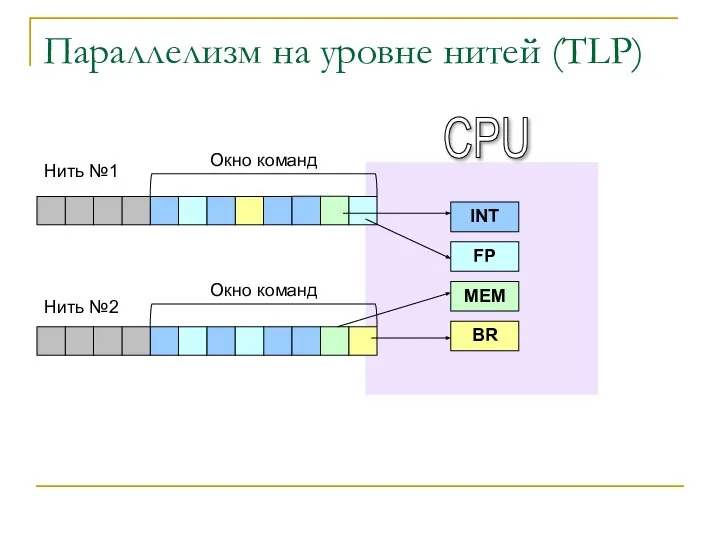

- 24. Параллелизм на уровне нитей (TLP) INT FP MEM BR Окно команд CPU Окно команд Нить №1

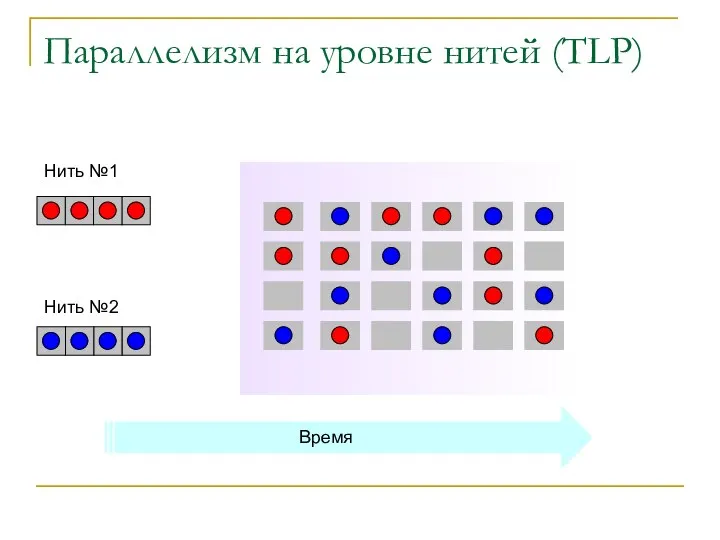

- 25. Параллелизм на уровне нитей (TLP) Время Нить №1 Нить №2

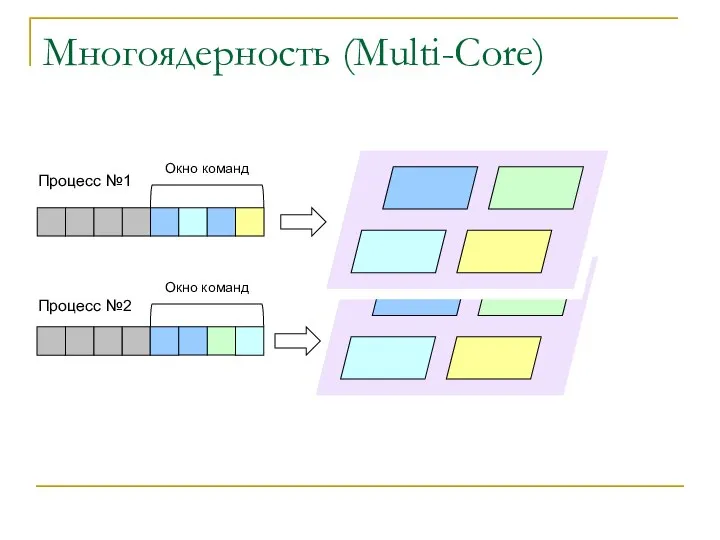

- 26. Многоядерность (Multi-Core) Окно команд Окно команд Процесс №1 Процесс №2

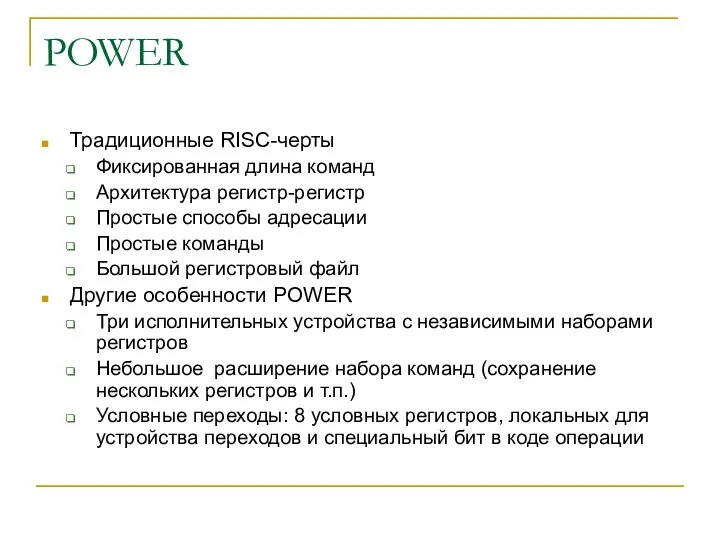

- 27. POWER Традиционные RISC-черты Фиксированная длина команд Архитектура регистр-регистр Простые способы адресации Простые команды Большой регистровый файл

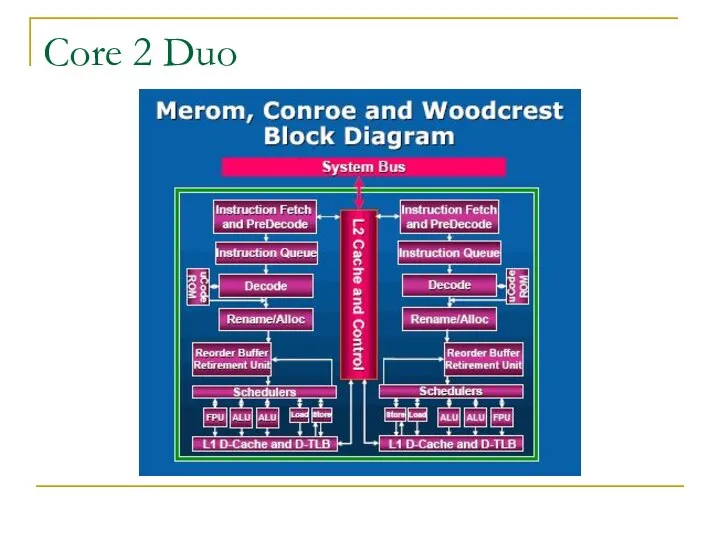

- 28. Core 2 Duo

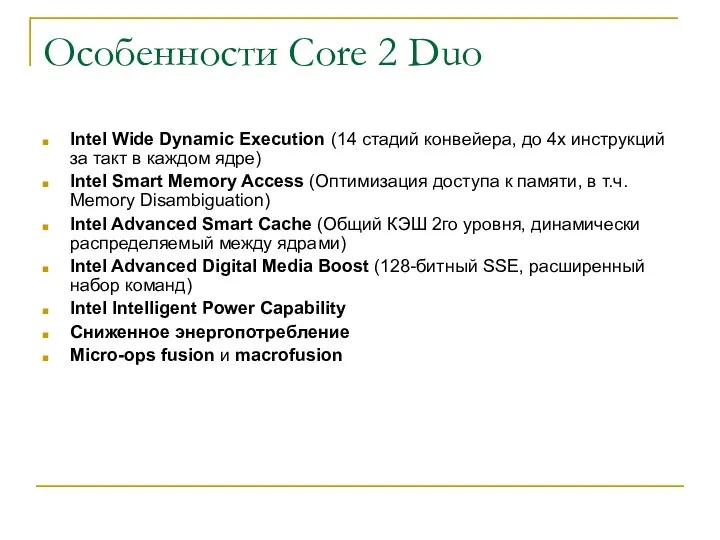

- 29. Особенности Core 2 Duo Intel Wide Dynamic Execution (14 стадий конвейера, до 4х инструкций за такт

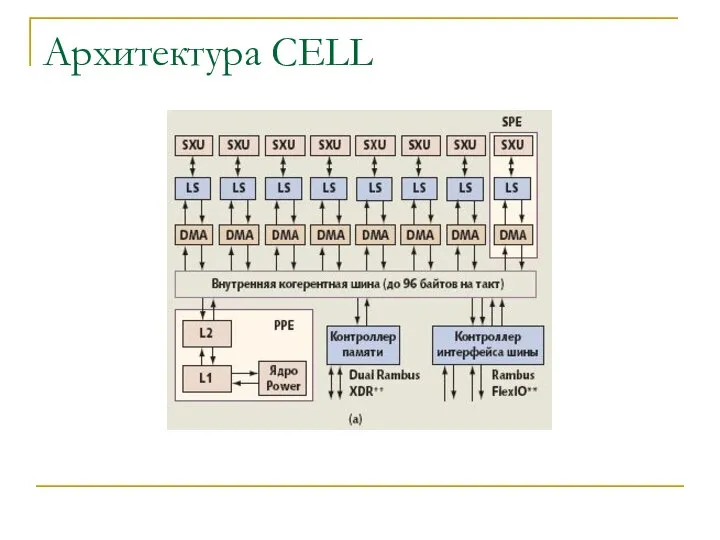

- 30. Архитектура CELL

- 32. Скачать презентацию

Автосалон. Продажа автомобилей

Автосалон. Продажа автомобилей Моделирование юбки

Моделирование юбки Рождение современных идеологий

Рождение современных идеологий Words and their parts

Words and their parts РЕАБИЛИТАЦИЯ СЕГОДНЯ и ЗАВТРА Докладчик: Булекбаева Ш.А., Председатель Правления АО РДРЦ, дмн, внештатный медицинский реабилитолог

РЕАБИЛИТАЦИЯ СЕГОДНЯ и ЗАВТРА Докладчик: Булекбаева Ш.А., Председатель Правления АО РДРЦ, дмн, внештатный медицинский реабилитолог Эдвард Мунк (1863-1944), норвежский живописец, график, театральный художник

Эдвард Мунк (1863-1944), норвежский живописец, график, театральный художник Основные элементы проектной деятельности

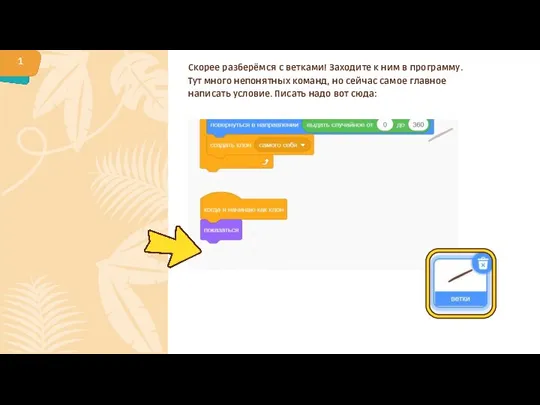

Основные элементы проектной деятельности изучаем алгоритмы

изучаем алгоритмы Урок _ 5_4

Урок _ 5_4 Акварель для начинающих Ван Гог

Акварель для начинающих Ван Гог НАРКОМАНИЯ

НАРКОМАНИЯ Презентация на тему My family 6 класс

Презентация на тему My family 6 класс ФГБОУ ВО Курская ГСХА. Экономический факультет

ФГБОУ ВО Курская ГСХА. Экономический факультет Филолог. Прокачай свой уровень филологичности за 15 минут

Филолог. Прокачай свой уровень филологичности за 15 минут Карта сборки electric generator

Карта сборки electric generator ГИА-9 Вариант -3

ГИА-9 Вариант -3 Instruktsia_po_prokhozhdeniyu_Frai_774_burgskogo_lichnostnogo_oprosnika

Instruktsia_po_prokhozhdeniyu_Frai_774_burgskogo_lichnostnogo_oprosnika Образовательный ликбез: знаем, понимаем, применяем на практике. Организации родителей детей-инвалидов

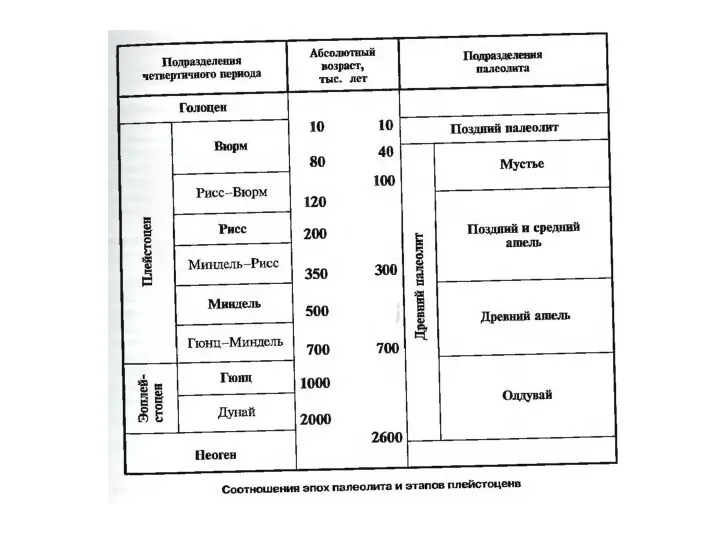

Образовательный ликбез: знаем, понимаем, применяем на практике. Организации родителей детей-инвалидов Первобытная идеология и искусство

Первобытная идеология и искусство ТЕСТ М.А.БУЛГАКОВ "МАСТЕР И МАРГАРИТА"

ТЕСТ М.А.БУЛГАКОВ "МАСТЕР И МАРГАРИТА" Строение и свойства вещества

Строение и свойства вещества Нормы Сан-Пина

Нормы Сан-Пина HotBOX.ru бесплатная электронная почтовая служба

HotBOX.ru бесплатная электронная почтовая служба Графика зимнего леса

Графика зимнего леса Символы в жизни и искусстве

Символы в жизни и искусстве ОЭР в школе в 2007/2008 уч.г.

ОЭР в школе в 2007/2008 уч.г. Пространство Поволжья

Пространство Поволжья BRIDGE

BRIDGE