Содержание

- 2. k-МДП Элементы КМОП-логики можно рассматривать как обобщение КМОП-инвертора. Общая закономерность построения таких элементов заключается в том,

- 3. k-МДП Пусть на обоих входах действует напряжение низкого уровня: Uвх1 =Uвх2 = 0 . Поскольку Uзи3

- 4. k-МДП Рассмотрим случай, когда Uвх1 = Uвх 2 = E . Теперь Uзи1 = Uзи2 =

- 5. k-МДП КМОП-элементы ИЛИ-НЕ занимают на кристалле значительно большую площадь, чем элементы И-НЕ. Это объясняется тем, что

- 6. k-МДП 1. Логические элементы, изготовленные по КМОП-технологии, потребляют значительно меньшую мощность, чем логические элементы на основе

- 8. Скачать презентацию

Слайд 2k-МДП

Элементы КМОП-логики можно рассматривать как обобщение

КМОП-инвертора. Общая закономерность построения таких элементов заключается

k-МДП

Элементы КМОП-логики можно рассматривать как обобщение

КМОП-инвертора. Общая закономерность построения таких элементов заключается

в том, что параллельное соединение транзисторов с каналами p-типа сопровождается последовательным соединением транзисторов с каналами

n-типа и наоборот.

Схема КМОП-элемента, реализующего операцию 2И-НЕ, показана на рисунке.

Транзисторы VT1 и VT2 с

каналом p-типа соединены

параллельно,

а n-канальные транзисторы

VT3 и VT4 – последовательно.

Подложки и истоки VT1 и

VT2 соединены с положительным зажимом источника питания, поэтому

Uзи1 = U - Eвх1 , Uзи2 = U - Eвх2 .

Схема КМОП-элемента, реализующего операцию 2И-НЕ, показана на рисунке.

Транзисторы VT1 и VT2 с

каналом p-типа соединены

параллельно,

а n-канальные транзисторы

VT3 и VT4 – последовательно.

Подложки и истоки VT1 и

VT2 соединены с положительным зажимом источника питания, поэтому

Uзи1 = U - Eвх1 , Uзи2 = U - Eвх2 .

Слайд 3k-МДП

Пусть на обоих входах действует напряжение низкого уровня:

Uвх1 =Uвх2 = 0 .

k-МДП

Пусть на обоих входах действует напряжение низкого уровня:

Uвх1 =Uвх2 = 0 .

Поскольку Uзи3 =Uвх1 = 0, Uзи4 = Uвх2 = 0, транзисторы VT3 и VT4 закрыты. При этом Uзи1 =Uзи2 = - E

и транзисторы VT1 и VT2 открыты.

Упрощенно цепь на рисунке выше можно представить эквивалентной схемой, показанной на рисунке а. Напряжения на открытых транзисторах VT1 и VT2

пренебрежимо малы, и выходное напряжение Uвых >> E .

Упрощенно цепь на рисунке выше можно представить эквивалентной схемой, показанной на рисунке а. Напряжения на открытых транзисторах VT1 и VT2

пренебрежимо малы, и выходное напряжение Uвых >> E .

Слайд 4k-МДП

Рассмотрим случай, когда Uвх1 = Uвх 2 = E . Теперь Uзи1

k-МДП

Рассмотрим случай, когда Uвх1 = Uвх 2 = E . Теперь Uзи1

= Uзи2 = 0 и транзисторы VT1 и VT2 закрыты, а VT3 и VT4 – открыты. Логический элемент можно представить эквивалентной схемой, показанной на рисунке б выше. Выходное напряжение

Uвых ≈ 0 » . Таким образом, схема реализует таблицу истинности логического элемента 2И-НЕ.

Логический элемент имеет два входа. Каждый новый вход

требует включения двух дополнительных транзисторов: p-канального в параллельную цепь и n-канального в последовательную. Это приводит к увеличению площади, занимаемой логическим элементом на кристалле. Увеличивается и паразитная емкость, ограничивающая быстродействие схемы. Поэтому число входов у элементов КМОП-логики, как правило, не превышает четырех. КМОП-элемент, реализующий операцию 2ИЛИ-НЕ, показан на рисунке. Здесь p-канальные транзисторы включены последовательно, а n-канальные – параллельно.

Логический элемент имеет два входа. Каждый новый вход

требует включения двух дополнительных транзисторов: p-канального в параллельную цепь и n-канального в последовательную. Это приводит к увеличению площади, занимаемой логическим элементом на кристалле. Увеличивается и паразитная емкость, ограничивающая быстродействие схемы. Поэтому число входов у элементов КМОП-логики, как правило, не превышает четырех. КМОП-элемент, реализующий операцию 2ИЛИ-НЕ, показан на рисунке. Здесь p-канальные транзисторы включены последовательно, а n-канальные – параллельно.

Слайд 5k-МДП

КМОП-элементы ИЛИ-НЕ занимают на кристалле значительно большую площадь, чем элементы И-НЕ. Это

k-МДП

КМОП-элементы ИЛИ-НЕ занимают на кристалле значительно большую площадь, чем элементы И-НЕ. Это

объясняется тем, что последовательно соединенные p-канальные транзисторы должны иметь большую ширину канала, чем при параллельном соединении. Действительно, два последовательно соединенных p-канальных транзистора можно рассматривать как один с каналом длиной 2L. Для согласования с n-канальными транзисторами они должны иметь канал шириной: 2Wp = 2Wn μn / μp.

Поэтому в схемах высокой степени интеграции для экономии площади кристалла целесообразно использовать элементы И-НЕ.

В настоящее время КМОП-технологии являются доминирующими при производстве цифровых интегральных схем и практически вытеснили логику на основе биполярных транзисторов. КМОП-логика используется в цифровых интегральных схемах как малой (1–10 логических элементов на кристалле) и средней (10–100 ЛЭ), так и большой степени интеграции. Это обусловлено следующими причинами.

Поэтому в схемах высокой степени интеграции для экономии площади кристалла целесообразно использовать элементы И-НЕ.

В настоящее время КМОП-технологии являются доминирующими при производстве цифровых интегральных схем и практически вытеснили логику на основе биполярных транзисторов. КМОП-логика используется в цифровых интегральных схемах как малой (1–10 логических элементов на кристалле) и средней (10–100 ЛЭ), так и большой степени интеграции. Это обусловлено следующими причинами.

Слайд 6k-МДП

1. Логические элементы, изготовленные по КМОП-технологии, потребляют значительно меньшую мощность, чем логические

k-МДП

1. Логические элементы, изготовленные по КМОП-технологии, потребляют значительно меньшую мощность, чем логические

элементы на основе биполярных транзисторов как в статическом, так и в динамическом режимах. Потребление мощности КМОП-элементами обусловлено в основном перезарядом паразитных емкостей при переключении элемента из одного логического состояния в другое.

2. Поскольку входы схем являются изолированными затворами МОП-транзисторов, то входные токи очень малы. Поэтому коэффициент разветвления по выходу очень высок. Высокое входное сопротивление МОП-транзисторов позволяет использовать накопленный заряд для хранения входной информации. Это свойство широко используется в микросхемах памяти.

3. МОП-транзистор занимает на кристалле значительно меньшую площадь, чем биполярный. Современные технологии производства СБИС позволяют создавать МОП-транзисторы с длиной канала 0.06 мкм. Уменьшение геометрических размеров, а также малое потребление мощности дают возможность изготавливать СБИС, которые содержат десятки миллионов МОП-транзисторов.

2. Поскольку входы схем являются изолированными затворами МОП-транзисторов, то входные токи очень малы. Поэтому коэффициент разветвления по выходу очень высок. Высокое входное сопротивление МОП-транзисторов позволяет использовать накопленный заряд для хранения входной информации. Это свойство широко используется в микросхемах памяти.

3. МОП-транзистор занимает на кристалле значительно меньшую площадь, чем биполярный. Современные технологии производства СБИС позволяют создавать МОП-транзисторы с длиной канала 0.06 мкм. Уменьшение геометрических размеров, а также малое потребление мощности дают возможность изготавливать СБИС, которые содержат десятки миллионов МОП-транзисторов.

- Предыдущая

Построения в пространствеСледующая -

Экслибрис Занятие для детей 6 – 7 лет с синдромом гиперактивности тема: «Мы - разные, мы - вместе».

Занятие для детей 6 – 7 лет с синдромом гиперактивности тема: «Мы - разные, мы - вместе». Анализ товарных и финансовых рынков

Анализ товарных и финансовых рынков Привет (Hello)

Привет (Hello) Химическая авария

Химическая авария The Story of St. Valentine (История святого Валентина)

The Story of St. Valentine (История святого Валентина) Icons Webshop Promodomo

Icons Webshop Promodomo Компания FINFIRE

Компания FINFIRE «Педагогическая технология – это описание процесса достижения планируемых результатов обучения»

«Педагогическая технология – это описание процесса достижения планируемых результатов обучения»  Презентация на тему Религия (11 класс)

Презентация на тему Религия (11 класс) Невская битва

Невская битва 1C:Смета

1C:Смета Биография семьи в биографии страны

Биография семьи в биографии страны Конституция России

Конституция России Порядок применения льгот по налогу на доходы (прибыль) для микрокредитных организаций

Порядок применения льгот по налогу на доходы (прибыль) для микрокредитных организаций Информационная эвристика в Интернет(опыт специального курса на историческом факультете МГУ)

Информационная эвристика в Интернет(опыт специального курса на историческом факультете МГУ) Психическая травма у детей: особенности проявления и психологическая помощь

Психическая травма у детей: особенности проявления и психологическая помощь Реакции ионного обмена (8 класс)

Реакции ионного обмена (8 класс) Эндокринология беременности

Эндокринология беременности 14_10_2022

14_10_2022 Зимние виды спорта

Зимние виды спорта Сертификация. Лекция №3

Сертификация. Лекция №3 Развитие сплоченности

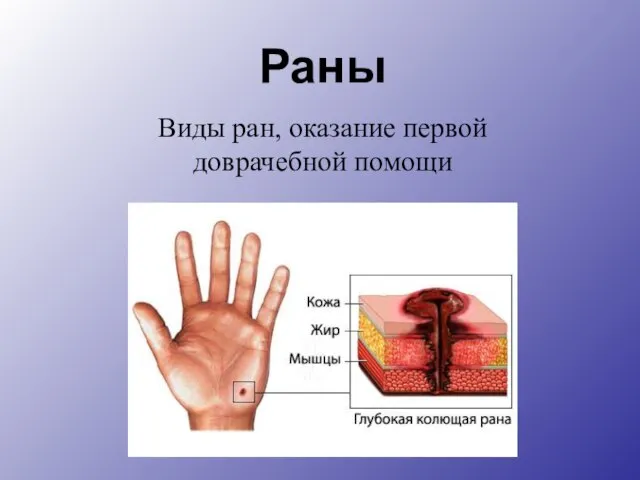

Развитие сплоченности Презентация на тему Раны Виды ран оказание первой доврачебной помощи

Презентация на тему Раны Виды ран оказание первой доврачебной помощи  Повторим орфографию. (для подготовки К ЕГЭ) Проверяемые безударные гласные. П…льба,ум… лять зн..чение, бл…госл…вить, обн…жать, по

Повторим орфографию. (для подготовки К ЕГЭ) Проверяемые безударные гласные. П…льба,ум… лять зн..чение, бл…госл…вить, обн…жать, по Презентация на тему Что такое планета

Презентация на тему Что такое планета Уровневая модель методической системы школы

Уровневая модель методической системы школы КОРПОРАЦИЯ ПО РАЗВИТИЮ И ПРОДВИЖЕНИЮ ЭКСПОРТА

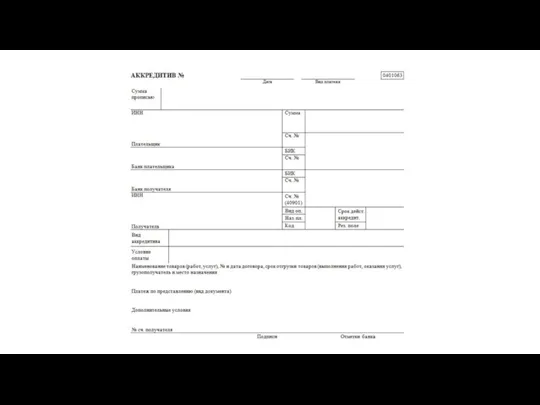

КОРПОРАЦИЯ ПО РАЗВИТИЮ И ПРОДВИЖЕНИЮ ЭКСПОРТА Аккредитив

Аккредитив