Содержание

- 2. 1К — это 1024, то есть 210; 1М — это 1048576, то есть 220; 1Г —

- 3. Информационные выводы микросхем памяти: ПЗУ (а), ОЗУ с двунаправленной шиной данных (б), ОЗУ с раздельными шинами

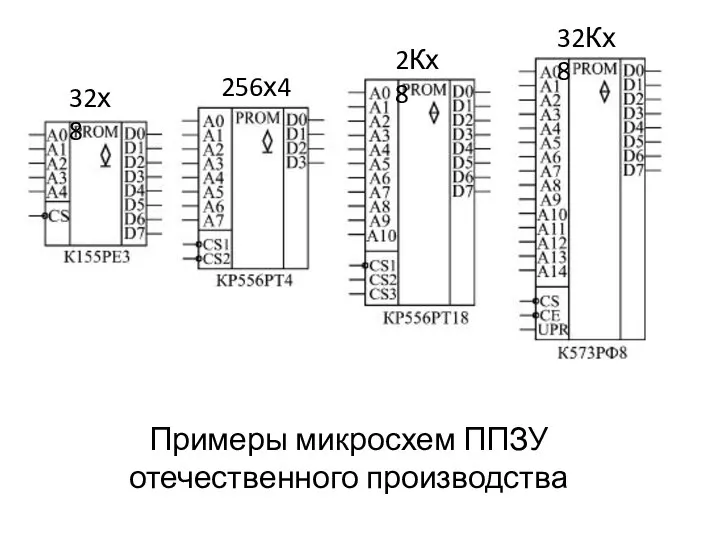

- 4. Примеры микросхем ППЗУ отечественного производства 32х8 256х4 2Кх8 32Кх8

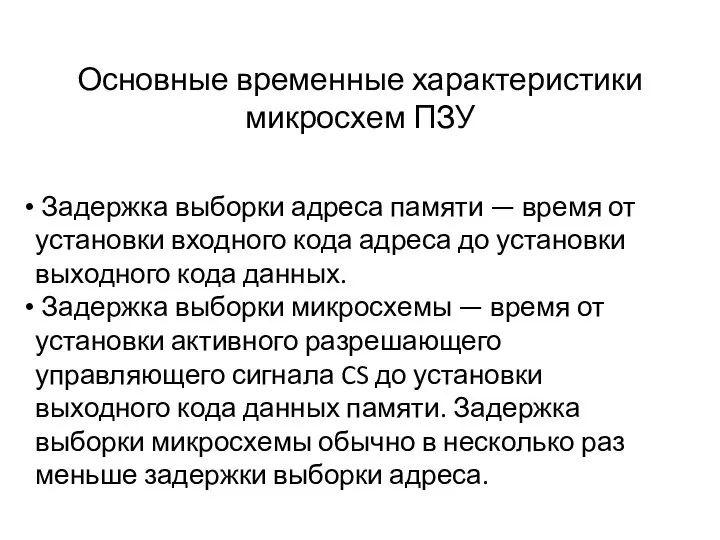

- 5. Основные временные характеристики микросхем ПЗУ Задержка выборки адреса памяти — время от установки входного кода адреса

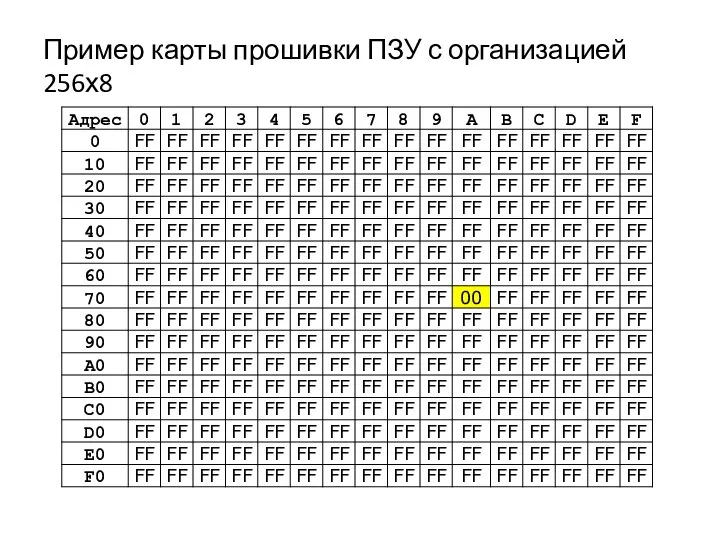

- 6. Пример карты прошивки ПЗУ с организацией 256х8

- 7. Уменьшение количества адресных разрядов ПЗУ (из 2Кх8 делаем 512х8)

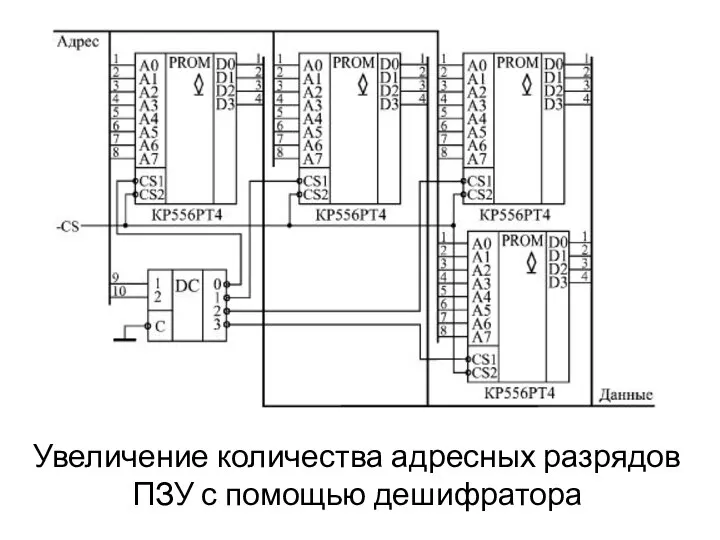

- 8. Увеличение количества адресных разрядов ПЗУ с помощью дешифратора

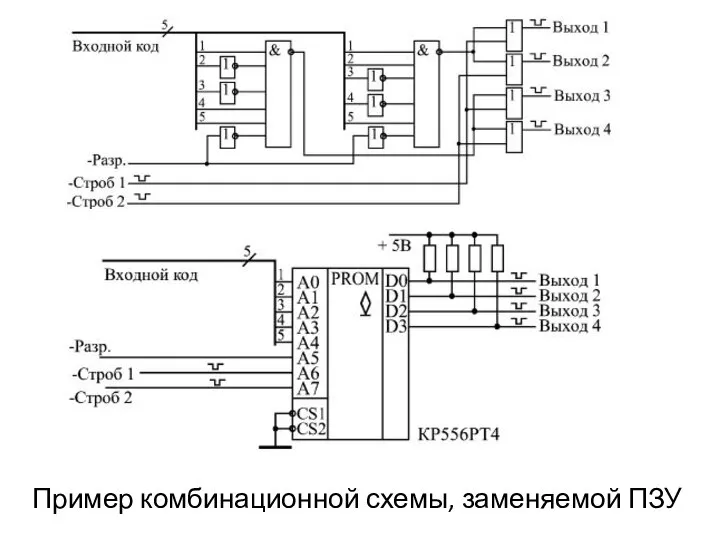

- 9. Пример комбинационной схемы, заменяемой ПЗУ

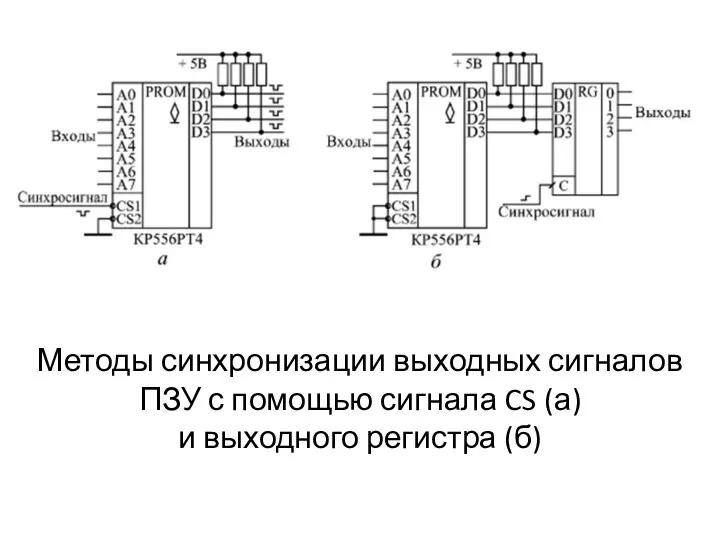

- 10. Методы синхронизации выходных сигналов ПЗУ с помощью сигнала CS (а) и выходного регистра (б)

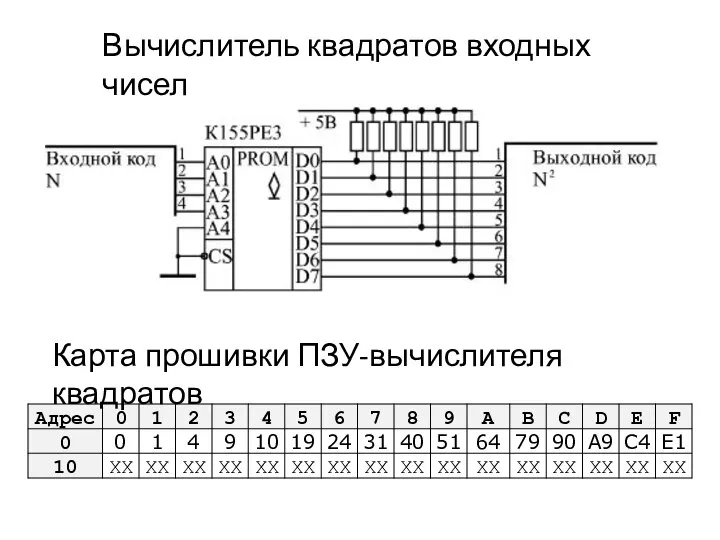

- 11. Вычислитель квадратов входных чисел Карта прошивки ПЗУ-вычислителя квадратов

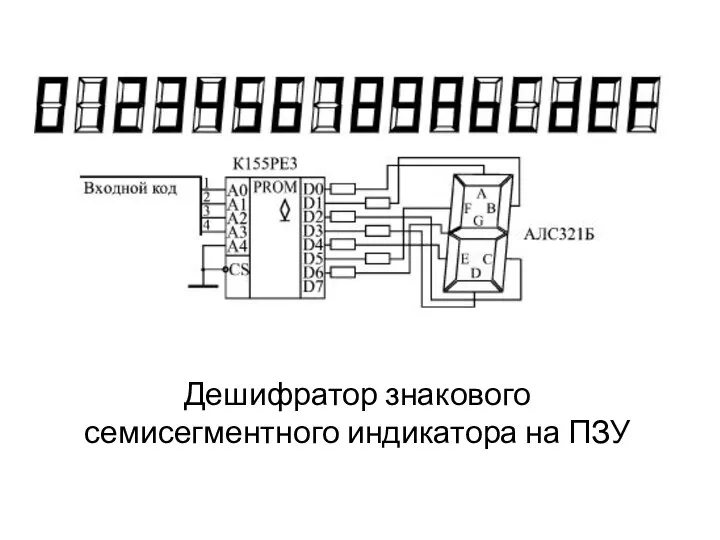

- 12. Дешифратор знакового семисегментного индикатора на ПЗУ

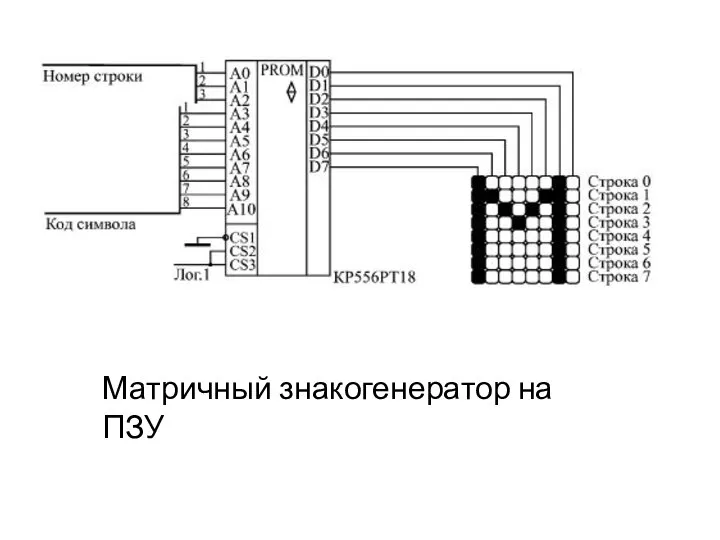

- 13. Матричный знакогенератор на ПЗУ

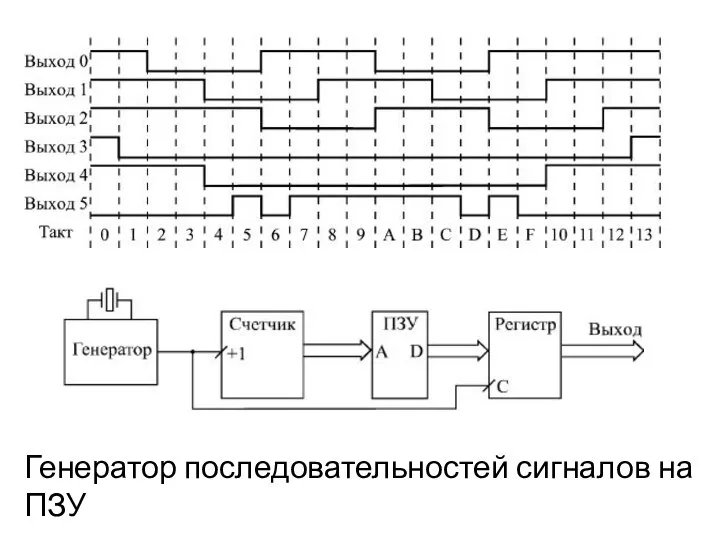

- 14. Генератор последовательностей сигналов на ПЗУ

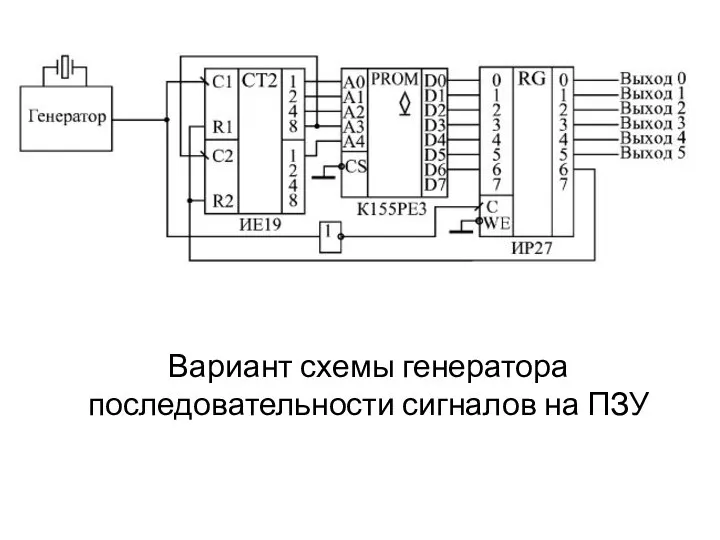

- 15. Вариант схемы генератора последовательности сигналов на ПЗУ

- 16. Прошивка ПЗУ генератора последовательности сигналов

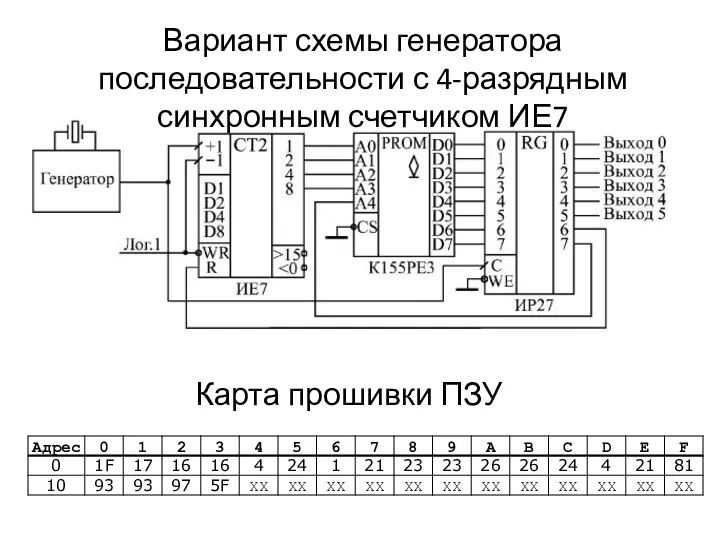

- 17. Вариант схемы генератора последовательности с 4-разрядным синхронным счетчиком ИЕ7 Карта прошивки ПЗУ

- 18. Структура микропрограммного автомата. Адреса перебираются в порядке, который определяется прошивкой ПЗУ (микропрограммой)

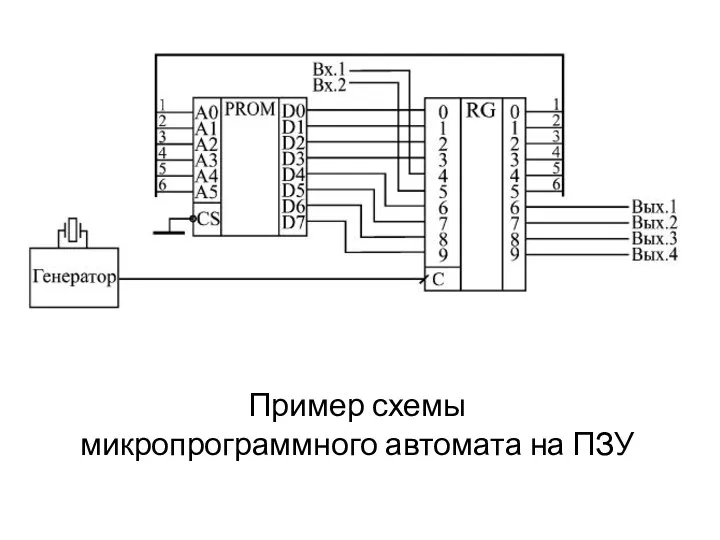

- 19. Пример схемы микропрограммного автомата на ПЗУ

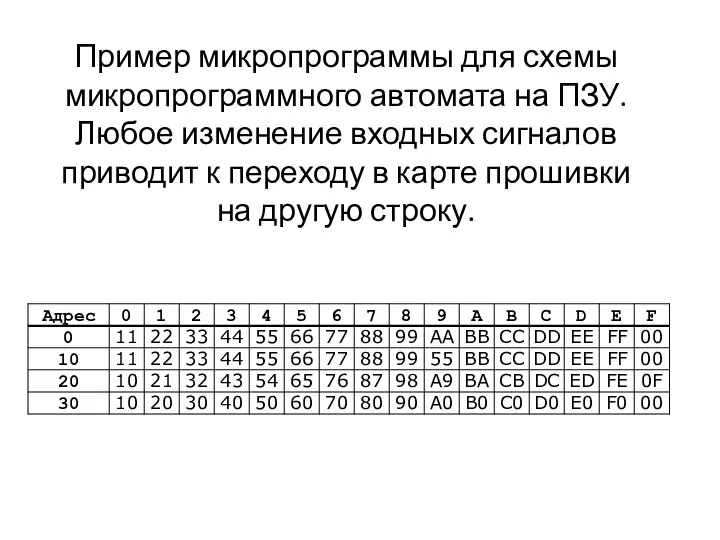

- 20. Пример микропрограммы для схемы микропрограммного автомата на ПЗУ. Любое изменение входных сигналов приводит к переходу в

- 21. Оперативная память (RAM) Статическая память: Ячейка представляет собой регистр из триггерных ячеек. Динамическая память: Информация хранится

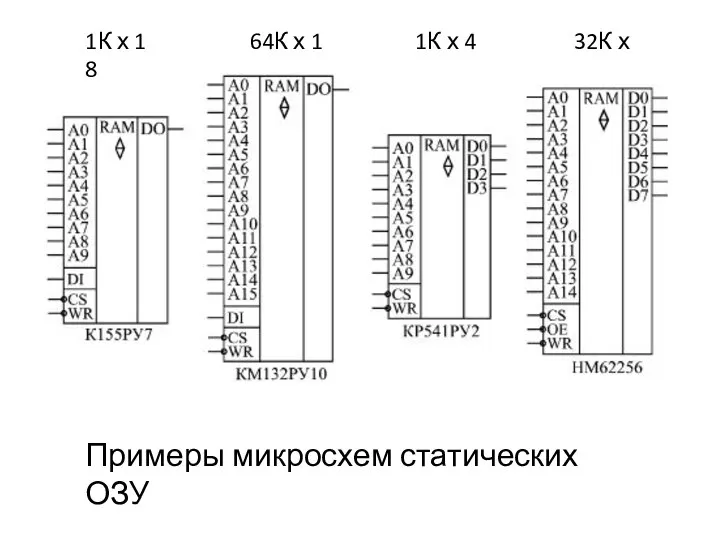

- 22. Примеры микросхем статических ОЗУ 1К х 1 64К х 1 1К х 4 32К х 8

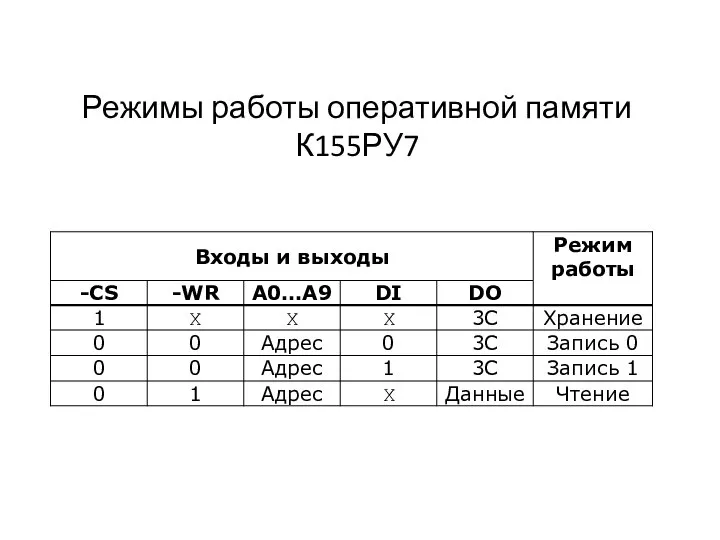

- 23. Режимы работы оперативной памяти К155РУ7

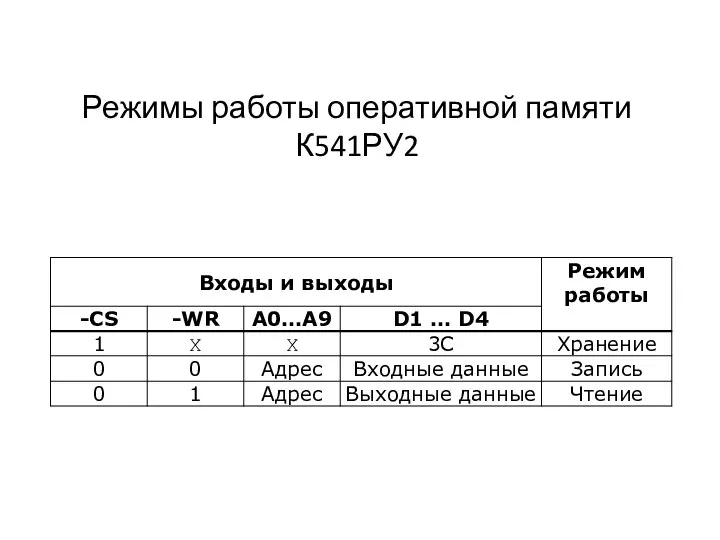

- 24. Режимы работы оперативной памяти К541РУ2

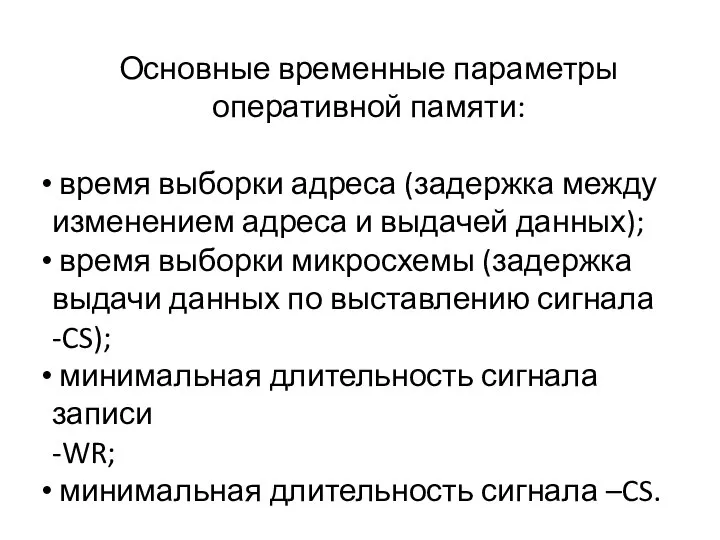

- 25. Основные временные параметры оперативной памяти: время выборки адреса (задержка между изменением адреса и выдачей данных); время

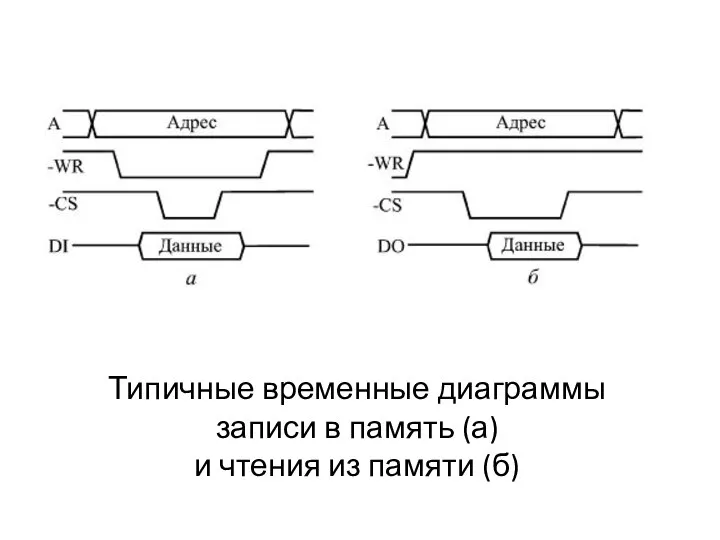

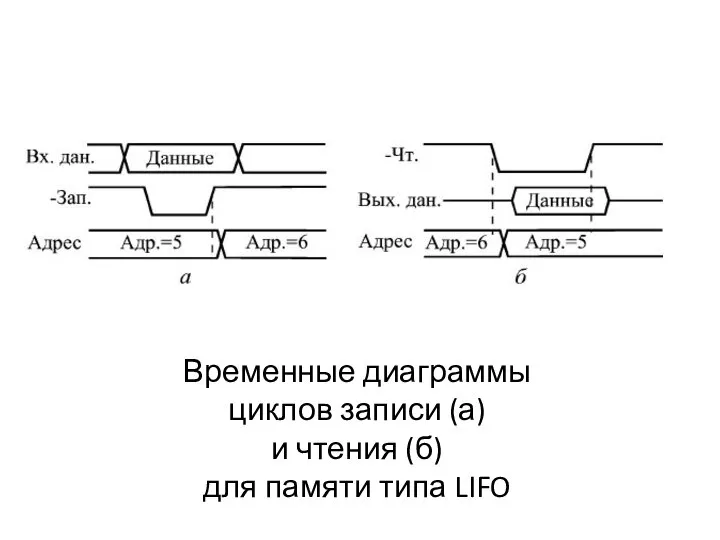

- 26. Типичные временные диаграммы записи в память (а) и чтения из памяти (б)

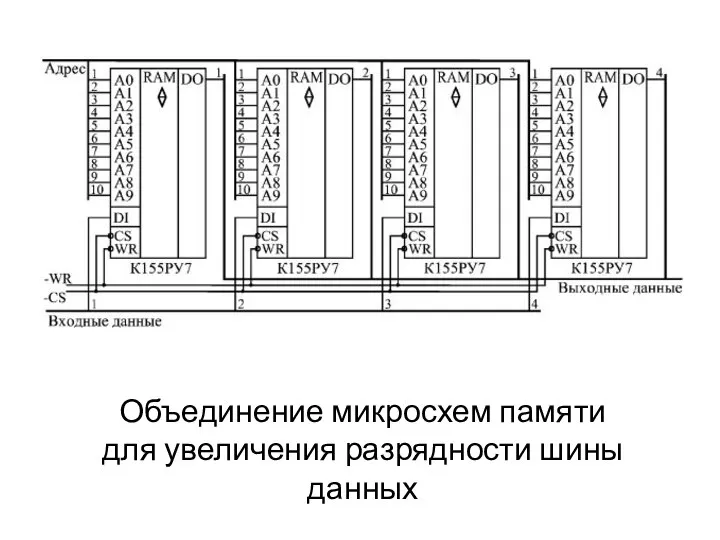

- 27. Объединение микросхем памяти для увеличения разрядности шины данных

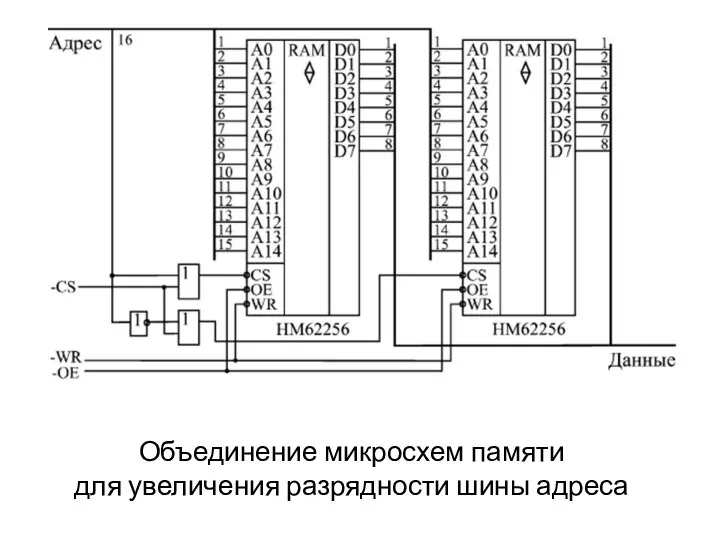

- 28. Объединение микросхем памяти для увеличения разрядности шины адреса

- 29. ОЗУ с параллельным (произвольным) доступом ОЗУ с последовательным доступом память типа "первым вошел - первым вышел"

- 30. Функциональная схема памяти типа FIFO

- 31. Функциональная схема памяти типа LIFO

- 32. Временные диаграммы циклов записи (а) и чтения (б) для памяти типа LIFO

- 33. Функциональная схема памяти для хранения массивов данных (FIFO)

- 35. Скачать презентацию

Презентация на тему Античная лирика

Презентация на тему Античная лирика Система счисления

Система счисления Вид графического изображения силуэт

Вид графического изображения силуэт Талант помогает исправиться

Талант помогает исправиться Динамические процессы в малой группе

Динамические процессы в малой группе Предложение

Предложение Карачаево-Черкесская республика – наш край родной

Карачаево-Черкесская республика – наш край родной КОНЦЕПЦИЯ УНИВЕРСАЛЬНОЙ ПЛАТФОРМЫ ДЛЯ ГРУЗОВОГО, ПАССАЖИРСКОГО И СПЕЦИАЛЬНОГО АВТОТРАНСПОРТА НА ОСНОВЕ ЭЛЕКТРИЧЕСКОЙ ТРАНСМИСС

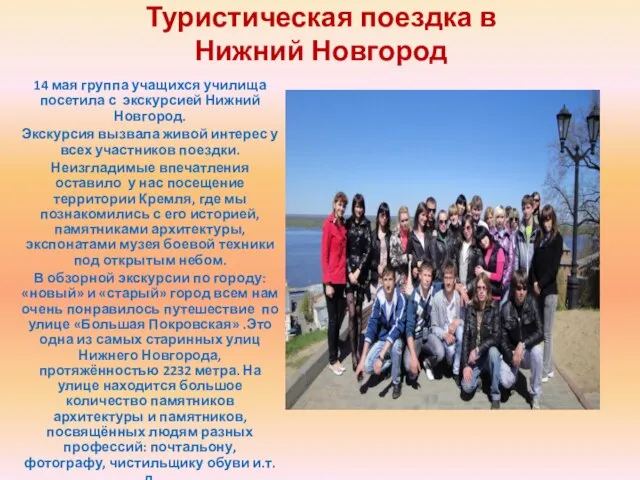

КОНЦЕПЦИЯ УНИВЕРСАЛЬНОЙ ПЛАТФОРМЫ ДЛЯ ГРУЗОВОГО, ПАССАЖИРСКОГО И СПЕЦИАЛЬНОГО АВТОТРАНСПОРТА НА ОСНОВЕ ЭЛЕКТРИЧЕСКОЙ ТРАНСМИСС Туристическая поездка в Нижний Новгород

Туристическая поездка в Нижний Новгород Новое направление Armelle. Функциональное питание

Новое направление Armelle. Функциональное питание Музеи мира

Музеи мира Компьютерные доспехи

Компьютерные доспехи Летний юбилей курсов

Летний юбилей курсов Миротворческие силы России

Миротворческие силы России Критерии оценки персонала

Критерии оценки персонала Blackstar наушники. Внешний вид и упаковка

Blackstar наушники. Внешний вид и упаковка Картины Мане

Картины Мане Презентация на тему Достопримечательности Москвы

Презентация на тему Достопримечательности Москвы  С Новым Годом

С Новым Годом Презентация на тему "Информационная культура личности" - скачать презентации по Педагогике

Презентация на тему "Информационная культура личности" - скачать презентации по Педагогике Социальные сети для HR

Социальные сети для HR Lektsiya dlya vechernikov_ Upravlenie kontentom v organizatsii

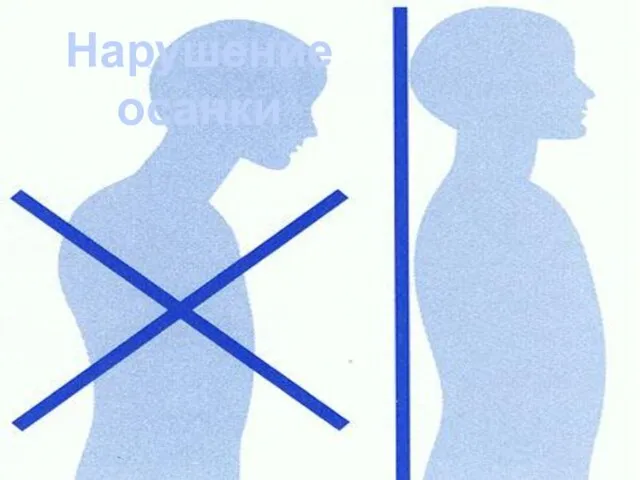

Lektsiya dlya vechernikov_ Upravlenie kontentom v organizatsii Презентация на тему Нарушение осанки

Презентация на тему Нарушение осанки Самарский государственный экономический университет

Самарский государственный экономический университет Сюжетные картины

Сюжетные картины Сводный каталог и МОБИС Аветисов М.А. Главный технолог ЦНСХБ

Сводный каталог и МОБИС Аветисов М.А. Главный технолог ЦНСХБ Языковая экология

Языковая экология Понятие самораскрытия в трудах С. Джурарда. Самораскрытие в психотерапии

Понятие самораскрытия в трудах С. Джурарда. Самораскрытие в психотерапии