Содержание

- 2. Распределение памяти предполагает удовлетворение потребностей как пользователей, так и системных средств. Эти требования в большей части

- 3. Функции системы управления памятью : - учет состояния свободных и уже распределенных областей памяти и модернизация

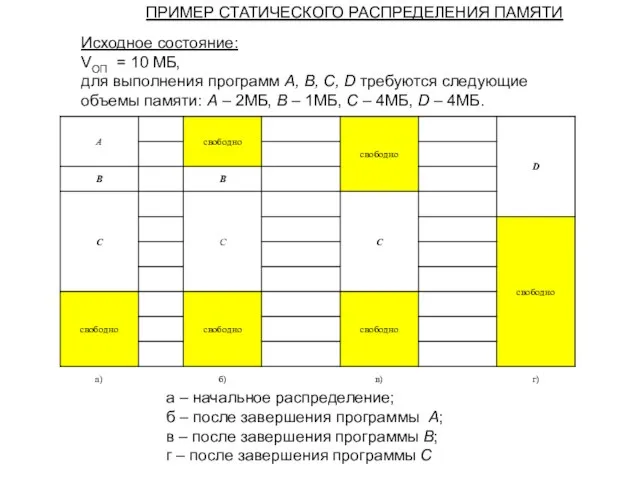

- 4. a – начальное распределение; б – после завершения программы A; в – после завершения программы B;

- 5. При динамическом распределении памяти каждой программе в начальный момент выделяется лишь часть от всей необходимой ей

- 6. Принцип виртуальной памяти предполагает, что пользователь при подготовке своей программы имеет дело не с физической ОП,

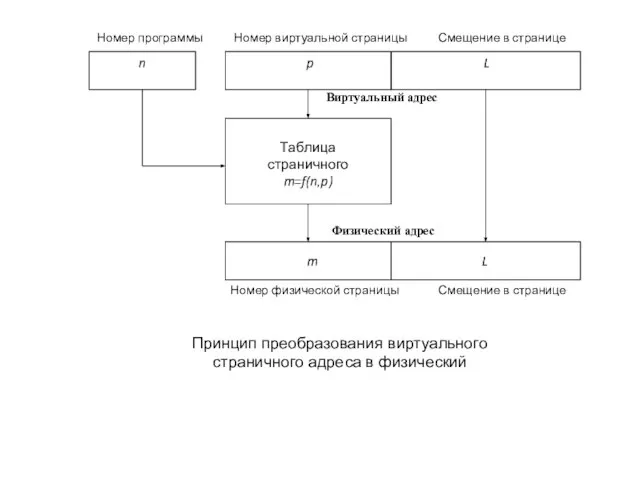

- 7. Принцип преобразования виртуального страничного адреса в физический

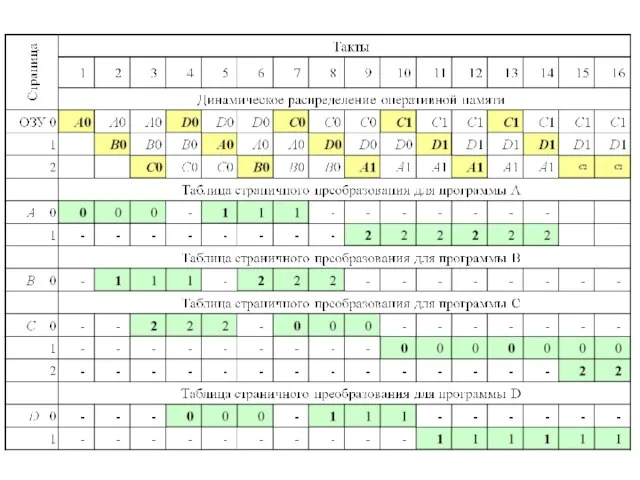

- 8. Пример преобразования адреса виртуальной страницы в адрес физической страницы Пусть компьютер использует адресное пространство, предполагающее разбиение

- 10. Архитектура компьютера различает физическое адресное пространство (ФАП) и логическое адресное пространство (ЛАП). Физическое адресное пространство –

- 11. Варианты организации логического адресного пространства : – плоское (линейное) ЛАП; состоит из массива байтов, не имеющего

- 12. Режимы формирования физического адреса: - режим реальных адресов (реальный режим); - режим защищенной памяти (защищенный режим).

- 13. ФА - физический адрес ЭА - эффективный адрес (смещение в сегменте, формируемое исходя из режима адресации

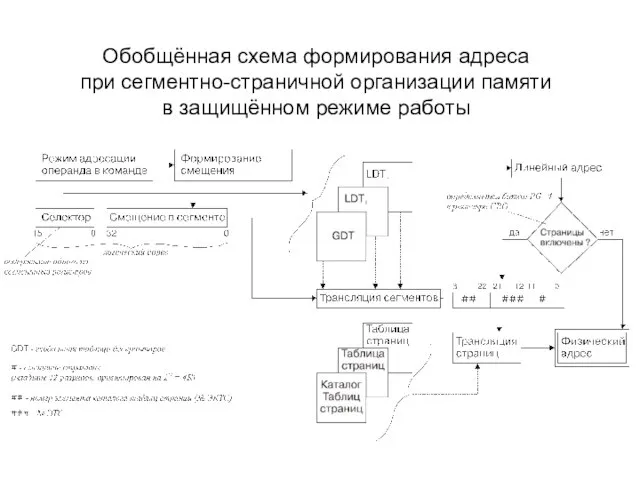

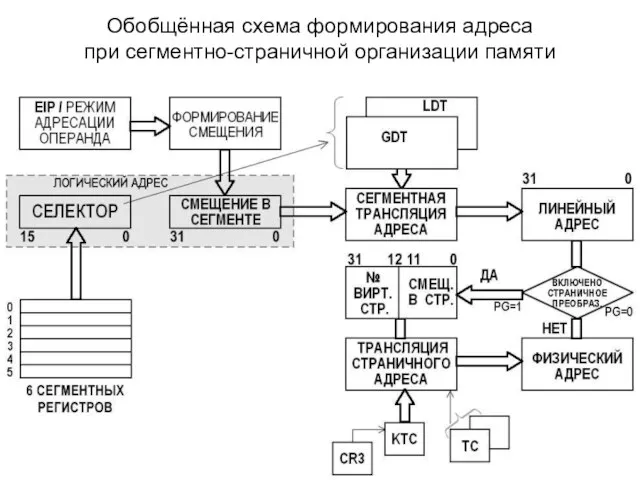

- 14. Обобщённая схема формирования адреса при сегментно-страничной организации памяти в защищённом режиме работы

- 15. Обобщённая схема формирования адреса при сегментно-страничной организации памяти

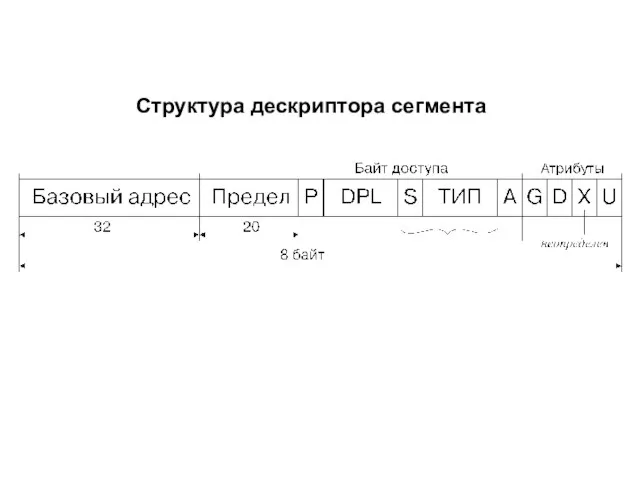

- 16. Структура дескриптора сегмента

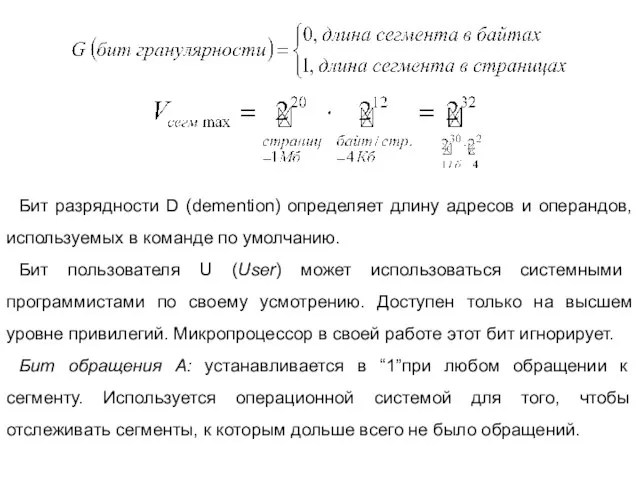

- 17. Бит разрядности D (demention) определяет длину адресов и операндов, используемых в команде по умолчанию. Бит пользователя

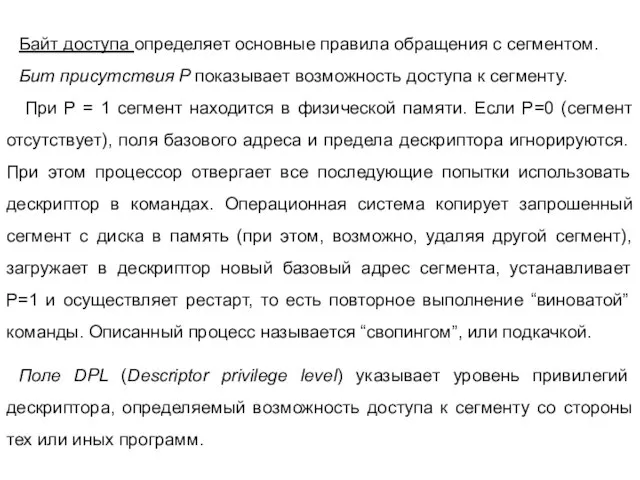

- 18. Байт доступа определяет основные правила обращения с сегментом. Бит присутствия P показывает возможность доступа к сегменту.

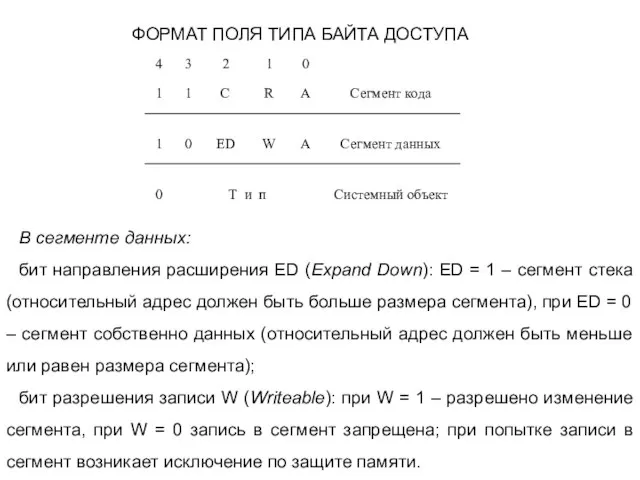

- 19. ФОРМАТ ПОЛЯ ТИПА БАЙТА ДОСТУПА В сегменте данных: бит направления расширения ED (Expand Down): ED =

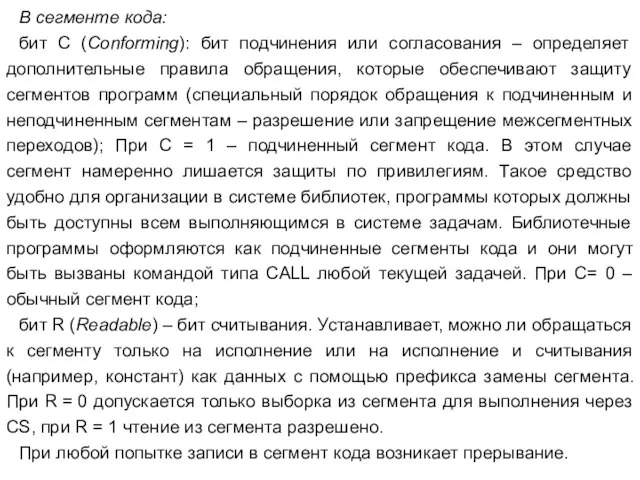

- 20. В сегменте кода: бит C (Conforming): бит подчинения или согласования – определяет дополнительные правила обращения, которые

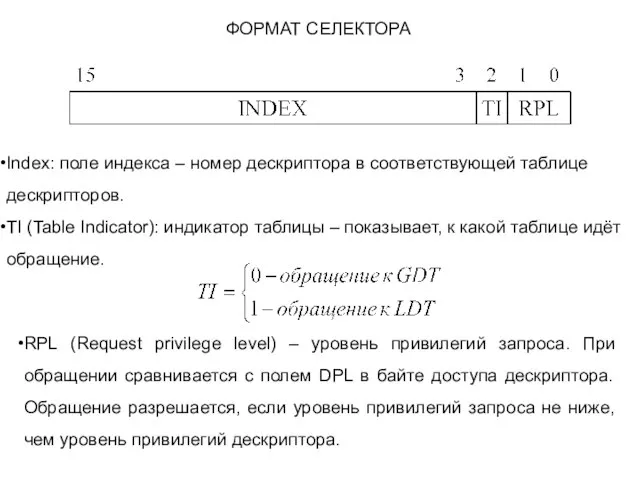

- 21. ФОРМАТ СЕЛЕКТОРА Index: поле индекса – номер дескриптора в соответствующей таблице дескрипторов. TI (Table Indicator): индикатор

- 23. Скачать презентацию

Учебный Центр БИТ

Учебный Центр БИТ Торф

Торф Представление корректирующих сведений персонифицированного учета

Представление корректирующих сведений персонифицированного учета Voľba študijného odboru

Voľba študijného odboru Технология .NET Remoting

Технология .NET Remoting Награды в сфере нанотехнологий

Награды в сфере нанотехнологий Global Trading St. Petersburg

Global Trading St. Petersburg Калькуляция

Калькуляция Python_-_задача_на_пару__HiNjSk

Python_-_задача_на_пару__HiNjSk Музыка эпохи классицизма

Музыка эпохи классицизма Международная транспортная инфраструктура, региональная интеграция и развитие (на примере Украины)

Международная транспортная инфраструктура, региональная интеграция и развитие (на примере Украины) Формирование международной проектной команды для выполнения многоцелевого проекта в области ИТ. Игорь Ковалев Директор по ИТ про

Формирование международной проектной команды для выполнения многоцелевого проекта в области ИТ. Игорь Ковалев Директор по ИТ про Оплата частями от Target Finance

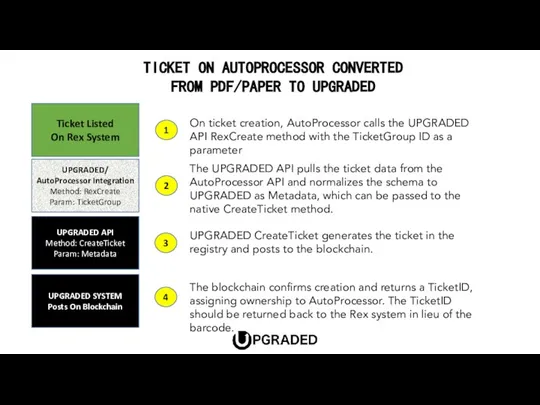

Оплата частями от Target Finance AutoProcessor UPGRADED Integration

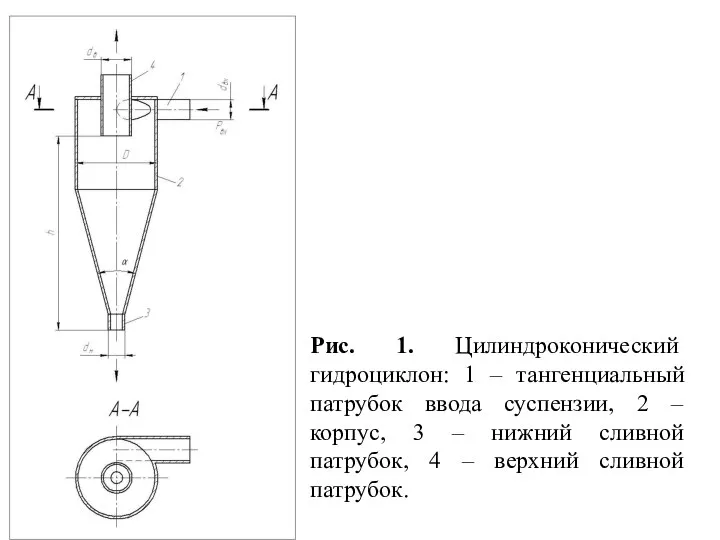

AutoProcessor UPGRADED Integration Гидромеханические установки. Цилиндроконический гидроциклон. (Лекция 5)

Гидромеханические установки. Цилиндроконический гидроциклон. (Лекция 5) Old English Grammar

Old English Grammar Равновесие тел

Равновесие тел Казахские национальные блюда

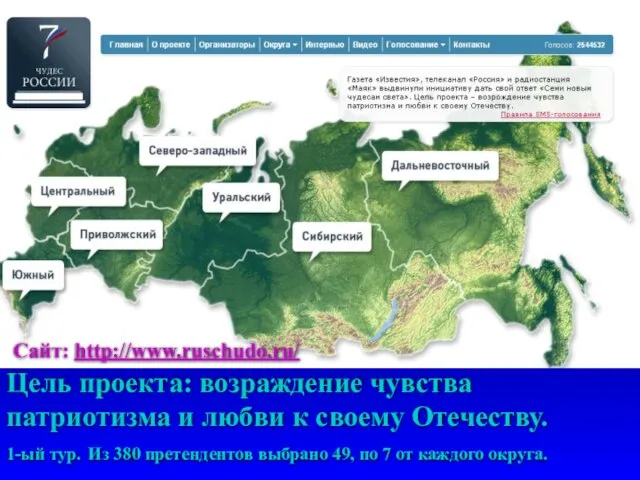

Казахские национальные блюда Сайт: http://www.ruschudo.ru/ Цель проекта: возраждение чувства патриотизма и любви к своему Отечеству.1-ый тур. Из 380 претендентов выбрано 49,

Сайт: http://www.ruschudo.ru/ Цель проекта: возраждение чувства патриотизма и любви к своему Отечеству.1-ый тур. Из 380 претендентов выбрано 49,  «Виды речевых нарушений у дошкольников»

«Виды речевых нарушений у дошкольников» Maxim Calujac

Maxim Calujac Проектирование образовательных кейсов с использованием дистанционных технологий

Проектирование образовательных кейсов с использованием дистанционных технологий Геополитика Узбекистана

Геополитика Узбекистана Юдина Татьяна Владимировна

Юдина Татьяна Владимировна Презентация на тему Различные группы антибиотиков: характеристика, получение, применение

Презентация на тему Различные группы антибиотиков: характеристика, получение, применение  Использование технологии развития критического мышления на уроке английского языка по теме:«Телевидение: за и против».

Использование технологии развития критического мышления на уроке английского языка по теме:«Телевидение: за и против». Пейзаж в линейной перспективе

Пейзаж в линейной перспективе игра

игра