Содержание

- 2. Фирма STMicroelectronics В настоящее время фирма STM - ведущий мировой производитель п/п продукции для микроэлектроники. В

- 3. Фирма ARM Limited ARM Limited - известная британская компания в области информационных технологий. “ARM” - Advanced

- 4. Краткая характеристика серий микроконтроллеров STM32

- 5. В настоящее время STM32 производит около 300 вариантов МК, которые можно классифицировать по 2 признакам: критерию

- 6. Основные характеристики ядра Cortex-M4 микроконтроллеров STM32

- 7. Микроконтроллер STM32F410RBТ • Ядро ARM 32‑битное Cortex-M4. • Частота тактирования: 168 МГц. • Поддержка DSP-инструкций. •

- 8. • Внешний источник тактирования 4–26 МГц и для RTC — 32,768 кГц. • Модули отладки SWD/JTAG,

- 9. • До 17 таймеров (16 и 32 разряда). Некоторые оснащены каналами входного захвата и выходного сравнения

- 10. Режимы пониженного напряжения: Режим Sleep. Только ядро останавливает свою работу. Вся периферия продолжает работать и пробуждает

- 11. 2. Функциональная схема STM32F4xx

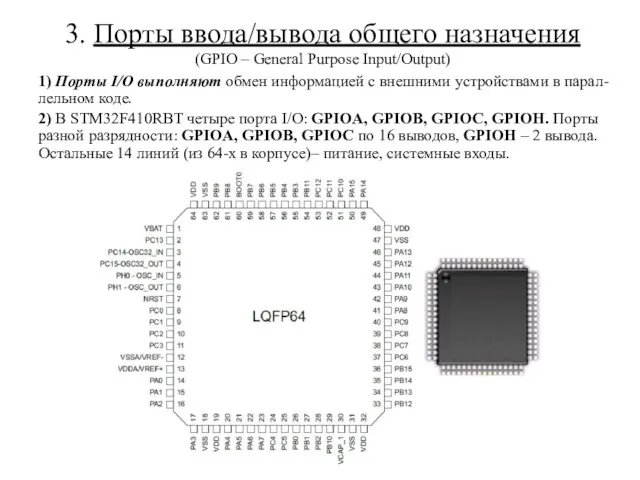

- 12. 3. Порты ввода/вывода общего назначения (GPIO – General Purpose Input/Output) 1) Порты I/O выполняют обмен информацией

- 13. 3) Назначение выводов, не относящихся к портам: VSS/VDD – цифровая земля/цифровое питание; VBAT – дополнительное батарейное

- 14. 5) Основные свойства портов ввода/вывода До 16 линий ввода/вывода могут находиться под управлением порта; Для каждой

- 15. 6) ПЛМ портов I/O: - GPIOx_MODER – регистр режима работы; GPIOx_OTYPER – задания типа выхода; GPIOx_OSPEEDR

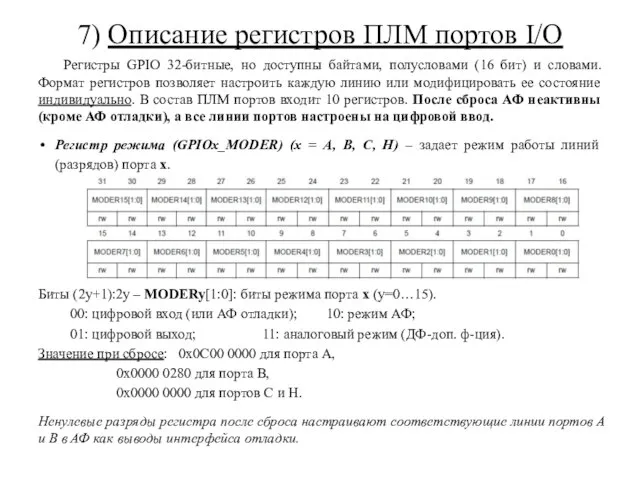

- 16. 7) Описание регистров ПЛМ портов I/O Регистры GPIO 32-битные, но доступны байтами, полусловами (16 бит) и

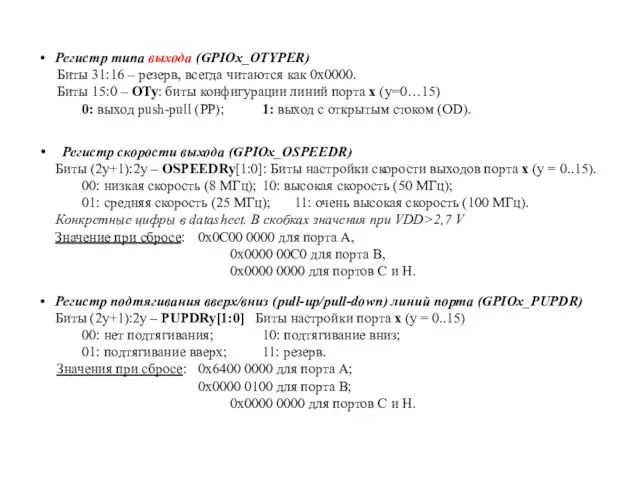

- 17. Регистр типа выхода (GPIOx_OTYPER) Биты 31:16 – резерв, всегда читаются как 0х0000. Биты 15:0 – ОТу:

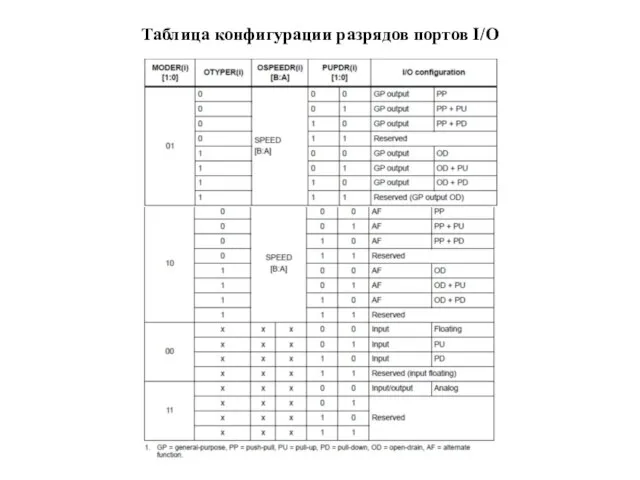

- 18. Таблица конфигурации разрядов портов I/O

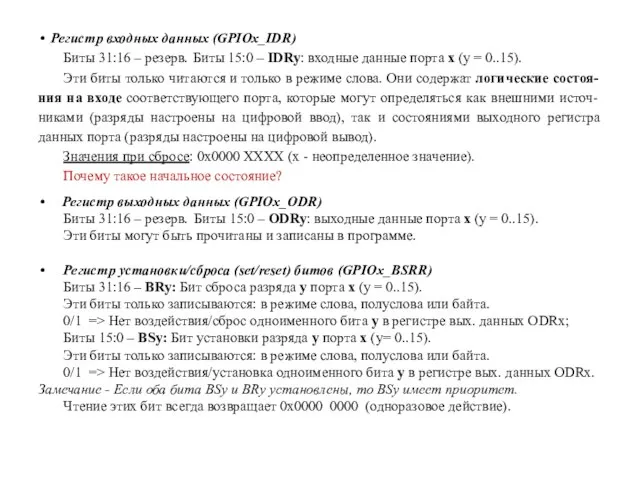

- 19. Регистр входных данных (GPIOx_IDR) Биты 31:16 – резерв. Биты 15:0 – IDRy: входные данные порта х

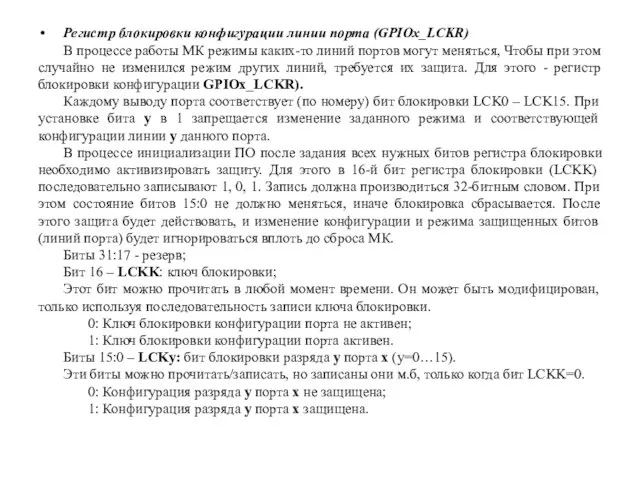

- 20. Регистр блокировки конфигурации линии порта (GPIOx_LCKR) В процессе работы МК режимы каких-то линий портов могут меняться,

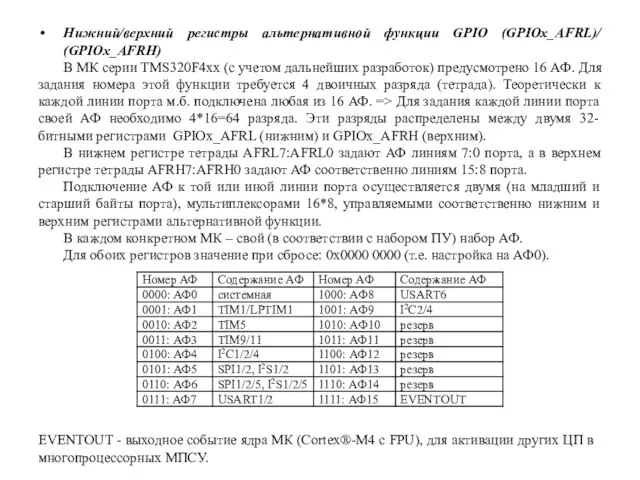

- 21. Нижний/верхний регистры альтернативной функции GPIO (GPIOx_AFRL)/ (GPIOx_AFRH) В МК серии TMS320F4xx (с учетом дальнейших разработок) предусмотрено

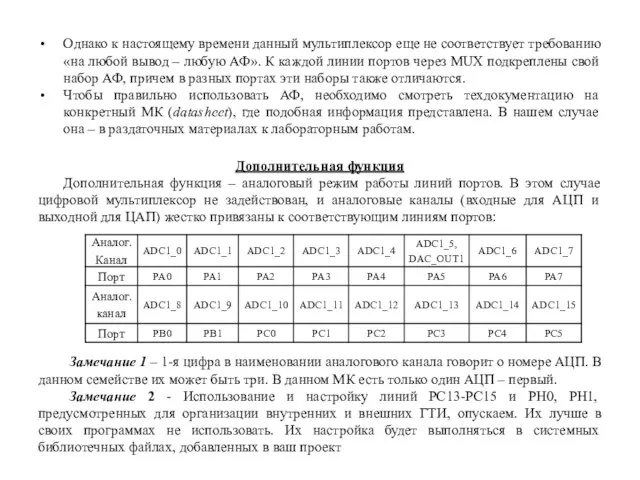

- 22. Однако к настоящему времени данный мультиплексор еще не соответствует требованию «на любой вывод – любую АФ».

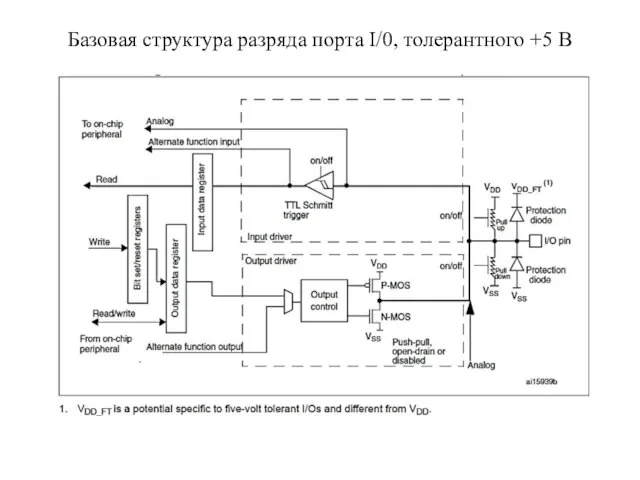

- 23. Базовая структура разряда порта I/0, толерантного +5 В

- 24. 10) Операции над отдельными разрядами регистров ПЛМ портов I/O. Рекомендации к программам. Часто в МПСУ приходится

- 25. В файле «STM32f1410rx.h» для каждого разряда портов и регистров ПУ прописана своя 16-/32-битная слово-маска. Пример 1:

- 26. Обобщенные выражения для операций маскирования над одним разрядом: Установка в 1 бита у регистра REG порта

- 27. записью в порт соответствующего числа и нуля; while (1) { GPIOC->ODR = 0x0020; // недостаток? for

- 28. - установкой бита в 1 и инверсией бита; while (1) { GPIOC->ODR |= GPIO_ODR_OD5; for (i=0;

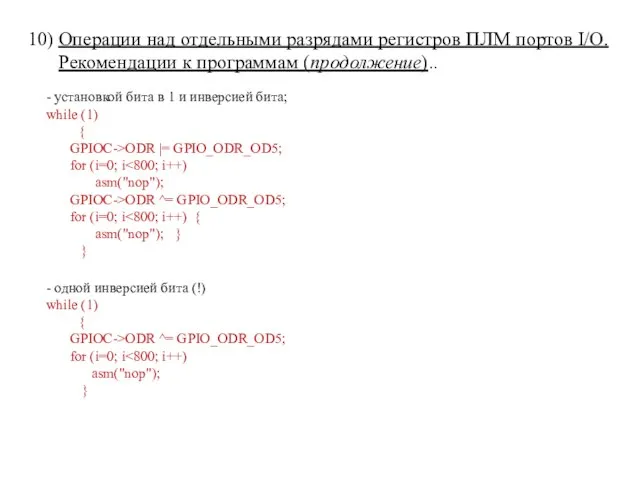

- 29. Работа с кнопкой пользователя (PC13) while (1) { if(GPIOC->IDR & GPIO_IDR_ID13) //анализ маскирования разряда PC13 {

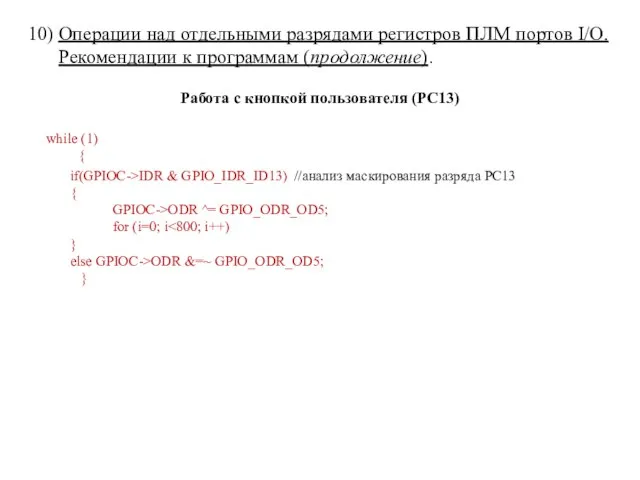

- 31. Скачать презентацию

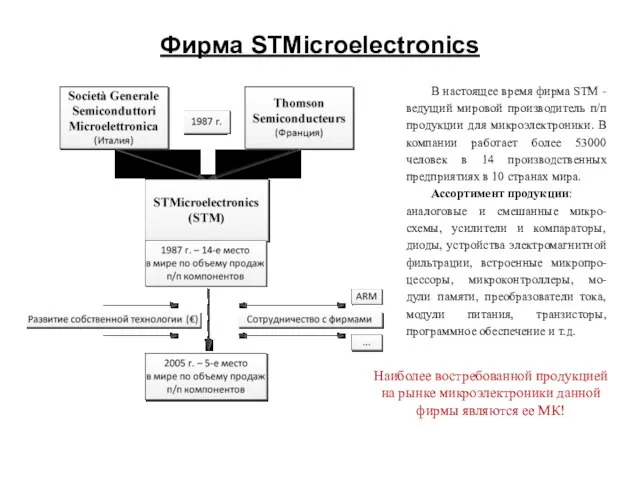

Слайд 2Фирма STMicroelectronics

В настоящее время фирма STM - ведущий мировой производитель п/п продукции

Фирма STMicroelectronics

В настоящее время фирма STM - ведущий мировой производитель п/п продукции

Ассортимент продукции:

аналоговые и смешанные микро-схемы, усилители и компараторы, диоды, устройства электромагнитной фильтрации, встроенные микропро-цессоры, микроконтроллеры, мо-дули памяти, преобразователи тока, модули питания, транзисторы, программное обеспечение и т.д.

Наиболее востребованной продукцией на рынке микроэлектроники данной фирмы являются ее МК!

Слайд 3Фирма ARM Limited

ARM Limited - известная британская компания в области информационных технологий.

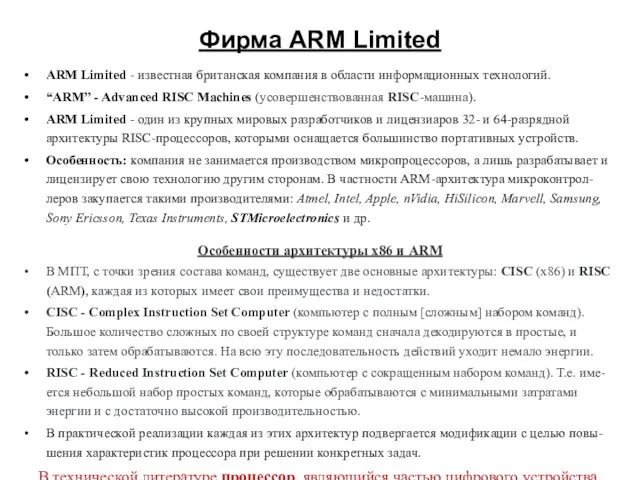

Фирма ARM Limited

ARM Limited - известная британская компания в области информационных технологий.

“ARM” - Advanced RISC Machines (усовершенствованная RISC-машина).

ARM Limited - один из крупных мировых разработчиков и лицензиаров 32- и 64-разрядной архитектуры RISC-процессоров, которыми оснащается большинство портативных устройств.

Особенность: компания не занимается производством микропроцессоров, а лишь разрабатывает и лицензирует свою технологию другим сторонам. В частности ARM-архитектура микроконтрол-леров закупается такими производителями: Atmel, Intel, Apple, nVidia, HiSilicon, Marvell, Samsung, Sony Ericsson, Texas Instruments, STMicroelectronics и др.

Особенности архитектуры x86 и ARM

В МПТ, с точки зрения состава команд, существует две основные архитектуры: CISC (x86) и RISC (ARM), каждая из которых имеет свои преимущества и недостатки.

CISC - Complex Instruction Set Computer (компьютер с полным [сложным] набором команд). Большое количество сложных по своей структуре команд сначала декодируются в простые, и только затем обрабатываются. На всю эту последовательность действий уходит немало энергии.

RISC - Reduced Instruction Set Computer (компьютер с сокращенным набором команд). Т.е. име-ется небольшой набор простых команд, которые обрабатываются с минимальными затратами энергии и с достаточно высокой производительностью.

В практической реализации каждая из этих архитектур подвергается модификации с целью повы-шения характеристик процессора при решении конкретных задач.

В технической литературе процессор, являющийся частью цифрового устройства, реализованного на кристалле, называется ядром (Core).

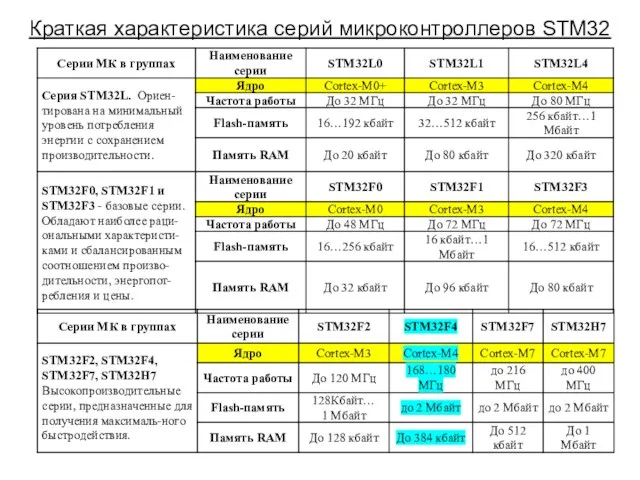

Слайд 4Краткая характеристика серий микроконтроллеров STM32

Краткая характеристика серий микроконтроллеров STM32

Слайд 5В настоящее время STM32 производит около 300 вариантов МК, которые можно классифицировать

В настоящее время STM32 производит около 300 вариантов МК, которые можно классифицировать

По критерию оптимизации:

- с пониженным энергопотреблением (энергосберегающие) STM32L0/1/4;

- с оптимальным соотношением производительности, энергопотребления и цены (базовые серии) STM32F0, STM32F1 и STM32F3);

- с высокой производительностью STM32F2/F4/F7/H7.

По используемому ARM-ядру:

- с ARM-ядром Cortex-M0 (STM32L0/F0);

- с ARM-ядром Cortex-M3 (STM32L1/F1/F2);

- с ARM-ядром Cortex-M4 (STM32L4/F3/F4);

- с ARM-ядром Cortex-M7 (STM32F7/H7).

Приведенные выше обозначения – это обозначение серии МК. В обозначении конкретной модели добавляются цифры и буквы.

Так, далее мы будем изучать МК типа STM32F410RB, относящийся к высокопроизводи-тельным МК с ARM-ядром Cortex-M4.

Классификация серий микроконтроллеров STM32

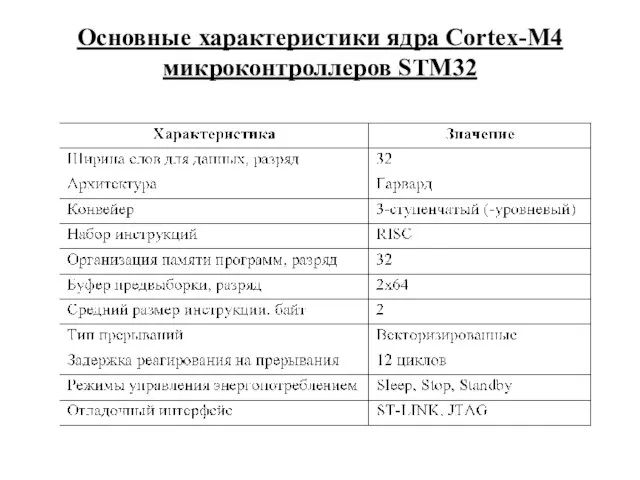

Слайд 6Основные характеристики ядра Cortex-M4 микроконтроллеров STM32

Основные характеристики ядра Cortex-M4 микроконтроллеров STM32

Слайд 7Микроконтроллер STM32F410RBТ

• Ядро ARM 32‑битное Cortex-M4.

• Частота тактирования: 168 МГц.

• Поддержка DSP-инструкций.

•

Микроконтроллер STM32F410RBТ

• Ядро ARM 32‑битное Cortex-M4.

• Частота тактирования: 168 МГц.

• Поддержка DSP-инструкций.

•

• До 1 Mбайт флэш-памяти с ускорителем памяти (ART-Accelerator), обеспечивает работу с флэш-памятью с такой же скоростью, что и с ОЗУ.

• До 192 + 4 кбайт SRAM-памяти (статической оперативной памяти), включая область резервного питания.

• Напряжение питания: 1,8–3,6 В. Режимы пониженного энергопотребления: Sleep, Stop, Standby. Резервное (батарейное) питание.

• Внутренние RC-генераторы на 16 МГц и 32 кГц (для Real Time Clock - RTC).

1. Характеристики семейства STM32F4xx:

Слайд 8• Внешний источник тактирования 4–26 МГц и для RTC — 32,768 кГц.

•

• Внешний источник тактирования 4–26 МГц и для RTC — 32,768 кГц.

•

• Аппаратный генератор случайных чисел (Random number generator - RNG).

• Часы реального времени (Real Time Clock - RTC).

• Модуль шифрования (позволяет «на лету» реализовать различные алгоритмы шифрования информации).

• Эффективная система прерываний по внутренним (от ПУ) и внешним событиям.

• До трех 12‑битных АЦП на 24 входных канала.

• До двух 12‑битных ЦАП.

• ПДП-контроллер на 16 потоков с поддержкой пакетной передачи (DMA - Direct Memory Access).

Характеристики семейства STM32F4xx

(продолжение):

Слайд 9• До 17 таймеров (16 и 32 разряда). Некоторые оснащены каналами входного

• До 17 таймеров (16 и 32 разряда). Некоторые оснащены каналами входного

• Два сторожевых таймера (WDG и IWDG).

• Коммуникационные интерфейсы: I2C, USART, SPI, I2S, CAN (2,0), USB 2.0.

• Интерфейс Ethernet.

• Контроллер карт памяти SDIO.

• Интерфейс цифровой камеры.

• Контроллер внешней статической памяти и графических дисплеев FSMC.

• Порты ввода/вывода общего назначения (GPIO - General-Purpose Input Output). Все ПУ связаны с внешним миром через порты (альтернативная функция портов).

Особенность: большая часть линий портов в режиме цифрового ввода может генерировать запрос на прерывание.

• Расширенный температурный диапазон: –40…105 °C.

Характеристики семейства STM32F4xx

(продолжение):

Слайд 10Режимы пониженного напряжения:

Режим Sleep. Только ядро останавливает свою работу. Вся периферия продолжает

Режимы пониженного напряжения:

Режим Sleep. Только ядро останавливает свою работу. Вся периферия продолжает

Режим Stop. Все тактирование в зоне 1,2 В останавливается. Все схемы высокочастотного тактирования отключаются. В данном режиме МК продолжает работать от низкоскоростных источников тактирования. Состояние SRAM и регистров при этом сохраняется. ЦП переходит в рабочий режим по заранее сконфигурированному событию.

Режим Standby. Обеспечивает самое низкое потребление. Питание 1,2 В полностью отключается. Данные SRAM и регистров не сохраняются, за исключением резервного домена и резервной SRAM. Для выхода из режима необходимо прерывание от часов РВ, общий сброс или возрастающий фронт на ножке WKUP.

Характеристики семейства STM32F4xx

(продолжение):

Слайд 112. Функциональная схема STM32F4xx

2. Функциональная схема STM32F4xx

Слайд 123. Порты ввода/вывода общего назначения

(GPIO – General Purpose Input/Output)

1) Порты I/O

3. Порты ввода/вывода общего назначения

(GPIO – General Purpose Input/Output)

1) Порты I/O

2) В STM32F410RBТ четыре порта I/O: GPIOA, GPIOB, GPIOС, GPIOН. Порты разной разрядности: GPIOA, GPIOB, GPIOС по 16 выводов, GPIOН – 2 вывода. Остальные 14 линий (из 64-х в корпусе)– питание, системные входы.

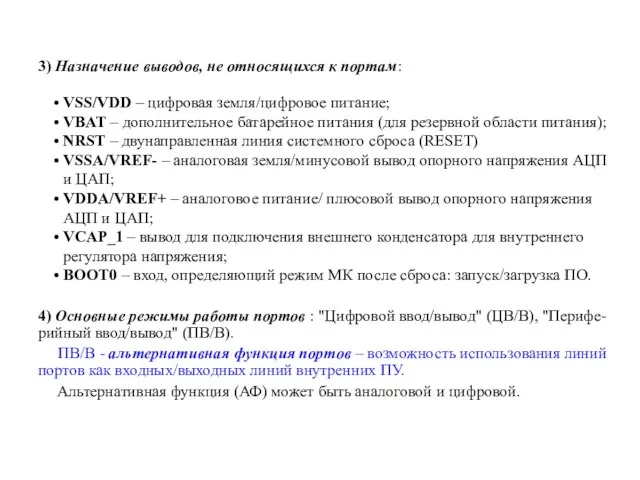

Слайд 133) Назначение выводов, не относящихся к портам:

VSS/VDD – цифровая земля/цифровое питание;

VBAT –

3) Назначение выводов, не относящихся к портам:

VSS/VDD – цифровая земля/цифровое питание;

VBAT –

NRST – двунаправленная линия системного сброса (RESET)

VSSA/VREF- – аналоговая земля/минусовой вывод опорного напряжения АЦП и ЦАП;

VDDA/VREF+ – аналоговое питание/ плюсовой вывод опорного напряжения АЦП и ЦАП;

VCAP_1 – вывод для подключения внешнего конденсатора для внутреннего регулятора напряжения;

BOOT0 – вход, определяющий режим МК после сброса: запуск/загрузка ПО.

4) Основные режимы работы портов : "Цифровой ввод/вывод" (ЦВ/В), "Перифе-рийный ввод/вывод" (ПВ/В).

ПВ/В - альтернативная функция портов – возможность использования линий портов как входных/выходных линий внутренних ПУ.

Альтернативная функция (АФ) может быть аналоговой и цифровой.

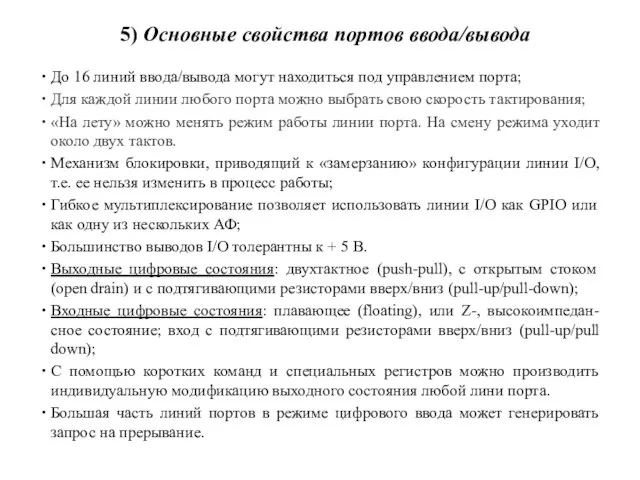

Слайд 145) Основные свойства портов ввода/вывода

До 16 линий ввода/вывода могут находиться под управлением

5) Основные свойства портов ввода/вывода

До 16 линий ввода/вывода могут находиться под управлением

Для каждой линии любого порта можно выбрать свою скорость тактирования;

«На лету» можно менять режим работы линии порта. На смену режима уходит около двух тактов.

Механизм блокировки, приводящий к «замерзанию» конфигурации линии I/O, т.е. ее нельзя изменить в процесс работы;

Гибкое мультиплексирование позволяет использовать линии I/O как GPIO или как одну из нескольких АФ;

Большинство выводов I/O толерантны к + 5 В.

Выходные цифровые состояния: двухтактное (push-pull), с открытым стоком (open drain) и с подтягивающими резисторами вверх/вниз (pull-up/pull-down);

Входные цифровые состояния: плавающее (floating), или Z-, высокоимпедан-сное состояние; вход с подтягивающими резисторами вверх/вниз (pull-up/pull down);

С помощью коротких команд и специальных регистров можно производить индивидуальную модификацию выходного состояния любой лини порта.

Большая часть линий портов в режиме цифрового ввода может генерировать запрос на прерывание.

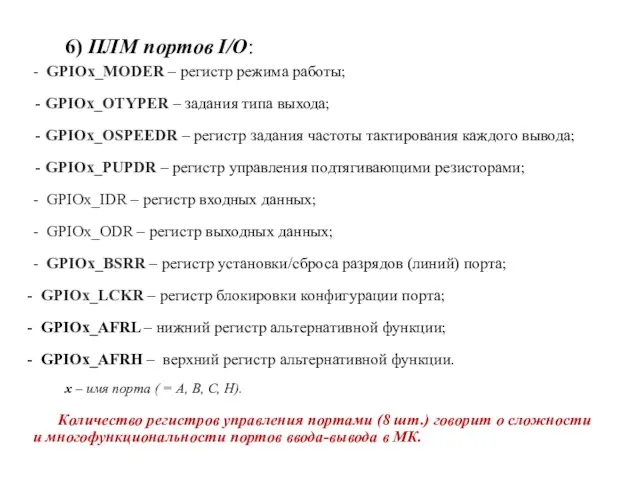

Слайд 15 6) ПЛМ портов I/O:

- GPIOx_MODER – регистр режима работы;

GPIOx_OTYPER – задания типа

6) ПЛМ портов I/O:

- GPIOx_MODER – регистр режима работы;

GPIOx_OTYPER – задания типа

GPIOx_OSPEEDR – регистр задания частоты тактирования каждого вывода;

GPIOx_PUPDR – регистр управления подтягивающими резисторами;

- GPIOx_IDR – регистр входных данных;

- GPIOx_ODR – регистр выходных данных;

- GPIOx_BSRR – регистр установки/сброса разрядов (линий) порта;

GPIOx_LCKR – регистр блокировки конфигурации порта;

GPIOx_AFRL – нижний регистр альтернативной функции;

GPIOx_AFRH – верхний регистр альтернативной функции.

х – имя порта ( = A, B, С, Н).

Количество регистров управления портами (8 шт.) говорит о сложности и многофункциональности портов ввода-вывода в МК.

Слайд 167) Описание регистров ПЛМ портов I/O

Регистры GPIO 32-битные, но доступны байтами, полусловами

7) Описание регистров ПЛМ портов I/O

Регистры GPIO 32-битные, но доступны байтами, полусловами

Регистр режима (GPIOx_MODER) (x = A, В, C, H) – задает режим работы линий (разрядов) порта х.

Биты (2у+1):2у – MODERy[1:0]: биты режима порта х (у=0…15).

00: цифровой вход (или АФ отладки); 10: режим АФ;

01: цифровой выход; 11: аналоговый режим (ДФ-доп. ф-ция).

Значение при сбросе: 0х0С00 0000 для порта А,

0х0000 0280 для порта В,

0х0000 0000 для портов С и Н.

Ненулевые разряды регистра после сброса настраивают соответствующие линии портов А и В в АФ как выводы интерфейса отладки.

Слайд 17Регистр типа выхода (GPIOx_OTYPER)

Биты 31:16 – резерв, всегда читаются как 0х0000.

Биты 15:0

Регистр типа выхода (GPIOx_OTYPER)

Биты 31:16 – резерв, всегда читаются как 0х0000.

Биты 15:0

0: выход push-pull (РР); 1: выход с открытым стоком (OD).

Регистр скорости выхода (GPIOx_OSPEEDR)

Биты (2y+1):2y – OSPEEDRy[1:0]: Биты настройки скорости выходов порта х (y = 0..15).

00: низкая скорость (8 МГц); 10: высокая скорость (50 МГц);

01: средняя скорость (25 МГц); 11: очень высокая скорость (100 МГц).

Конкретные цифры в datasheet. В скобках значения при VDD>2,7 V

Значение при сбросе: 0x0C00 0000 для порта A,

0x0000 00C0 для порта B,

0x0000 0000 для портов С и Н.

Регистр подтягивания вверх/вниз (pull-up/pull-down) линий порта (GPIOx_PUPDR)

Биты (2y+1):2y – PUPDRy[1:0] Биты настройки порта х (y = 0..15)

00: нет подтягивания; 10: подтягивание вниз;

01: подтягивание вверх; 11: резерв.

Значения при сбросе: 0x6400 0000 для порта A;

0x0000 0100 для порта B;

0x0000 0000 для портов С и Н.

Слайд 18Таблица конфигурации разрядов портов I/O

Таблица конфигурации разрядов портов I/O

Слайд 19Регистр входных данных (GPIOx_IDR)

Биты 31:16 – резерв. Биты 15:0 – IDRy: входные

Регистр входных данных (GPIOx_IDR)

Биты 31:16 – резерв. Биты 15:0 – IDRy: входные

Эти биты только читаются и только в режиме слова. Они содержат логические состоя-ния на входе соответствующего порта, которые могут определяться как внешними источ-никами (разряды настроены на цифровой ввод), так и состояниями выходного регистра данных порта (разряды настроены на цифровой вывод).

Значения при сбросе: 0x0000 ХХХХ (х - неопределенное значение).

Почему такое начальное состояние?

Регистр выходных данных (GPIOx_ODR)

Биты 31:16 – резерв. Биты 15:0 – ODRy: выходные данные порта х (y = 0..15).

Эти биты могут быть прочитаны и записаны в программе.

Регистр установки/сброса (set/reset) битов (GPIOx_BSRR)

Биты 31:16 – BRy: Бит сброса разряда у порта х (y = 0..15).

Эти биты только записываются: в режиме слова, полуслова или байта.

0/1 => Нет воздействия/сброс одноименного бита у в регистре вых. данных ODRx;

Биты 15:0 – BSy: Бит установки разряда y порта х (y= 0..15).

Эти биты только записываются: в режиме слова, полуслова или байта.

0/1 => Нет воздействия/установка одноименного бита у в регистре вых. данных ODRx.

Замечание - Если оба бита BSу и BRу установлены, то BSу имеет приоритет.

Чтение этих бит всегда возвращает 0x0000 0000 (одноразовое действие).

Слайд 20Регистр блокировки конфигурации линии порта (GPIOx_LCKR)

В процессе работы МК режимы каких-то линий

Регистр блокировки конфигурации линии порта (GPIOx_LCKR)

В процессе работы МК режимы каких-то линий

Каждому выводу порта соответствует (по номеру) бит блокировки LCK0 – LCK15. При установке бита у в 1 запрещается изменение заданного режима и соответствующей конфигурации линии у данного порта.

В процессе инициализации ПО после задания всех нужных битов регистра блокировки необходимо активизировать защиту. Для этого в 16-й бит регистра блокировки (LCKK) последовательно записывают 1, 0, 1. Запись должна производиться 32-битным словом. При этом состояние битов 15:0 не должно меняться, иначе блокировка сбрасывается. После этого защита будет действовать, и изменение конфигурации и режима защищенных битов (линий порта) будет игнорироваться вплоть до сброса МК.

Биты 31:17 - резерв;

Бит 16 – LCKK: ключ блокировки;

Этот бит можно прочитать в любой момент времени. Он может быть модифицирован, только используя последовательность записи ключа блокировки.

0: Ключ блокировки конфигурации порта не активен;

1: Ключ блокировки конфигурации порта активен.

Биты 15:0 – LCKy: бит блокировки разряда у порта х (у=0…15).

Эти биты можно прочитать/записать, но записаны они м.б, только когда бит LCKK=0.

0: Конфигурация разряда у порта х не защищена;

1: Конфигурация разряда у порта х защищена.

Слайд 21Нижний/верхний регистры альтернативной функции GPIO (GPIOx_AFRL)/ (GPIOx_AFRH)

В МК серии TMS320F4xx (с учетом

Нижний/верхний регистры альтернативной функции GPIO (GPIOx_AFRL)/ (GPIOx_AFRH)

В МК серии TMS320F4xx (с учетом

В нижнем регистре тетрады AFRL7:AFRL0 задают АФ линиям 7:0 порта, а в верхнем регистре тетрады AFRН7:AFRН0 задают АФ соответственно линиям 15:8 порта.

Подключение АФ к той или иной линии порта осуществляется двумя (на младший и старший байты порта), мультиплексорами 16*8, управляемыми соответственно нижним и верхним регистрами альтернативной функции.

В каждом конкретном МК – свой (в соответствии с набором ПУ) набор АФ.

Для обоих регистров значение при сбросе: 0x0000 0000 (т.е. настройка на АФ0).

EVENTOUT - выходное событие ядра МК (Cortex®-M4 с FPU), для активации других ЦП в многопроцессорных МПСУ.

Слайд 22Однако к настоящему времени данный мультиплексор еще не соответствует требованию «на любой

Однако к настоящему времени данный мультиплексор еще не соответствует требованию «на любой

Чтобы правильно использовать АФ, необходимо смотреть техдокументацию на конкретный МК (datasheet), где подобная информация представлена. В нашем случае она – в раздаточных материалах к лабораторным работам.

Дополнительная функция

Дополнительная функция – аналоговый режим работы линий портов. В этом случае цифровой мультиплексор не задействован, и аналоговые каналы (входные для АЦП и выходной для ЦАП) жестко привязаны к соответствующим линиям портов:

Замечание 1 – 1-я цифра в наименовании аналогового канала говорит о номере АЦП. В данном семействе их может быть три. В данном МК есть только один АЦП – первый.

Замечание 2 - Использование и настройку линий РС13-РС15 и РН0, РН1, предусмотренных для организации внутренних и внешних ГТИ, опускаем. Их лучше в своих программах не использовать. Их настройка будет выполняться в системных библиотечных файлах, добавленных в ваш проект

Слайд 23Базовая структура разряда порта I/0, толерантного +5 В

Базовая структура разряда порта I/0, толерантного +5 В

Слайд 2410) Операции над отдельными разрядами регистров ПЛМ портов I/O. Рекомендации к программам.

Часто

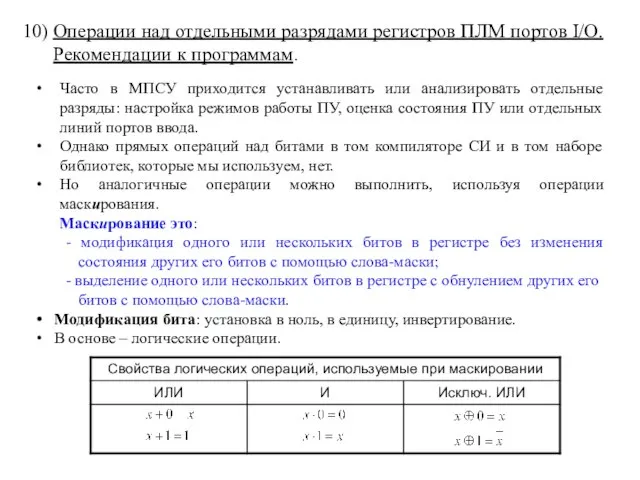

10) Операции над отдельными разрядами регистров ПЛМ портов I/O. Рекомендации к программам.

Часто

Однако прямых операций над битами в том компиляторе CИ и в том наборе библиотек, которые мы используем, нет.

Но аналогичные операции можно выполнить, используя операции маскирования.

Маскирование это:

- модификация одного или нескольких битов в регистре без изменения состояния других его битов с помощью слова-маски;

- выделение одного или нескольких битов в регистре с обнулением других его битов с помощью слова-маски.

Модификация бита: установка в ноль, в единицу, инвертирование.

В основе – логические операции.

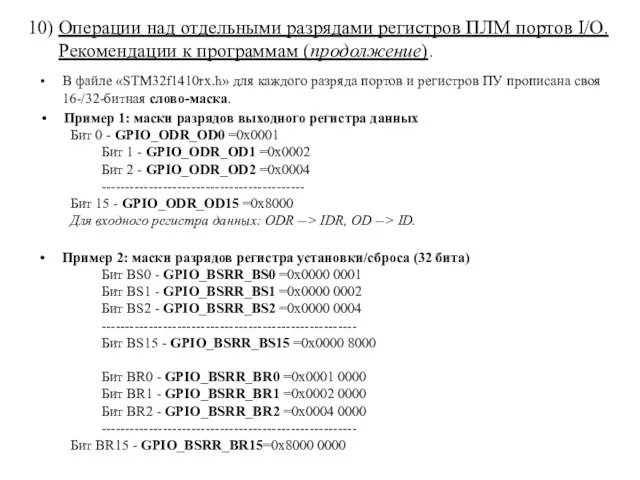

Слайд 25В файле «STM32f1410rx.h» для каждого разряда портов и регистров ПУ прописана своя

В файле «STM32f1410rx.h» для каждого разряда портов и регистров ПУ прописана своя

Пример 1: маски разрядов выходного регистра данных

Бит 0 - GPIO_ODR_OD0 =0x0001

Бит 1 - GPIO_ODR_OD1 =0x0002

Бит 2 - GPIO_ODR_OD2 =0x0004

-------------------------------------------

Бит 15 - GPIO_ODR_OD15 =0x8000

Для входного регистра данных: ODR --> IDR, OD --> ID.

Пример 2: маски разрядов регистра установки/сброса (32 бита)

Бит BS0 - GPIO_BSRR_BS0 =0x0000 0001

Бит BS1 - GPIO_BSRR_BS1 =0x0000 0002

Бит BS2 - GPIO_BSRR_BS2 =0x0000 0004

------------------------------------------------------

Бит BS15 - GPIO_BSRR_BS15 =0x0000 8000

Бит BR0 - GPIO_BSRR_BR0 =0x0001 0000

Бит BR1 - GPIO_BSRR_BR1 =0x0002 0000

Бит BR2 - GPIO_BSRR_BR2 =0x0004 0000

------------------------------------------------------

Бит BR15 - GPIO_BSRR_BR15=0x8000 0000

10) Операции над отдельными разрядами регистров ПЛМ портов I/O. Рекомендации к программам (продолжение).

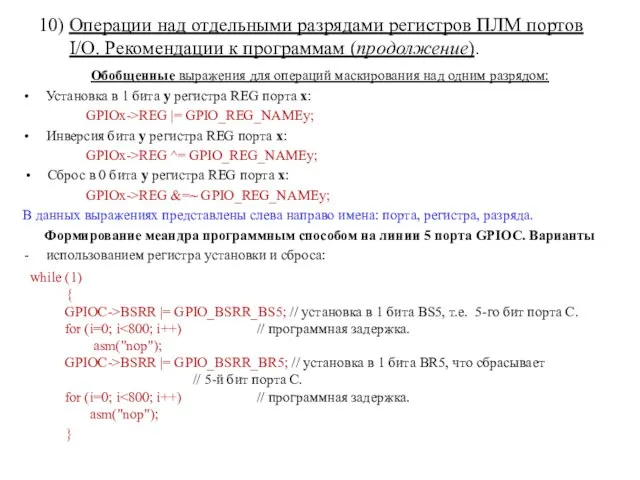

Слайд 26Обобщенные выражения для операций маскирования над одним разрядом:

Установка в 1 бита у

Обобщенные выражения для операций маскирования над одним разрядом:

Установка в 1 бита у

GPIOх->REG |= GPIO_REG_NAMEy;

Инверсия бита у регистра REG порта х:

GPIOх->REG ^= GPIO_REG_NAMEy;

Сброс в 0 бита у регистра REG порта х:

GPIOх->REG &=~ GPIO_REG_NAMEy;

В данных выражениях представлены слева направо имена: порта, регистра, разряда.

Формирование меандра программным способом на линии 5 порта GPIOC. Варианты

- использованием регистра установки и сброса:

while (1)

{

GPIOC->BSRR |= GPIO_BSRR_BS5; // установка в 1 бита BS5, т.е. 5-го бит порта С.

for (i=0; i<800; i++) // программная задержка.

asm("nop");

GPIOC->BSRR |= GPIO_BSRR_BR5; // установка в 1 бита BR5, что сбрасывает

// 5-й бит порта С.

for (i=0; i<800; i++) // программная задержка.

asm("nop");

}

10) Операции над отдельными разрядами регистров ПЛМ портов I/O. Рекомендации к программам (продолжение).

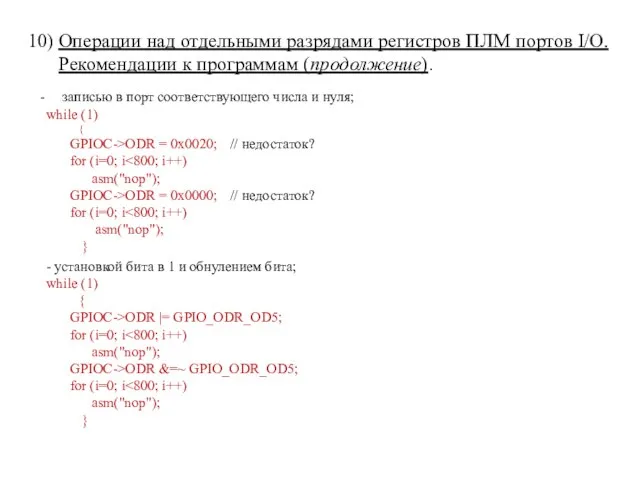

Слайд 27записью в порт соответствующего числа и нуля;

while (1)

{

GPIOC->ODR = 0x0020; // недостаток?

for

записью в порт соответствующего числа и нуля;

while (1)

{

GPIOC->ODR = 0x0020; // недостаток?

for

asm("nop");

GPIOC->ODR = 0x0000; // недостаток?

for (i=0; i<800; i++)

asm("nop");

}

- установкой бита в 1 и обнулением бита;

while (1)

{

GPIOC->ODR |= GPIO_ODR_OD5;

for (i=0; i<800; i++)

asm("nop");

GPIOC->ODR &=~ GPIO_ODR_OD5;

for (i=0; i<800; i++)

asm("nop");

}

10) Операции над отдельными разрядами регистров ПЛМ портов I/O. Рекомендации к программам (продолжение).

Слайд 28- установкой бита в 1 и инверсией бита;

while (1)

{

GPIOC->ODR |= GPIO_ODR_OD5;

for

- установкой бита в 1 и инверсией бита;

while (1)

{

GPIOC->ODR |= GPIO_ODR_OD5;

for

asm("nop");

GPIOC->ODR ^= GPIO_ODR_OD5;

for (i=0; i<800; i++) {

asm("nop"); }

}

- одной инверсией бита (!)

while (1)

{

GPIOC->ODR ^= GPIO_ODR_OD5;

for (i=0; i<800; i++)

asm("nop");

}

10) Операции над отдельными разрядами регистров ПЛМ портов I/O. Рекомендации к программам (продолжение)..

Слайд 29Работа с кнопкой пользователя (PC13)

while (1)

{

if(GPIOC->IDR & GPIO_IDR_ID13) //анализ маскирования разряда PC13

Работа с кнопкой пользователя (PC13)

while (1)

{

if(GPIOC->IDR & GPIO_IDR_ID13) //анализ маскирования разряда PC13

{

GPIOC->ODR ^= GPIO_ODR_OD5;

for (i=0; i<800; i++)

}

else GPIOC->ODR &=~ GPIO_ODR_OD5;

}

10) Операции над отдельными разрядами регистров ПЛМ портов I/O. Рекомендации к программам (продолжение).

Индивидуализация и дифференциация обучения

Индивидуализация и дифференциация обучения Методические рекомендации по аттестации педагогических и руководящих работников

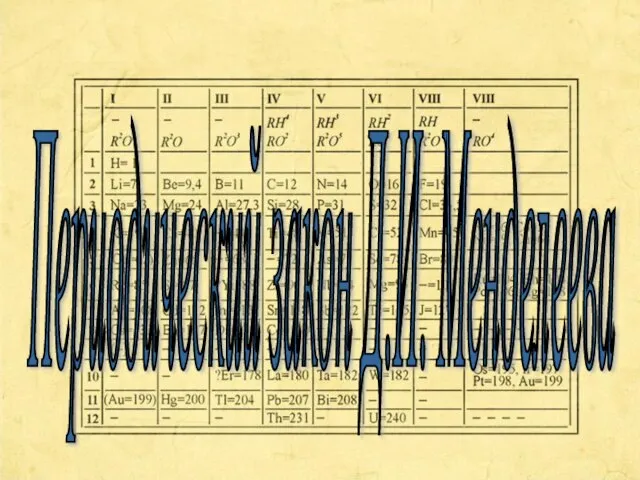

Методические рекомендации по аттестации педагогических и руководящих работников Периодический закон Д.И. Менделеева

Периодический закон Д.И. Менделеева Сергий Радонежский

Сергий Радонежский Недвижимость. Торги, лот №8, г. Хабаровск

Недвижимость. Торги, лот №8, г. Хабаровск Научный руководитель: кандидат исторических наук, доцент Е.А. Красулин

Научный руководитель: кандидат исторических наук, доцент Е.А. Красулин Вода в произведениях устного народного творчества

Вода в произведениях устного народного творчества Упражнения под музыкальное сопровождение

Упражнения под музыкальное сопровождение Процессуальные соглашения в МЧП: отличие от автономии воли

Процессуальные соглашения в МЧП: отличие от автономии воли Модель методического сопровождения педагогов, проучившихся в ММЦ

Модель методического сопровождения педагогов, проучившихся в ММЦ ПАВЛОВСКАЯ КРЕПОСТЬ

ПАВЛОВСКАЯ КРЕПОСТЬ Основные стратегии аккультурации

Основные стратегии аккультурации Вредные Советы

Вредные Советы Основные принципы построения автоматического теста при помощи QTP

Основные принципы построения автоматического теста при помощи QTP Орган

Орган Клиники, дружественные к подросткам и молодежи, или Куда пойти подростку?

Клиники, дружественные к подросткам и молодежи, или Куда пойти подростку? Экология

Экология  Муниципальное бюджетное образовательное учреждение дополнительного образования детей

Муниципальное бюджетное образовательное учреждение дополнительного образования детей Вредные привычки

Вредные привычки Длина отрезка

Длина отрезка Турнир знатоков информатики

Турнир знатоков информатики Роль Ирана в исламской культуре

Роль Ирана в исламской культуре Современные подходы к пониманию права

Современные подходы к пониманию права Название ИССЛЕДОВАНИЯ

Название ИССЛЕДОВАНИЯ «Принципы и направления развития таможенных органов.» Работу выполнили студентки 1-го курса ФТД группы Т-116 Сафонова Эллина и Панк

«Принципы и направления развития таможенных органов.» Работу выполнили студентки 1-го курса ФТД группы Т-116 Сафонова Эллина и Панк Управление качеством в проекте

Управление качеством в проекте Сибгат Х?ким(1911-1986)

Сибгат Х?ким(1911-1986) Цех слоения и шоковой заморозки ХБИ

Цех слоения и шоковой заморозки ХБИ