Содержание

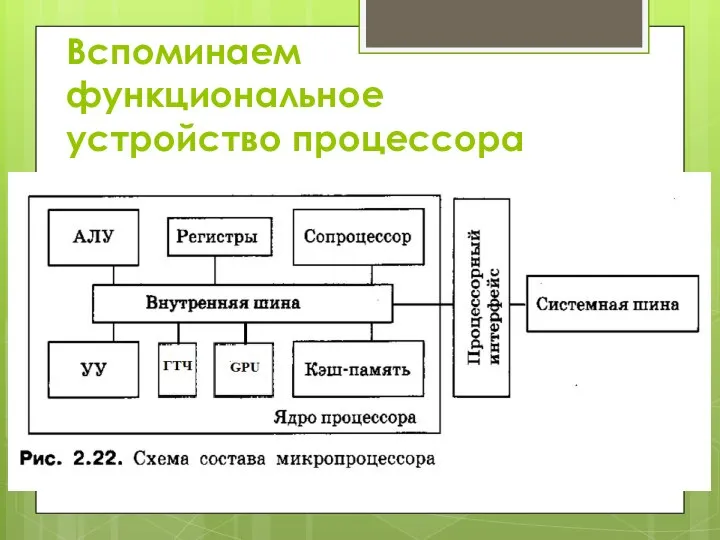

- 2. Вспоминаем функциональное устройство процессора

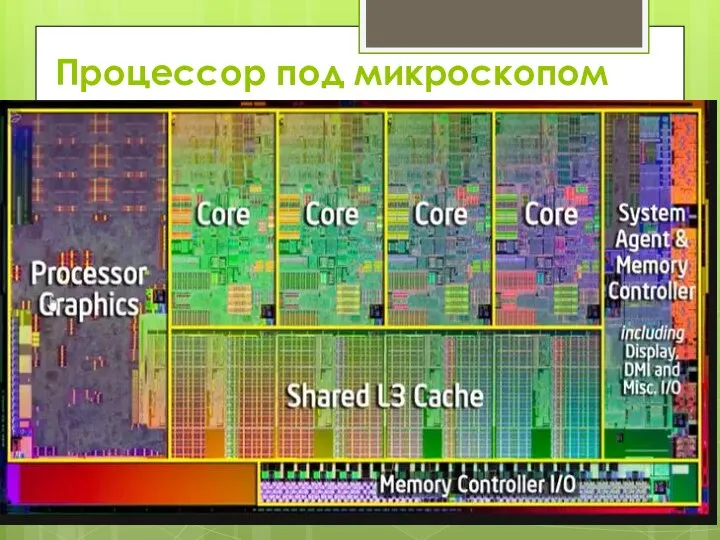

- 3. Процессор под микроскопом

- 4. Введение Вспомним… П р о ц е с с о р и о п е р

- 5. 3.1. Общее представление о структуре и архитектуре процессоров Системы команд Основные команды ЭВМ классифицируются следующим образом:

- 6. Увеличение разрядности позволяет увеличить адресность команды и длину адреса (т. е. объем памяти, доступной данной команде,

- 7. Классы процессоров В зависимости от набора и порядка выполнения команд процессоры подразделяются на четыре класса:

- 8. CISC (Complex Instruction Set Computer) Классическая архитектура процессоров, которая начала свое развитие в 1940-х гг. с

- 9. Типичным примером CISC являются процессоры Intel х86 (в частности, семейство Pentium). Количество команд: более 200 команд

- 10. Такое многообразие выполняемых команд и способов адресации позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач.

- 11. RISC (Redused Instuction Set Computer) Архитектура отличается использованием ограниченного набора команд фиксированного формата. Первый процессор RISC

- 12. Значительно сокращается число используемых способов адресации. В результате процессор на 20—30 % реже обращается к оперативной

- 13. Упростилась топология процессора, выполняемого в виде одной интегральной схемы, сократились сроки ее разработки, она стала дешевле.

- 14. CISC или RISС? В то время, как в процессоре CISC для выполнения одной команды необходимо в

- 15. Процессор MISC Работает с минимальным набором длинных команд и характеризуется небольшим набором чаще всего встречающихся команд.

- 16. VLIW (Very Large Instruction Word) архитектура, которая появилась относительно недавно (в 1990-х гг.). Ее особенностью является

- 18. Компилятор В давние времена, когда компьютеры были большими, время доступа к памяти было небольшим, но и

- 19. Специальный компилятор планирования перед выполнением прикладной программы проводит ее анализ. По множеству ветвей последовательности операций определяет

- 20. Во-первых, в течение одного такта выполнять группу коротких («обычных») команд, Во-вторых — упростить структуру процессора. Этим

- 21. К VLIW-типу можно отнести процессор Elbrus, объявленный российской компанией «Эльбрус».

- 22. 3.2. Технологии повышения производительности процессоров и эффективности ЭВМ Конвейерная обработка команд Обработка команды, или цикл процессора,

- 23. Все команды в таких процессорах следуют одна за другой – это носит название конвейерной (pipeline) обработки.

- 24. Конвейеризация Конвейеризация технология, осуществляющая многопоточную параллельную обработку команд. В каждый момент одна из команд считывается, другая

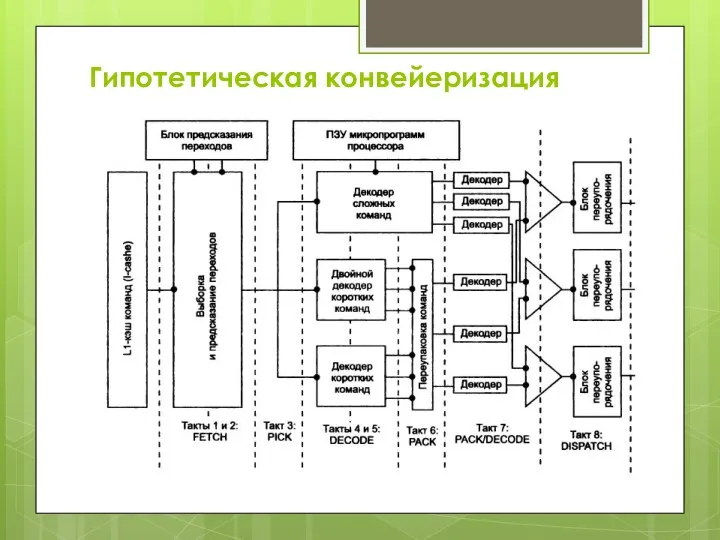

- 25. Гипотетическая конвейеризация

- 26. Конвейеризация реальная

- 27. Пояснение к схемам Причина увеличения длины конвейера заключается в том, что многие команды являются довольно сложными

- 28. Свойства конвейеризации С ростом числа линий конвейера и увеличением числа ступеней на линии увеличивается пропускная способность

- 29. Суперскаляризация Процессоры с несколькими линиями конвейера получили название с у п е р с к а

- 30. Суперскалярный процессор Суперскалярный процессор - Процессор, поддерживающий так называемый параллелизм на уровне инструкций (то есть, процессор,

- 31. Во многих вычислительных системах, наряду с конвейером команд, используются конвейеры данных. Сочетание этих двух конвейеров дает

- 32. Сопроцессоры Для расширения вычислительных возможностей центрального процессора — выполнения арифметических операций над вещественными числами (с плавающей

- 33. Применение сопроцессора повышает производительность вычислений в сотни раз. В разных поколениях процессоров он назывался по-разному —

- 34. Блоки операций с плавающей запятой С программной точки зрения сопроцессор и процессор выглядят как единое целое.

- 35. Увеличение разрядности систем В 1980-е годы соответствие между типом ЭВМ и ее разрядностью имело простейший вид:

- 37. Использование GPU GPU - отдельное устройство персонального компьютера, выполняющее графический рендеринг. GPU это вспомогательный микрочип, который

- 38. Видеокарта GPU способна быстро проводить расчёты, где используется одна или схожая формула (например, вычисление точки затенения

- 40. Как по внешнему виду понять встроенная видео карта или внешняя

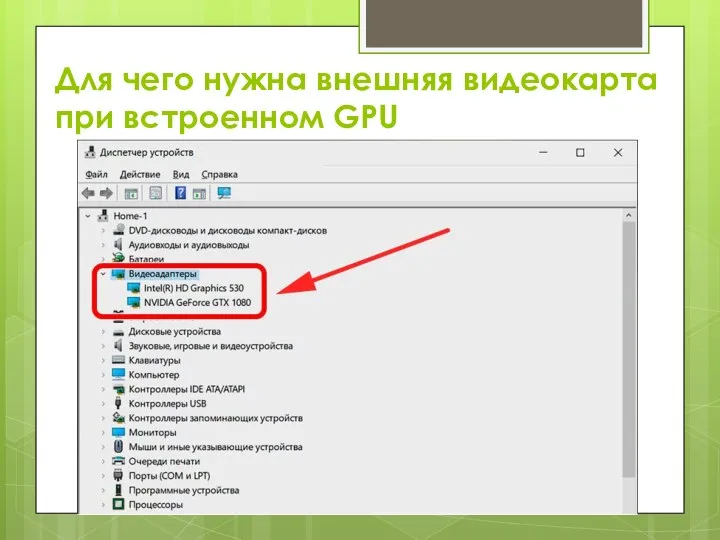

- 41. Для чего нужна внешняя видеокарта при встроенном GPU

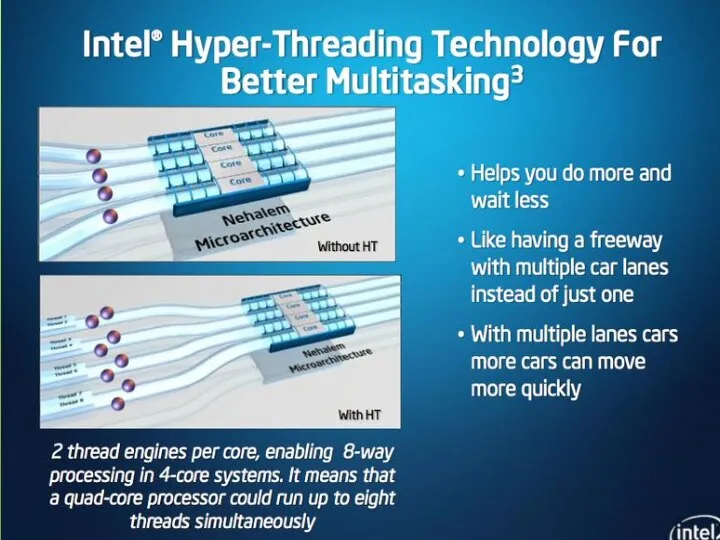

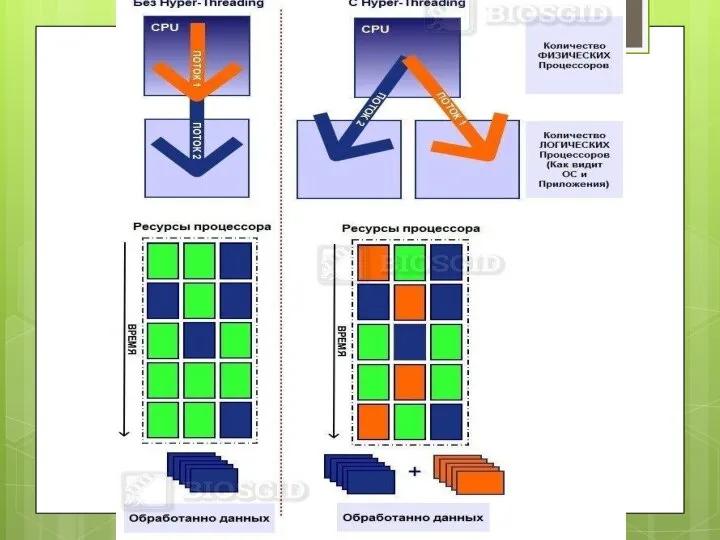

- 42. Использование виртуализации процессора Hyper-threading (англ. hyper-threading — гиперпоточность, HTT или HT) — технология, разработанная компанией Intel

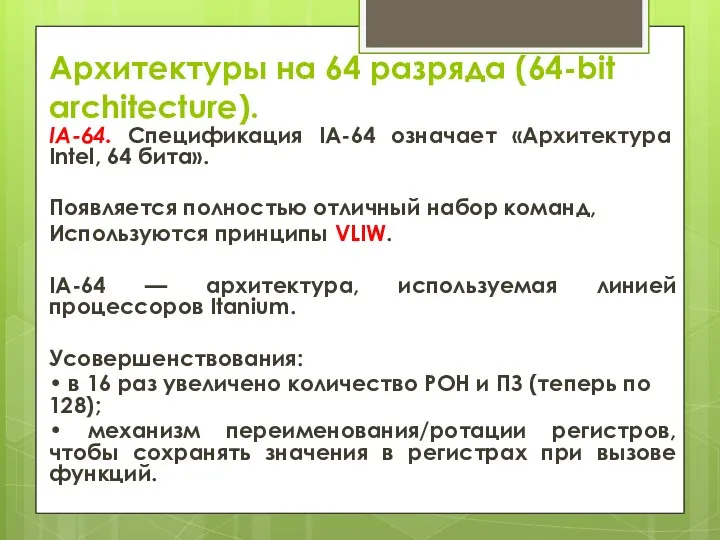

- 45. Архитектуры на 64 разряда (64-bit architecture). IA-64. Спецификация IA-64 означает «Архитектура Intel, 64 бита». Появляется полностью

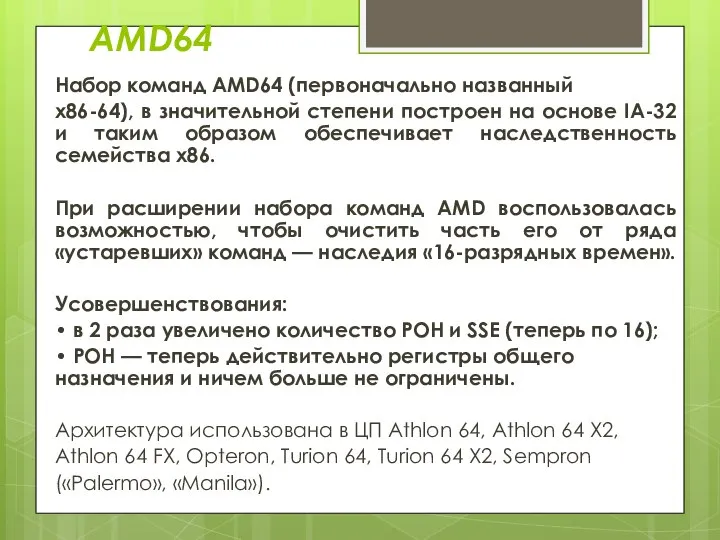

- 46. AMD64 Набор команд AMD64 (первоначально названный х86-64), в значительной степени построен на основе IA-32 и таким

- 47. EM64T (Extended Memory 64-bit Technology, или Intel 64) — набор команд (ранее известный как Yamhill), объявленный

- 48. Векторная обработка (SIMD-команды) В классификации Г. Флинна имеется рубрика SIMD — поток данных, обрабатываемых одной командой.

- 49. MMX MMX (MultiMedia extension) — архитектура системы команд, непосредственно предназначенных для задач мультимедиа, связи и графических

- 50. Это и определило новую структуру данных и расширение системы команд. При этом было достигнуто общее повышение

- 51. Архитектура 3DNow! впервые реализована в процессорах AMD К6-2 (май 1998 г.). Технология 3DNow! включает 21 дополнительную

- 52. Динамическое исполнение (dynamic execution technology) Динамическое исполнение — технология обработки данных процессором, обеспечивающая более эффективную работу

- 53. Внеочередное выполнение Внеочередное выполнение (выполнение вне естественного порядка — out-of-order execution). Процессор анализирует поток команд и

- 54. Переименование (ротация) регистров Переименование (ротация) регистров (register rename) Чтобы избежать пересылок данных между регистрами в соответствующей

- 55. Выполнение по предположению Выполнение по предположению (спекулятивное — speculative). Процессор выполняет инструкции (до пяти инструкций одновременно)

- 56. Предикация (predication) — одновременное исполнение нескольких ветвей программы вместо предсказания переходов (выполнения наиболее вероятного); Если в

- 57. Опережающее чтение данных Опережающее чтение данных (speculative loading), т. е. загрузка данных в регистры с опережением,

- 59. Скачать презентацию

State Establishment “N.N. Alexandrov National Cancer Centre of Belarus”

State Establishment “N.N. Alexandrov National Cancer Centre of Belarus” Добро пожаловать на встречу За чашкой чая

Добро пожаловать на встречу За чашкой чая Презентация на тему Рождество и Новый год

Презентация на тему Рождество и Новый год  Работа оборонно-спортивного комплекса

Работа оборонно-спортивного комплекса Полировочная система Jota

Полировочная система Jota Особенности введения и апробации курса «Основы религиозных культур и светской этики» (обобщение опыта)

Особенности введения и апробации курса «Основы религиозных культур и светской этики» (обобщение опыта) Зависимость силы тока от напряжения. Электрическое сопротивление проводников

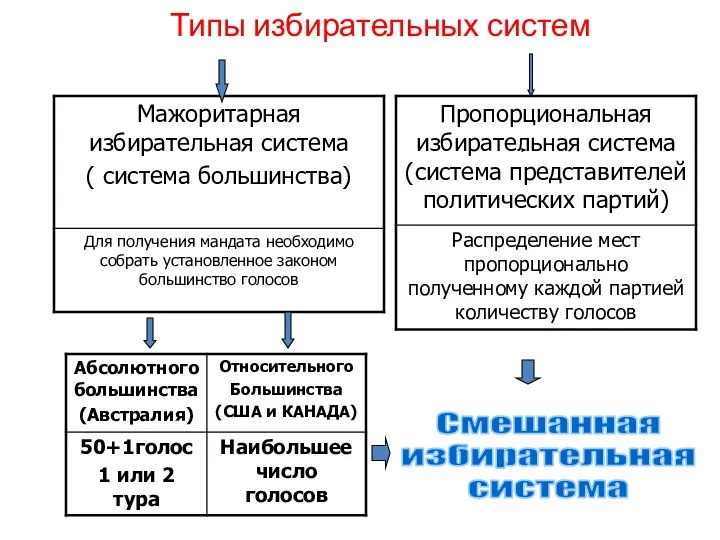

Зависимость силы тока от напряжения. Электрическое сопротивление проводников Типы избирательных систем

Типы избирательных систем Эстетическое формирование искусством окружающей среды

Эстетическое формирование искусством окружающей среды О фильтре «ТЫ СПАМНЫЙ». Оптимизируем тексты под новые требования Яндекса

О фильтре «ТЫ СПАМНЫЙ». Оптимизируем тексты под новые требования Яндекса Город «на игле».Что мешает «культурной столице» стать «креативным городом»

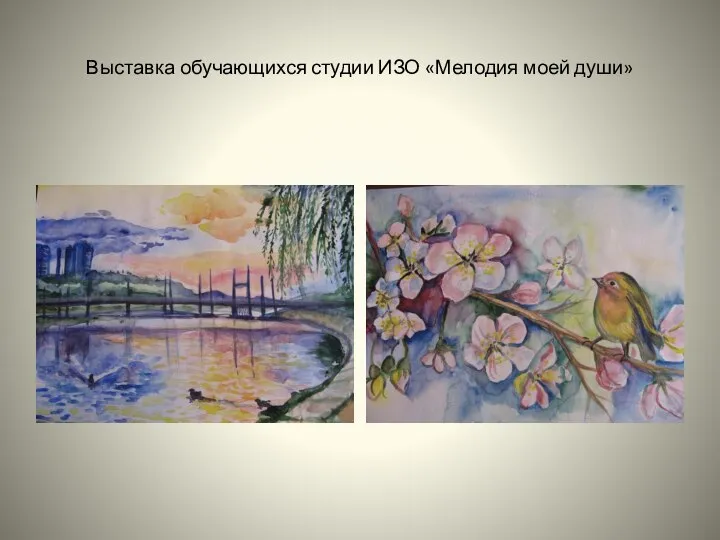

Город «на игле».Что мешает «культурной столице» стать «креативным городом» Выставка обучающихся студии ИЗО Мелодия моей души

Выставка обучающихся студии ИЗО Мелодия моей души Музыка в театре

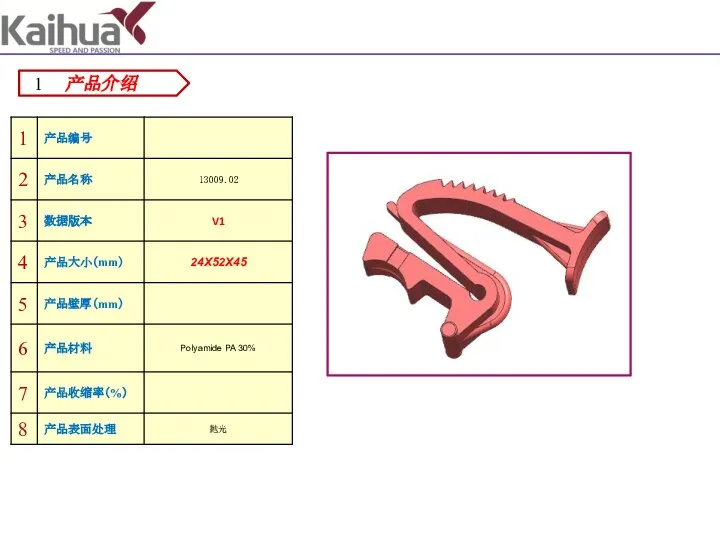

Музыка в театре 产品介绍. 产品编号

产品介绍. 产品编号 Проблемы соблюдения, охраны и защиты конституционного права на свободу совести и вероисповедания при получении документов

Проблемы соблюдения, охраны и защиты конституционного права на свободу совести и вероисповедания при получении документов Международная конкурентоспособность российского инвестклимата

Международная конкурентоспособность российского инвестклимата Преступность подростков

Преступность подростков Презентация на тему Как образуется иней, роса, дождь и снег

Презентация на тему Как образуется иней, роса, дождь и снег  Новая жизнь нашему дому

Новая жизнь нашему дому РАСПРЕДЕЛЕНИЕ ПРАВ ПОЛЬЗОВАНИЯ ЧАСТОТНЫМ СПЕКТРОМ В РФ: РАЗРАБОТКА ОПТИМАЛЬНОГО МЕХАНИЗМА С ТОЧКИ ЗРЕНИЯ ТЕОРИИ АУКЦИОНОВ

РАСПРЕДЕЛЕНИЕ ПРАВ ПОЛЬЗОВАНИЯ ЧАСТОТНЫМ СПЕКТРОМ В РФ: РАЗРАБОТКА ОПТИМАЛЬНОГО МЕХАНИЗМА С ТОЧКИ ЗРЕНИЯ ТЕОРИИ АУКЦИОНОВ Современная идентичность как вектор стратегического развития имиджа территорий Москва, 20 октября 2010

Современная идентичность как вектор стратегического развития имиджа территорий Москва, 20 октября 2010 Презентация на тему Перпендикулярные прямые в пространстве

Презентация на тему Перпендикулярные прямые в пространстве Проект по экологии человека Формула здоровья

Проект по экологии человека Формула здоровья Mykola Amosov

Mykola Amosov СЕКЦИЯ «АТЛЕТИЧЕСКАЯГИМНАСИКА»

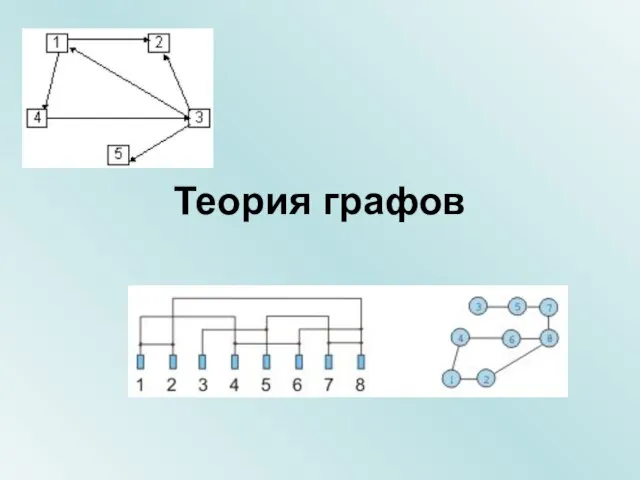

СЕКЦИЯ «АТЛЕТИЧЕСКАЯГИМНАСИКА» Теория графов

Теория графов Организация межведомственного взаимодействия по оказанию услуг населению

Организация межведомственного взаимодействия по оказанию услуг населению Подобные слагаемые

Подобные слагаемые