Содержание

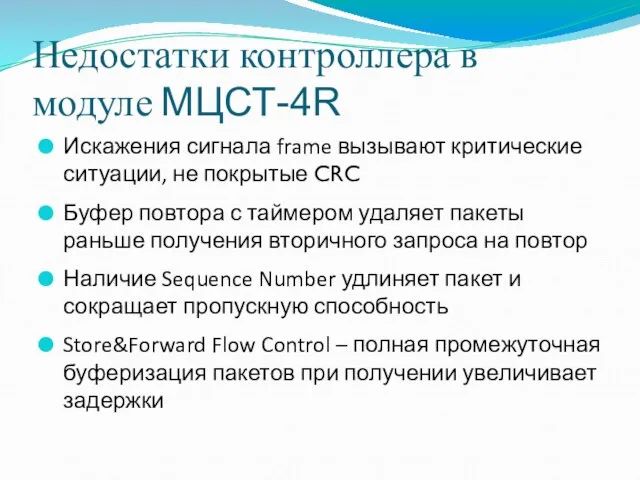

- 2. Недостатки контроллера в модуле МЦСТ-4R Искажения сигнала frame вызывают критические ситуации, не покрытые CRC Буфер повтора

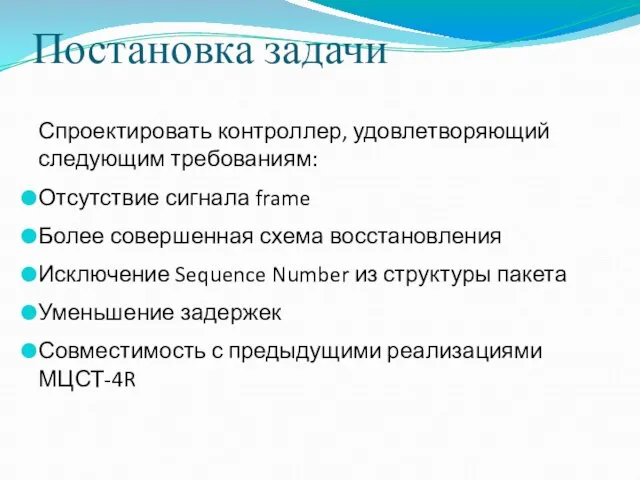

- 3. Постановка задачи Спроектировать контроллер, удовлетворяющий следующим требованиям: Отсутствие сигнала frame Более совершенная схема восстановления Исключение Sequence

- 4. Соответствие МЦСТ-4R Постановка задачи маршрутный физический Пакеты 4 типов 23 бит 57 бит 80 бит 539

- 5. Store&Forward Cut-through Уменьшение задержек Протокол контроллера Общий принцип передачи пакетов Разбиение больших пакетов на части с

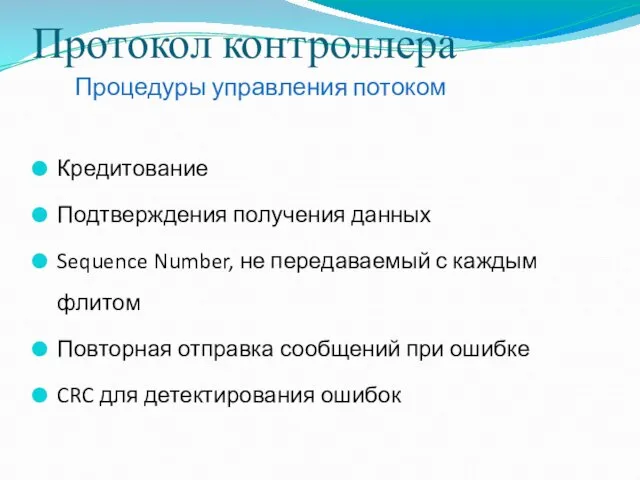

- 6. Кредитование Подтверждения получения данных Sequence Number, не передаваемый с каждым флитом Повторная отправка сообщений при ошибке

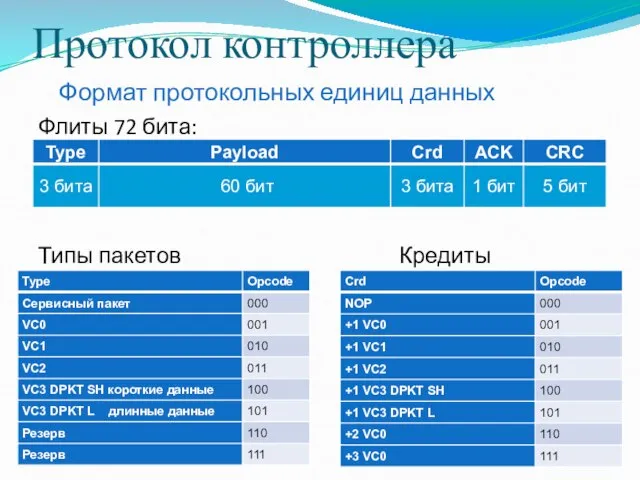

- 7. Протокол контроллера Флиты 72 бита: Типы пакетов Кредиты Формат протокольных единиц данных

- 8. Распределение пакетов по 60 битам в payload 9 23 битные по 2.5 57 битные по 1

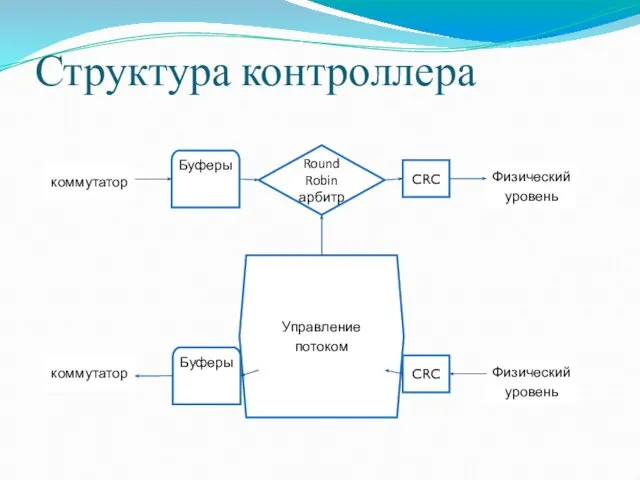

- 9. Структура контроллера

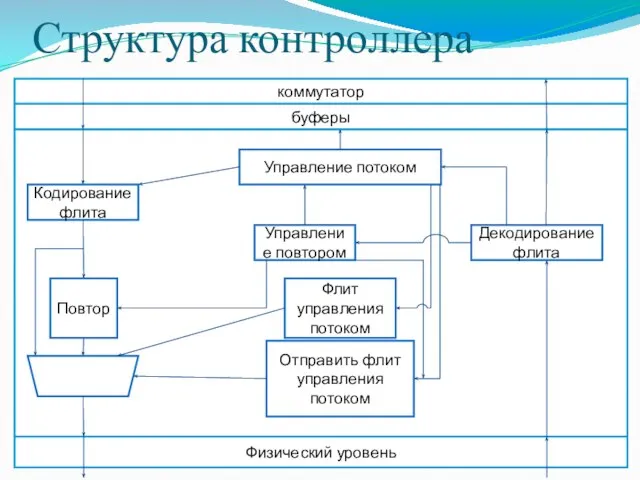

- 10. коммутатор Структура контроллера Кодирование флита Повтор Управление потоком Управление повтором Флит управления потоком Отправить флит управления

- 11. Схема восстановления

- 12. Схема восстановления

- 13. Типы контрольных флитов

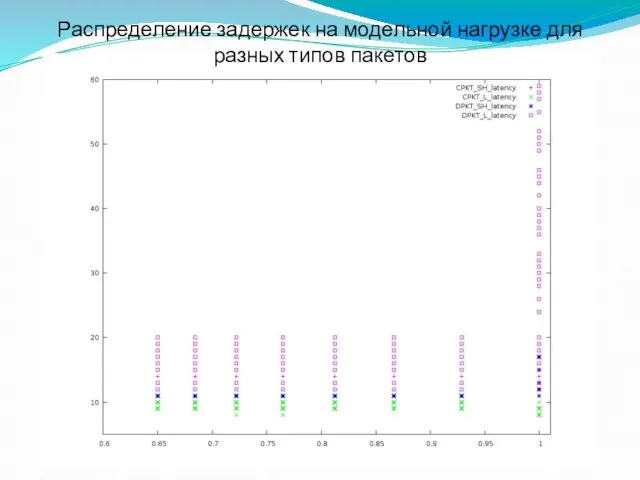

- 14. Распределение задержек на модельной нагрузке для разных типов пакетов

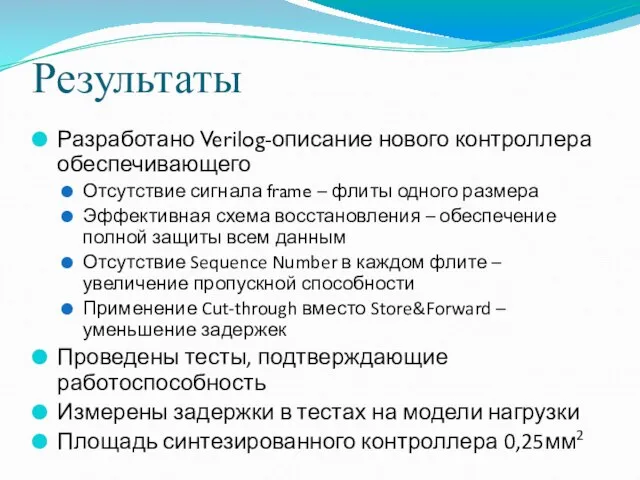

- 15. Результаты Разработано Verilog-описание нового контроллера обеспечивающего Отсутствие сигнала frame – флиты одного размера Эффективная схема восстановления

- 17. Скачать презентацию

Общественно-активная школа: эффективность и качество.

Общественно-активная школа: эффективность и качество. 197368

197368 С какво свързваш древногръцкото облекло?

С какво свързваш древногръцкото облекло? Презентация на тему Экономика и ее роль в обществе

Презентация на тему Экономика и ее роль в обществе Фотоальбом. Велосипеди

Фотоальбом. Велосипеди Узорочья Севера

Узорочья Севера Цветы для моей семьи

Цветы для моей семьи Открытые горные работы, их элементы и терминология

Открытые горные работы, их элементы и терминология Бизнес инсайт. Продуктивность как система

Бизнес инсайт. Продуктивность как система Где летит птица?

Где летит птица? Итоги 1 полугодия 2010-2011 уч.года

Итоги 1 полугодия 2010-2011 уч.года Творческий проект Кукла своими руками

Творческий проект Кукла своими руками Буквы О-Ё после шипящих и Ц

Буквы О-Ё после шипящих и Ц Формы взаимодействия с семьей (из опыта работы)

Формы взаимодействия с семьей (из опыта работы) КОММУНИКАТИВНАЯ ПОЛИТИКА ХОЛДИНГОВ

КОММУНИКАТИВНАЯ ПОЛИТИКА ХОЛДИНГОВ Государственное регулирование цен на лекарственные средства на региональном уровне и проблемы, возникающие в рамках действующег

Государственное регулирование цен на лекарственные средства на региональном уровне и проблемы, возникающие в рамках действующег Презентация прочитанной книги

Презентация прочитанной книги Филиал ООО компания Тензор. Сфера торгов

Филиал ООО компания Тензор. Сфера торгов Рекуперативный воздухонагреватель, с использованием жидких горючих отходов.

Рекуперативный воздухонагреватель, с использованием жидких горючих отходов. Интерактивно-аналитический онлайн-сервиса Калькулятор процедур

Интерактивно-аналитический онлайн-сервиса Калькулятор процедур Элла Фицджеральд - выдающаяся джазовая певица, актриса 1917-1996

Элла Фицджеральд - выдающаяся джазовая певица, актриса 1917-1996 Места на направление Товароведение

Места на направление Товароведение Праця неповнолітніх

Праця неповнолітніх Прямолинейное распространение света

Прямолинейное распространение света Документовед он-лайн сервис оформления документов Документы для регистрации общества с ограниченной ответственностью за 15 минут.

Документовед он-лайн сервис оформления документов Документы для регистрации общества с ограниченной ответственностью за 15 минут. Как правильно оформить презентацию и web-сайт?

Как правильно оформить презентацию и web-сайт? Капитализм XVIII века. Промышленный переворот в Англии

Капитализм XVIII века. Промышленный переворот в Англии Работать с молодёжью: как?

Работать с молодёжью: как?