Содержание

- 3. Основные характеристики и типы МП Однокристальные МП с фиксированной разрядностью слова, с фиксированной системой команд и

- 4. Основные характеристики и типы МП Многокристальные (секционные) микро- программируемые МП с изменяемой разрядностью слова и фиксированным

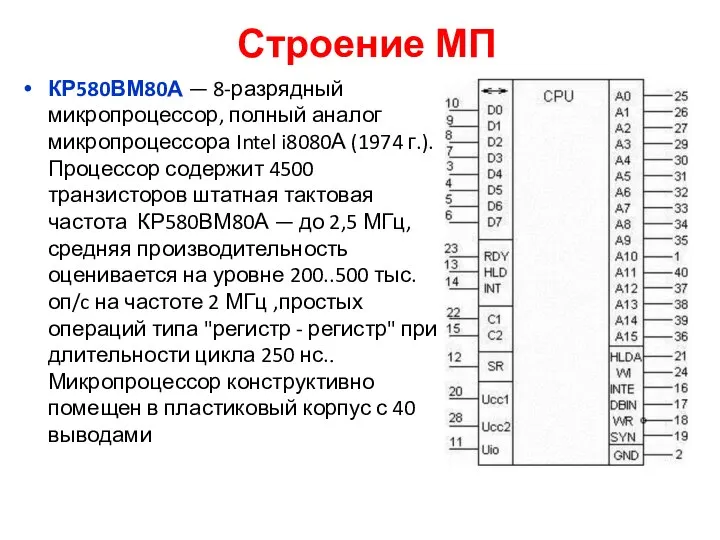

- 5. Строение МП КР580ВМ80А — 8-разрядный микропроцессор, полный аналог микропроцессора Intel i8080А (1974 г.). Процессор содержит 4500

- 6. Состав МПК КР580 Для формирования управляющих сигналов и буферирования данных в микропроцессорных системах на базе микропроцессора

- 7. Состав МПК КР580 Для связи микропроцессора с системной шиной применяют адресные регистры с повышенной нагрузочной способностью

- 8. Состав МПК КР580 Микросхема КР580ВВ55А – программируемое устройство ввода-вывода параллельной информации, применяется в качестве элемента ввода-вывода

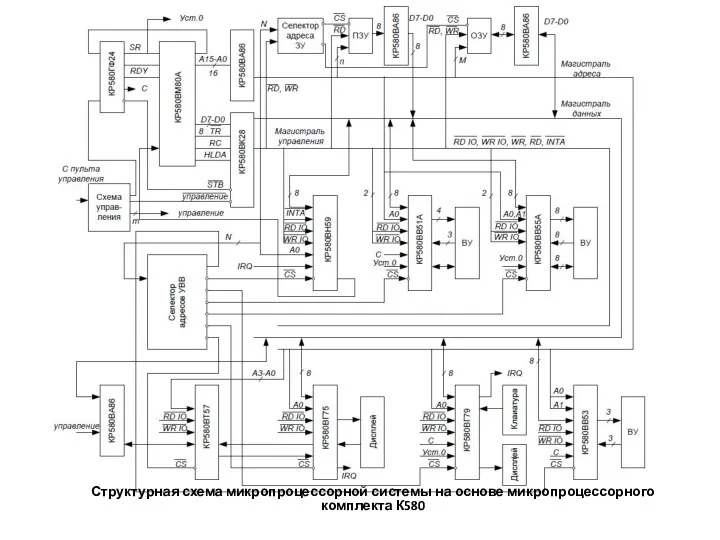

- 10. Структурная схема микропроцессорной системы на основе микропроцессорного комплекта К580

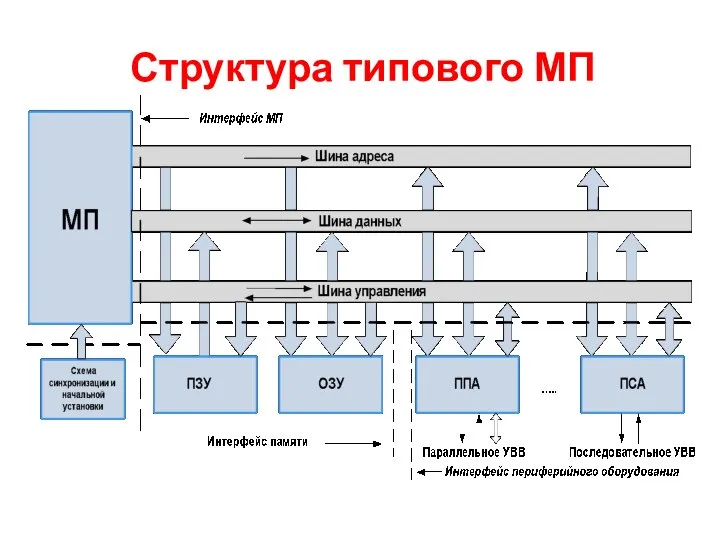

- 11. Структура, организация микро ЭВМ Микропроцессор является основным компонентом любого микрокомпьютера или микро-ЭВМ. В основу построения микро-ЭВМ

- 12. Структура, организация микро ЭВМ Магистральность – это способ соединения между различными модулями компьютера, когда входные и

- 13. Структура, организация микро ЭВМ Современные ЭВМ могут иметь различную архитектуру, но обязательно содержат в своей структуре

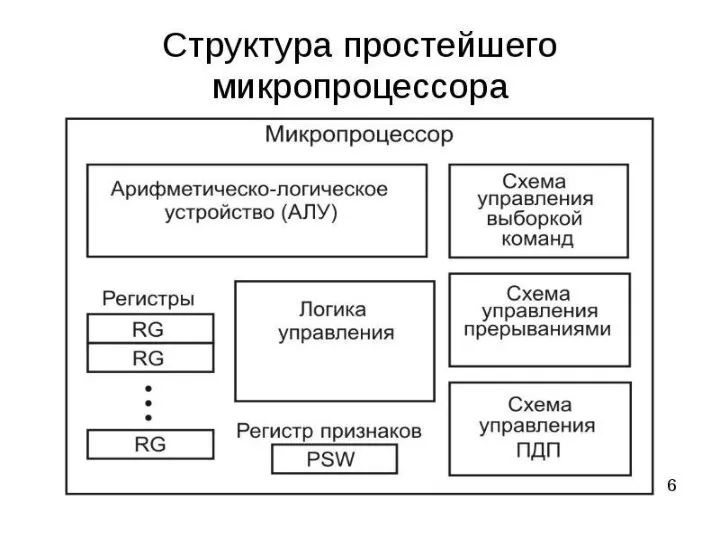

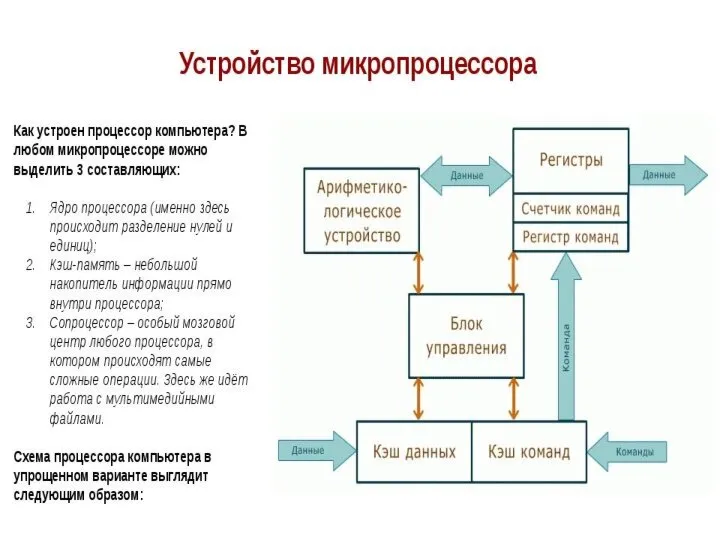

- 16. Структура типового МП

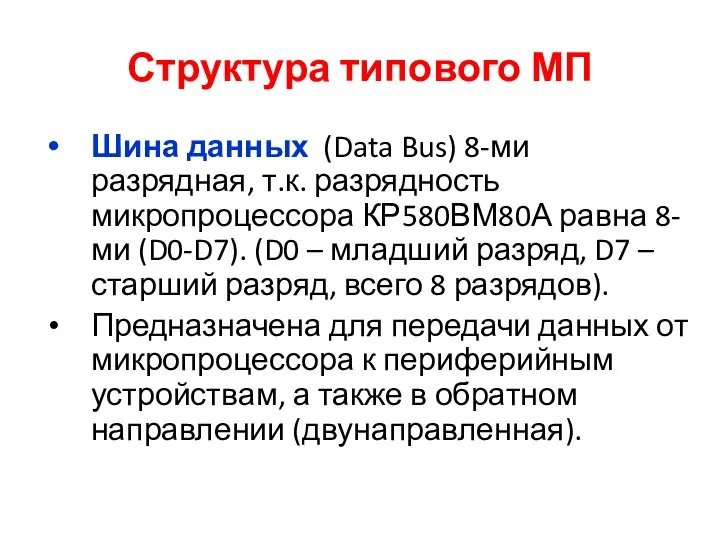

- 17. Структура типового МП Шина данных (Data Bus) 8-ми разрядная, т.к. разрядность микропроцессора КР580ВМ80А равна 8-ми (D0-D7).

- 18. Структура типового МП Шина адреса (Address Bus), 16-ти разрядная (А0-А15), служит для определения адреса (номера) устройства,

- 19. Структура типового МП Шина управления (Control Bus), постоянной размерности не имеет, состоит из отдельных управляющих сигналов.

- 20. Структура типового МП ОЗУ хранит информацию только при наличии напряжения питания. ОЗУ-это простейший регистр построенный на

- 21. Структура типового МП Соединение всего многообразия внешних устройств с шинами МК осуществляется с помощью интерфейсов, которые

- 22. Структура типового МП Обмен данными с внешними устройствами осуществляется через порты ввода/вывода. Для микропроцессора Intel 8080

- 23. Микропроцессор Intel 8080A ориентирован на работу с памятью, имеющую байтовую организацию (8 бит). Это значит, что

- 24. Схема подключения выводов микропроцессора КР580ВМ80А и их назначения.

- 25. Выводы синхронизации: F1, F2 – выводы двух неперекрывающихся последовательностей синхроимпульсов; SYNC – выход синхронизации, сигнал определяет

- 26. Выводы управления ожиданием: READY – готово внешнее устройство (READY = 1) или не готово (READY =

- 27. Выводы управления памятью: WR – управление записью в память или во внешние устройства; низкий уровень указывает,

- 28. Выводы управления магистралью данных: DBIN – указывает, что магистраль данных (D7-D0) находится в режиме приема. Используется

- 29. Выводы управления прерыванием: INT – запрос прерывания внешним устройством, запрашивающих обмен с процессором в режиме прерывания.

- 30. Выводы управления захватом магистралей в режиме ПДП: HLD – вход запроса захвата магистралей D7-D0 и магистрали

- 31. Архитектура микропроцессора Устройство разделения на страницы Декодер Арифметико-логическое устройство Регистры Управляющее устройство Устройство защитного тестирования Устройство

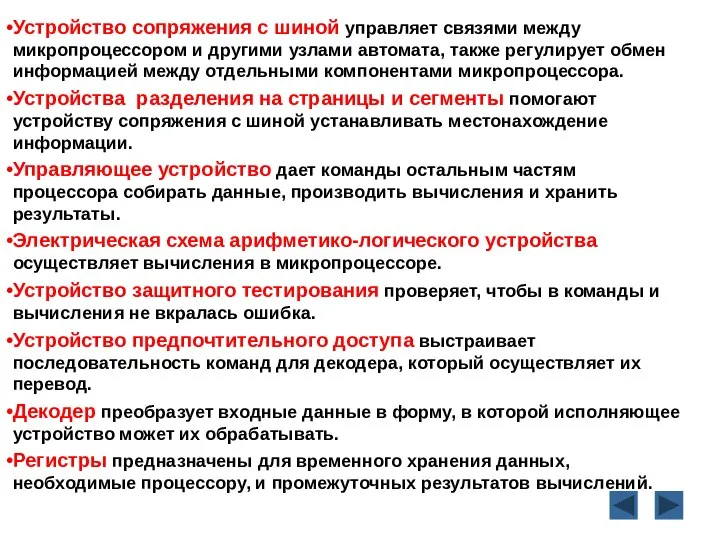

- 32. Устройство сопряжения с шиной управляет связями между микропроцессором и другими узлами автомата, также регулирует обмен информацией

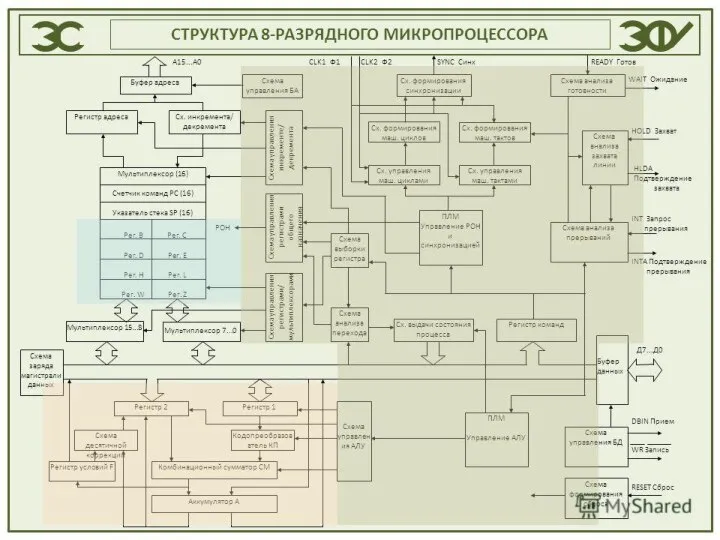

- 34. Структурная схема микропроцессора КР580ВМ80А (i8080А)

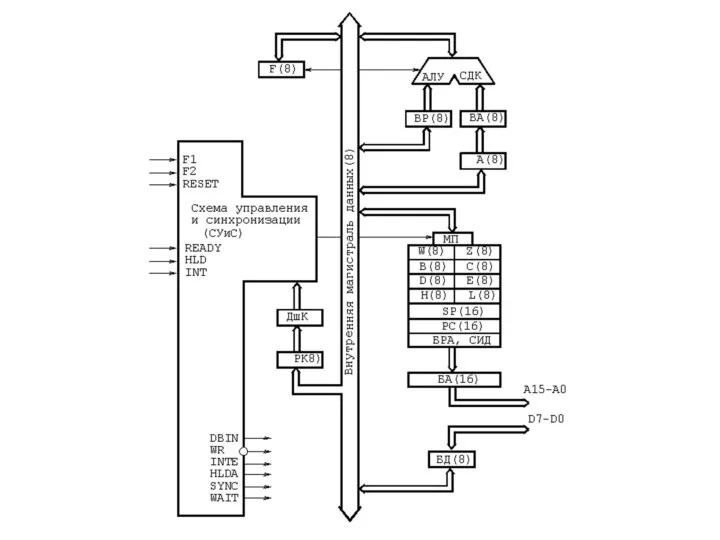

- 36. Микропроцессор КР580ВМ80А реализован на основе общей внутренней магистрали данных и включает в себя следующие функциональные узлы:

- 37. Блок регистров Содержит шесть 16-ти битовых регистров, образующих статическую память с произвольным доступом (регистр – пространство

- 38. При выполнении арифметических и логических операций с регистровой адресацией в регистрах хранятся 8-ми разрядные операнды, которые

- 39. Регистр-счетчик (РС) Используется в качестве программного счетчика и хранит адрес текущей команды программы. Его содержимое автоматически

- 40. Указатель стека (SP) SP хранит адрес ячейки стековой области памяти, к которой было сделано последнее обращение.

- 41. Пара регистров W и Z Это 8-разрядные регистры. Они недоступны программисту. Используются для запоминания двухбайтовых и

- 42. Адресная логика предназначена для хранения, программного изменения и выдачи на магистраль А15-А0 адресов данных и команду.

- 43. Блок АЛУ. Предназначен для выполнения арифметических и логических операций над числами в параллельном 8-ми разрядном двоичном

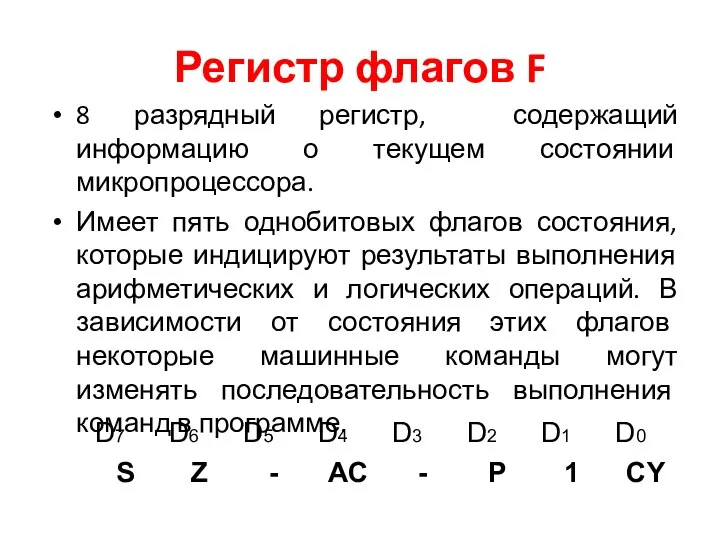

- 44. Регистр флагов F 8 разрядный регистр, содержащий информацию о текущем состоянии микропроцессора. Имеет пять однобитовых флагов

- 45. Двунаправленная магистраль данных Служит для организации связи микропроцессора с другими микросхемами, входящими в состав микро-ЭВМ. Она

- 46. В режиме вывода информация с внутренней магистрали загружается в буферный регистр, а затем передается на внешнюю

- 48. Скачать презентацию

Предквантум

Предквантум Старинные зимние обычаи и праздники, «Рождество», «Святки»

Старинные зимние обычаи и праздники, «Рождество», «Святки» ВИДЕО-СТЕНА DIBOSS LB-40

ВИДЕО-СТЕНА DIBOSS LB-40 Новый подход к интеграции календарно-сетевых графиков и смет

Новый подход к интеграции календарно-сетевых графиков и смет Областной конкурс Методическая разработка дистанционного урока - 2021

Областной конкурс Методическая разработка дистанционного урока - 2021 Музей путешествий. Поклонная гора. Парк Победы

Музей путешествий. Поклонная гора. Парк Победы Товары и услуги

Товары и услуги Техническое регулирование

Техническое регулирование 20140305_lekarstvennye_rasteniya_buturlinovskogo_rayona

20140305_lekarstvennye_rasteniya_buturlinovskogo_rayona Консолидация ритейла в Украине: роль логистики 1.Предпосылки для консолидации ритейла 2.Когда ритейлеру нужен 3PL-оператор? 3.Case study 4.

Консолидация ритейла в Украине: роль логистики 1.Предпосылки для консолидации ритейла 2.Когда ритейлеру нужен 3PL-оператор? 3.Case study 4. Project on the Indian Ocean

Project on the Indian Ocean  Портретная студийная съёмка

Портретная студийная съёмка Внешняя политика Советского государства 1920-х

Внешняя политика Советского государства 1920-х СТРОКА, ОБОРВАННАЯ ПУЛЕЙ

СТРОКА, ОБОРВАННАЯ ПУЛЕЙ ЕГЭ В 3 «Площади»

ЕГЭ В 3 «Площади» Цветовой контраст (хроматический)

Цветовой контраст (хроматический) Фотожурналист Владимир Вяткин

Фотожурналист Владимир Вяткин 26-27 апреля 2006 года Центр практической психологии РГУ имени С.А. Есенина Московский городской психолого-педагогический университе

26-27 апреля 2006 года Центр практической психологии РГУ имени С.А. Есенина Московский городской психолого-педагогический университе Кейс-стади для педагогов

Кейс-стади для педагогов Об аксиомах геометрии

Об аксиомах геометрии Презентация на тему Родная природа в стихотворениях поэтов xx века

Презентация на тему Родная природа в стихотворениях поэтов xx века  Каталог Атоми

Каталог Атоми Особенности организации и проведения школьного этапа Всероссийской олимпиады школьников по русскому языку Соловьева Т.В., предсе

Особенности организации и проведения школьного этапа Всероссийской олимпиады школьников по русскому языку Соловьева Т.В., предсе Создание новогодней открытки на основе пейзажа «Зимние россыпи»

Создание новогодней открытки на основе пейзажа «Зимние россыпи» Внесем порядок в хаос! ИЗО 7 класс

Внесем порядок в хаос! ИЗО 7 класс Космонавты, рожденные Украиной: космонавты Луганщины

Космонавты, рожденные Украиной: космонавты Луганщины Межрегиональный образовательный форум «Открытое образовательное пространство: живая праКтика тьюторства»

Межрегиональный образовательный форум «Открытое образовательное пространство: живая праКтика тьюторства» ДДК. Экскурсия

ДДК. Экскурсия