Содержание

- 2. _______id381 г. Мурманск, гимназия№4 Типовые логические устройства ЭВМ Сумматоры Полусумматоры Триггеры Счетчики Регистры Шифраторы Дешифраторы

- 3. _______id381 г. Мурманск, гимназия№4 Двоичными сумматорами называют логические устройства, выполняющие операцию сложения двух чисел, представленных в

- 4. _______id381 г. Мурманск, гимназия№4 Последовательные или одноразрядные Последовательные сумматоры строятся на основе одноразрядной суммирующей схемы. В

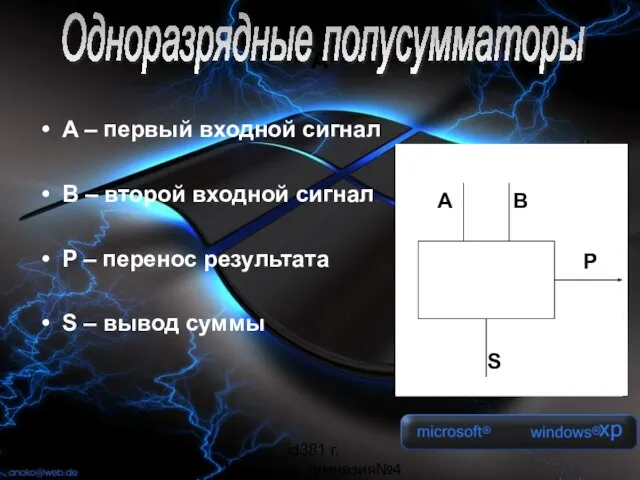

- 5. _______id381 г. Мурманск, гимназия№4 Одноразрядный полусумматор Одноразрядный двоичный сумматор на два входа и два выхода называется

- 6. _______id381 г. Мурманск, гимназия№4 A B P S A A – первый входной сигнал B –

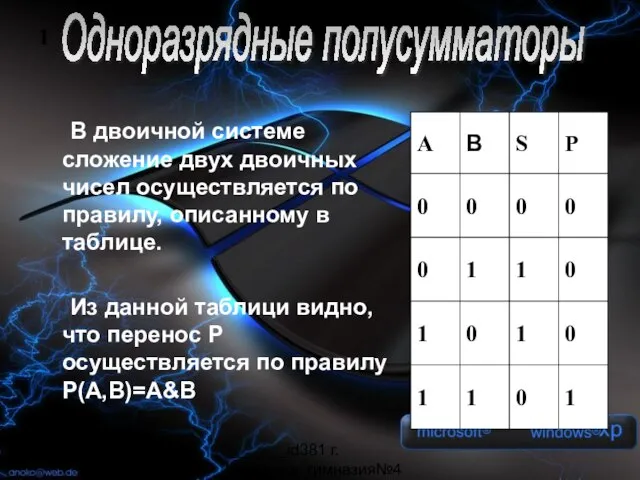

- 7. _______id381 г. Мурманск, гимназия№4 1 В двоичной системе сложение двух двоичных чисел осуществляется по правилу, описанному

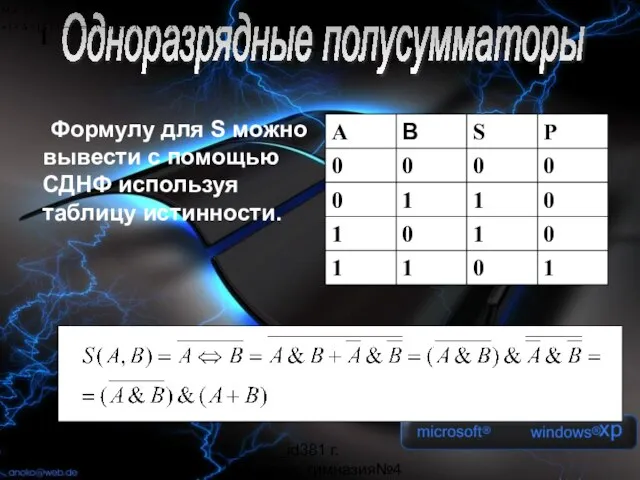

- 8. _______id381 г. Мурманск, гимназия№4 1 Формулу для S можно вывести с помощью СДНФ используя таблицу истинности.

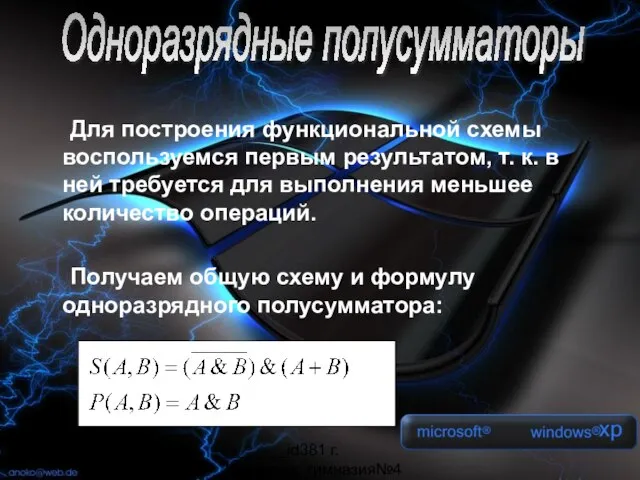

- 9. _______id381 г. Мурманск, гимназия№4 Для построения функциональной схемы воспользуемся первым результатом, т. к. в ней требуется

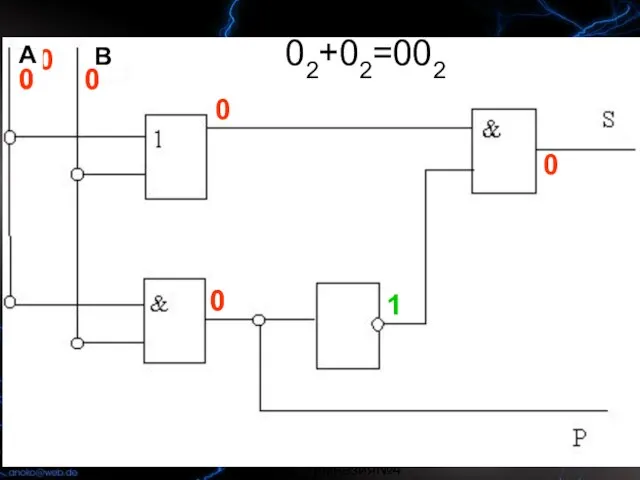

- 10. _______id381 г. Мурманск, гимназия№4 0 0 0 0 0 0 1 0 02+02=002 0 0 A

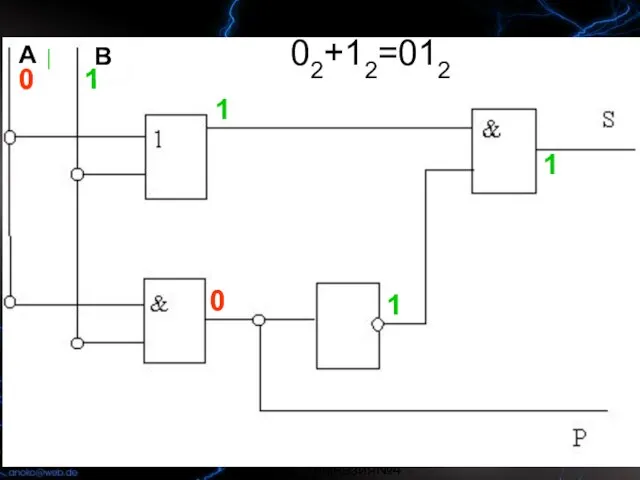

- 11. _______id381 г. Мурманск, гимназия№4 1 1 0 1 0 0 1 1 02+12=012 0 1 A

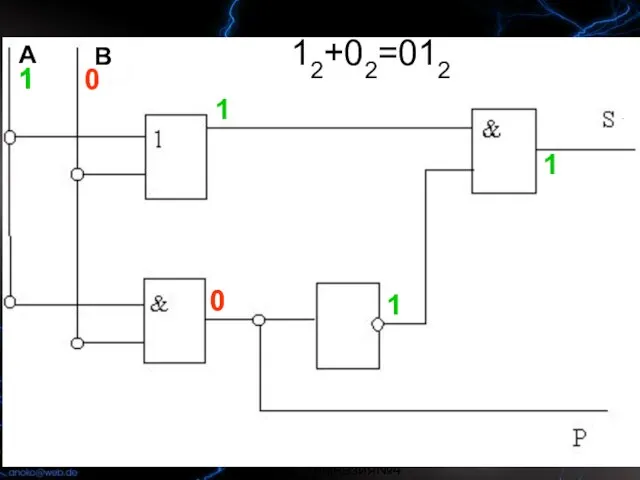

- 12. _______id381 г. Мурманск, гимназия№4 1 1 0 1 0 0 1 1 12+02=012 1 0 A

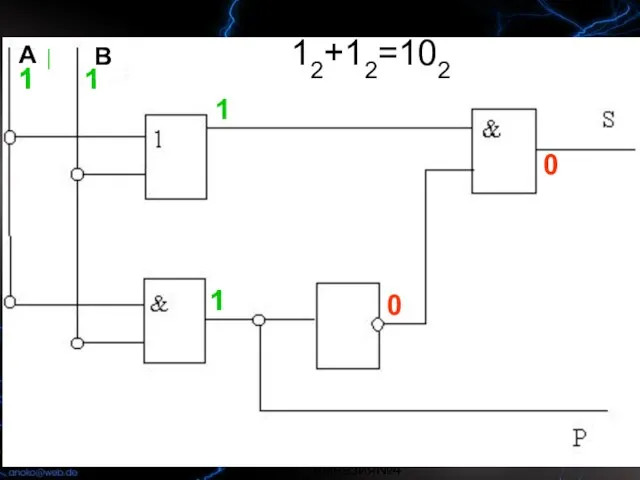

- 13. _______id381 г. Мурманск, гимназия№4 1 1 1 1 1 1 0 0 12+12=102 1 1 A

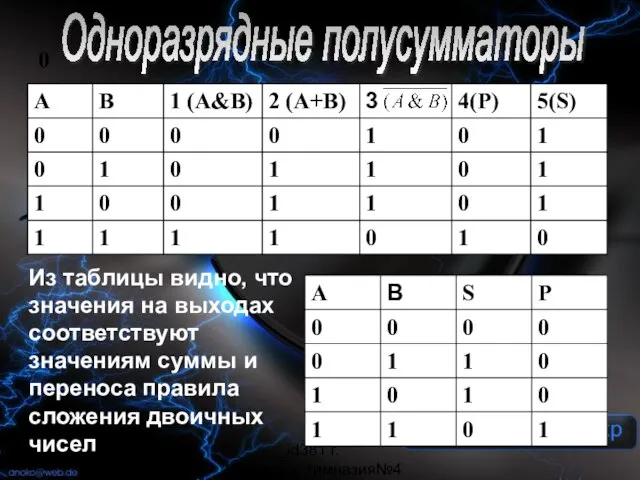

- 14. _______id381 г. Мурманск, гимназия№4 0 Одноразрядные полусумматоры Из таблицы видно, что значения на выходах соответствуют значениям

- 15. _______id381 г. Мурманск, гимназия№4 Полный одноразрядный сумматор Одноразрядный двоичный сумматор на три входа и два выхода

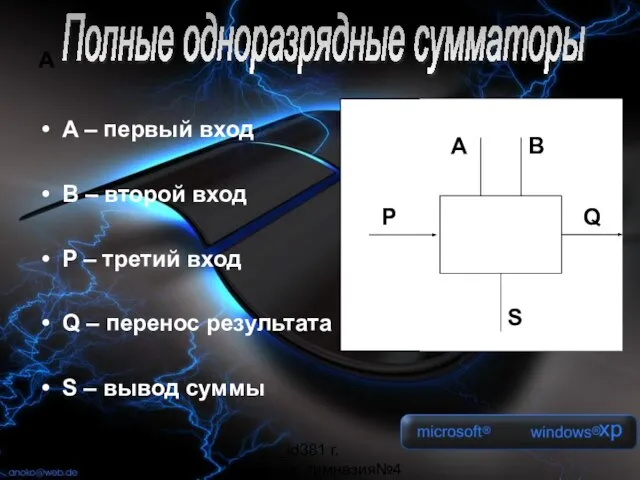

- 16. _______id381 г. Мурманск, гимназия№4 А A – первый вход B – второй вход P – третий

- 17. _______id381 г. Мурманск, гимназия№4 Принцип действия: Через вход A и B сумматор воспринимает двоичные цифры (слагаемые

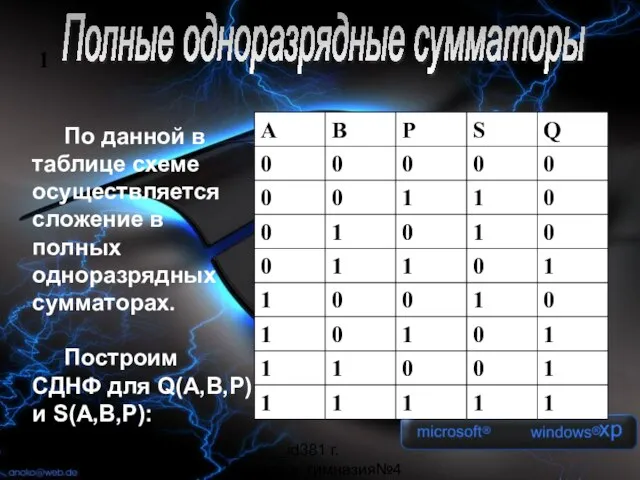

- 18. _______id381 г. Мурманск, гимназия№4 1 Полные одноразрядные сумматоры По данной в таблице схеме осуществляется сложение в

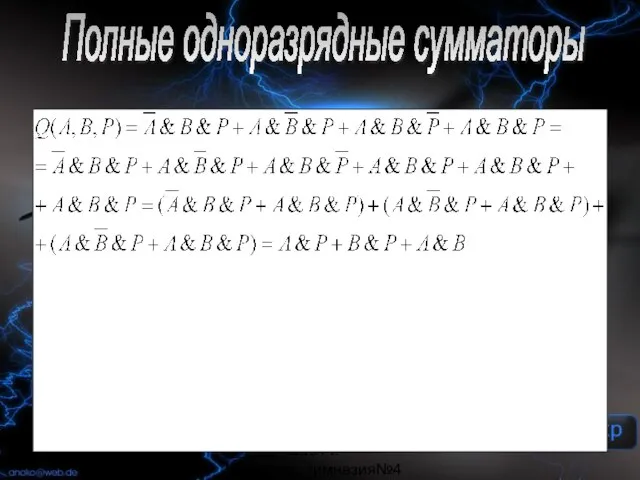

- 19. _______id381 г. Мурманск, гимназия№4 Полные одноразрядные сумматоры

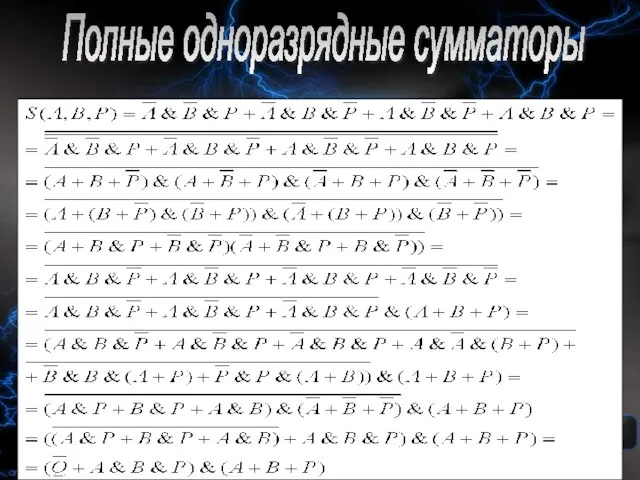

- 20. _______id381 г. Мурманск, гимназия№4 Полные одноразрядные сумматоры

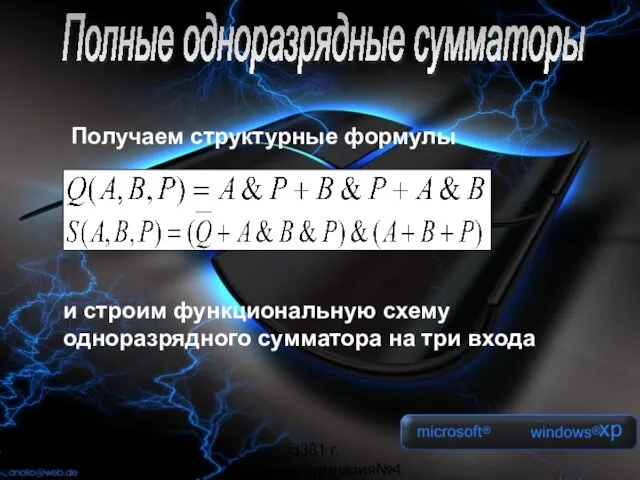

- 21. _______id381 г. Мурманск, гимназия№4 Получаем структурные формулы и строим функциональную схему одноразрядного сумматора на три входа

- 22. _______id381 г. Мурманск, гимназия№4 1 Полные одноразрядные сумматоры 1 & & & & 1 1 &

- 23. _______id381 г. Мурманск, гимназия№4 Параллельные или многоразрядные Параллельные сумматоры комбинационного типа представляют собой композиции одноразрядных суммирующих

- 24. _______id381 г. Мурманск, гимназия№4 Параллельные многоразрядные сумматоры предназначены для одновременного суммирования двух многоразрядных чисел и характеризуются

- 25. _______id381 г. Мурманск, гимназия№4 Простейшими из параллельных сумматоров (ПС) являются ПС с последовательной передачей сигналов переноса

- 26. _______id381 г. Мурманск, гимназия№4 Параллельные многоразрядные сумматоры

- 27. _______id381 г. Мурманск, гимназия№4 Быстродействие сумматора при сложении двух n-разрядных чисел характеризуется временем суммирования, которое в

- 28. _______id381 г. Мурманск, гимназия№4 Серьезным недостатком сумматоров с одновременным переносом является значительный рост аппаратурных затрат при

- 29. _______id381 г. Мурманск, гимназия№4 В сумматорах с комбинированным переносом полные одноразрядные сумматоры объединяются в группы. Внутри

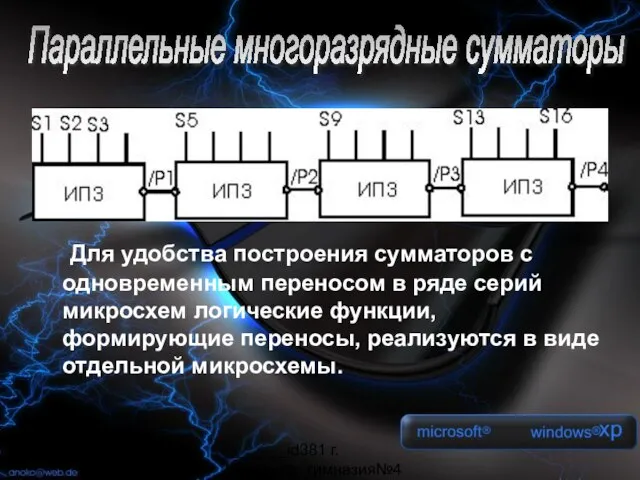

- 30. _______id381 г. Мурманск, гимназия№4 Для удобства построения сумматоров с одновременным переносом в ряде серий микросхем логические

- 32. Скачать презентацию

Стилизация человека

Стилизация человека Евро - валюта Европейских стран

Евро - валюта Европейских стран Общее устройство тормозной системы автомобилей

Общее устройство тормозной системы автомобилей Изменение имён прилагательных по родам и числам 3 класс

Изменение имён прилагательных по родам и числам 3 класс Коммуникативный акт

Коммуникативный акт Космические дали в Перми

Космические дали в Перми Тема текста

Тема текста Конкурс болельщиков

Конкурс болельщиков Сибирский специалитет. Промо – дегустация

Сибирский специалитет. Промо – дегустация О результатах внедрения федеральных государственных требований к структуре основной общеобразовательной программы дошкольного

О результатах внедрения федеральных государственных требований к структуре основной общеобразовательной программы дошкольного  Общее представление о строении металлов

Общее представление о строении металлов Презентация на тему Корней Иванович Чуковский

Презентация на тему Корней Иванович Чуковский «Четвертый канал» «Четвертый канал» - это первая независимая негосударственная телекомпания Екатеринбурга. Наша работа отмечена

«Четвертый канал» «Четвертый канал» - это первая независимая негосударственная телекомпания Екатеринбурга. Наша работа отмечена  Технология распознавания движения Move assistant

Технология распознавания движения Move assistant Микропроцессоры

Микропроцессоры Интерьер как художественно-архитектурная среда и жанр изобразительного искусства. 7 класс

Интерьер как художественно-архитектурная среда и жанр изобразительного искусства. 7 класс Температура воздуха

Температура воздуха Искусство и я (4 класс)

Искусство и я (4 класс) Уникальные животные Тувы

Уникальные животные Тувы Темы 2.1 и 2.2. Организация и схема проведения внешнеэкономической операции при прямых и косвенных связях между контрагентами. Орган

Темы 2.1 и 2.2. Организация и схема проведения внешнеэкономической операции при прямых и косвенных связях между контрагентами. Орган Праздники, традиции, обычаи народов мира

Праздники, традиции, обычаи народов мира Отчет по практике по получению профессиональных навыков

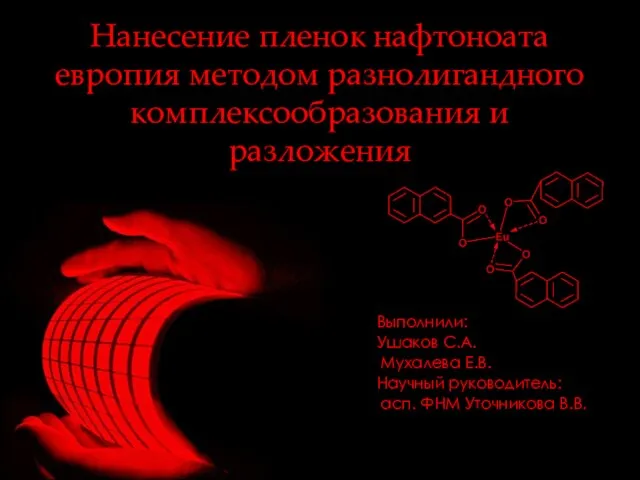

Отчет по практике по получению профессиональных навыков Нанесение пленок нафтоноата европия методом разнолигандного комплексообразования и разложения

Нанесение пленок нафтоноата европия методом разнолигандного комплексообразования и разложения Концертный зал Измайлово ____________________________.

Концертный зал Измайлово ____________________________. Предзаказы на 8 марта. Шашлычная

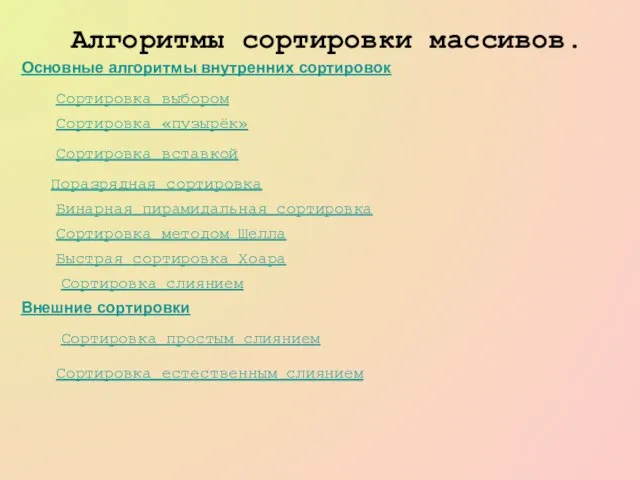

Предзаказы на 8 марта. Шашлычная Алгоритмы сортировки массивов.

Алгоритмы сортировки массивов. Безопасность на водных объектах

Безопасность на водных объектах Информационные модели 6-7 класс

Информационные модели 6-7 класс