Содержание

- 2. Основные устройства АЛУ АЛУ – арифметическо-логическое устройство, входит в состав процессора Выполняет арифметические и логические операции

- 3. Триггер Триггер - это устройство последова-тельного типа с двумя устойчивыми состояниями равновесия, предназна-ченное для записи и

- 4. Триггер RS-триггер или SR-триггер — триггер, который сохраня-ет своё предыдущее состоя-ние при нулевых входах, и меняет

- 5. Триггер Один триггер хранит бит информации. Для хранения 1 байта необходимо ? триггеров Динамическая память (оперативная)

- 6. Регистр Несколько триггеров можно объединить в регистр – устройство для хранения чисел с двоичным представлением цифр

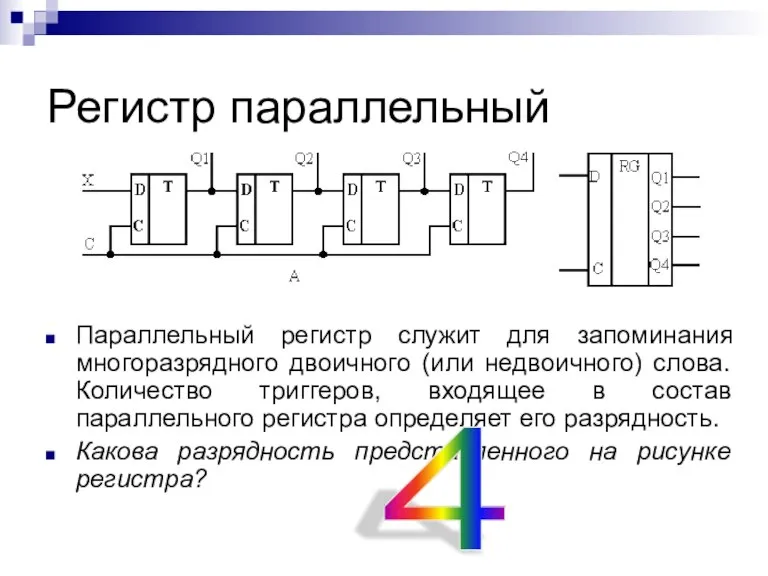

- 7. Регистр параллельный Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. Количество триггеров, входящее в

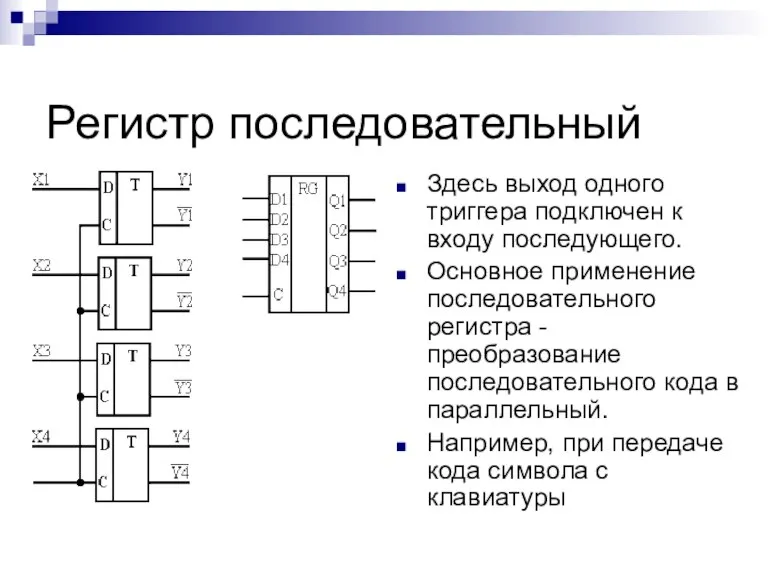

- 8. Регистр последовательный Здесь выход одного триггера подключен к входу последующего. Основное применение последовательного регистра - преобразование

- 9. Типы регистров Сумматор – регистр АЛУ, способный производить сложение, участвует в выполнении каждой арифметической операции Сдвиговый

- 10. Сумматор Сумматор является центральным узлом арифметическо-логического устройства компьютера Сумматор выполняет сложение много-значных двоичных чисел Он представляет

- 11. Сумматор По числу входов и выходов одноразрядных двоичных сумматоров различают: полусумматоры, характеризующиеся наличием двух входов, на

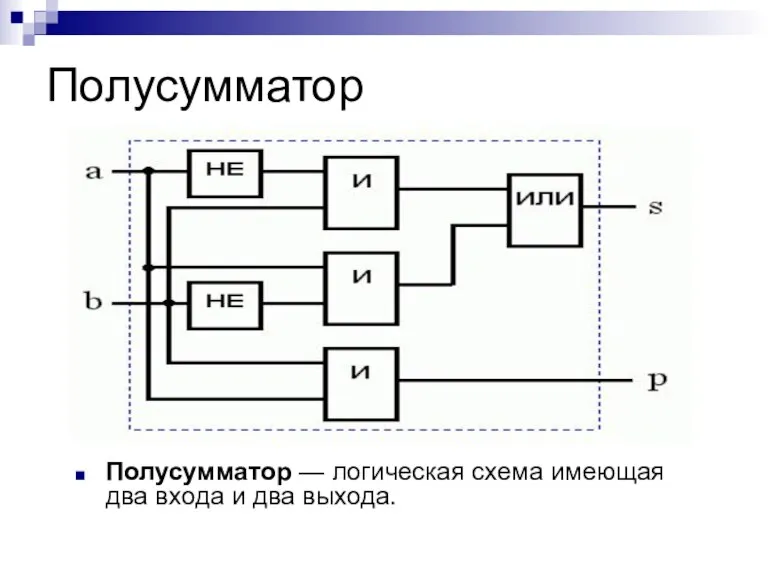

- 12. Полусумматор Полусумматор — логическая схема имеющая два входа и два выхода.

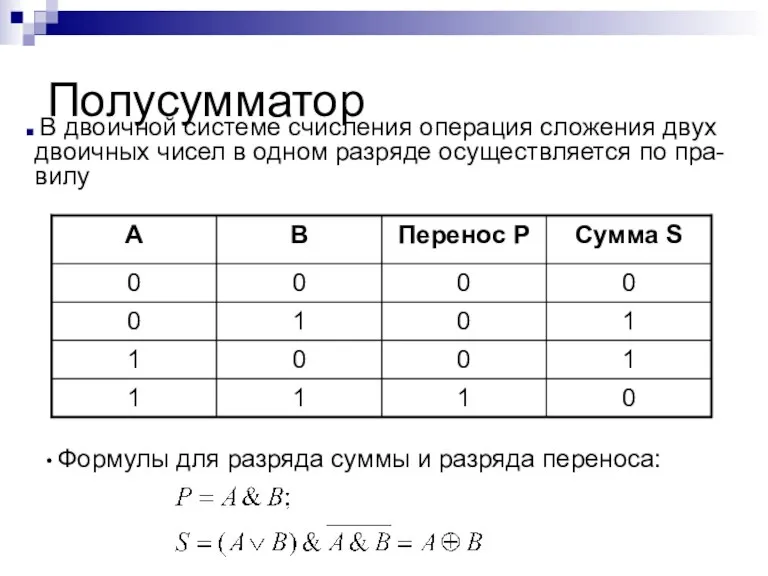

- 13. Полусумматор Формулы для разряда суммы и разряда переноса: В двоичной системе счисления операция сложения двух двоичных

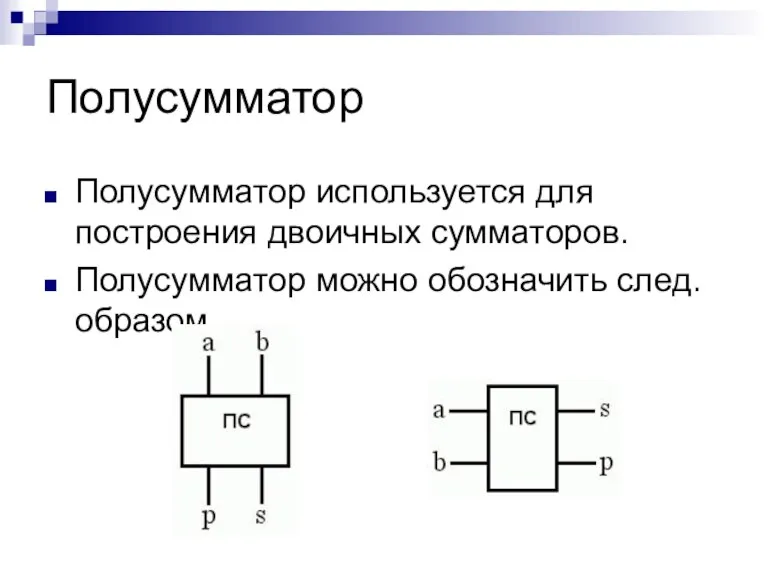

- 14. Полусумматор Полусумматор используется для построения двоичных сумматоров. Полусумматор можно обозначить след. образом

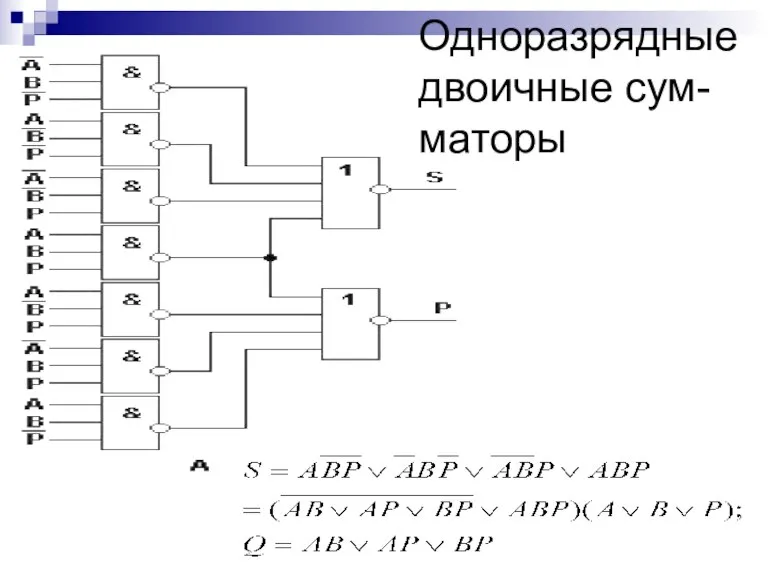

- 15. Одноразрядные двоичные сумматоры характеризующиеся нали-чием трёх входов, на которые подаются одноимённые раз-ряды двух складываемых чисел и

- 16. Одноразрядные двоичные сумматоры

- 17. Одноразрядные двоичные сум-маторы

- 19. Скачать презентацию

Черепно-мозговая травма

Черепно-мозговая травма  Предельные одноосновные карбоновые кислоты

Предельные одноосновные карбоновые кислоты ВРЕДНЫЕ ПРИВЫЧКИ

ВРЕДНЫЕ ПРИВЫЧКИ Альберт Дюрер (1471-1528)

Альберт Дюрер (1471-1528) Презентация на тему Изменчивость Мутации

Презентация на тему Изменчивость Мутации АЛЬТЕРНАТИВНЫЕ СТАРТЫ ТРАНСКРИПЦИИ И ИХ СВЯЗЬ С CpG-ОСТРОВАМИ

АЛЬТЕРНАТИВНЫЕ СТАРТЫ ТРАНСКРИПЦИИ И ИХ СВЯЗЬ С CpG-ОСТРОВАМИ Time management

Time management Презентация на классный час на тему_ Россия-страна возможностей_

Презентация на классный час на тему_ Россия-страна возможностей_ Наши ошибки в воспитании детей

Наши ошибки в воспитании детей Великая Отечественная Война1941-1945г.

Великая Отечественная Война1941-1945г. Род имён существительных (3 класс)

Род имён существительных (3 класс) rosreestr.ru

rosreestr.ru Стармикс Haribo

Стармикс Haribo Возможность CorelDRAW X3

Возможность CorelDRAW X3 Понятие о Богослужении

Понятие о Богослужении Простые предложения, осложненные обособленными членами предложения

Простые предложения, осложненные обособленными членами предложения В. В. ЛОСЕВПреступления против интересов службы: юридический анализ и правила квалификации

В. В. ЛОСЕВПреступления против интересов службы: юридический анализ и правила квалификации Тема 5. Правовое обеспечение интеллектуальной собственности

Тема 5. Правовое обеспечение интеллектуальной собственности 2008 г.

2008 г. Гравитационные стеллажи

Гравитационные стеллажи Комплекс упражнений "Полет к звезде"

Комплекс упражнений "Полет к звезде" El Transcantabrico 2011

El Transcantabrico 2011 Днепропетровск

Днепропетровск Типология современного урока

Типология современного урока Религия, ее место в жизни древних греков

Религия, ее место в жизни древних греков Потенциометр

Потенциометр Рекламное бюро. Создание бюро

Рекламное бюро. Создание бюро Преимущества применения геотекстиля в дорожном строительстве.

Преимущества применения геотекстиля в дорожном строительстве.