Содержание

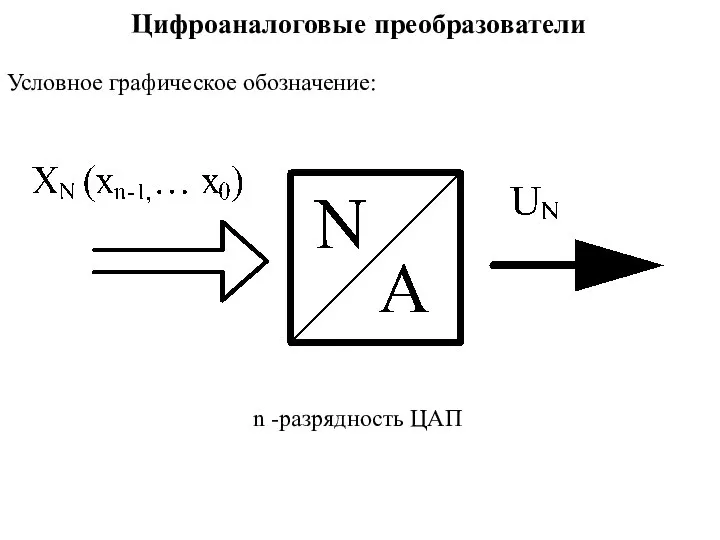

- 2. Условное графическое обозначение: n -разрядность ЦАП Цифроаналоговые преобразователи

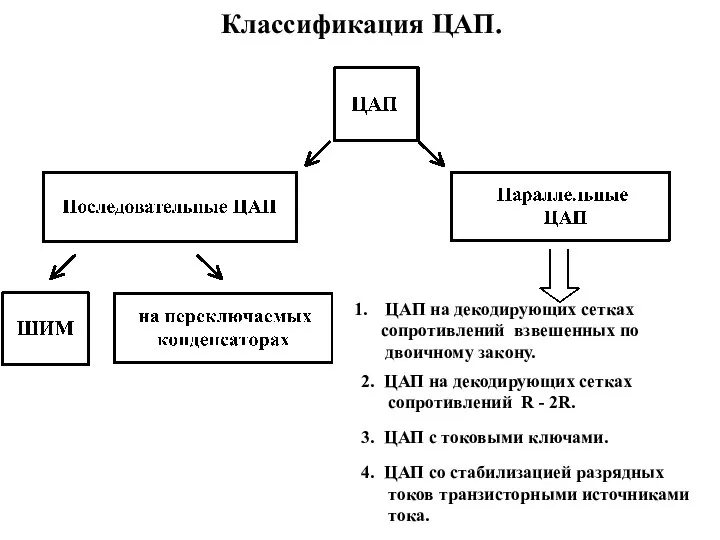

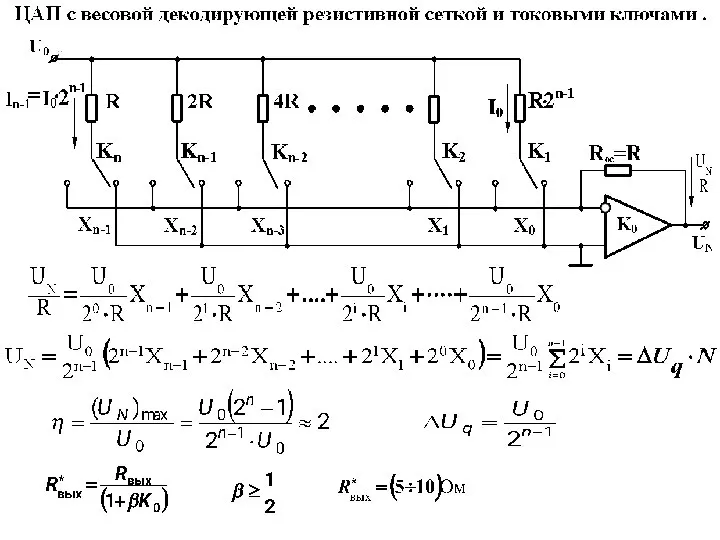

- 3. Классификация ЦАП. ЦАП на декодирующих сетках сопротивлений взвешенных по двоичному закону. 2. ЦАП на декодирующих сетках

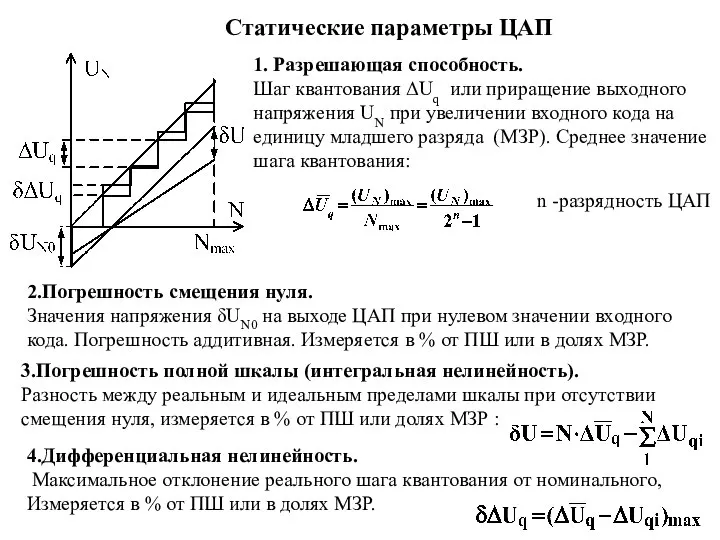

- 4. Статические параметры ЦАП 1. Разрешающая способность. Шаг квантования ΔUq или приращение выходного напряжения UN при увеличении

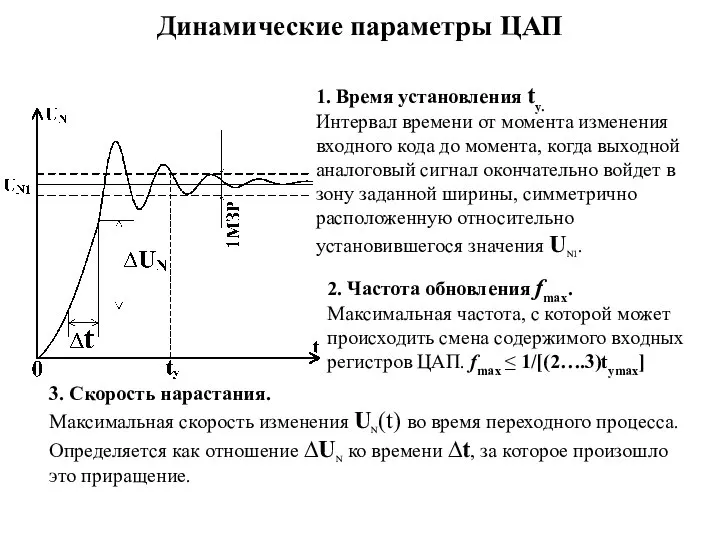

- 5. Динамические параметры ЦАП 1. Время установления tу. Интервал времени от момента изменения входного кода до момента,

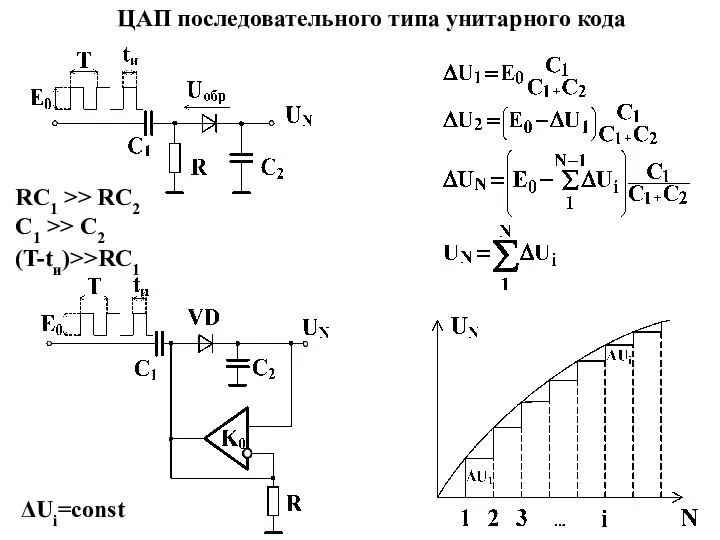

- 6. ΔUi=const ЦАП последовательного типа унитарного кода (T-tи)>>RC1

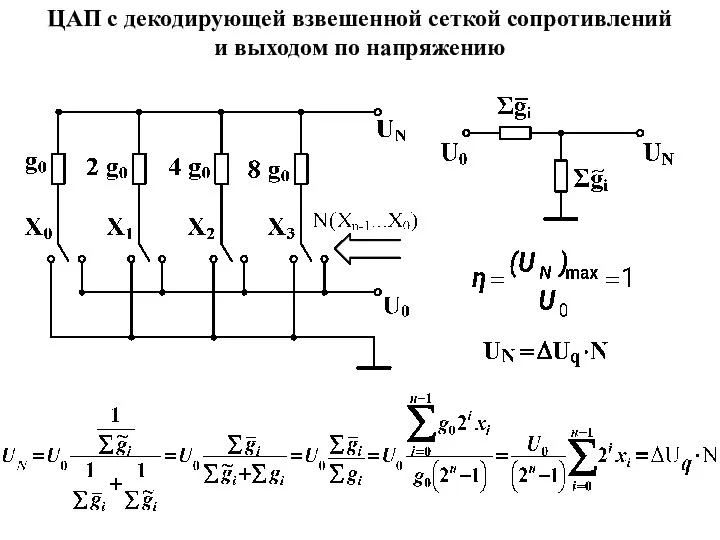

- 7. ЦАП с декодирующей взвешенной сеткой сопротивлений и выходом по напряжению

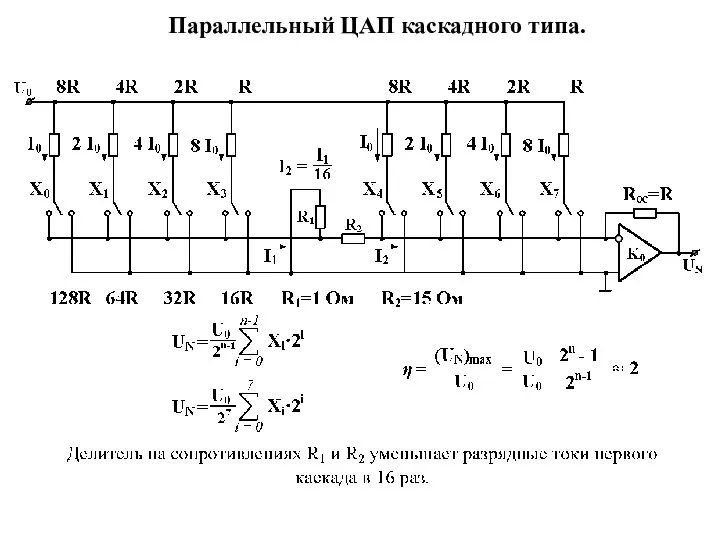

- 9. Параллельный ЦАП каскадного типа.

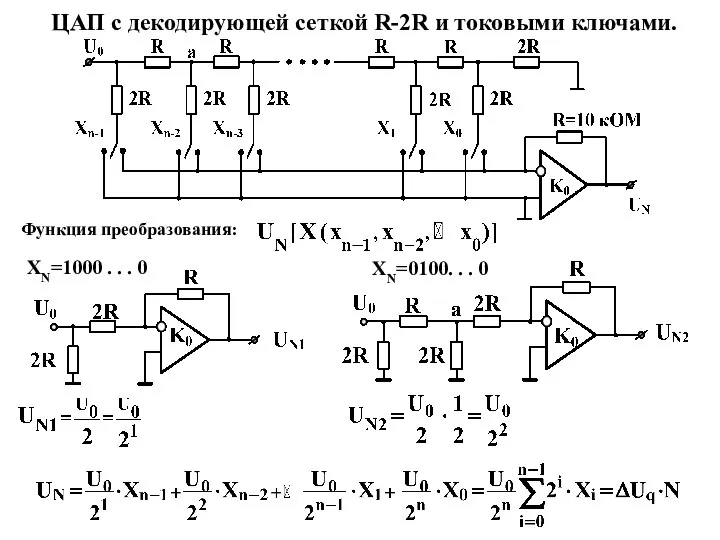

- 10. ЦАП с декодирующей сеткой R-2R и токовыми ключами. Функция преобразования:

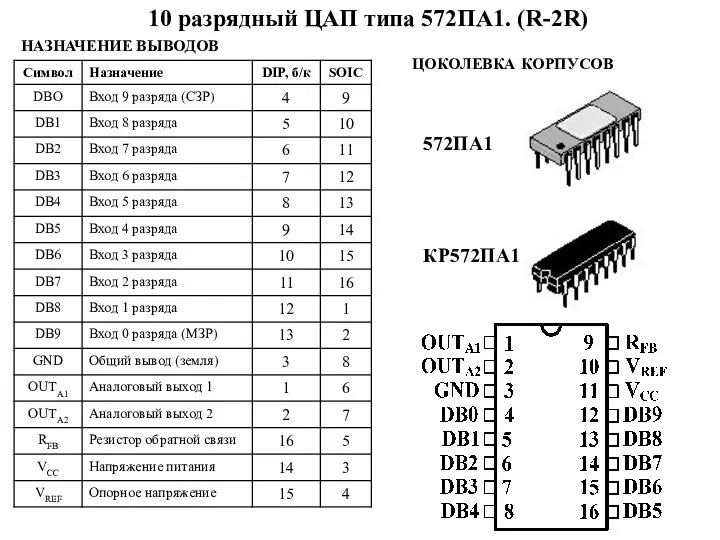

- 11. НАЗНАЧЕНИЕ ВЫВОДОВ 10 разрядный ЦАП типа 572ПА1. (R-2R) Основные электрические параметры при: ТА=+25 ±10ºС, VCC=+15В ±10%,

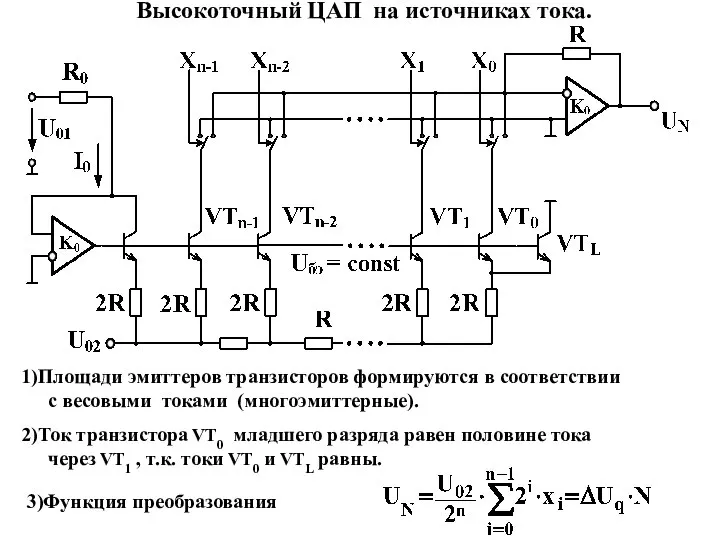

- 12. Высокоточный ЦАП на источниках тока. 1)Площади эмиттеров транзисторов формируются в соответствии с весовыми токами (многоэмиттерные). 2)Ток

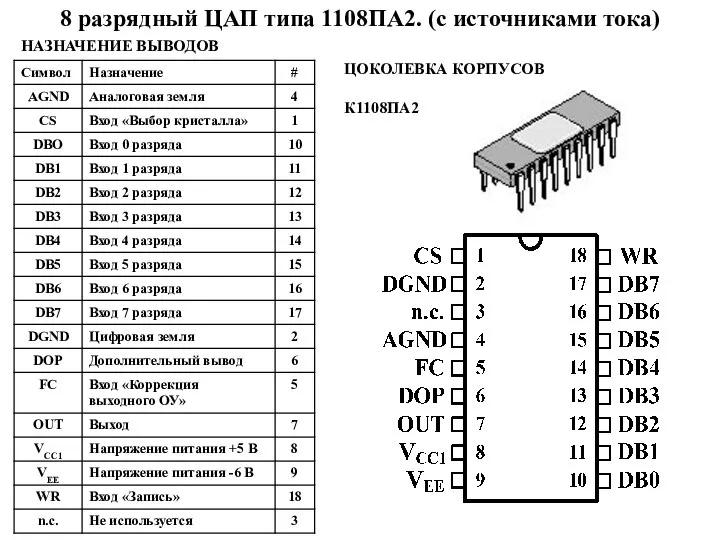

- 13. НАЗНАЧЕНИЕ ВЫВОДОВ 8 разрядный ЦАП типа 1108ПА2. (с источниками тока) Основные электрические параметры при: ТА=+25ºС, VCC=+5..15В

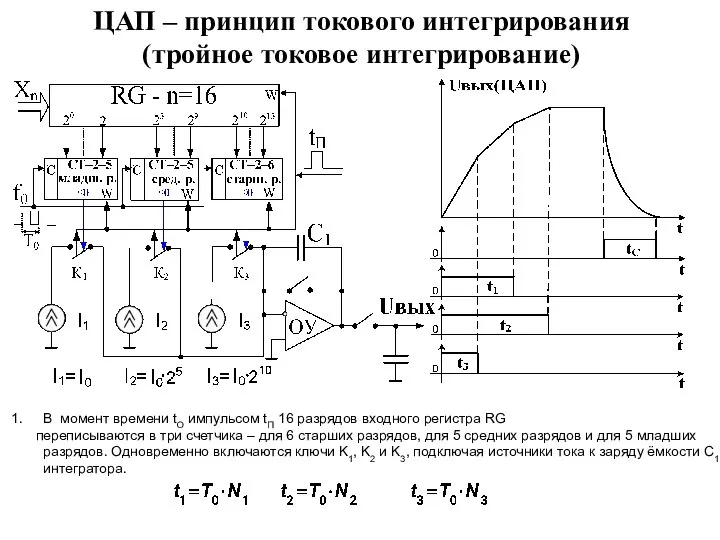

- 14. ЦАП – принцип токового интегрирования (тройное токовое интегрирование) В момент времени tО импульсом tП 16 разрядов

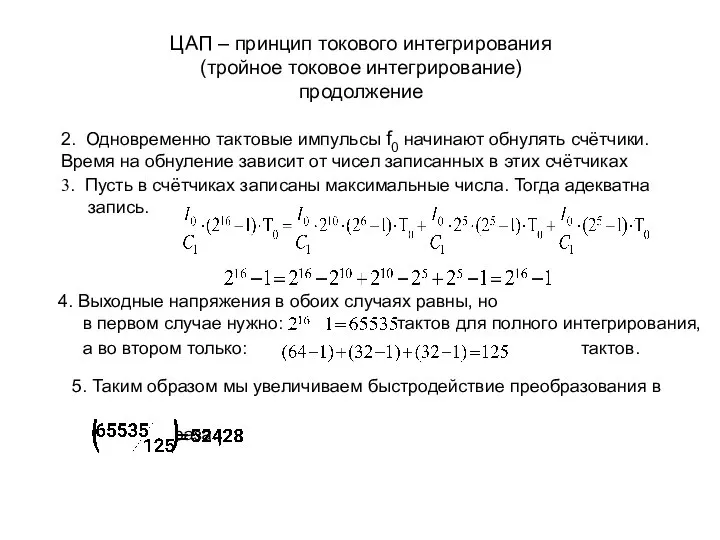

- 15. ЦАП – принцип токового интегрирования (тройное токовое интегрирование) продолжение 2. Одновременно тактовые импульсы f0 начинают обнулять

- 16. Интерфейсы цифроаналоговых преобразователей. Цифровые интерфейсы выполняют функцию связи управляющих входов ключей ЦАП с источниками цифровых сигналов

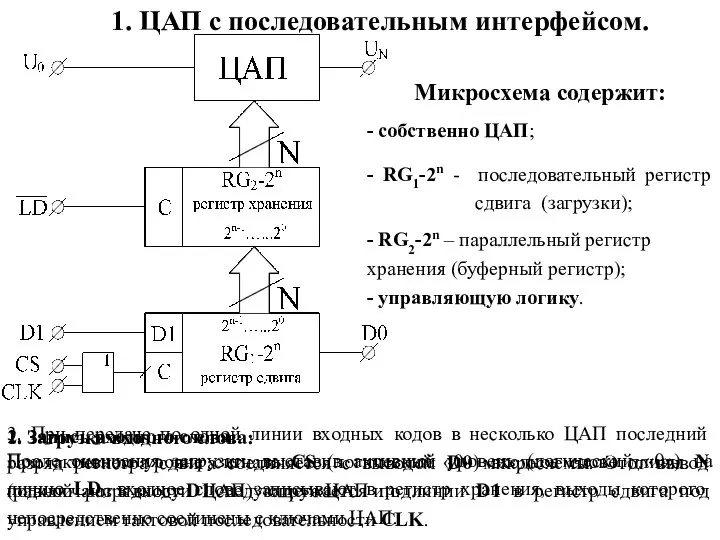

- 17. 1. ЦАП с последовательным интерфейсом. Микросхема содержит: - собственно ЦАП; - RG1-2n - последовательный регистр сдвига

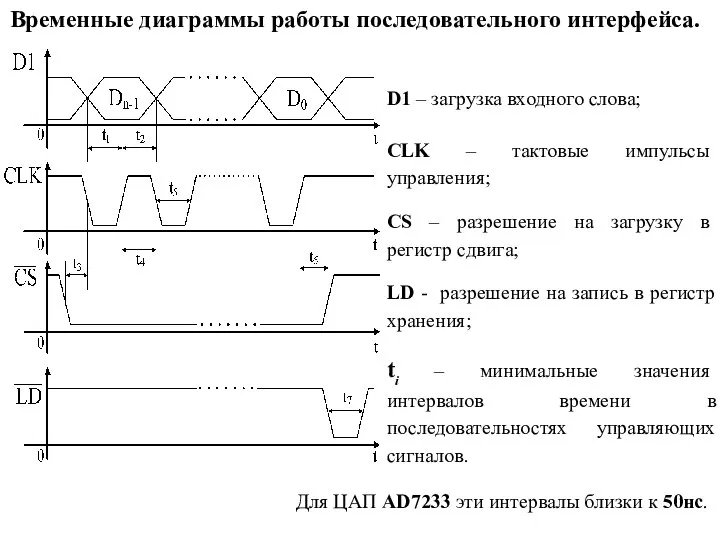

- 18. Временные диаграммы работы последовательного интерфейса. D1 – загрузка входного слова; CLK – тактовые импульсы управления; СS

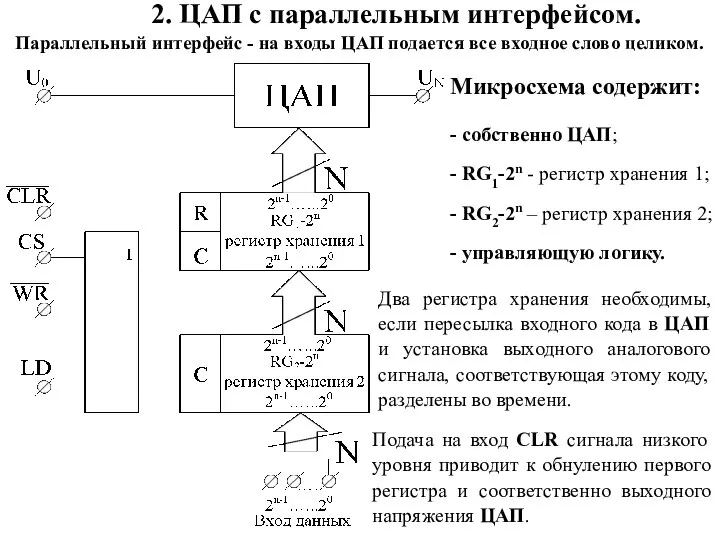

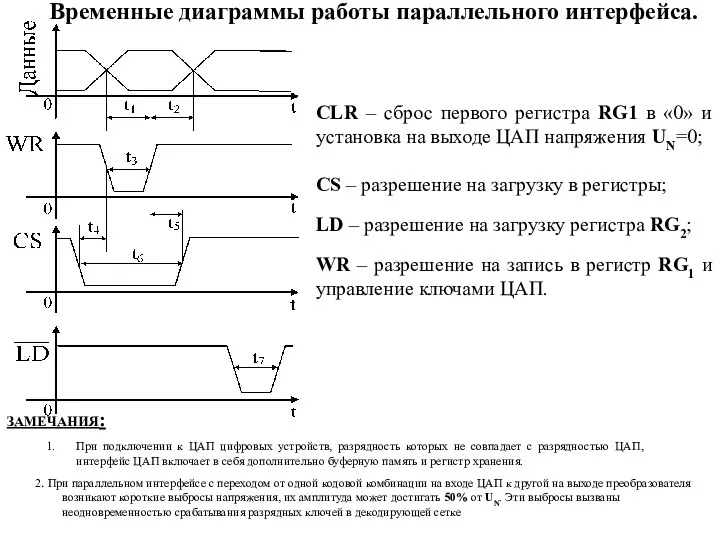

- 19. 2. ЦАП с параллельным интерфейсом. Параллельный интерфейс - на входы ЦАП подается все входное слово целиком.

- 20. При подключении к ЦАП цифровых устройств, разрядность которых не совпадает с разрядностью ЦАП, интерфейс ЦАП включает

- 22. Скачать презентацию

Межпредметные связи математики и физики

Межпредметные связи математики и физики Г. Х Андерсен «Снежная королева»

Г. Х Андерсен «Снежная королева» Вопросы применения метода RAB

Вопросы применения метода RAB Гражданское право

Гражданское право Диана пр1

Диана пр1 Параллельность прямых в пространстве

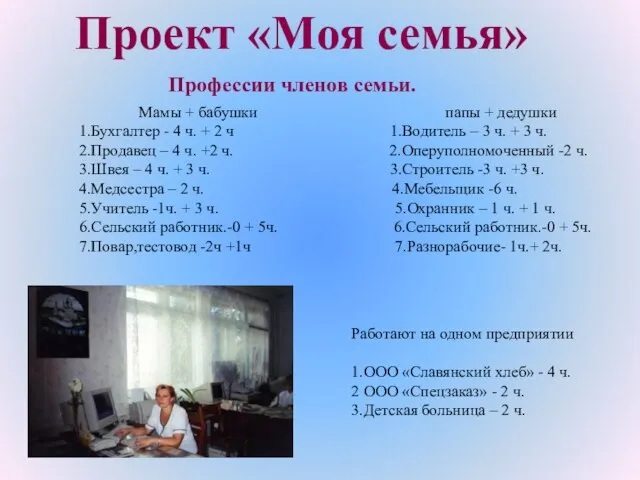

Параллельность прямых в пространстве Проект "Моя семья" 2 класс

Проект "Моя семья" 2 класс Һөйләмдә һүҙҙәр тәртибе

Һөйләмдә һүҙҙәр тәртибе С2.1 ГИА.

С2.1 ГИА. Представление опыта работы по организации профильных смен в учреждении дополнительного образования ДДТ У Белого озера

Представление опыта работы по организации профильных смен в учреждении дополнительного образования ДДТ У Белого озера История возникновения геометрии

История возникновения геометрии Кластеризация. Структура экзаменационных билетов

Кластеризация. Структура экзаменационных билетов Почему нужно есть много овощей и фруктов?

Почему нужно есть много овощей и фруктов? Лечебно-консультативная работа Сотрудниками кафедры ежегодно выполняется около 1200 наиболее сложных оперативных вмешательств (ок

Лечебно-консультативная работа Сотрудниками кафедры ежегодно выполняется около 1200 наиболее сложных оперативных вмешательств (ок ПРЕЗЕНТАЦИЯ

ПРЕЗЕНТАЦИЯ Высокоинтеллектуальные инновационные интернет технологии viitcompany.ru

Высокоинтеллектуальные инновационные интернет технологии viitcompany.ru День матери - это один из самых трогательных праздников, потому что каждый из нас с детства и до своих последних дней несет в своей д

День матери - это один из самых трогательных праздников, потому что каждый из нас с детства и до своих последних дней несет в своей д Растамани

Растамани Дело MSU

Дело MSU "Катюша"БМ - 13 оружие победы

"Катюша"БМ - 13 оружие победы Циолковский Константин Эдуардович

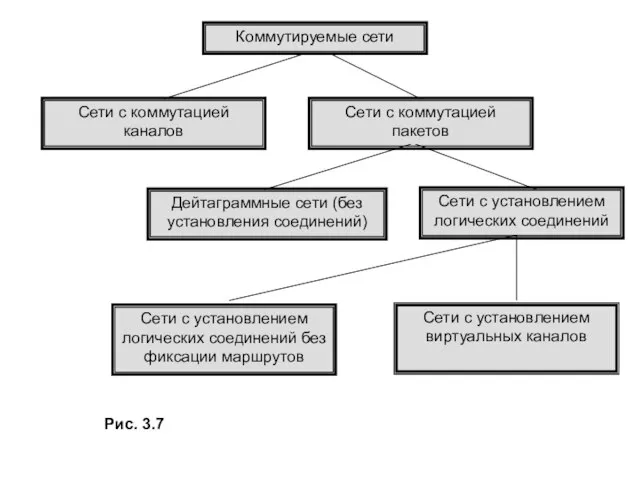

Циолковский Константин Эдуардович  Коммутируемые сети

Коммутируемые сети Административная юрисдикция

Административная юрисдикция Правонарушение. Преступление. Ответственность

Правонарушение. Преступление. Ответственность Эффективность поисковой рекламы: измерение конверсии в звонки (Call Tracking)

Эффективность поисковой рекламы: измерение конверсии в звонки (Call Tracking) K2_house

K2_house 2.Классы_эквивалентности_и_граничные_значения-235856-fb64ce

2.Классы_эквивалентности_и_граничные_значения-235856-fb64ce С новым годом !

С новым годом !