Слайд 2Цели и задачи

Разработать и описать конструкцию тестового кристалла

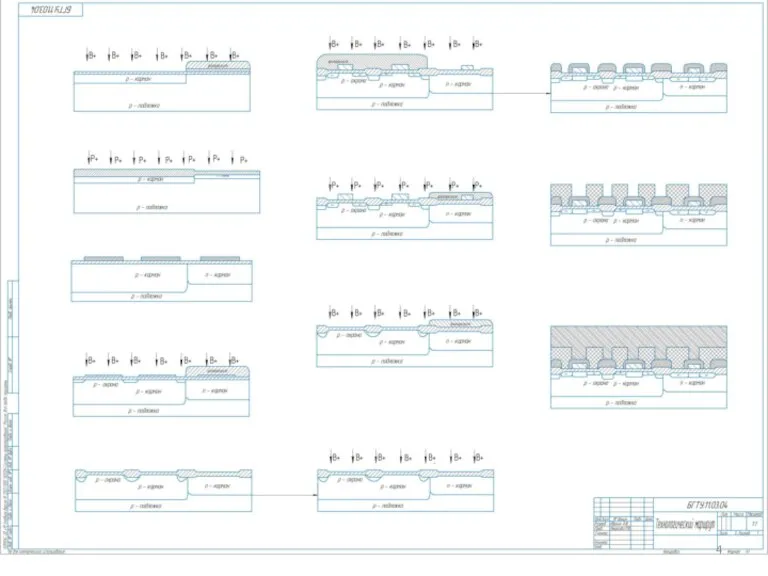

Разработать и описать технологию тестового

кристалла

Измерить и проанализировать параметры тестовых ячеек

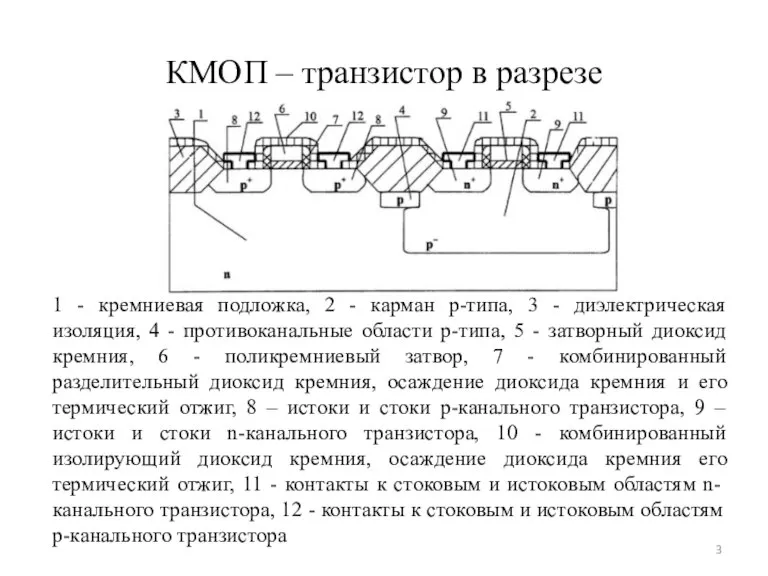

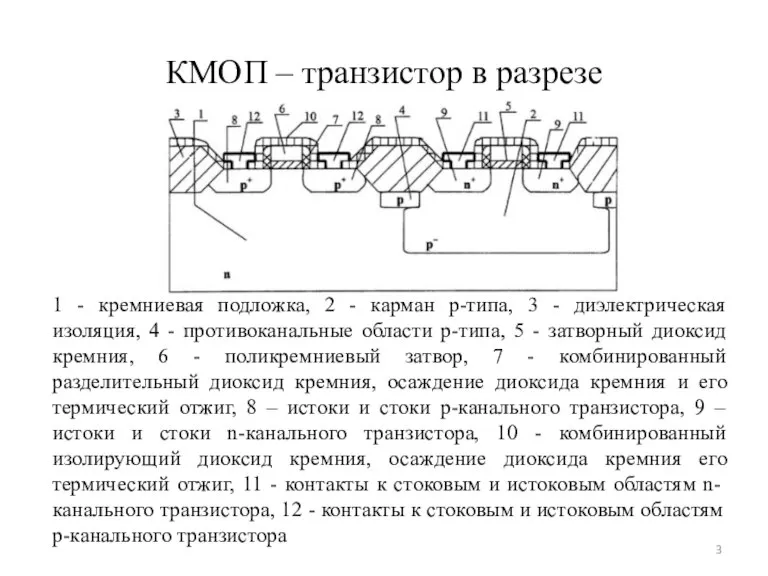

Слайд 3КМОП – транзистор в разрезе

1 - кремниевая подложка, 2 - карман р-типа,

3 - диэлектрическая изоляция, 4 - противоканальные области р-типа, 5 - затворный диоксид кремния, 6 - поликремниевый затвор, 7 - комбинированный разделительный диоксид кремния, осаждение диоксида кремния и его термический отжиг, 8 – истоки и стоки р-канального транзистора, 9 – истоки и стоки n-канального транзистора, 10 - комбинированный изолирующий диоксид кремния, осаждение диоксида кремния его термический отжиг, 11 - контакты к стоковым и истоковым областям n-канального транзистора, 12 - контакты к стоковым и истоковым областям р-канального транзистора

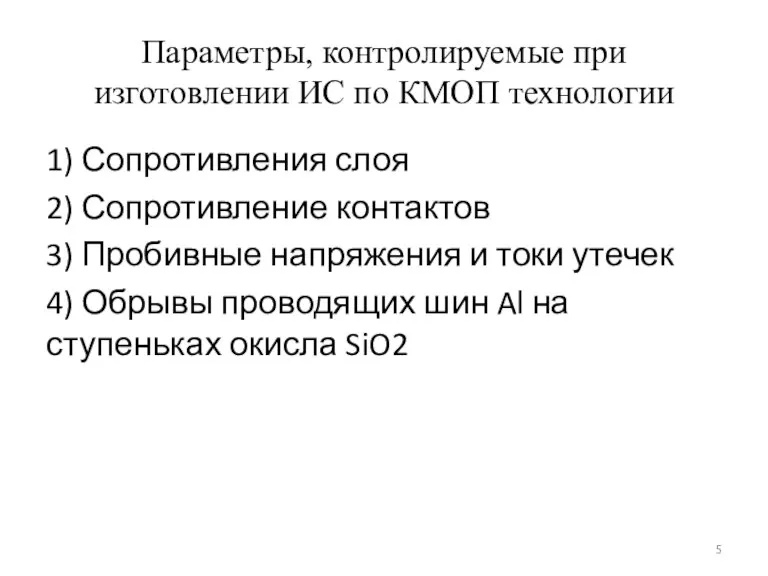

Слайд 5Параметры, контролируемые при изготовлении ИС по КМОП технологии

1) Сопротивления слоя

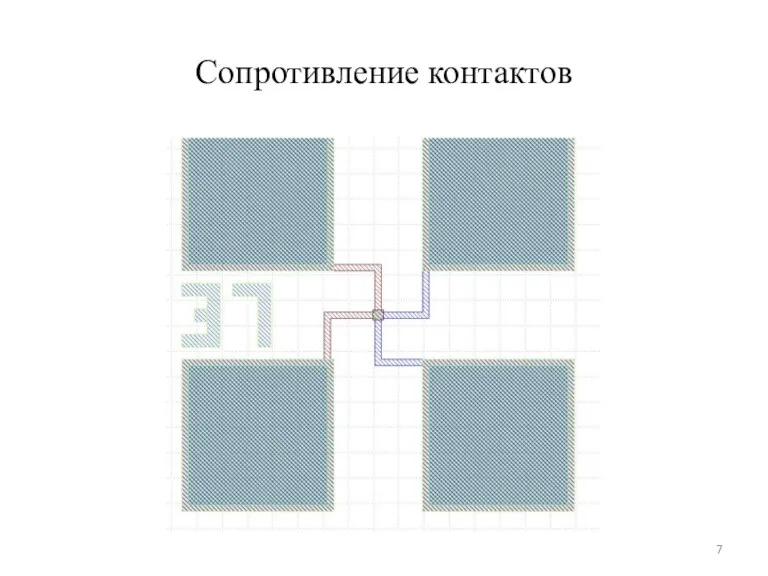

2) Сопротивление контактов

3)

Пробивные напряжения и токи утечек

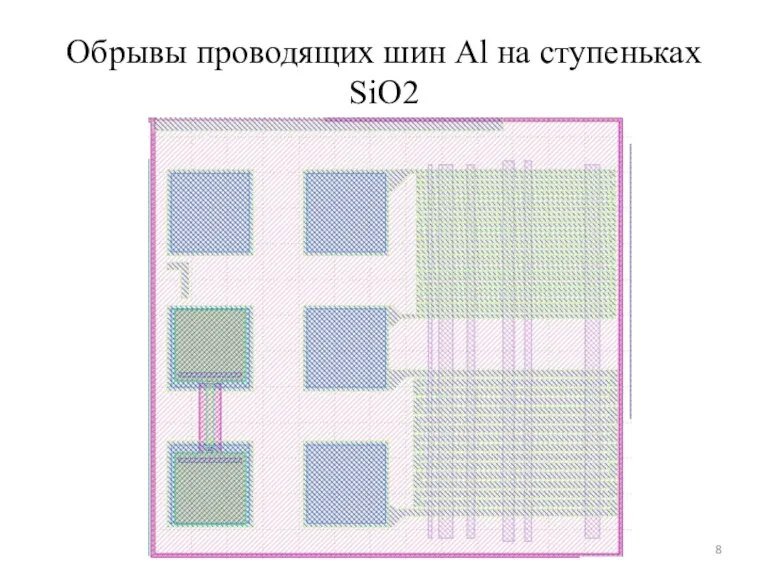

4) Обрывы проводящих шин Al на ступеньках окисла SiO2

Слайд 6Контроль сопротивления слоя

Фигура Ван дер Пау

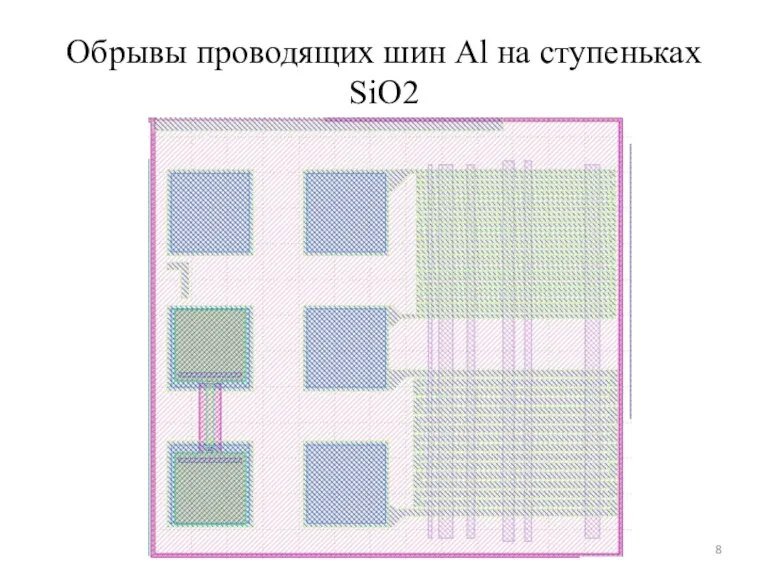

Слайд 8Обрывы проводящих шин Al на ступеньках SiO2

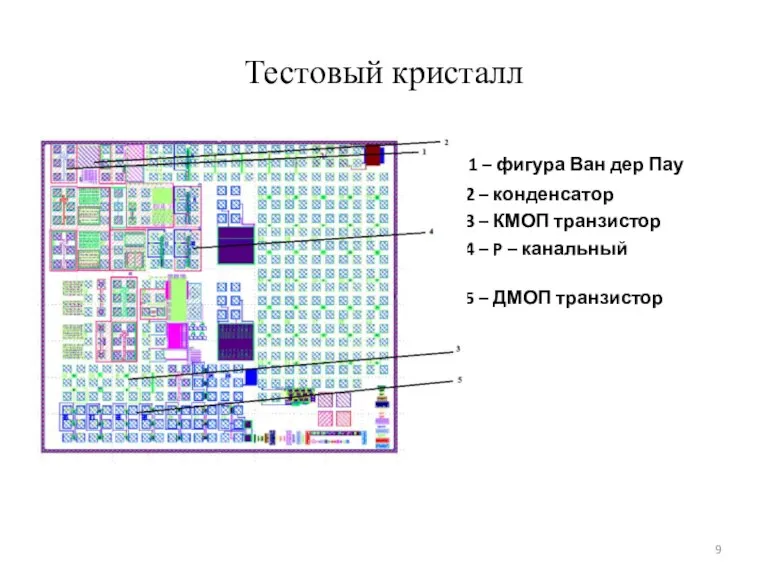

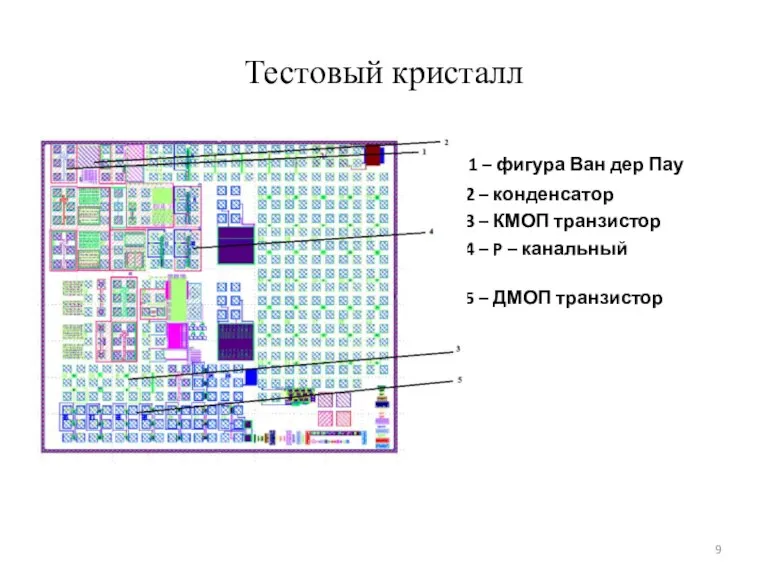

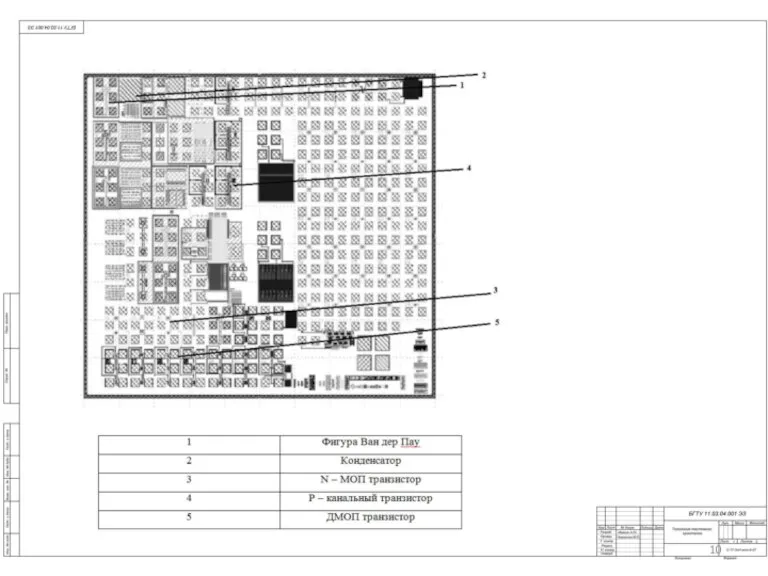

Слайд 9Тестовый кристалл

1 – фигура Ван дер Пау

2 – конденсатор

3 – КМОП транзистор

4 – P – канальный транзистор

5 – ДМОП транзистор

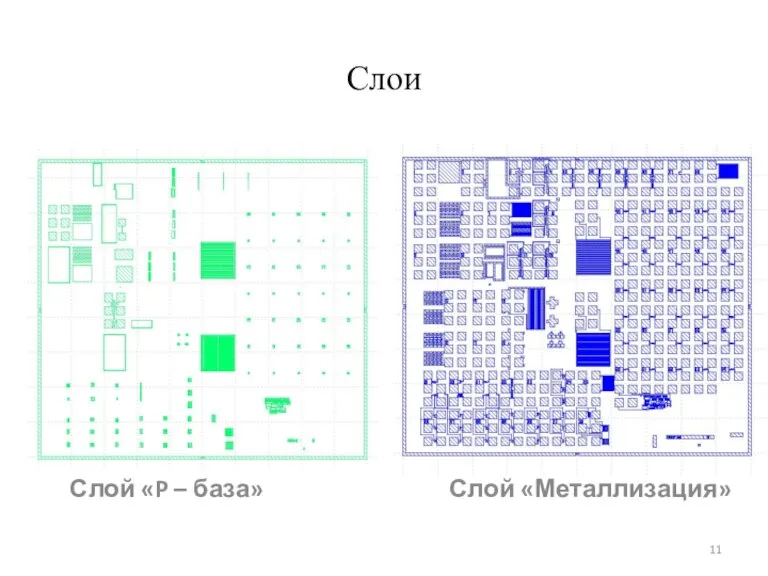

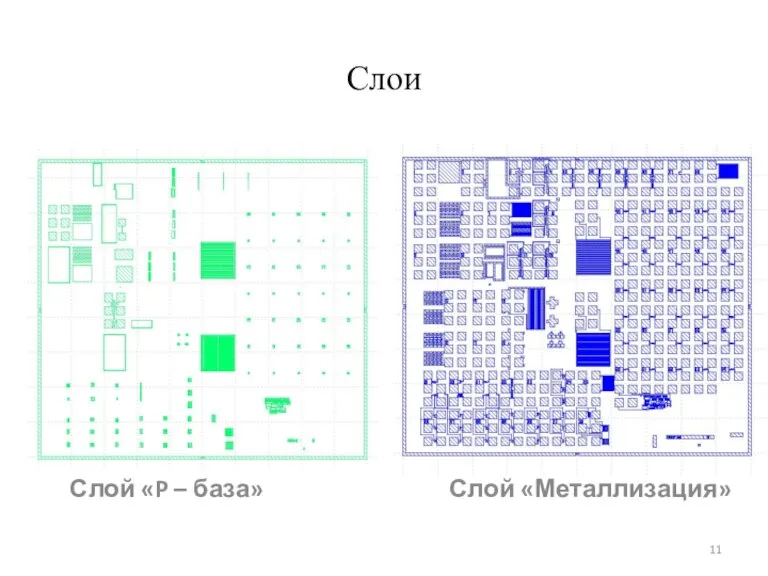

Слайд 11Слои

Слой «P – база» Слой «Металлизация»

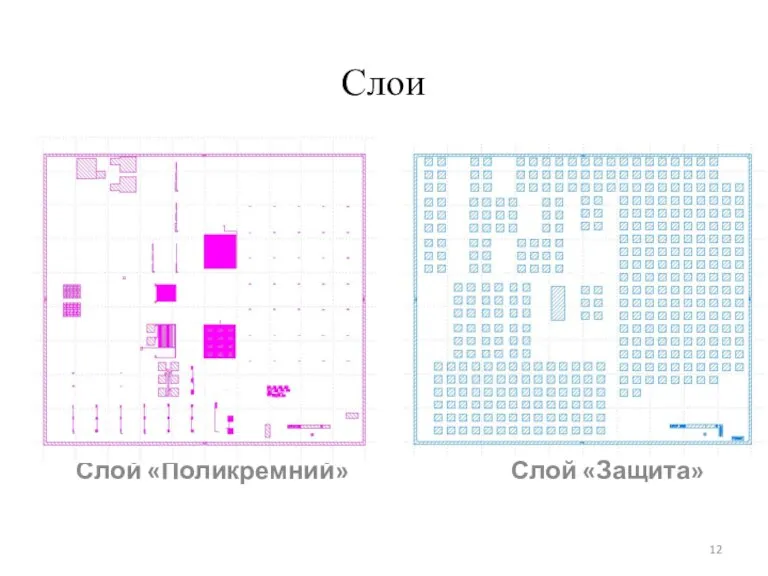

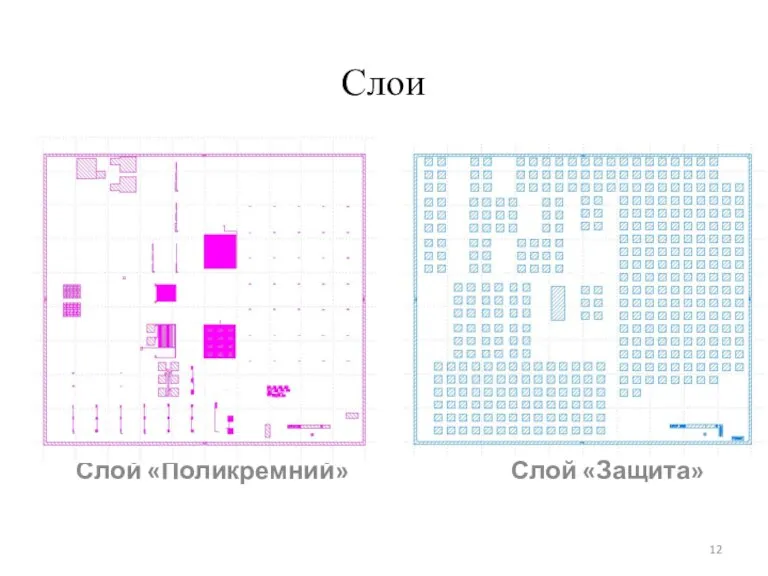

Слайд 12Слои

Слой «Поликремний» Слой «Защита»

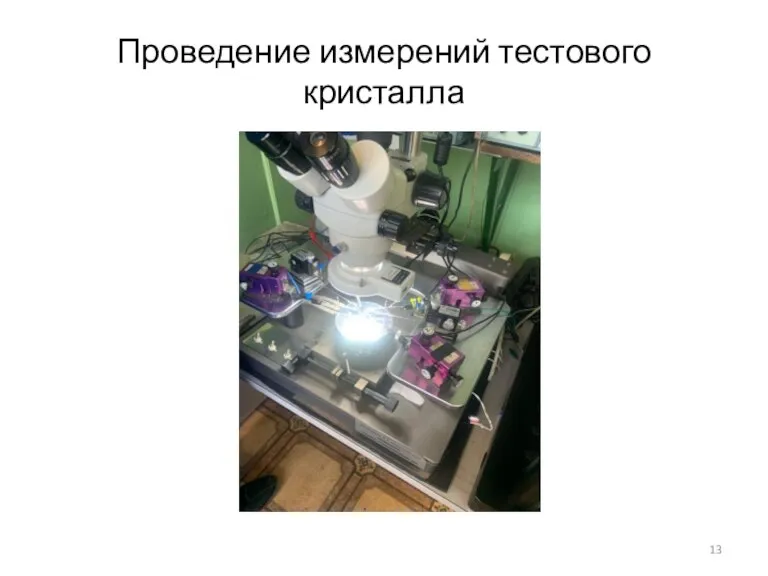

Слайд 13Проведение измерений тестового кристалла

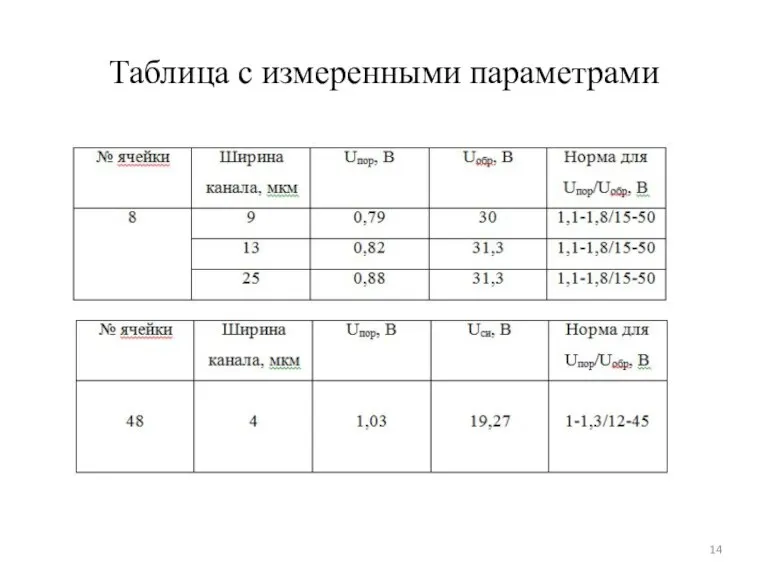

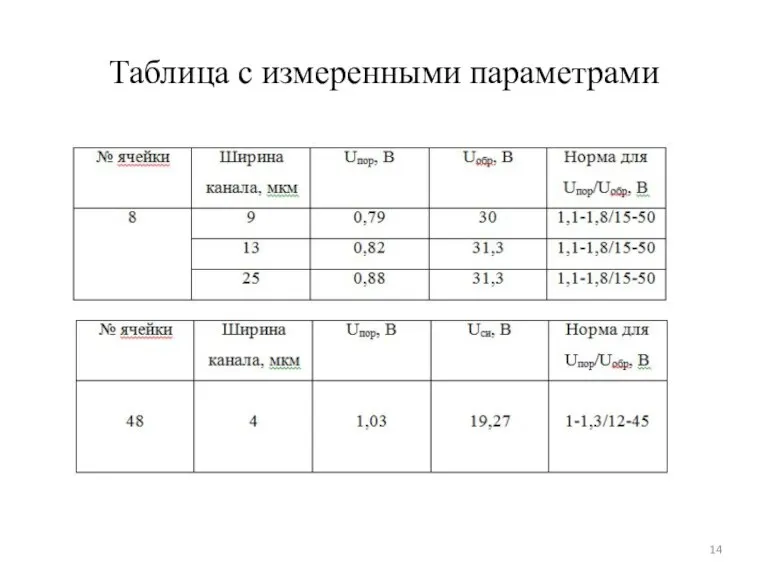

Слайд 14Таблица с измеренными параметрами

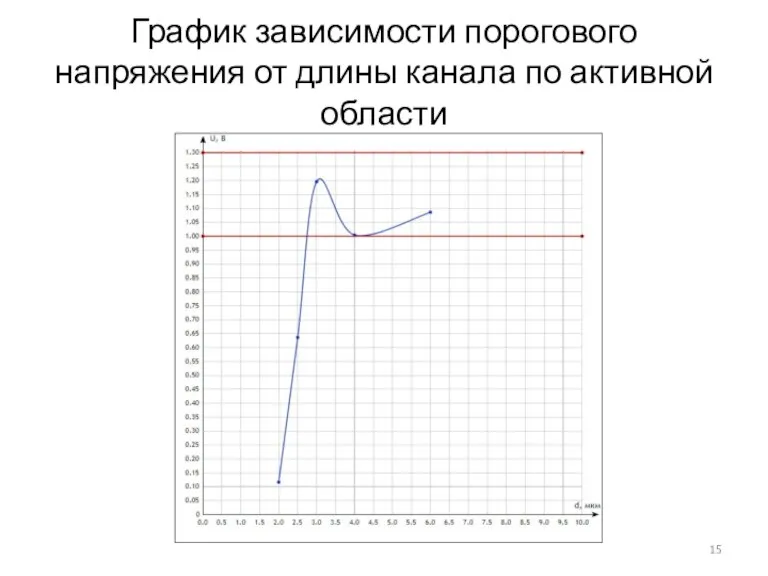

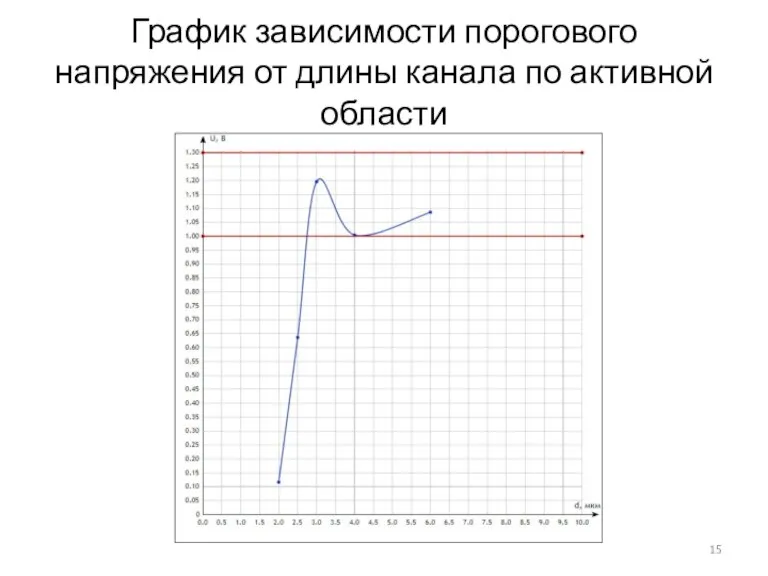

Слайд 15График зависимости порогового напряжения от длины канала по активной области

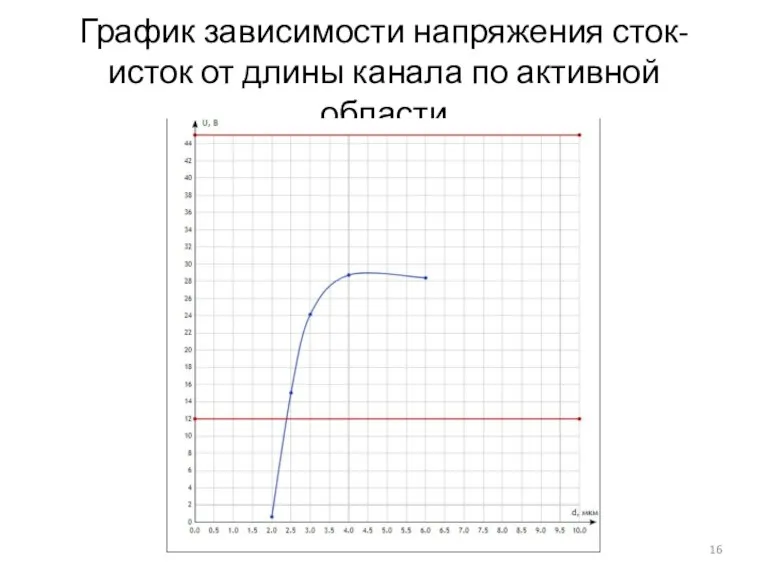

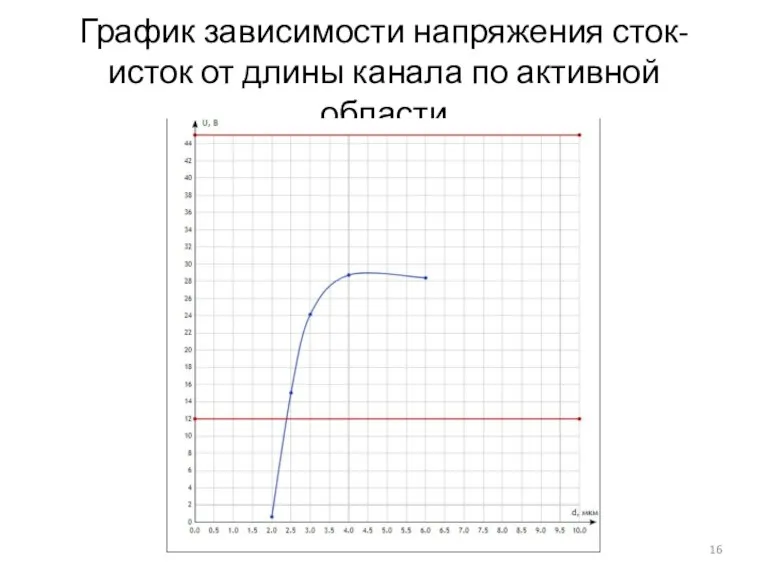

Слайд 16График зависимости напряжения сток-исток от длины канала по активной области

Слайд 17Результаты

Была разработана конструкция тестовых ячеек для контроля параметров ИС выполненных по КМОП

технологии

Была разработана технология тестовых ячеек для контроля параметров ИС выполненных по КМОП технологии

Измерены параметры тестового транзистора и построены зависимости пороговых напряжений и напряжений сток-исток от длины канала по активной области.

Индивидуальные особенности младшего дошкольного и старшего дошкольного возраста

Индивидуальные особенности младшего дошкольного и старшего дошкольного возраста Энциклопедия слова - земляника

Энциклопедия слова - земляника ООО «Аквасток-монтаж»

ООО «Аквасток-монтаж» 3aff641d30b4094e

3aff641d30b4094e Презентація (2)

Презентація (2) Цель: Научиться варить мыло в домашних условиях Задачи:1. Познакомиться с историей возникновения мыла. 2.Узнать технологию его изго

Цель: Научиться варить мыло в домашних условиях Задачи:1. Познакомиться с историей возникновения мыла. 2.Узнать технологию его изго Бакалавриат заочное отделение. Направления и профили подготовки

Бакалавриат заочное отделение. Направления и профили подготовки Презентация на тему Координатный луч (5 класс)

Презентация на тему Координатный луч (5 класс) Кабинет 510, тел 660-480

Кабинет 510, тел 660-480 Моббинг

Моббинг Лобачевский и его геометрия

Лобачевский и его геометрия Методические рекомендации по созданию мини-проектов в Microsoft PowerPoint

Методические рекомендации по созданию мини-проектов в Microsoft PowerPoint Восьмеричная система счисления

Восьмеричная система счисления История государственного флага РФ

История государственного флага РФ Технологии социального партнерства в деятельности образовательного учреждения

Технологии социального партнерства в деятельности образовательного учреждения Презентация на тему Права и свободы по Конституции РФ

Презентация на тему Права и свободы по Конституции РФ Нефте - и - водонасыщенность коллекторов

Нефте - и - водонасыщенность коллекторов Presentation Title

Presentation Title  PRESENT SIMPLE TENSE Настоящее простое время

PRESENT SIMPLE TENSE Настоящее простое время  Основные правила и принципы гражданского процесса

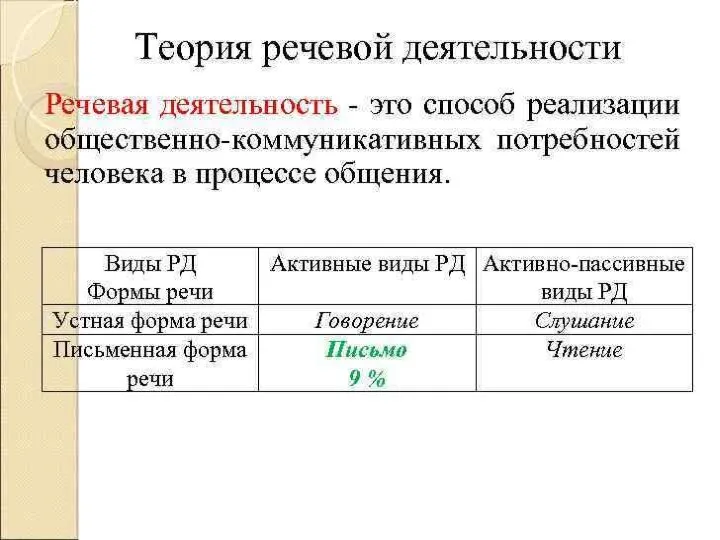

Основные правила и принципы гражданского процесса Теория речевой деятельности. Письмо как вид РД

Теория речевой деятельности. Письмо как вид РД Сергий Радонежский: идеальный образ русского святого(по агиографической повести Епифания Премудрого «Житие преподобного от

Сергий Радонежский: идеальный образ русского святого(по агиографической повести Епифания Премудрого «Житие преподобного от Китай

Китай Образовательный стандарт. История возникновения и развития в РФ

Образовательный стандарт. История возникновения и развития в РФ Стандарты оказания услуг салона красоты Beauty house

Стандарты оказания услуг салона красоты Beauty house АССОЦИАЦИЯ «МЕЖДУНАРОДНЫЙ КОНГРЕСС КАЧЕСТВА ТЕЛЕКОММУНИКАЦИЙ»

АССОЦИАЦИЯ «МЕЖДУНАРОДНЫЙ КОНГРЕСС КАЧЕСТВА ТЕЛЕКОММУНИКАЦИЙ» ОСОБЕННОСТИ РЕКЛАМНОГО РЫНКА «МАЛОГО» ГОРОДА

ОСОБЕННОСТИ РЕКЛАМНОГО РЫНКА «МАЛОГО» ГОРОДА Контур информационной безопасности предприятия

Контур информационной безопасности предприятия