Содержание

- 2. Основные устройства АЛУ АЛУ – арифметическо-логическое устройство, входит в состав процессора Выполняет арифметические и логические операции

- 3. Триггер Триггер - это устройство последова-тельного типа с двумя устойчивыми состояниями равновесия, предназна-ченное для записи и

- 4. Триггер RS-триггер или SR-триггер — триггер, который сохраня-ет своё предыдущее состоя-ние при нулевых входах, и меняет

- 5. Триггер Один триггер хранит бит информации. Для хранения 1 байта необходимо ? триггеров Динамическая память (оперативная)

- 6. Регистр Несколько триггеров можно объединить в регистр – устройство для хранения чисел с двоичным представлением цифр

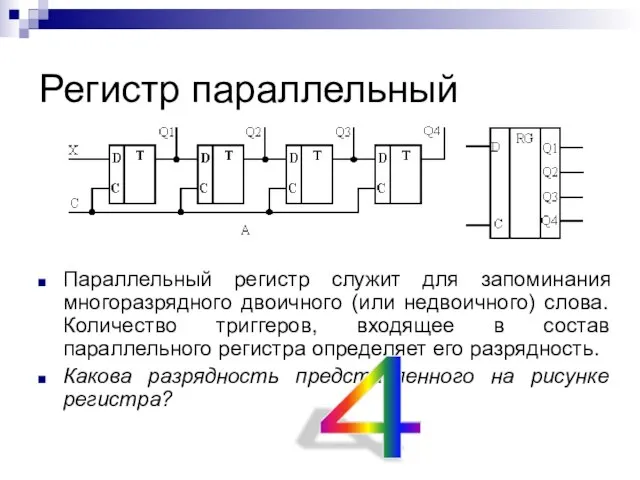

- 7. Регистр параллельный Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. Количество триггеров, входящее в

- 8. Регистр последовательный Здесь выход одного триггера подключен к входу последующего. Основное применение последовательного регистра - преобразование

- 9. Типы регистров Сумматор – регистр АЛУ, способный производить сложение, участвует в выполнении каждой арифметической операции Сдвиговый

- 10. Сумматор Сумматор является центральным узлом арифметическо-логического устройства компьютера Сумматор выполняет сложение много-значных двоичных чисел Он представляет

- 11. Сумматор По числу входов и выходов одноразрядных двоичных сумматоров различают: полусумматоры, характеризующиеся наличием двух входов, на

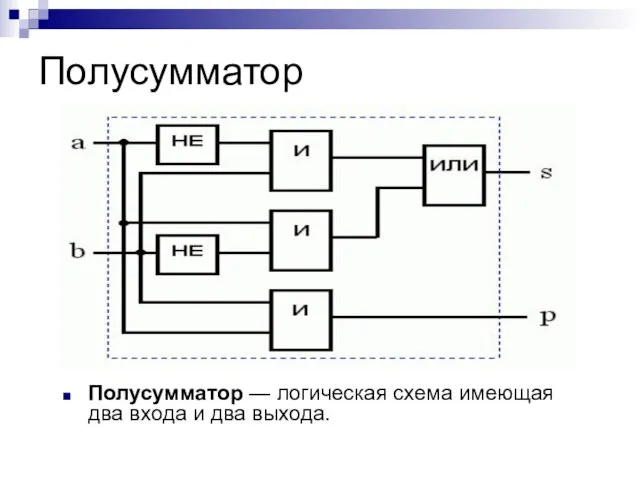

- 12. Полусумматор Полусумматор — логическая схема имеющая два входа и два выхода.

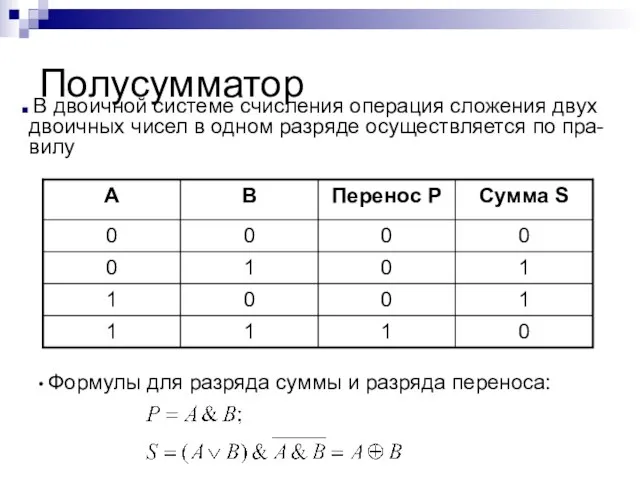

- 13. Полусумматор Формулы для разряда суммы и разряда переноса: В двоичной системе счисления операция сложения двух двоичных

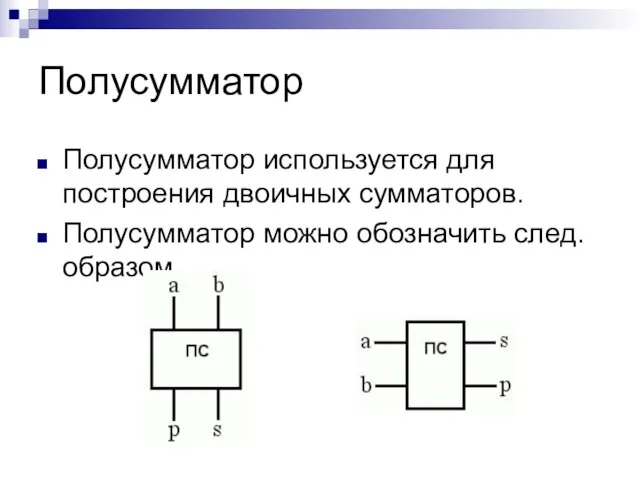

- 14. Полусумматор Полусумматор используется для построения двоичных сумматоров. Полусумматор можно обозначить след. образом

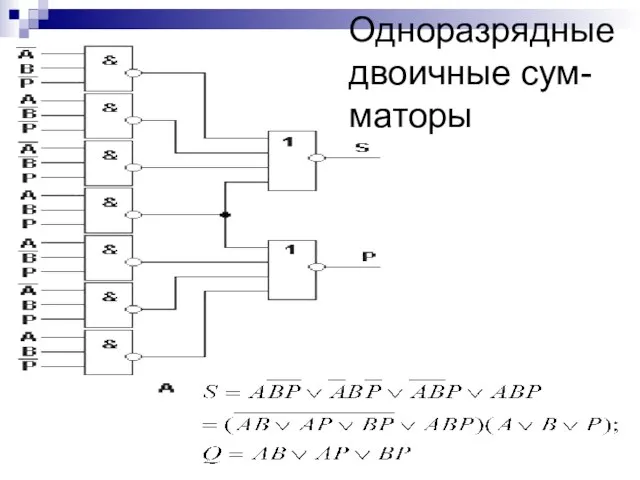

- 15. Одноразрядные двоичные сумматоры характеризующиеся нали-чием трёх входов, на которые подаются одноимённые раз-ряды двух складываемых чисел и

- 16. Одноразрядные двоичные сумматоры

- 17. Одноразрядные двоичные сум-маторы

- 19. Скачать презентацию

Типы астрономических объектов: галактики, звезды, планеты, астероиды, кометы, диффузное вещество

Типы астрономических объектов: галактики, звезды, планеты, астероиды, кометы, диффузное вещество Статистическая теория радиотехнических систем. Случайные процессы и величины. (Лекция 2)

Статистическая теория радиотехнических систем. Случайные процессы и величины. (Лекция 2) Физика в специальности

Физика в специальности Шлифовальные станки

Шлифовальные станки Принцип Гюйгенса-Френеля

Принцип Гюйгенса-Френеля Телескоп-рефрактор

Телескоп-рефрактор Статистическая теория радиотехнических систем. Задача фильтрации. (Лекция 13)

Статистическая теория радиотехнических систем. Задача фильтрации. (Лекция 13) Радиоуглеродный анализ. Естественные науки в помощь гуманитарным

Радиоуглеродный анализ. Естественные науки в помощь гуманитарным Основные положения МКТ

Основные положения МКТ Зубчатые передачи и их изображения на чертежах

Зубчатые передачи и их изображения на чертежах Презентация на тему Диффузия в газах, жидкостях и твердых телах

Презентация на тему Диффузия в газах, жидкостях и твердых телах  Конденсатор

Конденсатор Действие магнитного поля на проводник с током. Закон Ампера

Действие магнитного поля на проводник с током. Закон Ампера Презентация на тему Затухающие колебания

Презентация на тему Затухающие колебания  Проектная работа по физике Электромагнитное излучение и его влияние на здоровье человека

Проектная работа по физике Электромагнитное излучение и его влияние на здоровье человека Преобразование диаграммы условного напряжения - деформация в диаграмму истинного напряжения - деформация в программе Abaqus

Преобразование диаграммы условного напряжения - деформация в диаграмму истинного напряжения - деформация в программе Abaqus Электромагнитные волны. Радиоволны. Спектр электромагнитных волн

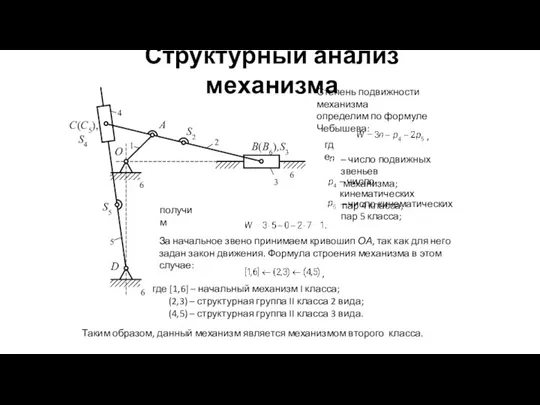

Электромагнитные волны. Радиоволны. Спектр электромагнитных волн Детали машин и основы конструирования. Кинематический расчет привода

Детали машин и основы конструирования. Кинематический расчет привода Кинематический анализ рычажного механизма. План скоростей. Практика №3

Кинематический анализ рычажного механизма. План скоростей. Практика №3 Газовые законы

Газовые законы Презентация на тему Самоиндукция

Презентация на тему Самоиндукция  Решение задач. Подготовка к контрольной работе

Решение задач. Подготовка к контрольной работе Установки и оборудование для аэроакустического эксперимента в ЦАГИ

Установки и оборудование для аэроакустического эксперимента в ЦАГИ Решение задач по теме магнитное поле

Решение задач по теме магнитное поле Ультрофеолетовые волны

Ультрофеолетовые волны Материалы, используемые в конструкциях космических аппаратов

Материалы, используемые в конструкциях космических аппаратов Давление твердых тел. 7 класс

Давление твердых тел. 7 класс физика

физика