Содержание

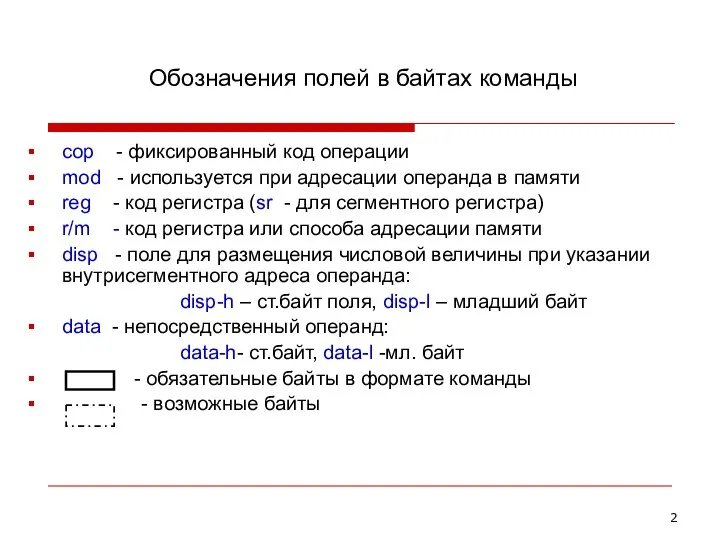

- 2. Обозначения полей в байтах команды cop - фиксированный код операции mod - используется при адресации операнда

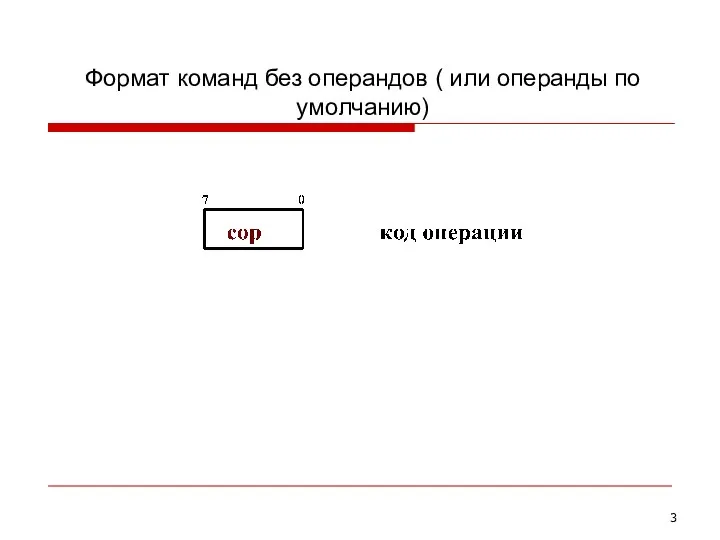

- 3. Формат команд без операндов ( или операнды по умолчанию)

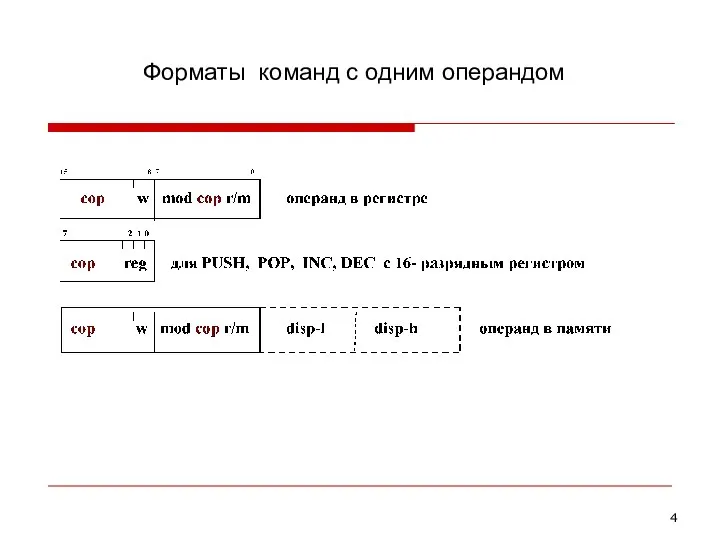

- 4. Форматы команд с одним операндом

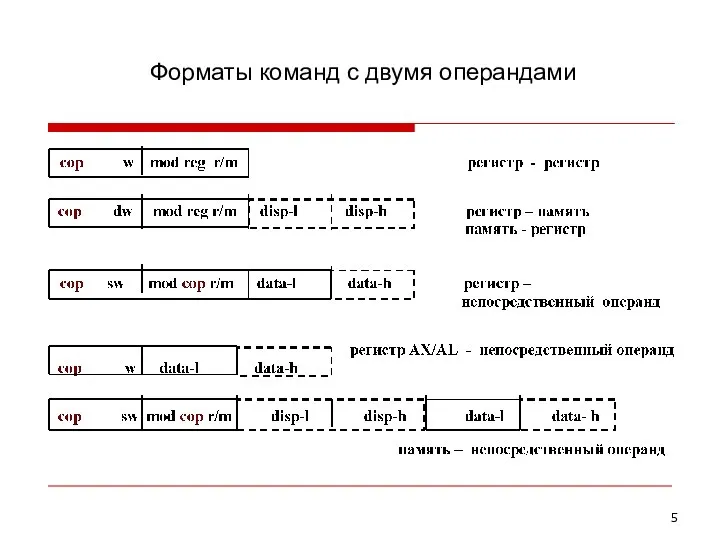

- 5. Форматы команд с двумя операндами

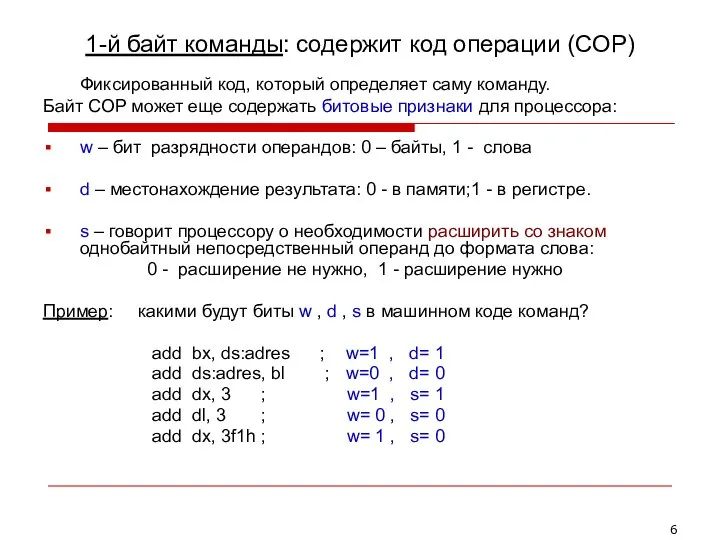

- 6. 1-й байт команды: содержит код операции (COP) Фиксированный код, который определяет саму команду. Байт COP может

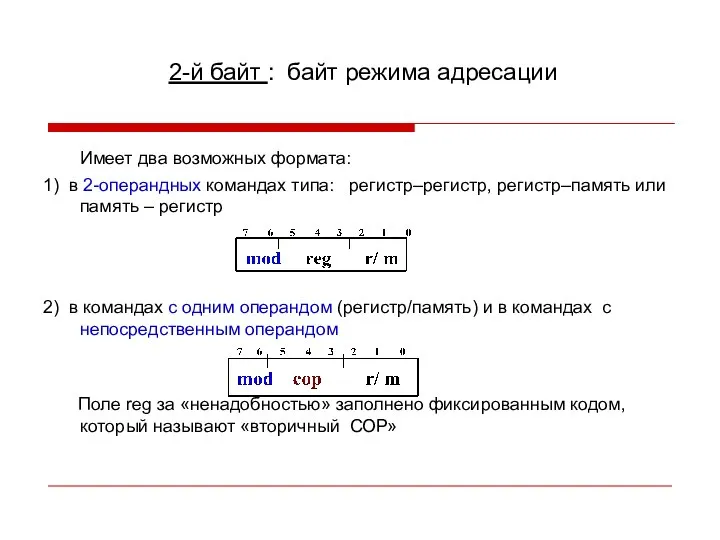

- 7. 2-й байт : байт режима адресации Имеет два возможных формата: 1) в 2-операндных командах типа: регистр–регистр,

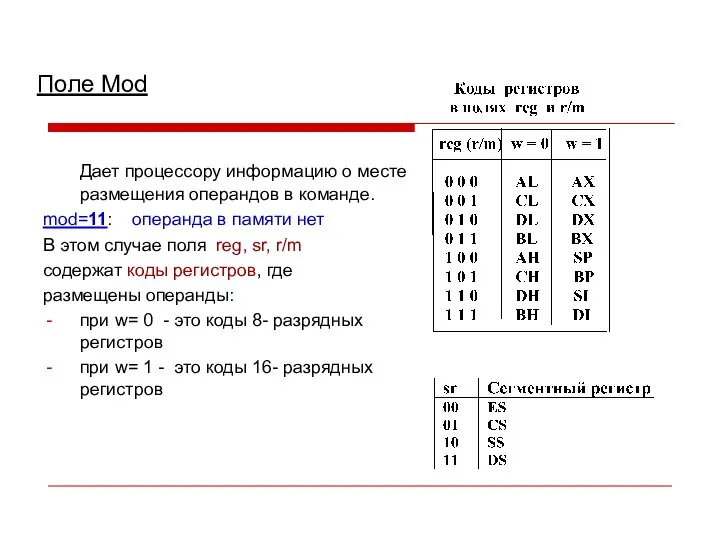

- 8. Поле Mod Дает процессору информацию о месте размещения операндов в команде. mod=11: операнда в памяти нет

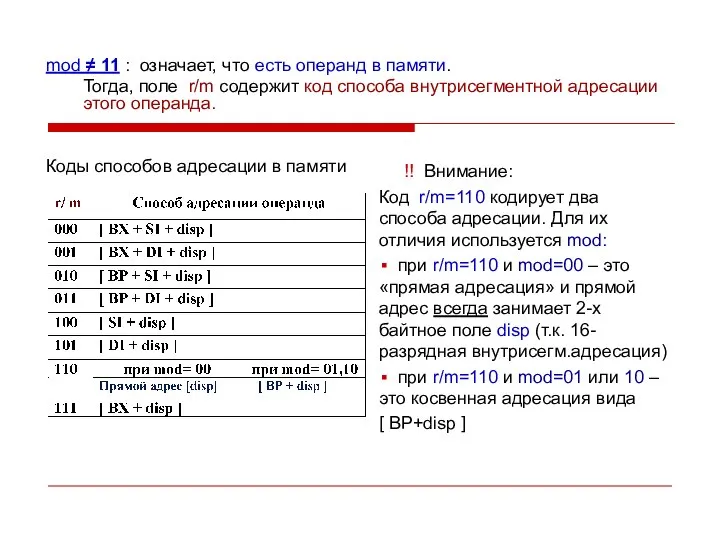

- 9. mod ≠ 11 : означает, что есть операнд в памяти. Тогда, поле r/m содержит код способа

- 10. Поле Disp При прямой адресации: поле disp содержит 16-разрядный прямой внутрисегментный адрес. То есть поле всегда

- 11. Адресация операнда в памяти: «префикс сегмента» Если при задании адреса операнда используется указатель сегмента, отличный от

- 12. Пример. Создать машинный код команды ADD AX, ds:[SI-2]. Дать подробные пояснения 1. Определимся с форматом команды.

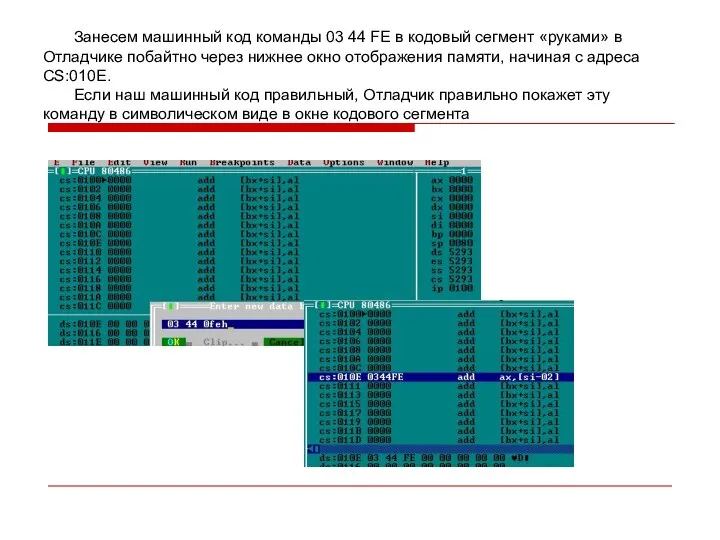

- 13. Занесем машинный код команды 03 44 FE в кодовый сегмент «руками» в Отладчике побайтно через нижнее

- 15. Скачать презентацию

![Пример. Создать машинный код команды ADD AX, ds:[SI-2]. Дать подробные пояснения 1.](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1088896/slide-11.jpg)

Рекомендации_по_созданию_презентации

Рекомендации_по_созданию_презентации Введение в информационную безопасность. Основы защиты информации

Введение в информационную безопасность. Основы защиты информации Роль информационных технологий в сфере дополнительного образования и их воспитательное значение

Роль информационных технологий в сфере дополнительного образования и их воспитательное значение Программа CD Burner XP

Программа CD Burner XP Концепт непрерывного мира в игровой разработке

Концепт непрерывного мира в игровой разработке Microsoft Office. Краткая характеристика изученных программ

Microsoft Office. Краткая характеристика изученных программ Яндекс.Медицина

Яндекс.Медицина Лекция 5

Лекция 5 Безопасность в интернете

Безопасность в интернете Внедрение дополнительного кода в исполняемый файл

Внедрение дополнительного кода в исполняемый файл Решение задачи о ферзях. Проект С++

Решение задачи о ферзях. Проект С++ Программирование в Lazarus. Массивы

Программирование в Lazarus. Массивы Основные методы обеспечения качества функционирования

Основные методы обеспечения качества функционирования Компьютер для чайников

Компьютер для чайников Информационная система по учету и контролю технического состояния производственных объектов

Информационная система по учету и контролю технического состояния производственных объектов Системы счисления. Кодирование информации

Системы счисления. Кодирование информации Сообщение Блюпринтов. Лекция 8

Сообщение Блюпринтов. Лекция 8 Базы данных. Access 2007. Макросы

Базы данных. Access 2007. Макросы Что, где, когда, Игра по информатике

Что, где, когда, Игра по информатике Реляционная модель данных и основы языка SQL. Семинар 1

Реляционная модель данных и основы языка SQL. Семинар 1 10 способов увеличения быстродействия компьютера

10 способов увеличения быстродействия компьютера Обучение по продукту. Онлайн-кассы

Обучение по продукту. Онлайн-кассы Развитие сайта. Представление

Развитие сайта. Представление Интерфейс пользователя e-Навигации в среде смешанной реальности на судне

Интерфейс пользователя e-Навигации в среде смешанной реальности на судне Анализ интернет-сайтов

Анализ интернет-сайтов ФРИИ: cтартап за неделю

ФРИИ: cтартап за неделю Условия if/elif/else

Условия if/elif/else C de Dosya İşlemler

C de Dosya İşlemler