Содержание

- 2. This week… Finish ARM assembly example from last time Walk though of the ARM ISA Software

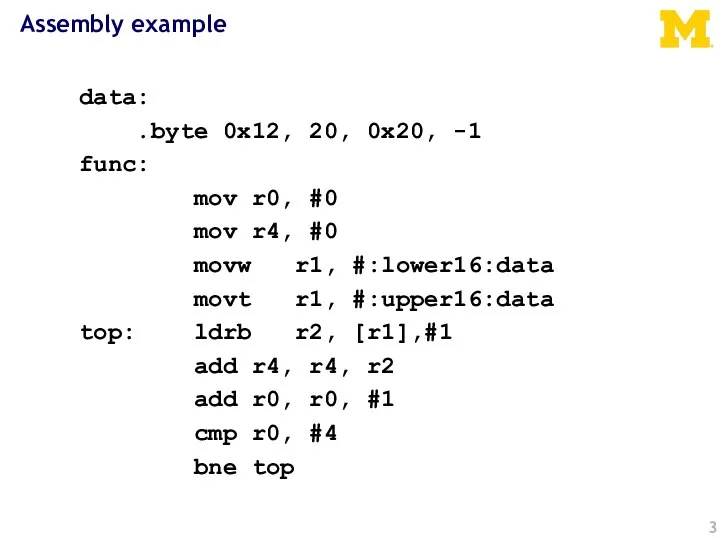

- 3. Assembly example data: .byte 0x12, 20, 0x20, -1 func: mov r0, #0 mov r4, #0 movw

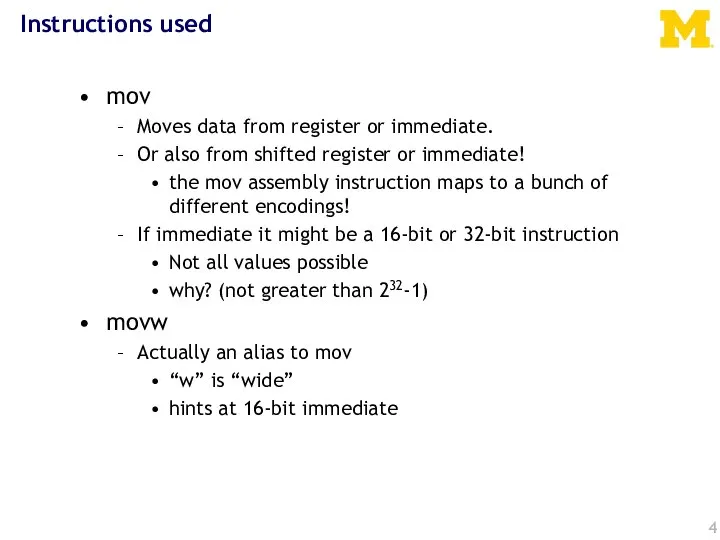

- 4. Instructions used mov Moves data from register or immediate. Or also from shifted register or immediate!

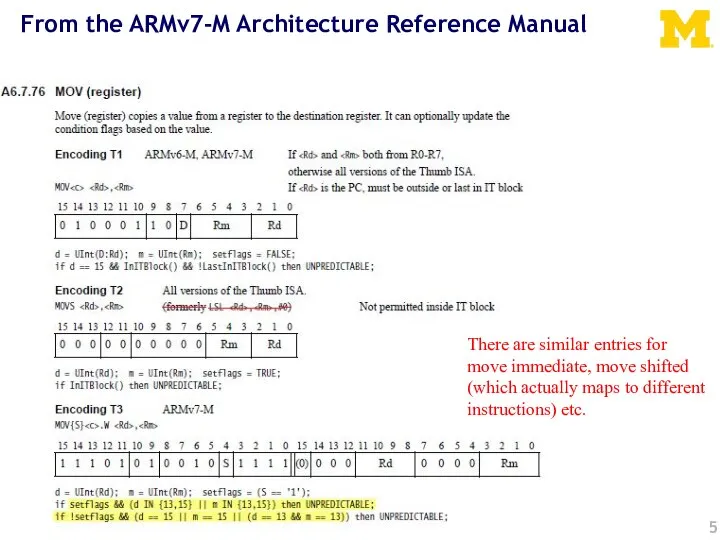

- 5. From the ARMv7-M Architecture Reference Manual There are similar entries for move immediate, move shifted (which

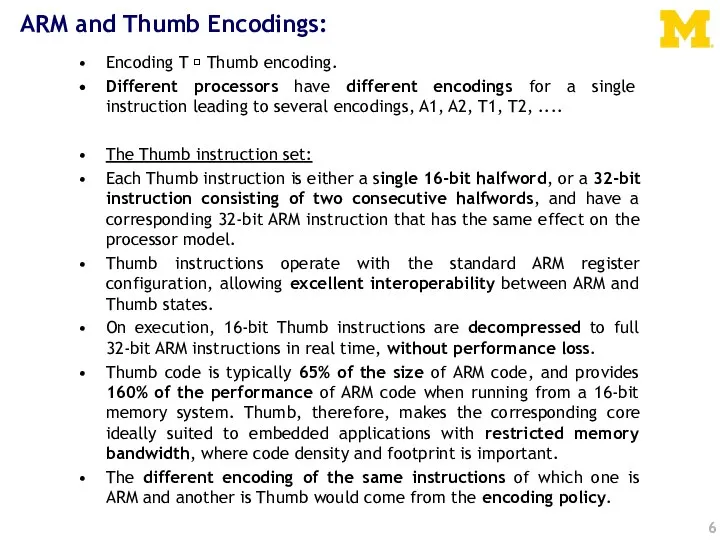

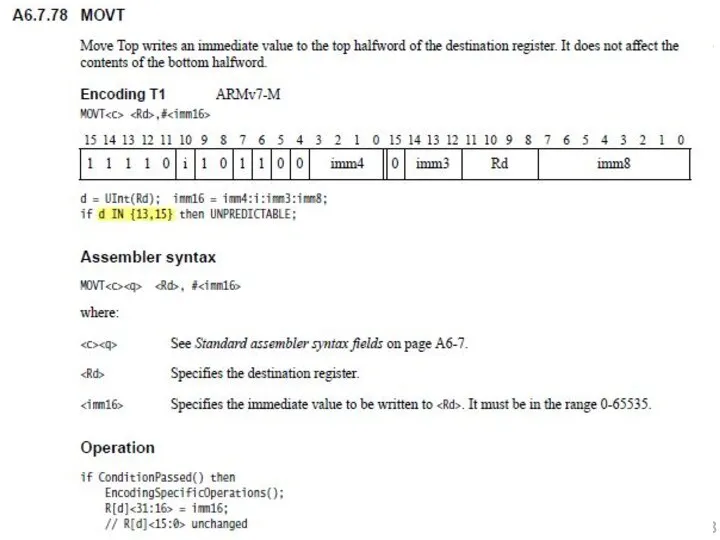

- 6. ARM and Thumb Encodings: Encoding T ? Thumb encoding. Different processors have different encodings for a

- 7. Directives #:lower16:data What does that do? Why? Note: “data” is a label for a memory address!

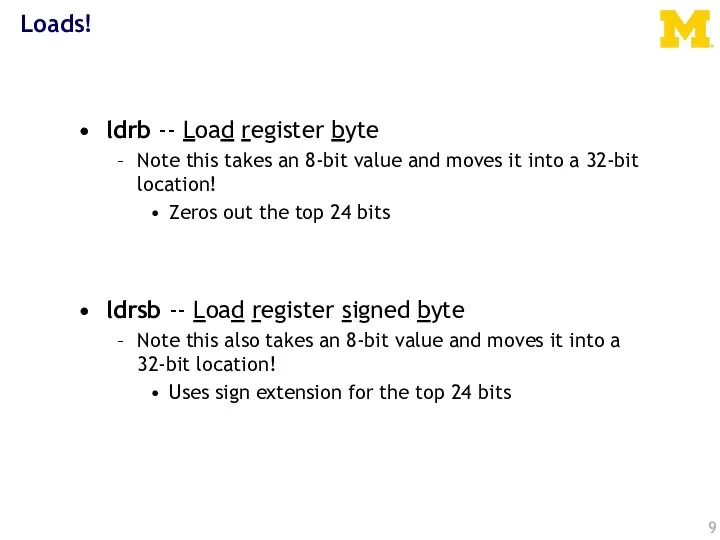

- 9. Loads! ldrb -- Load register byte Note this takes an 8-bit value and moves it into

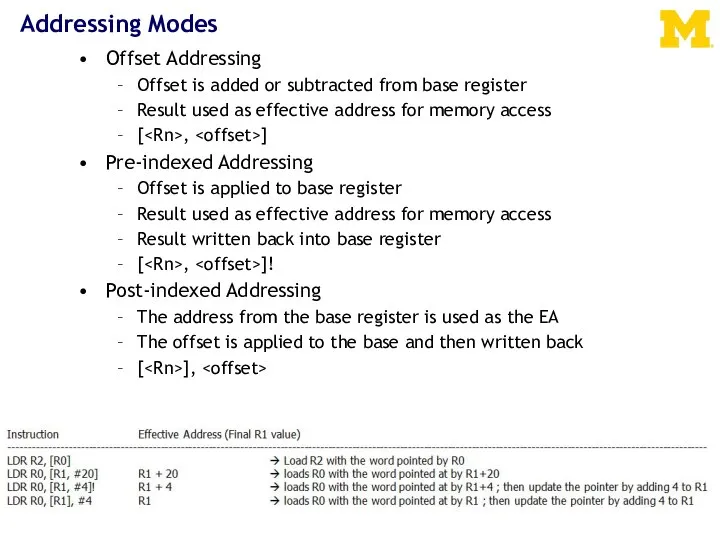

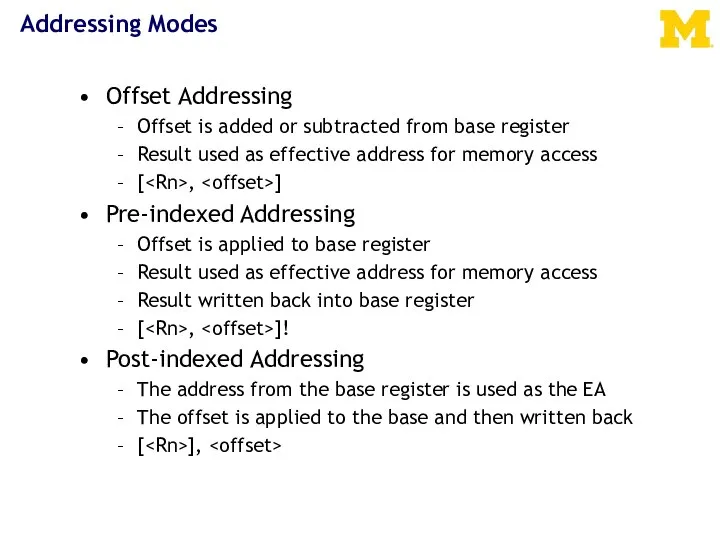

- 10. Addressing Modes Offset Addressing Offset is added or subtracted from base register Result used as effective

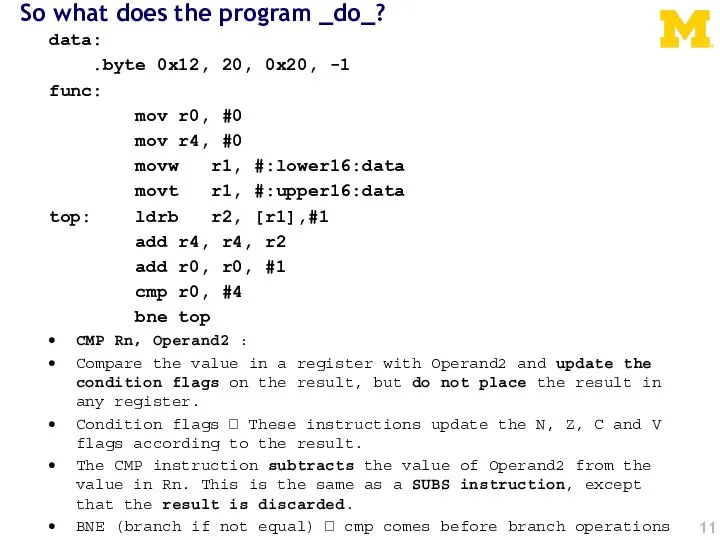

- 11. So what does the program _do_? data: .byte 0x12, 20, 0x20, -1 func: mov r0, #0

- 12. This Week… Finish ARM assembly example from last time Walk though of the ARM ISA Software

- 13. An ISA defines the hardware/software interface A “contract” between architects and programmers Register set Instruction set

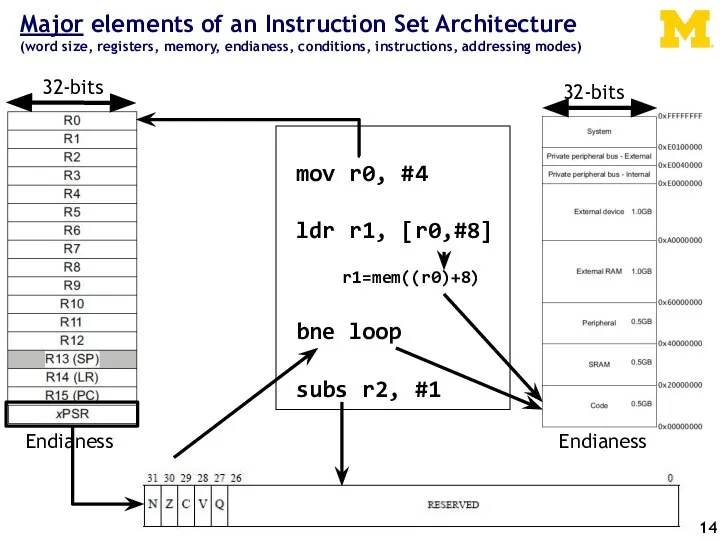

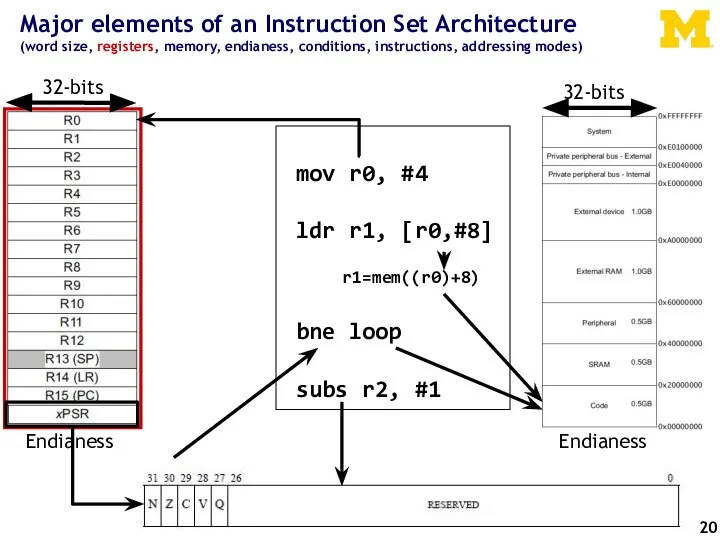

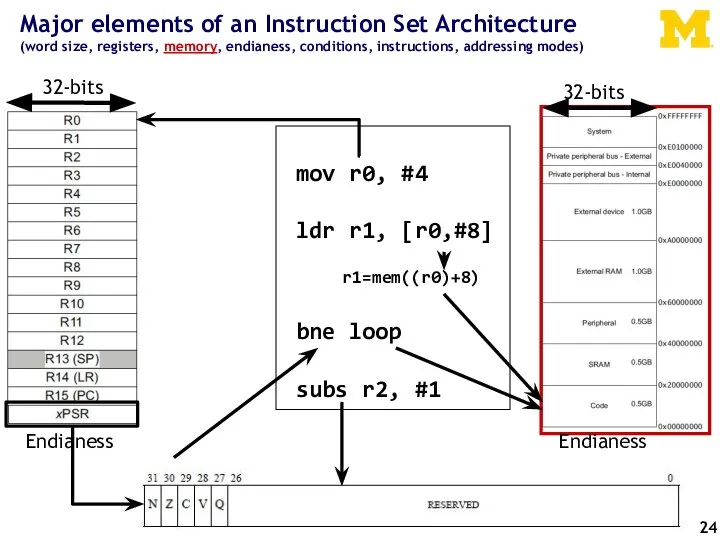

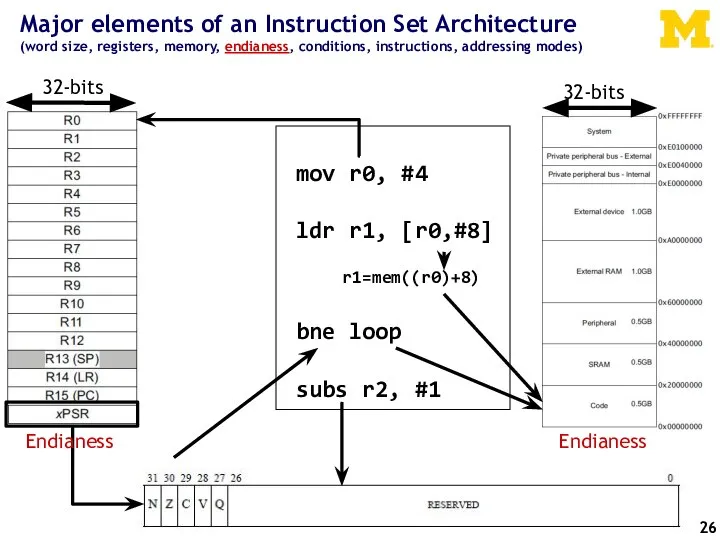

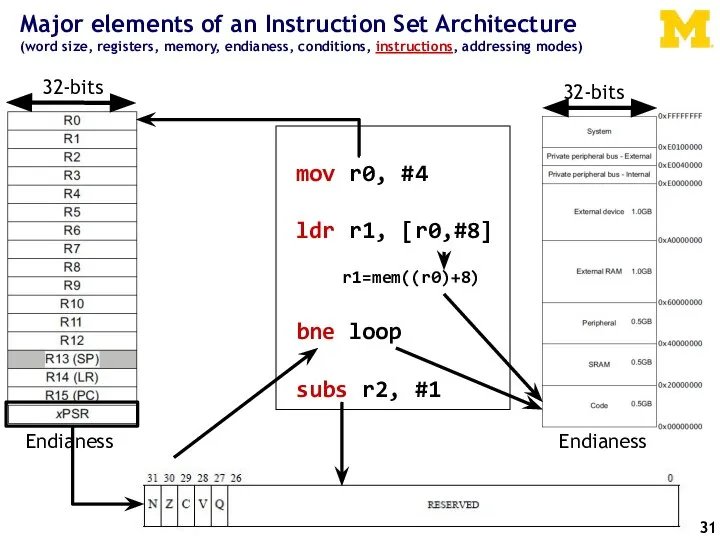

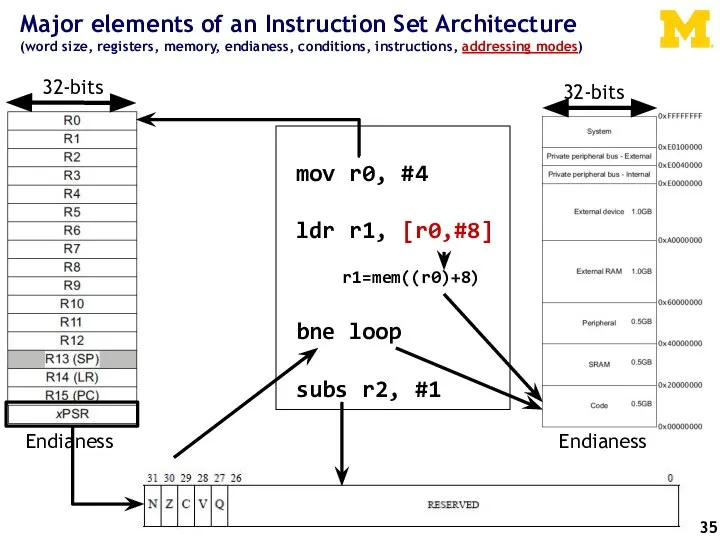

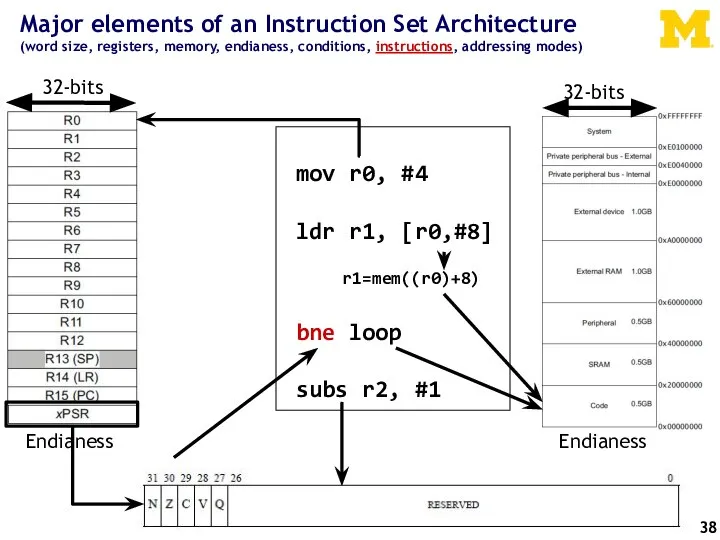

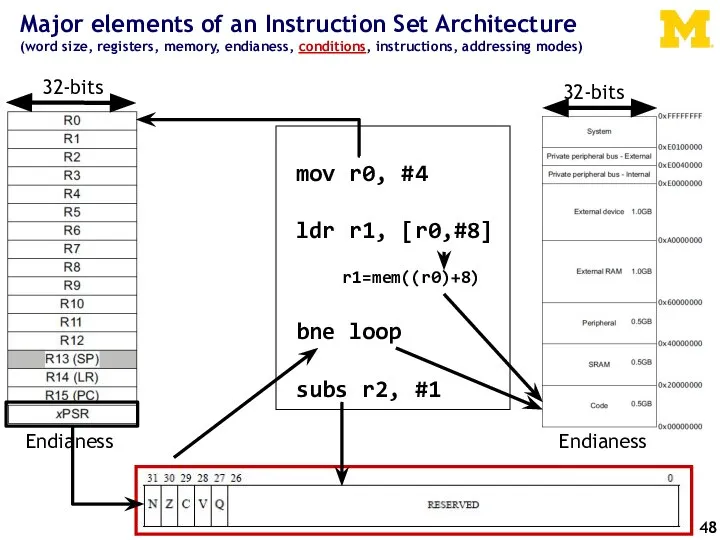

- 14. Major elements of an Instruction Set Architecture (word size, registers, memory, endianess, conditions, instructions, addressing modes)

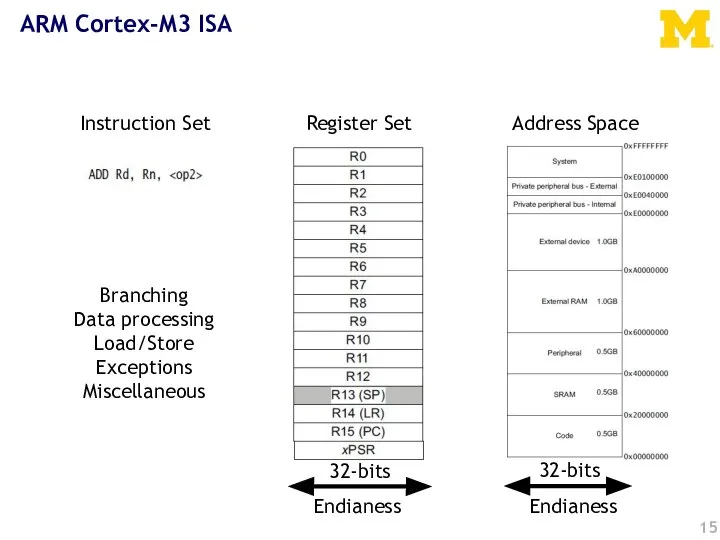

- 15. ARM Cortex-M3 ISA Register Set Address Space Branching Data processing Load/Store Exceptions Miscellaneous Instruction Set 32-bits

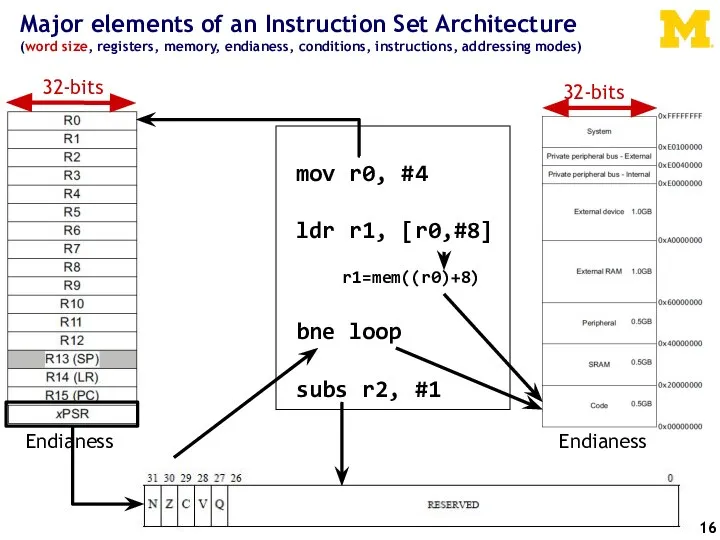

- 16. Major elements of an Instruction Set Architecture (word size, registers, memory, endianess, conditions, instructions, addressing modes)

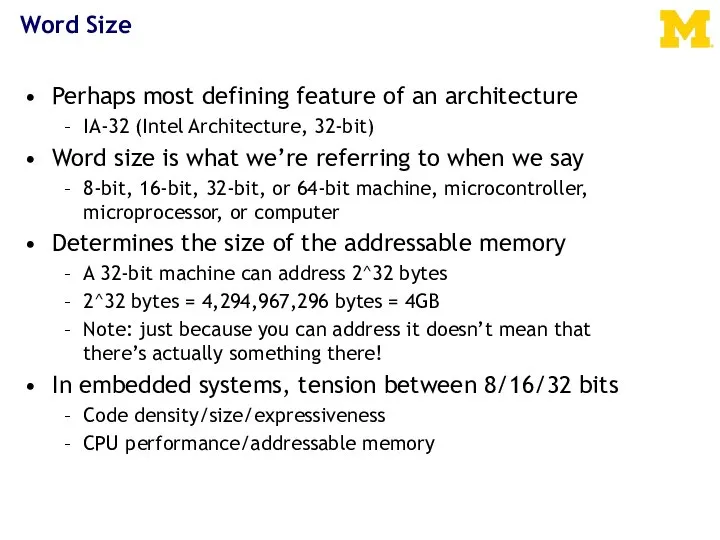

- 17. Word Size Perhaps most defining feature of an architecture IA-32 (Intel Architecture, 32-bit) Word size is

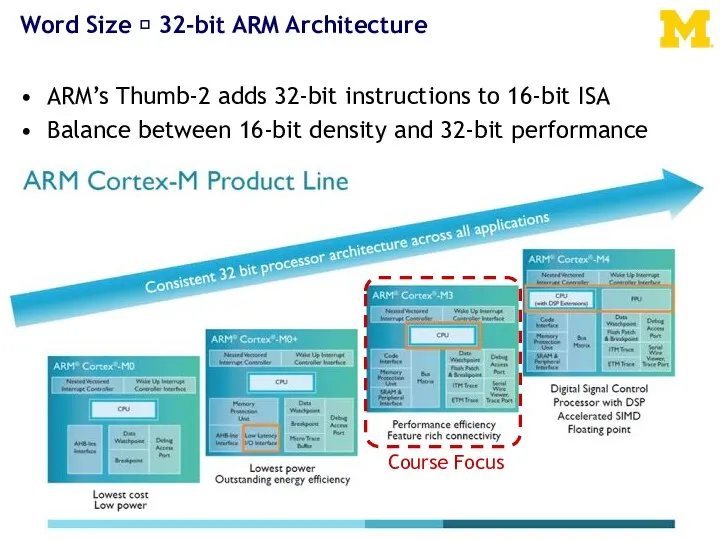

- 18. Word Size ? 32-bit ARM Architecture ARM’s Thumb-2 adds 32-bit instructions to 16-bit ISA Balance between

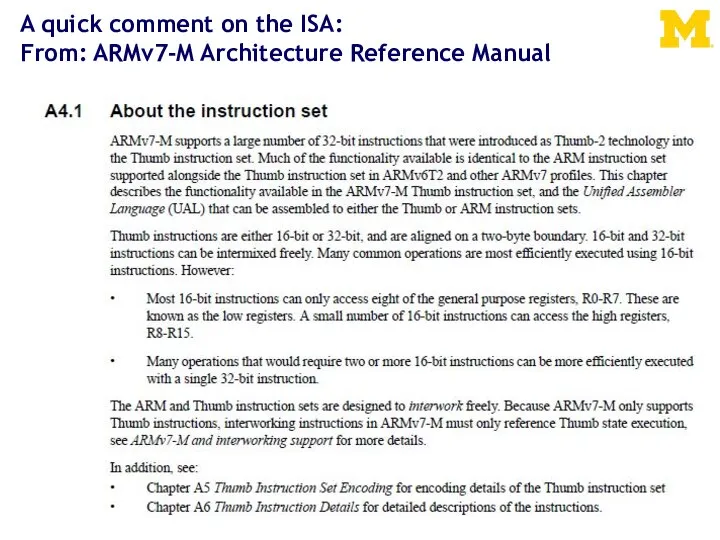

- 19. A quick comment on the ISA: From: ARMv7-M Architecture Reference Manual

- 20. Major elements of an Instruction Set Architecture (word size, registers, memory, endianess, conditions, instructions, addressing modes)

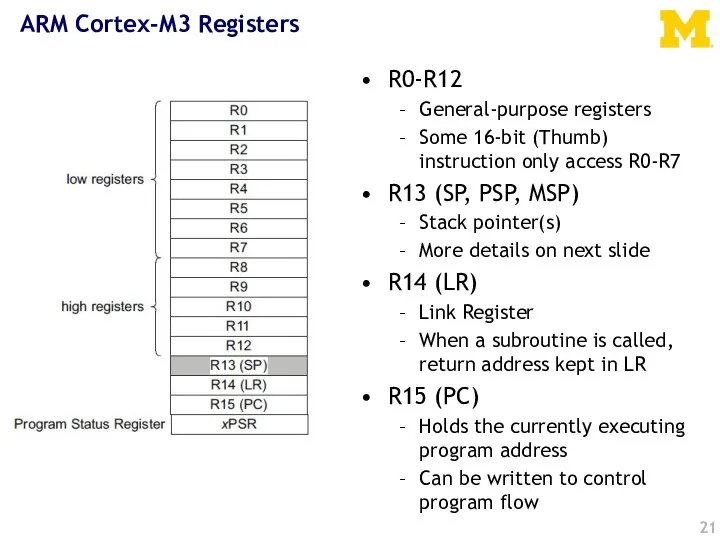

- 21. ARM Cortex-M3 Registers R0-R12 General-purpose registers Some 16-bit (Thumb) instruction only access R0-R7 R13 (SP, PSP,

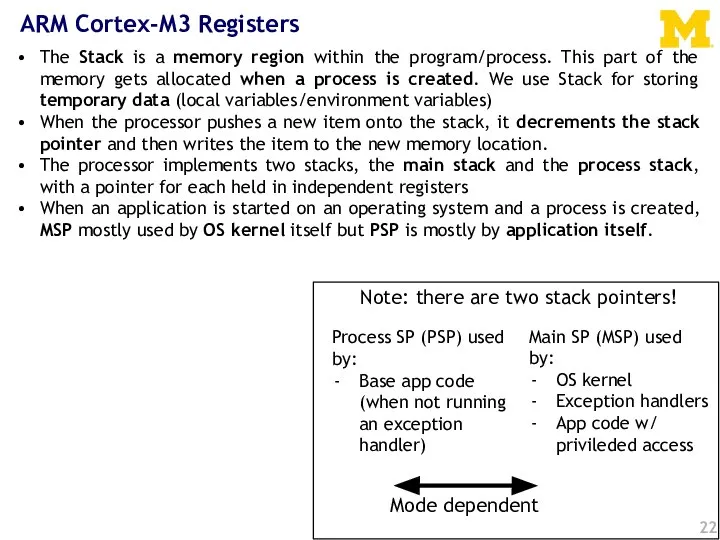

- 22. Mode dependent ARM Cortex-M3 Registers Main SP (MSP) used by: OS kernel Exception handlers App code

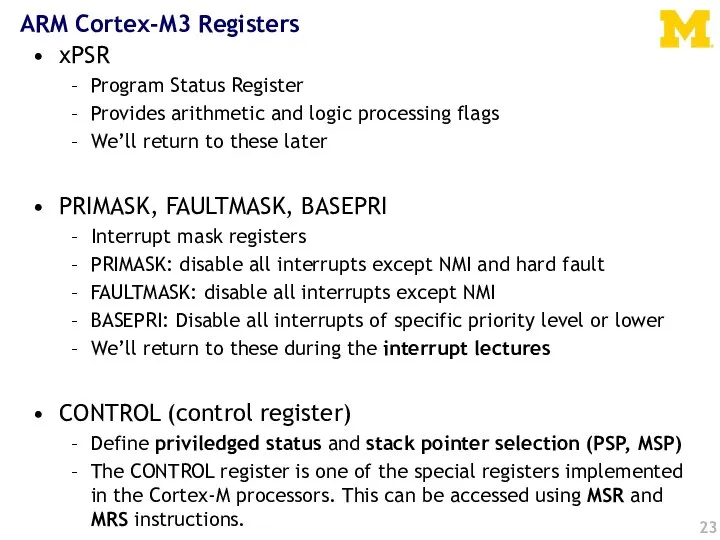

- 23. ARM Cortex-M3 Registers xPSR Program Status Register Provides arithmetic and logic processing flags We’ll return to

- 24. Major elements of an Instruction Set Architecture (word size, registers, memory, endianess, conditions, instructions, addressing modes)

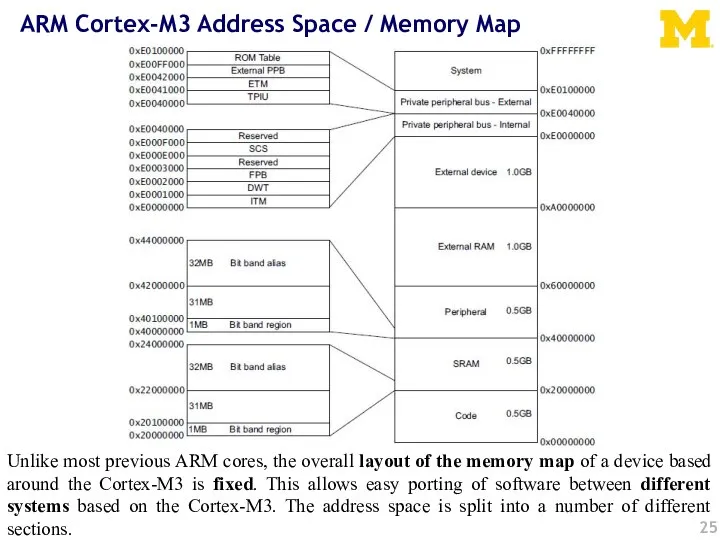

- 25. ARM Cortex-M3 Address Space / Memory Map Unlike most previous ARM cores, the overall layout of

- 26. Major elements of an Instruction Set Architecture (word size, registers, memory, endianess, conditions, instructions, addressing modes)

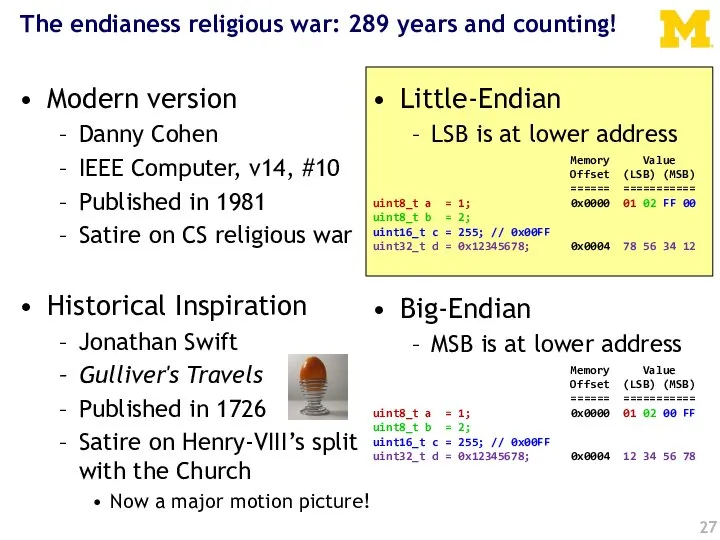

- 27. The endianess religious war: 289 years and counting! Modern version Danny Cohen IEEE Computer, v14, #10

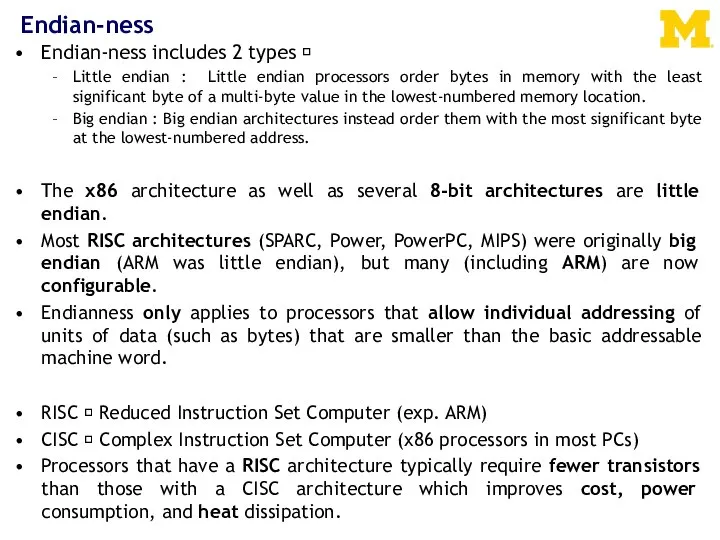

- 28. Endian-ness Endian-ness includes 2 types ? Little endian : Little endian processors order bytes in memory

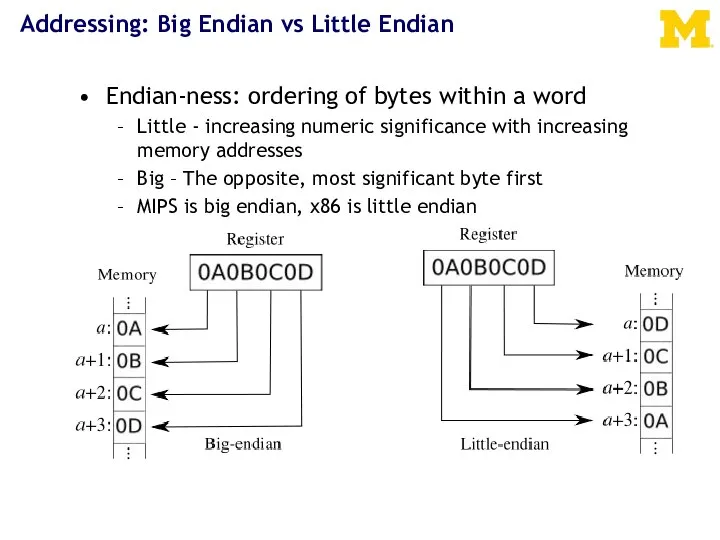

- 29. Addressing: Big Endian vs Little Endian Endian-ness: ordering of bytes within a word Little - increasing

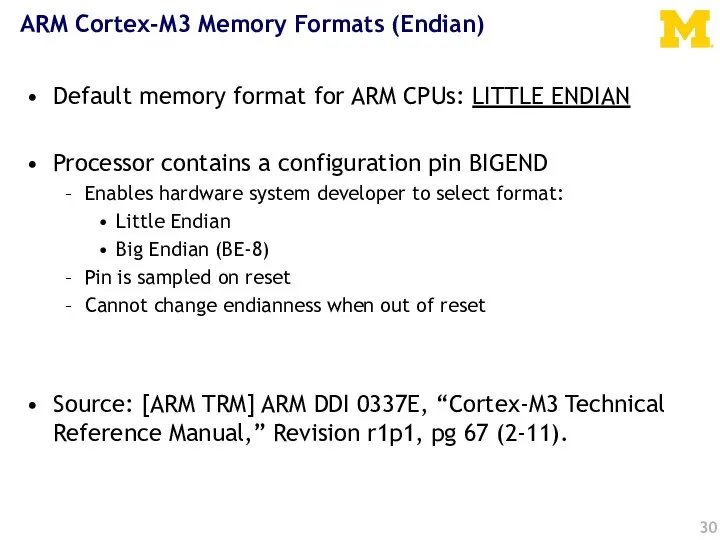

- 30. ARM Cortex-M3 Memory Formats (Endian) Default memory format for ARM CPUs: LITTLE ENDIAN Processor contains a

- 31. Major elements of an Instruction Set Architecture (word size, registers, memory, endianess, conditions, instructions, addressing modes)

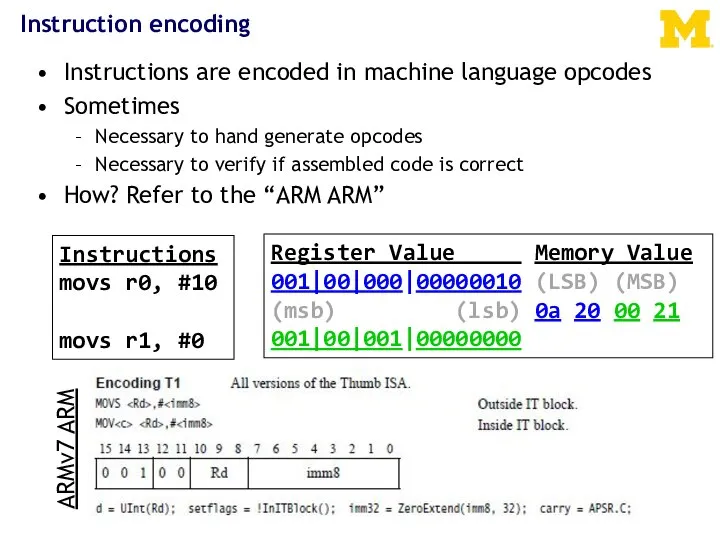

- 32. Instruction encoding Instructions are encoded in machine language opcodes Sometimes Necessary to hand generate opcodes Necessary

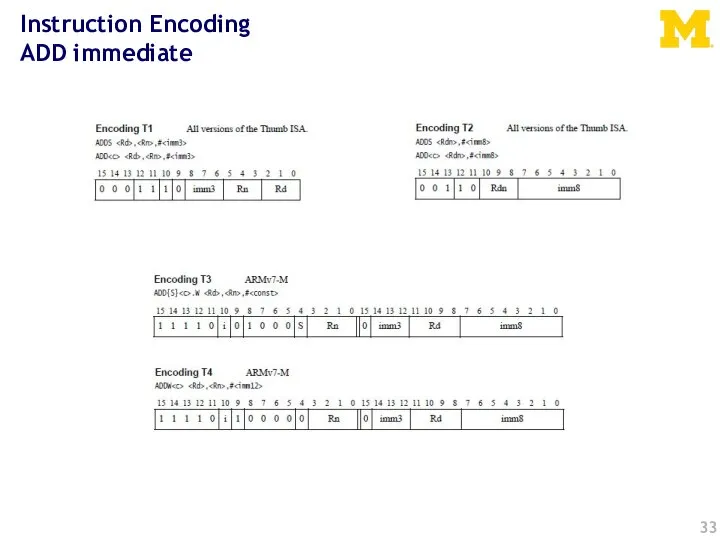

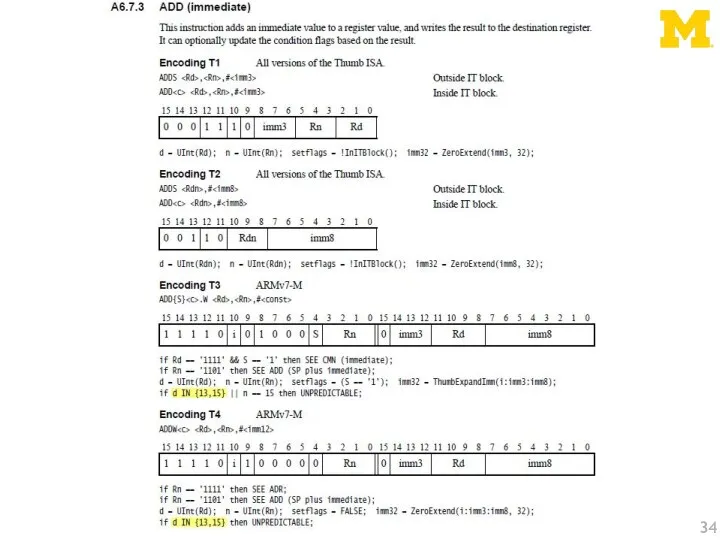

- 33. Instruction Encoding ADD immediate

- 35. Major elements of an Instruction Set Architecture (word size, registers, memory, endianess, conditions, instructions, addressing modes)

- 36. Addressing Modes Offset Addressing Offset is added or subtracted from base register Result used as effective

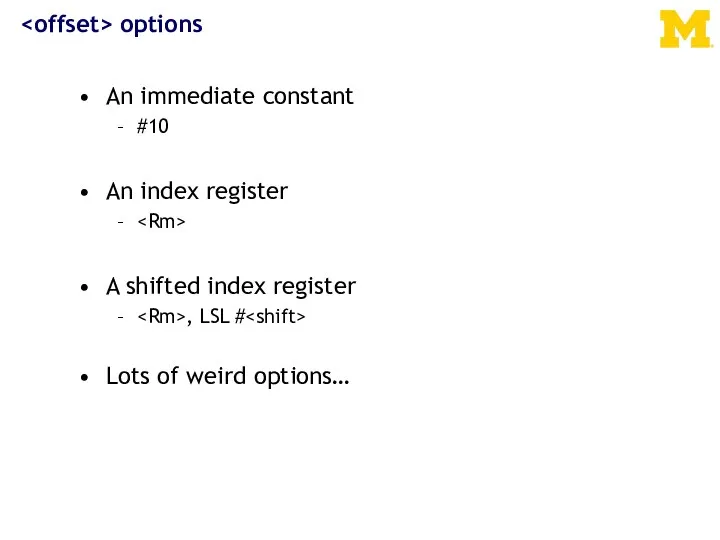

- 37. options An immediate constant #10 An index register A shifted index register , LSL # Lots

- 38. Major elements of an Instruction Set Architecture (word size, registers, memory, endianess, conditions, instructions, addressing modes)

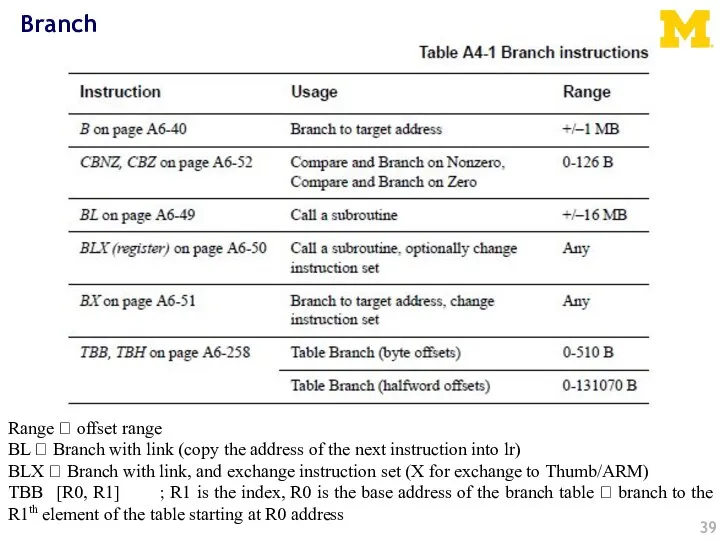

- 39. Branch Range ? offset range BL ? Branch with link (copy the address of the next

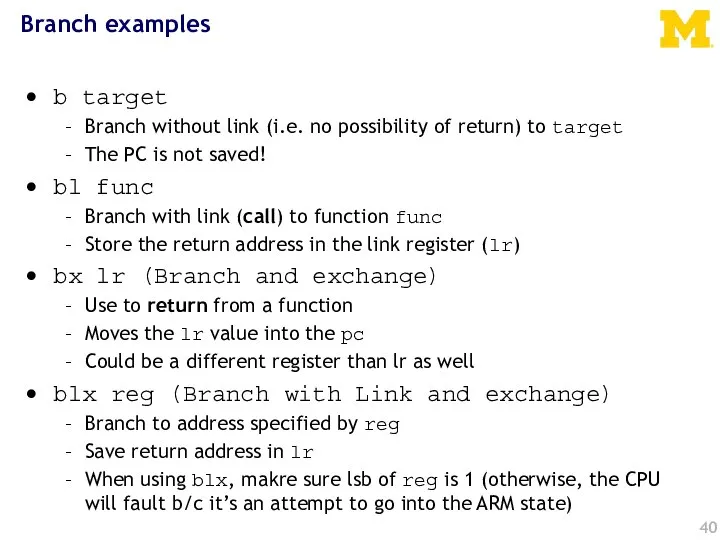

- 40. Branch examples b target Branch without link (i.e. no possibility of return) to target The PC

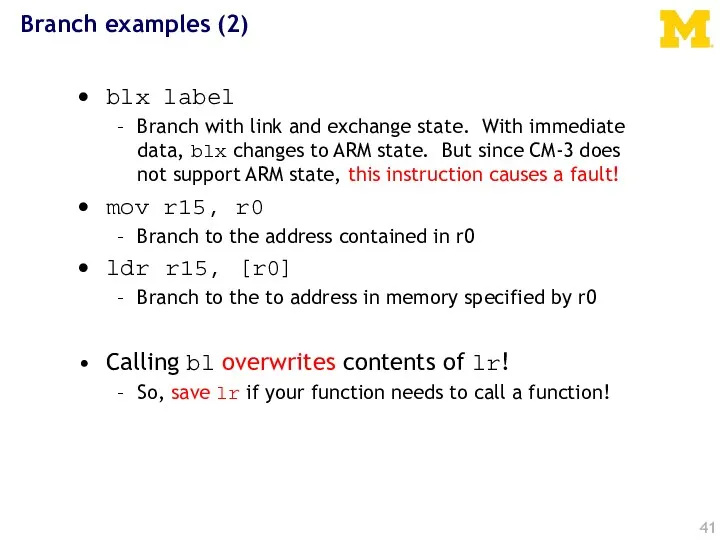

- 41. Branch examples (2) blx label Branch with link and exchange state. With immediate data, blx changes

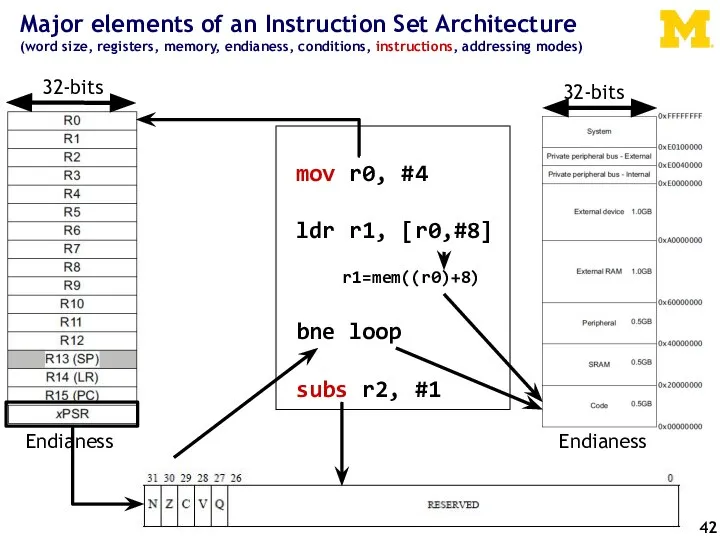

- 42. Major elements of an Instruction Set Architecture (word size, registers, memory, endianess, conditions, instructions, addressing modes)

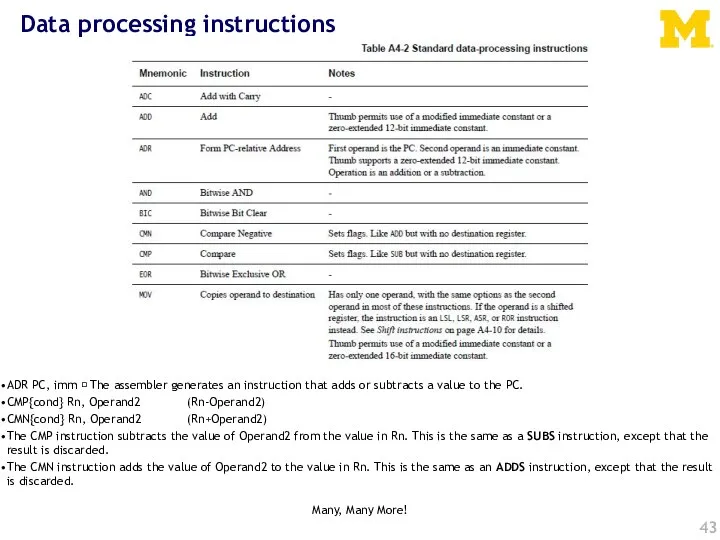

- 43. Data processing instructions ADR PC, imm ? The assembler generates an instruction that adds or subtracts

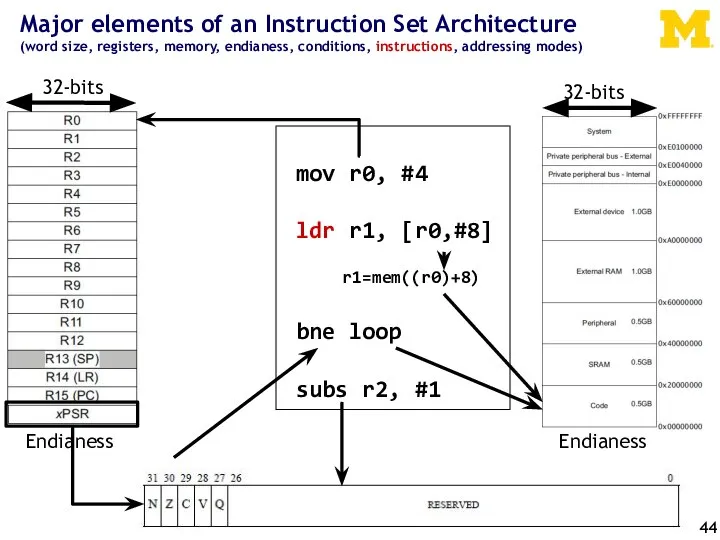

- 44. Major elements of an Instruction Set Architecture (word size, registers, memory, endianess, conditions, instructions, addressing modes)

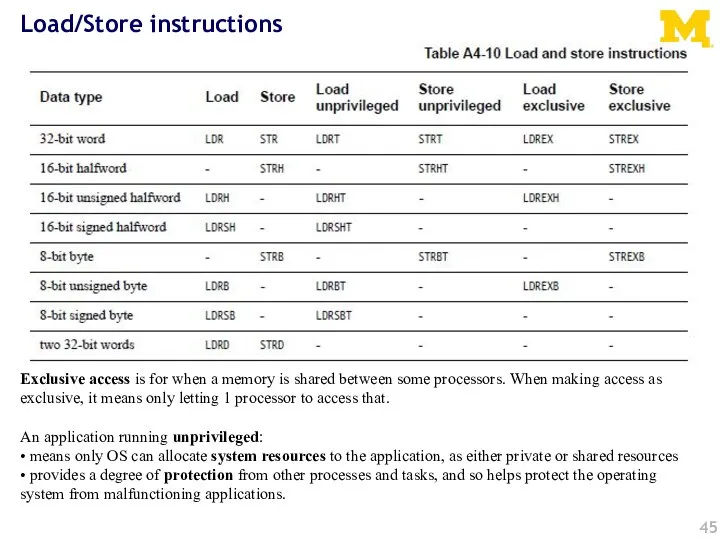

- 45. Load/Store instructions Exclusive access is for when a memory is shared between some processors. When making

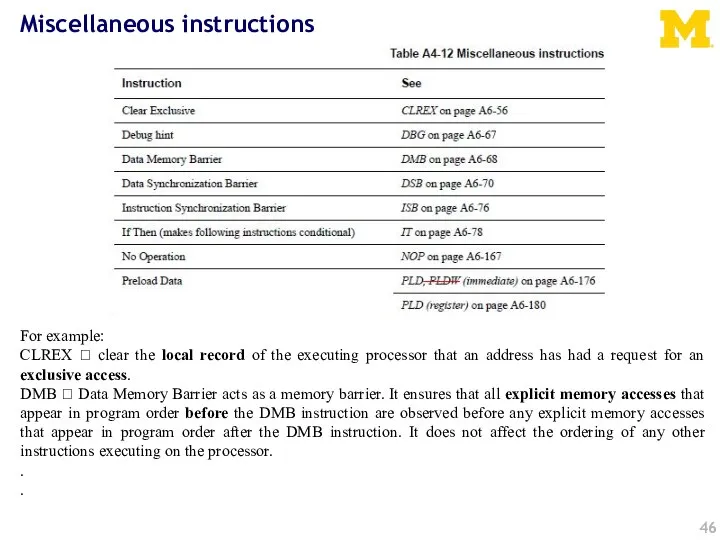

- 46. Miscellaneous instructions For example: CLREX ? clear the local record of the executing processor that an

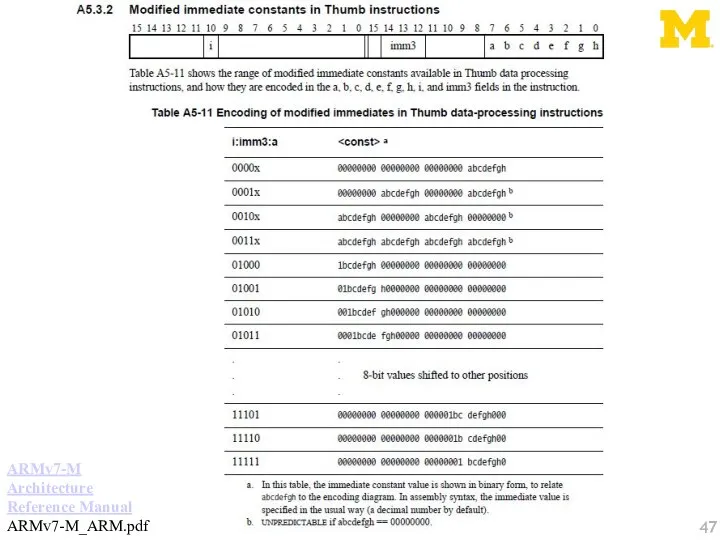

- 47. ARMv7-M Architecture Reference Manual ARMv7-M_ARM.pdf

- 48. Major elements of an Instruction Set Architecture (word size, registers, memory, endianess, conditions, instructions, addressing modes)

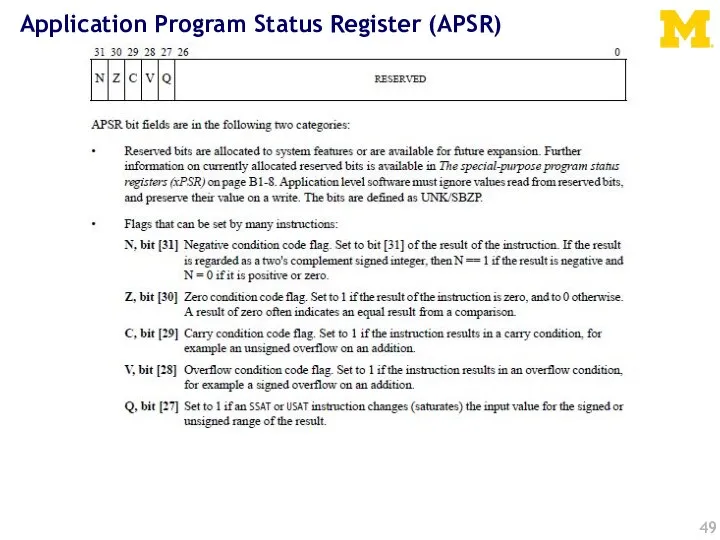

- 49. Application Program Status Register (APSR)

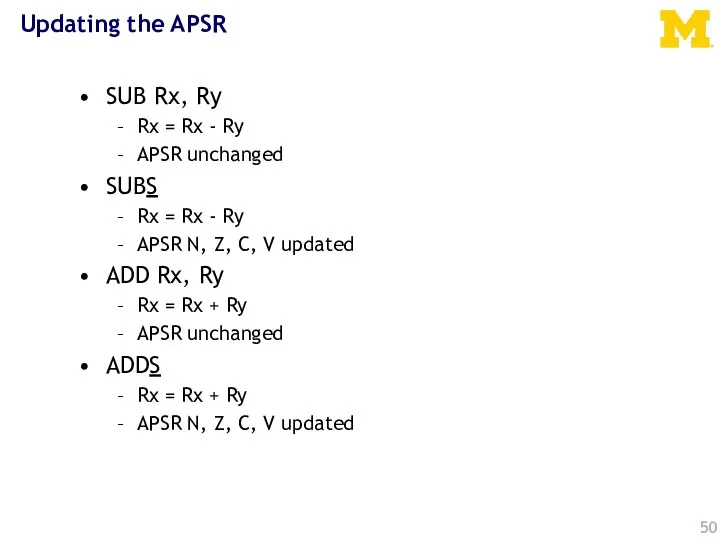

- 50. Updating the APSR SUB Rx, Ry Rx = Rx - Ry APSR unchanged SUBS Rx =

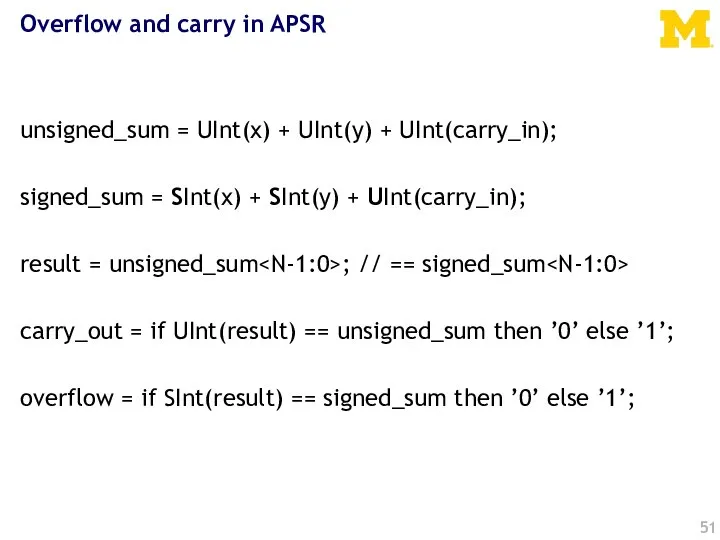

- 51. Overflow and carry in APSR unsigned_sum = UInt(x) + UInt(y) + UInt(carry_in); signed_sum = SInt(x) +

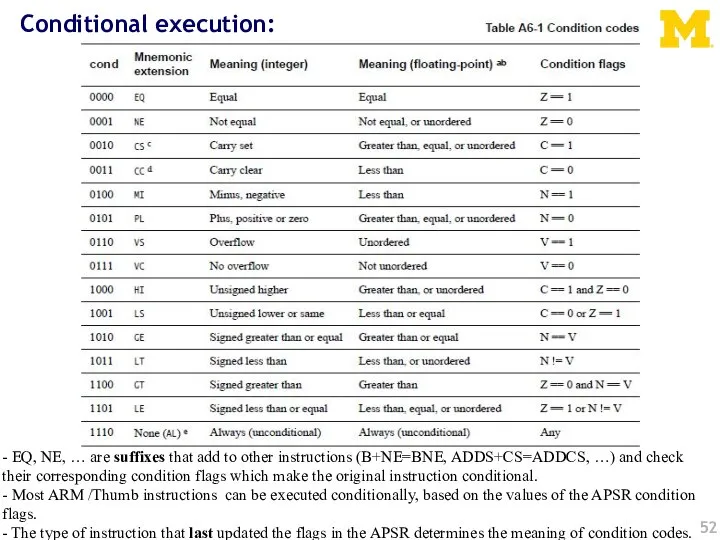

- 52. Conditional execution: - EQ, NE, … are suffixes that add to other instructions (B+NE=BNE, ADDS+CS=ADDCS, …)

- 53. IT blocks Conditional execution in C-M3 done in “IT” block IT [T|E]*3 More on this later…

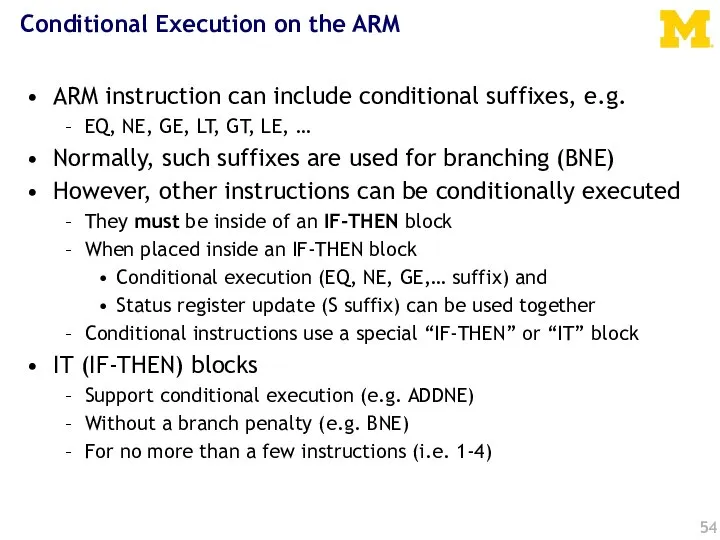

- 54. Conditional Execution on the ARM ARM instruction can include conditional suffixes, e.g. EQ, NE, GE, LT,

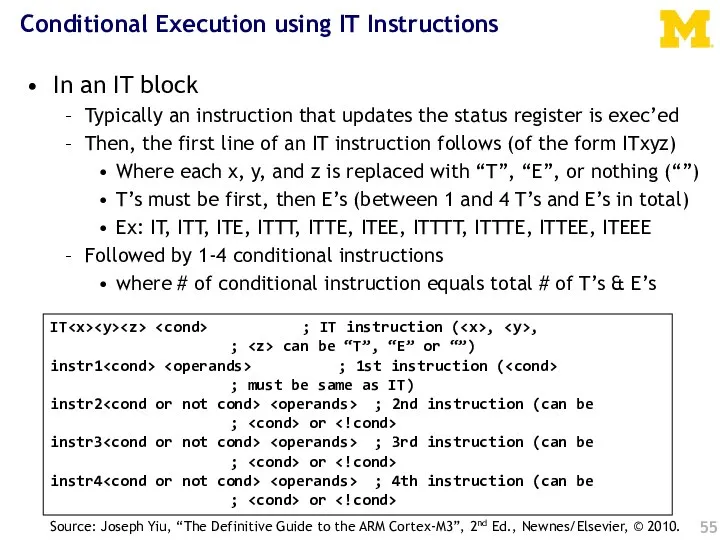

- 55. Conditional Execution using IT Instructions In an IT block Typically an instruction that updates the status

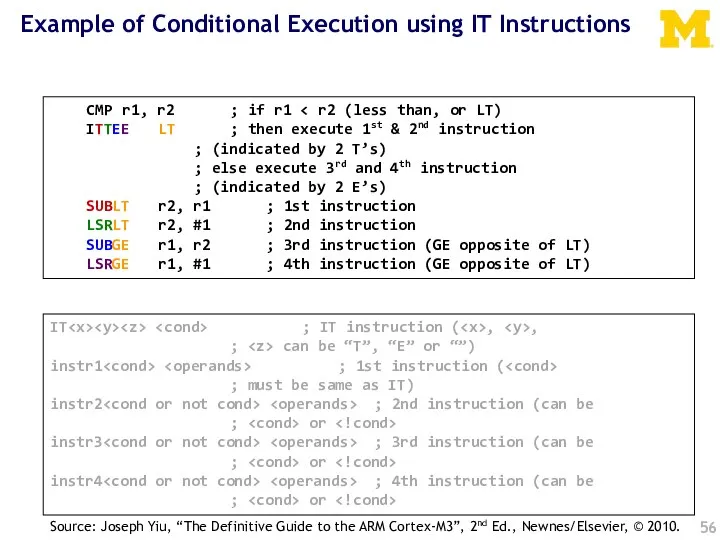

- 56. Example of Conditional Execution using IT Instructions IT ; IT instruction ( , , ; can

- 57. The ARM architecture “books” for this class

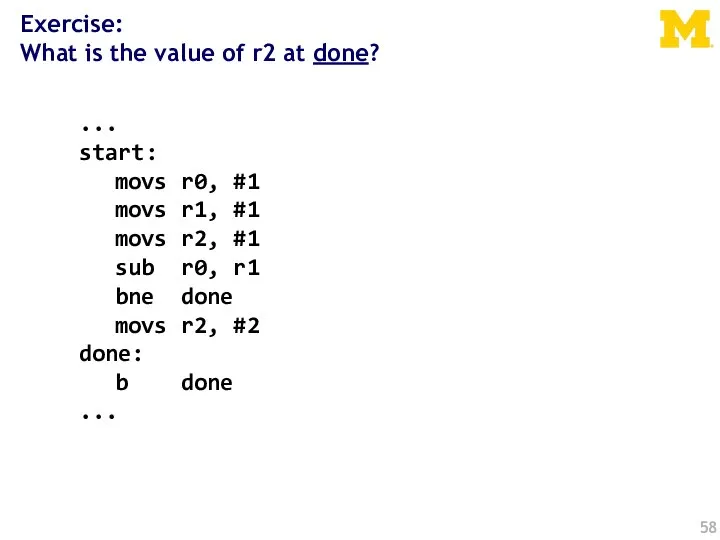

- 58. ... start: movs r0, #1 movs r1, #1 movs r2, #1 sub r0, r1 bne done

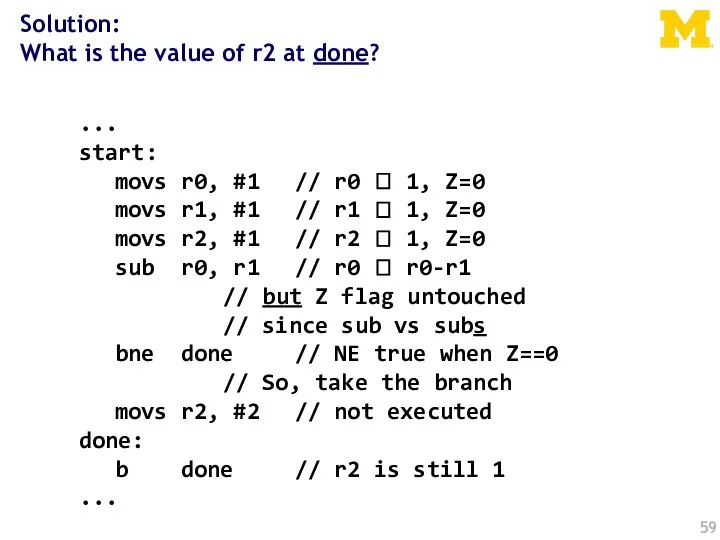

- 59. ... start: movs r0, #1 // r0 ? 1, Z=0 movs r1, #1 // r1 ?

- 60. Today… Finish ARM assembly example from last time Walk though of the ARM ISA Software Development

- 61. The ARM software tools “books” for this class

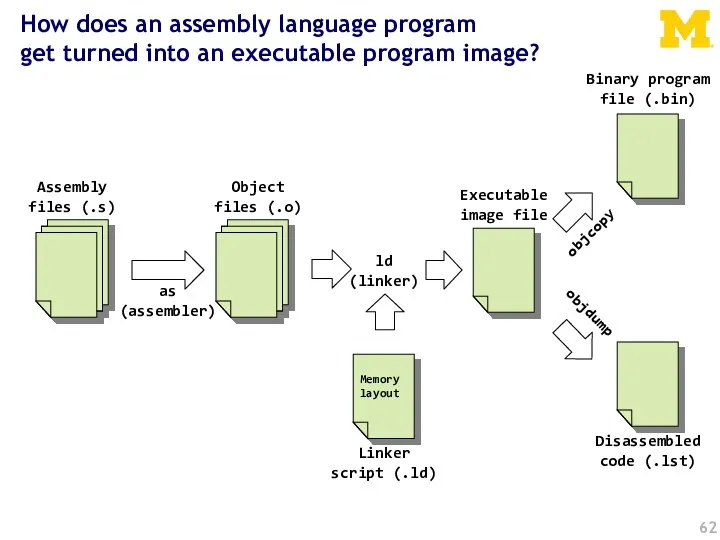

- 62. How does an assembly language program get turned into an executable program image? Assembly files (.s)

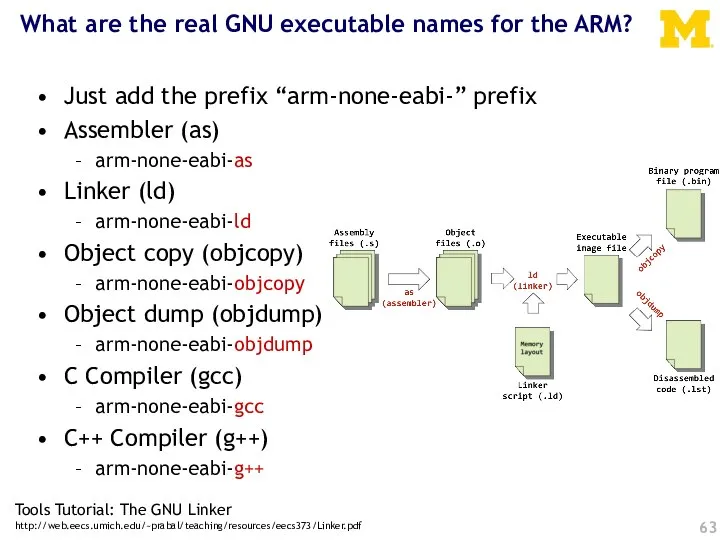

- 63. What are the real GNU executable names for the ARM? Just add the prefix “arm-none-eabi-” prefix

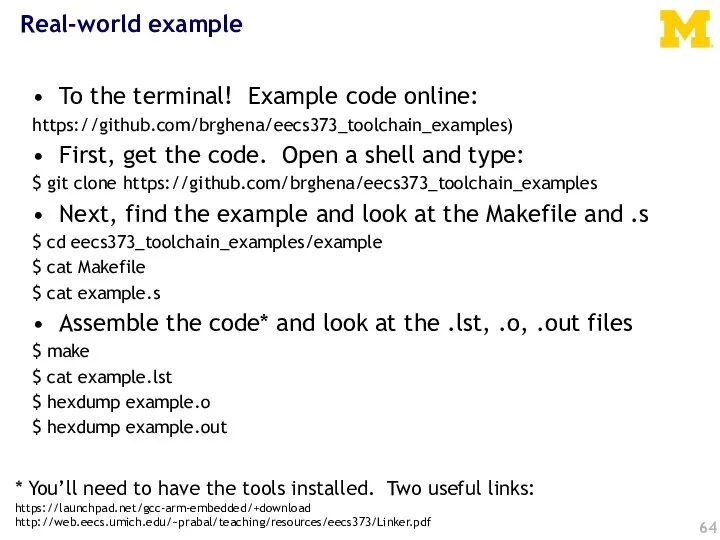

- 64. Real-world example To the terminal! Example code online: https://github.com/brghena/eecs373_toolchain_examples) First, get the code. Open a shell

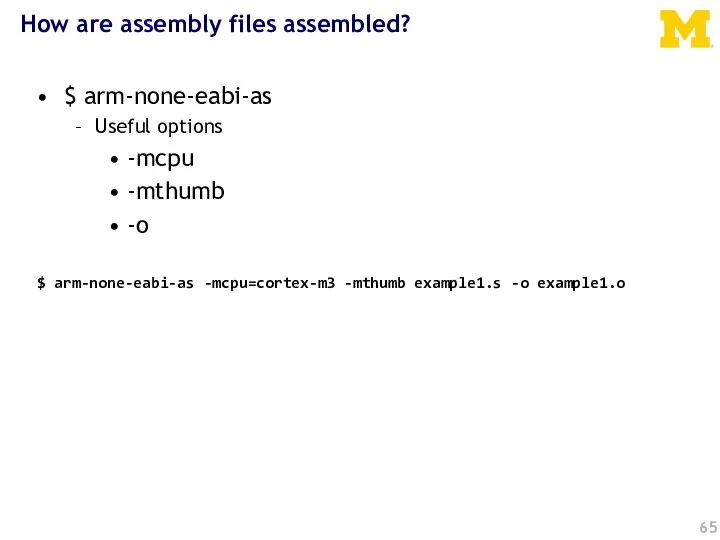

- 65. $ arm-none-eabi-as -mcpu=cortex-m3 -mthumb example1.s -o example1.o How are assembly files assembled? $ arm-none-eabi-as Useful options

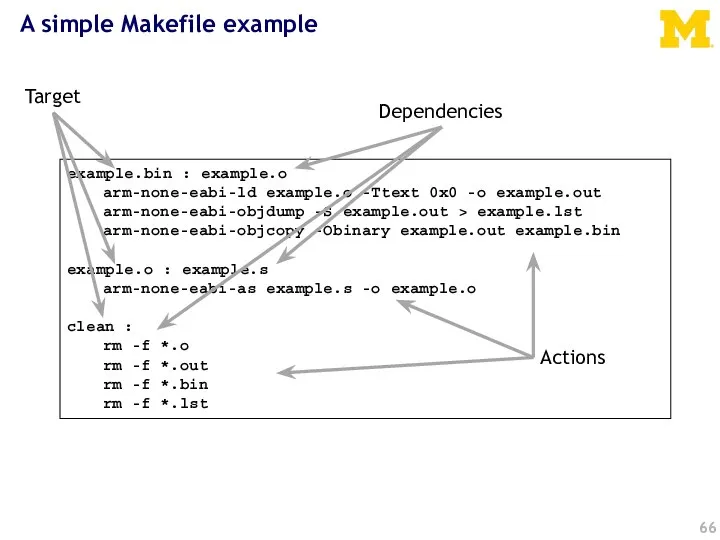

- 66. example.bin : example.o arm-none-eabi-ld example.o -Ttext 0x0 -o example.out arm-none-eabi-objdump -S example.out > example.lst arm-none-eabi-objcopy -Obinary

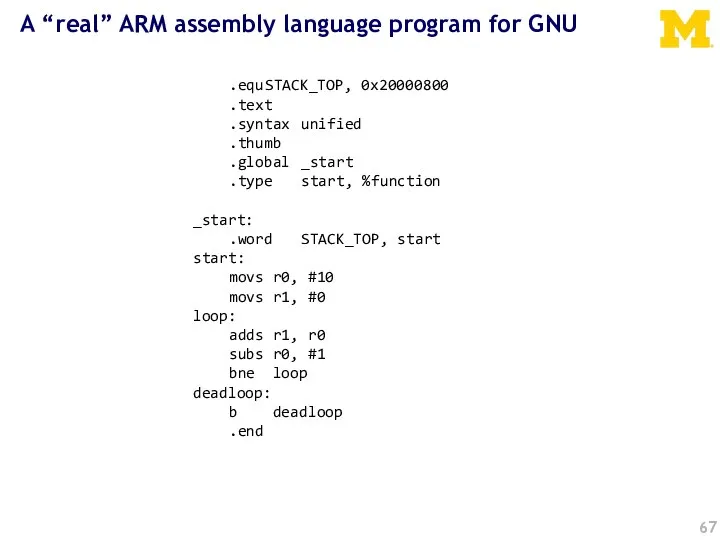

- 67. .equ STACK_TOP, 0x20000800 .text .syntax unified .thumb .global _start .type start, %function _start: .word STACK_TOP, start

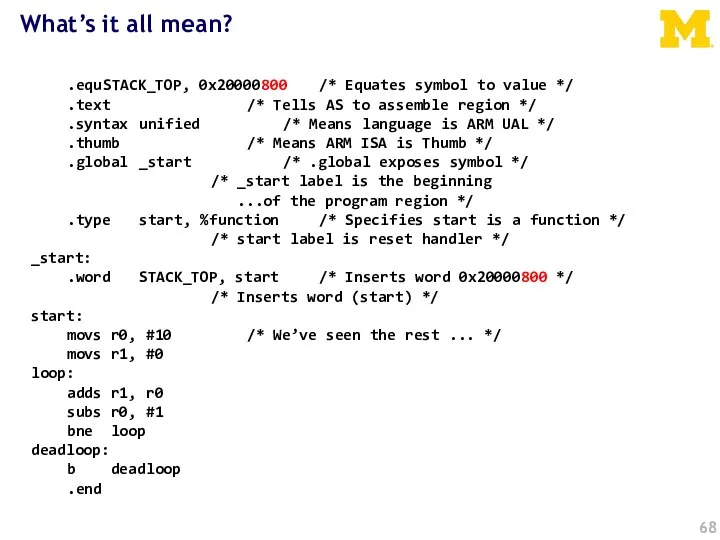

- 68. .equ STACK_TOP, 0x20000800 /* Equates symbol to value */ .text /* Tells AS to assemble region

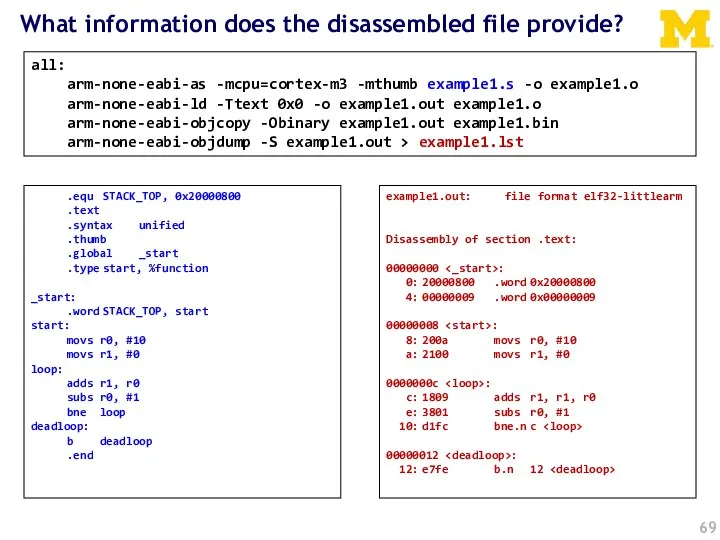

- 69. What information does the disassembled file provide? .equ STACK_TOP, 0x20000800 .text .syntax unified .thumb .global _start

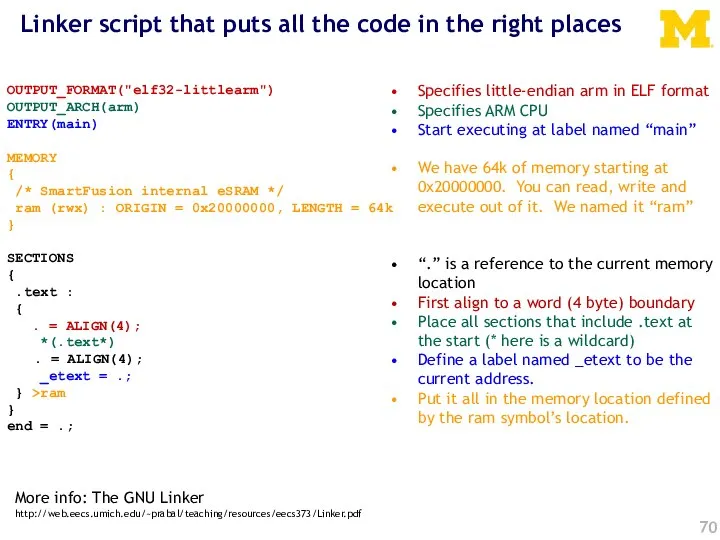

- 70. Linker script that puts all the code in the right places OUTPUT_FORMAT("elf32-littlearm") OUTPUT_ARCH(arm) ENTRY(main) MEMORY {

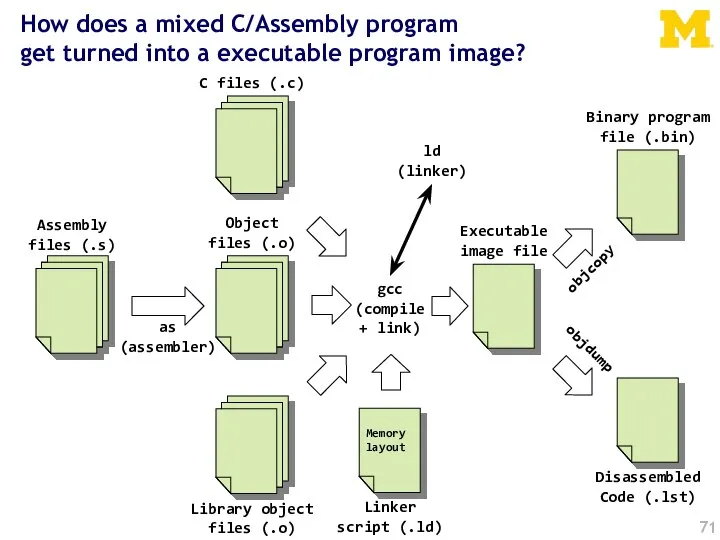

- 71. How does a mixed C/Assembly program get turned into a executable program image? Assembly files (.s)

- 72. Real-world example: Mixing C and assembly code To the terminal again! Example code online: https://github.com/brghena/eecs373_toolchain_examples $

- 73. Today… Finish ARM assembly example from last time Walk though of the ARM ISA Software Development

- 74. When is this relevant? The ABI establishes caller/callee responsibilities Who saves which registers How function parameters

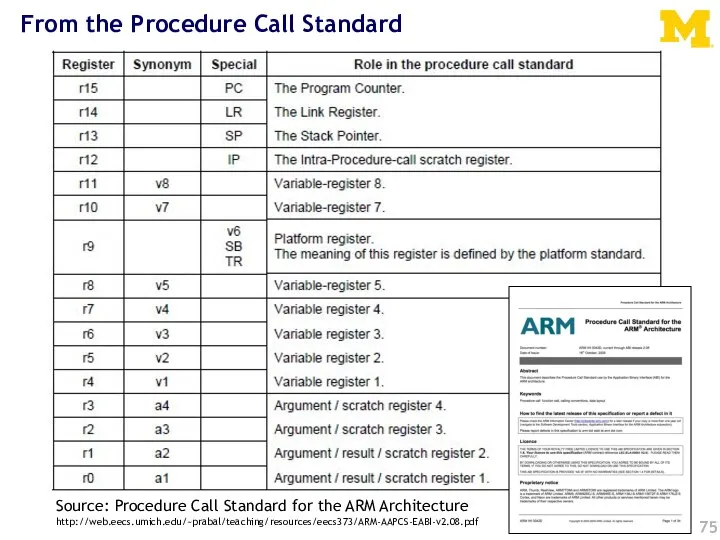

- 75. Source: Procedure Call Standard for the ARM Architecture http://web.eecs.umich.edu/~prabal/teaching/resources/eecs373/ARM-AAPCS-EABI-v2.08.pdf From the Procedure Call Standard

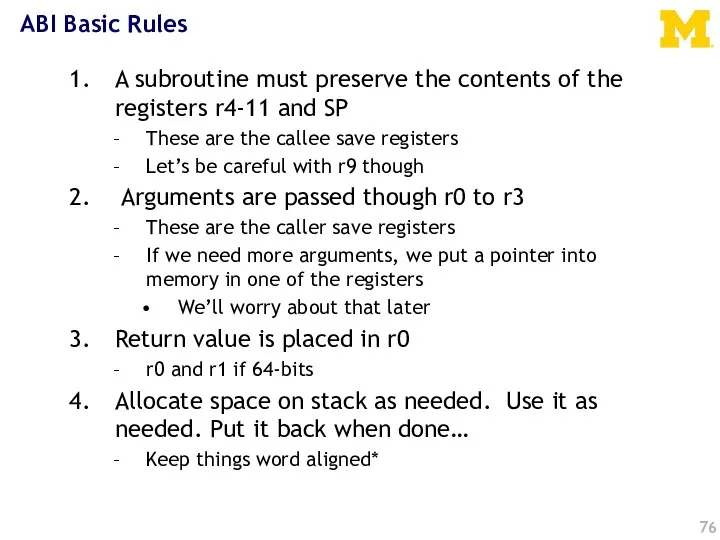

- 76. ABI Basic Rules A subroutine must preserve the contents of the registers r4-11 and SP These

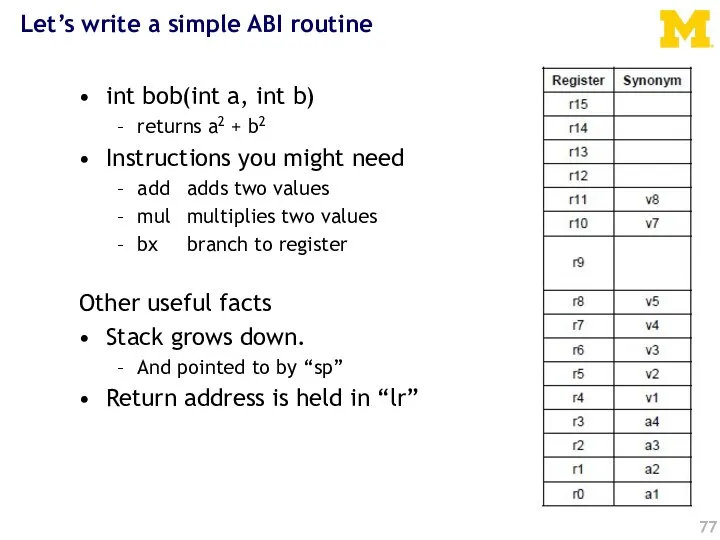

- 77. Let’s write a simple ABI routine int bob(int a, int b) returns a2 + b2 Instructions

- 79. Скачать презентацию

![IT blocks Conditional execution in C-M3 done in “IT” block IT [T|E]*3 More on this later…](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/946467/slide-52.jpg)

Зависимость от социальных сетей

Зависимость от социальных сетей Глобальная компьютерная сеть Интернет. Тест

Глобальная компьютерная сеть Интернет. Тест Система поиска автозапчастей

Система поиска автозапчастей Hiperteksta transporta protokols HTTP

Hiperteksta transporta protokols HTTP Lektsia_3

Lektsia_3 嵌入式系统的Boot Loader技术

嵌入式系统的Boot Loader技术 Двоичное кодирование. ( 6 класс)

Двоичное кодирование. ( 6 класс) Анатомия буквы

Анатомия буквы Разработка и продажа программного продукта в среде Visual Basic

Разработка и продажа программного продукта в среде Visual Basic Функции СУБД. Типовая организация СУБД. Дореляционные СУБД. Лекция №2

Функции СУБД. Типовая организация СУБД. Дореляционные СУБД. Лекция №2 CSS (каскадные документы стилей)

CSS (каскадные документы стилей) 1С: Номенклатура

1С: Номенклатура MagicDom. Game

MagicDom. Game Электронные ресурсы

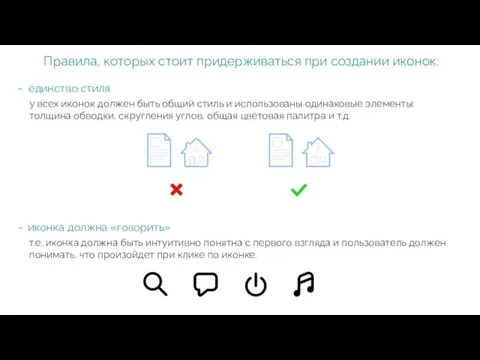

Электронные ресурсы Правила, которых стоит придерживаться при создании иконок

Правила, которых стоит придерживаться при создании иконок Сайти Інтернету

Сайти Інтернету Меры по обеспечению устойчивого экономического развития РО

Меры по обеспечению устойчивого экономического развития РО Поле чудес

Поле чудес Информационное общество. Плюсы и минусы

Информационное общество. Плюсы и минусы Уменьшение веса технологических машин, деталей и оборудования посредством трехмерного моделирования

Уменьшение веса технологических машин, деталей и оборудования посредством трехмерного моделирования Figma - жизнь до и после

Figma - жизнь до и после Файлы и файловая система

Файлы и файловая система Создание новостного текста

Создание новостного текста Группа Телеграм-каналов ВсеПроСпорт

Группа Телеграм-каналов ВсеПроСпорт ГИА составляется на основе стандарта основного общего образования, и сдать его успешно может любой выпускник IX класса

ГИА составляется на основе стандарта основного общего образования, и сдать его успешно может любой выпускник IX класса Представление целых чисел в компьютере. 8 класс

Представление целых чисел в компьютере. 8 класс Вводная презентация в региональный сетевой интернет-проект Дресс-код современного читателя

Вводная презентация в региональный сетевой интернет-проект Дресс-код современного читателя Персональный компьютер

Персональный компьютер