Слайд 2Архитектура ВМ

Архитектура – это функциональная организация ВМ без физической реализации.

Представление данных и

их связь с назначением, организация хранения и способы кодирования.

Адресация – способ определения адреса операнда по информации в адресной части команды.

Структура команд: части команд и взаимодействие частей.

Система команд – перечень команд.

Организация вычислительного процесса.

Организация ввода-вывода.

Система прерываний.

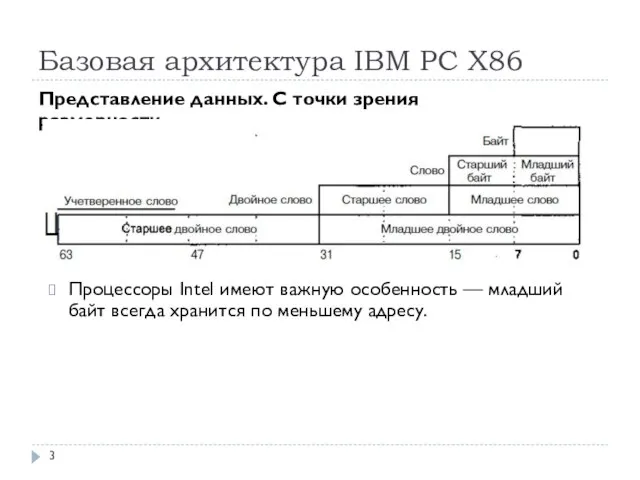

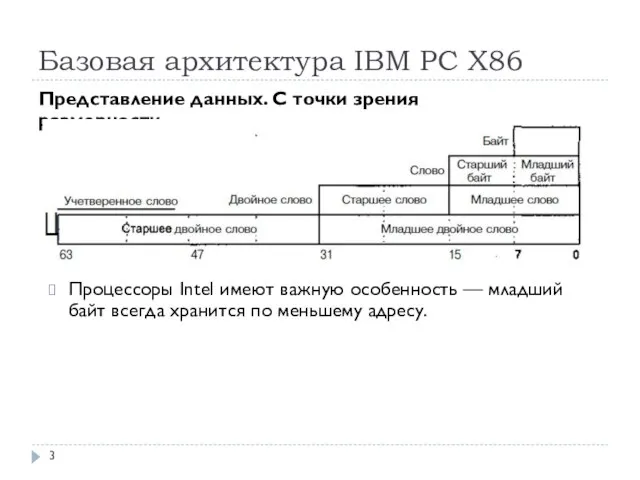

Слайд 3Базовая архитектура IBM PC Х86

Представление данных. С точки зрения размерности

Процессоры Intel имеют

важную особенность — младший байт всегда хранится по меньшему адресу.

Слайд 4Базовая архитектура IBM PC Х86

Представление данных. С точки зрения логической интерпретации

Целый тип

со знаком (в дополнительном коде)

8-разрядное целое— от-128 до+127;

16-разрядное целое — от -32 768 до +32 767;

32-разрядное целое — от -2^31 до +2^31 - 1.

Целый тип без знака

байт — от 0 до 255;

слово — от 0 до 65 535;

двойное слово— от 0 до 2^32 - 1.

Указатель на память

ближний тип — 32-разрядный логический адрес

дальний тип — 48-разрядный логический адрес

Слайд 5Базовая архитектура IBM PC Х86

Представление данных. С точки зрения логической интерпретации

Цепочка представляет

собой некоторый непрерывный набор байтов, слов или двойных слов максимальной длиной до 4 Гбайт.

Битовое поле. Каждый бит является независимым и может рассматриваться как отдельная переменная. Битовое поле может начинаться с любого бита любого байта и содержать до 32 битов.

Неупакованный двоично-десятичный тип — байтовое представление десятичной цифры от 0 до 9. По одной цифре в каждом бай

Упакованный двоично-десятичный тип. Хранит две десятичных цифр от 0 до 9 в одном байте. Каждая цифра хранится в своем полубайте.

Слайд 6Базовая архитектура IBM PC Х86

Представление данных. С точки зрения логической интерпретации

Типы данных

с плавающей точкой. Сопроцессор имеет несколько собственных типов данных, несовместимых с типами данных целочисленного устройства.

Типы данных MMX-расширения Pentium MMX/II/III/IV. Данный тип данных появился в процессоре Pentium MMX.

Типы данных MMX-расширения Pentium III/IV. Этот тип данных появился в процессоре Pentium III.

Слайд 7Базовая архитектура IBM PC Х86

Организация вычислительного процесса

Вычислительный процесс организован в полном соответствии

с принципами фон Неймана.

Для ускорения введено понятие конвейера команд,

из которого извлекается следующая команда.

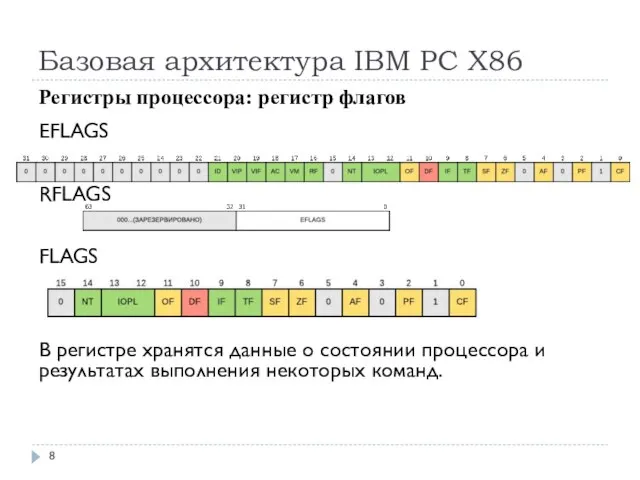

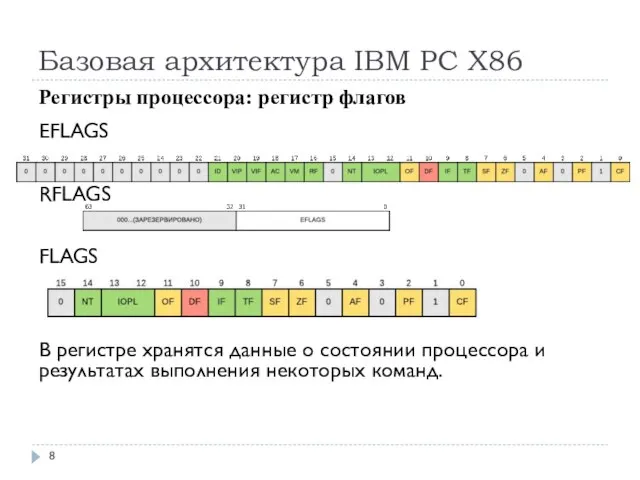

Слайд 8Базовая архитектура IBM PC Х86

Регистры процессора: регистр флагов

EFLAGS

RFLAGS

FLAGS

В регистре хранятся данные о

состоянии процессора и результатах выполнения некоторых команд.

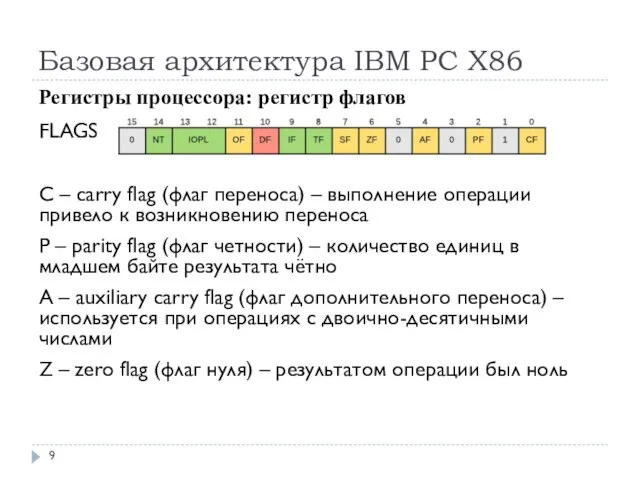

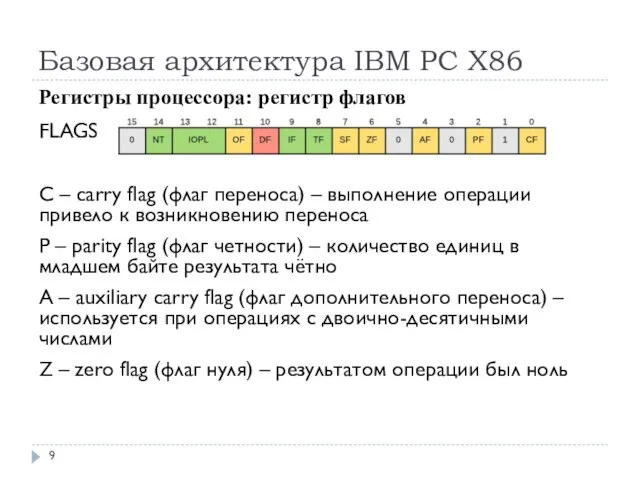

Слайд 9Базовая архитектура IBM PC Х86

Регистры процессора: регистр флагов

FLAGS

C – carry flag (флаг

переноса) – выполнение операции привело к возникновению переноса

P – parity flag (флаг четности) – количество единиц в младшем байте результата чётно

A – auxiliary carry flag (флаг дополнительного переноса) – используется при операциях с двоично-десятичными числами

Z – zero flag (флаг нуля) – результатом операции был ноль

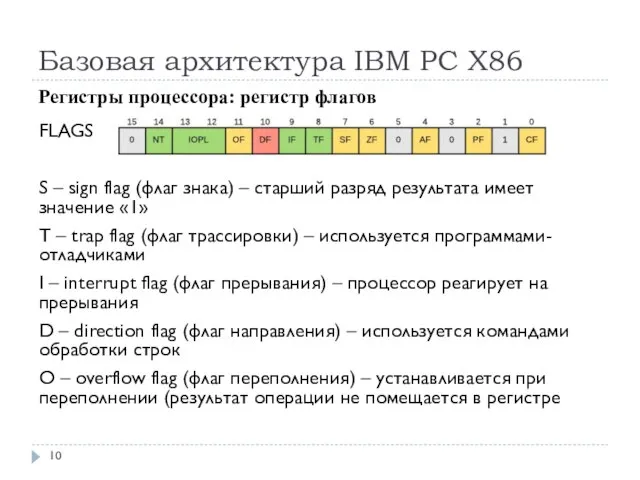

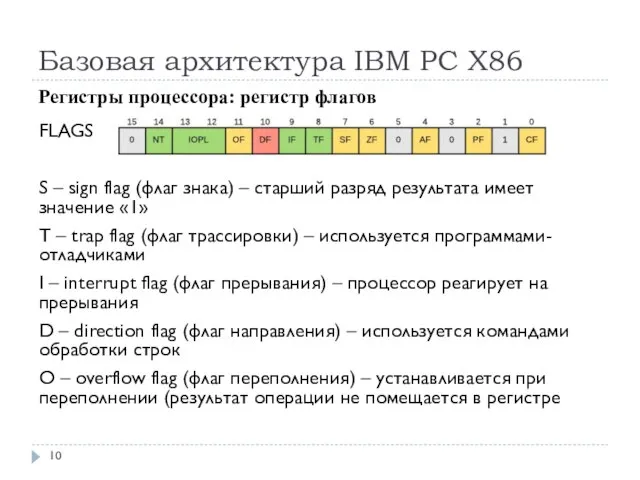

Слайд 10Базовая архитектура IBM PC Х86

Регистры процессора: регистр флагов

FLAGS

S – sign flag (флаг

знака) – старший разряд результата имеет значение «1»

T – trap flag (флаг трассировки) – используется программами-отладчиками

I – interrupt flag (флаг прерывания) – процессор реагирует на прерывания

D – direction flag (флаг направления) – используется командами обработки строк

O – overflow flag (флаг переполнения) – устанавливается при переполнении (результат операции не помещается в регистре

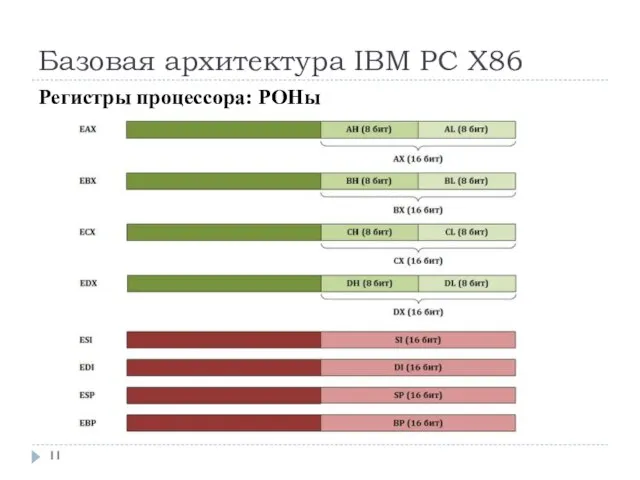

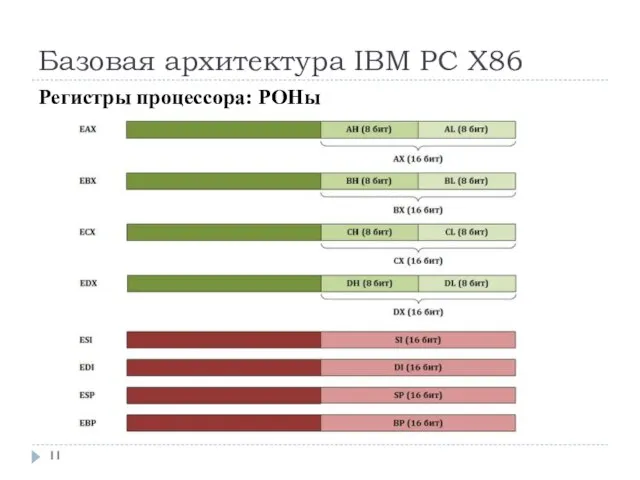

Слайд 11Базовая архитектура IBM PC Х86

Регистры процессора: РОНы

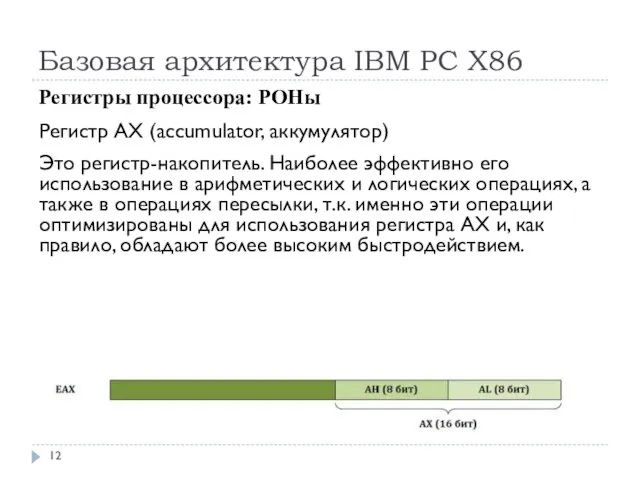

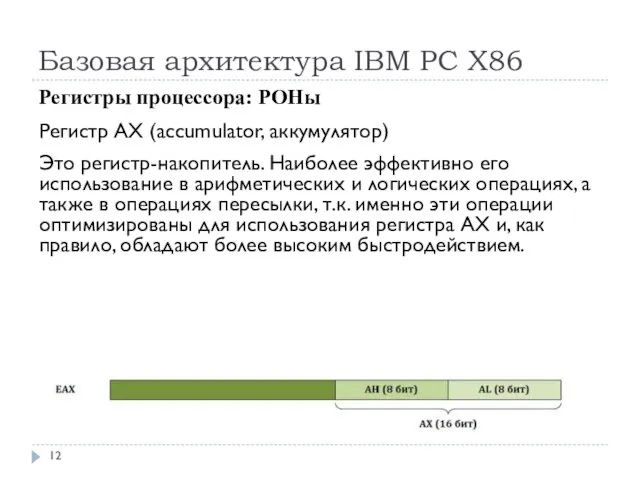

Слайд 12Базовая архитектура IBM PC Х86

Регистры процессора: РОНы

Регистр AX (accumulator, аккумулятор)

Это регистр-накопитель. Наиболее

эффективно его использование в арифметических и логических операциях, а также в операциях пересылки, т.к. именно эти операции оптимизированы для использования регистра AX и, как правило, обладают более высоким быстродействием.

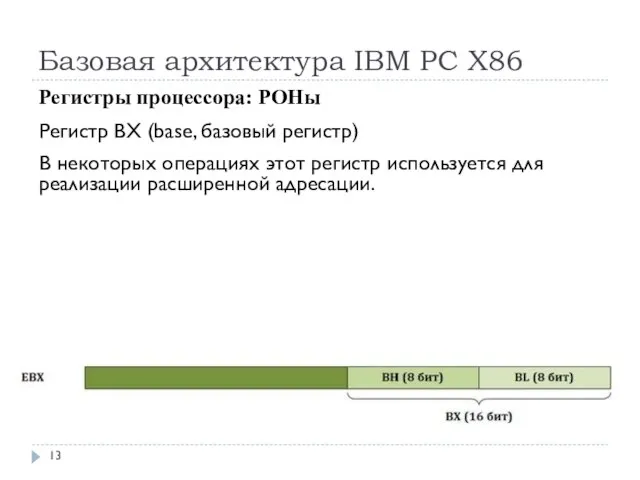

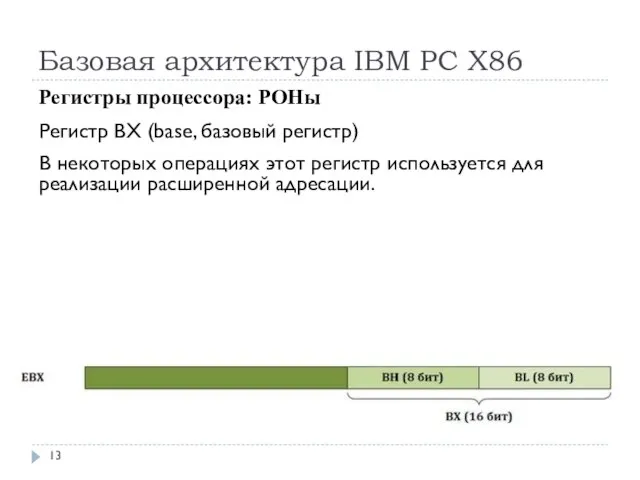

Слайд 13Базовая архитектура IBM PC Х86

Регистры процессора: РОНы

Регистр BX (base, базовый регистр)

В некоторых

операциях этот регистр используется для реализации расширенной адресации.

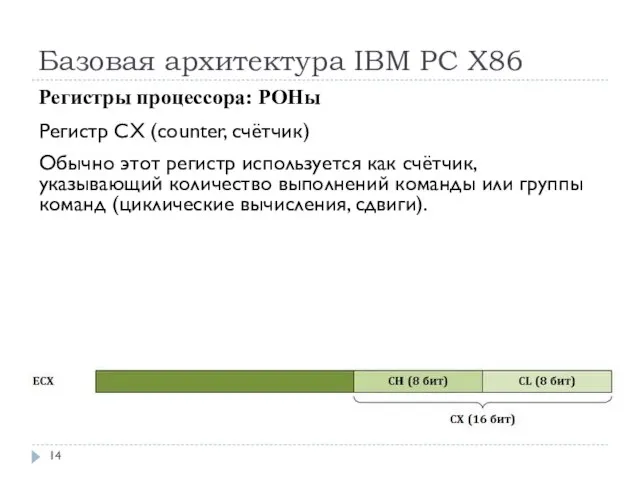

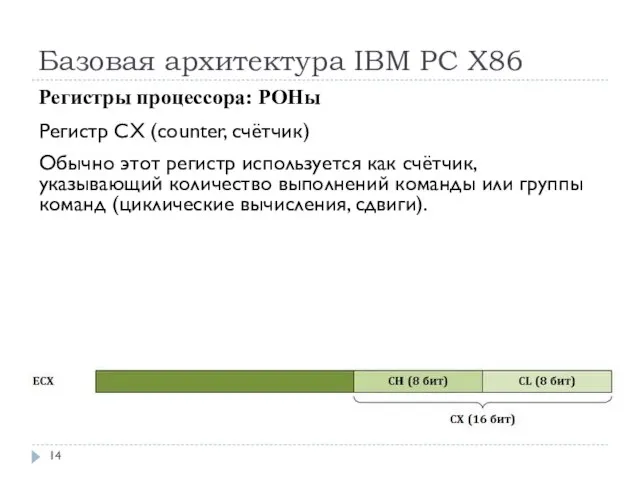

Слайд 14Базовая архитектура IBM PC Х86

Регистры процессора: РОНы

Регистр CX (counter, счётчик)

Обычно этот регистр

используется как счётчик, указывающий количество выполнений команды или группы команд (циклические вычисления, сдвиги).

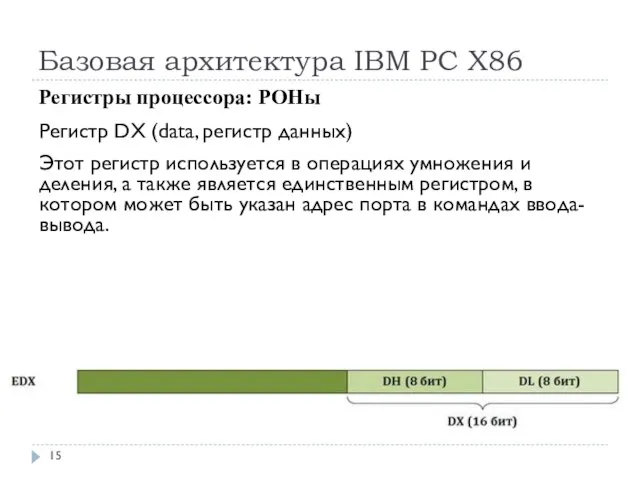

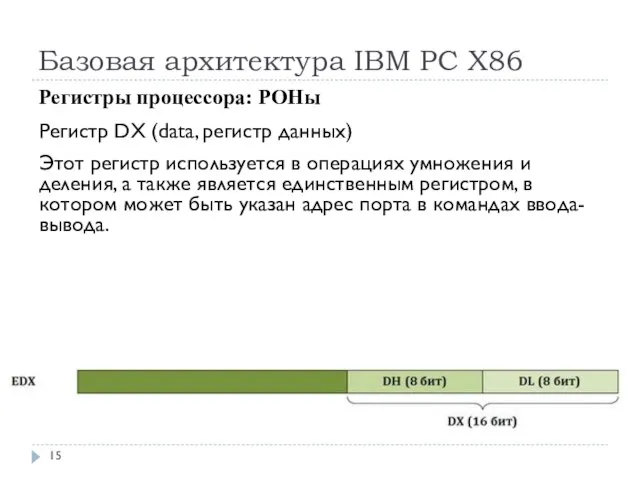

Слайд 15Базовая архитектура IBM PC Х86

Регистры процессора: РОНы

Регистр DX (data, регистр данных)

Этот регистр

используется в операциях умножения и деления, а также является единственным регистром, в котором может быть указан адрес порта в командах ввода-вывода.

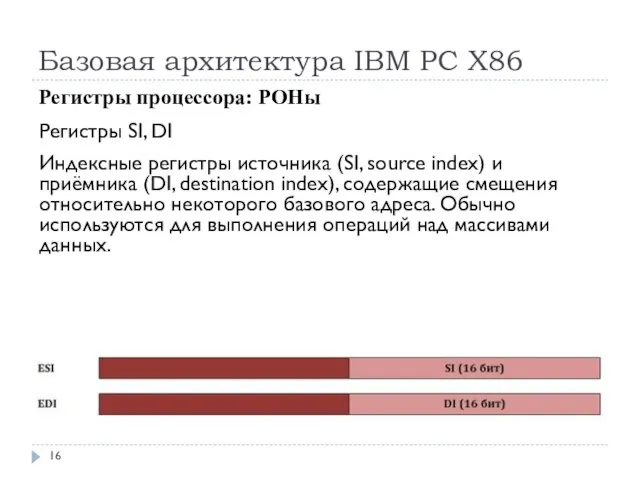

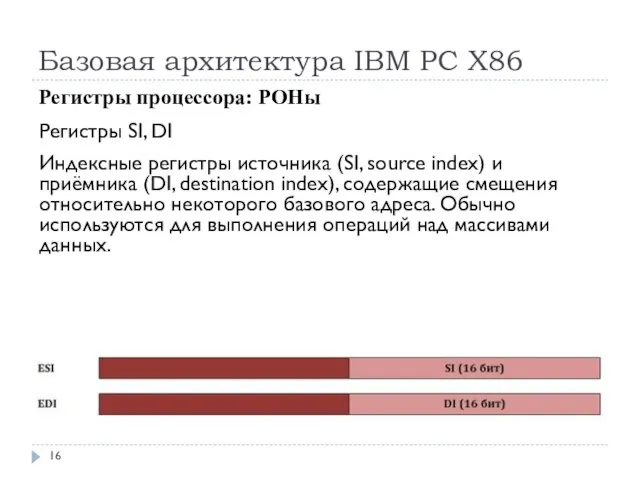

Слайд 16Базовая архитектура IBM PC Х86

Регистры процессора: РОНы

Регистры SI, DI

Индексные регистры источника (SI,

source index) и приёмника (DI, destination index), содержащие смещения относительно некоторого базового адреса. Обычно используются для выполнения операций над массивами данных.

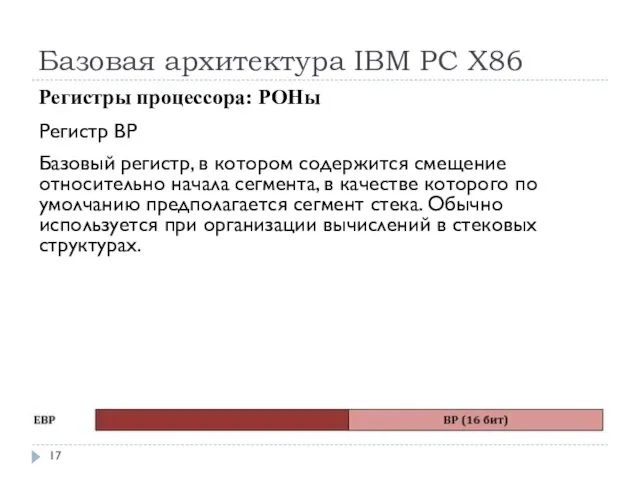

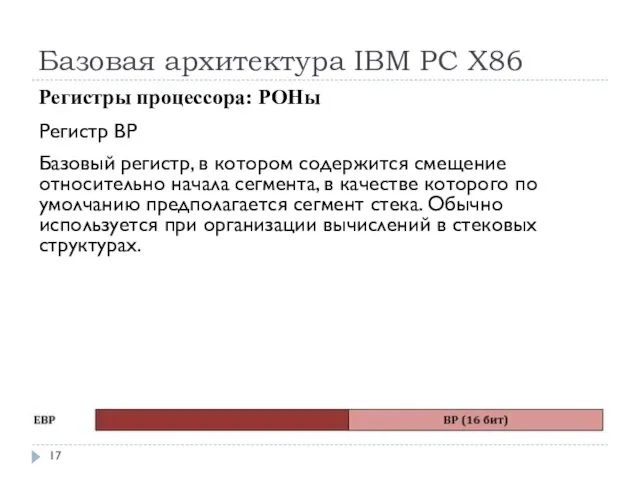

Слайд 17Базовая архитектура IBM PC Х86

Регистры процессора: РОНы

Регистр BP

Базовый регистр, в котором содержится

смещение относительно начала сегмента, в качестве которого по умолчанию предполагается сегмент стека. Обычно используется при организации вычислений в стековых структурах.

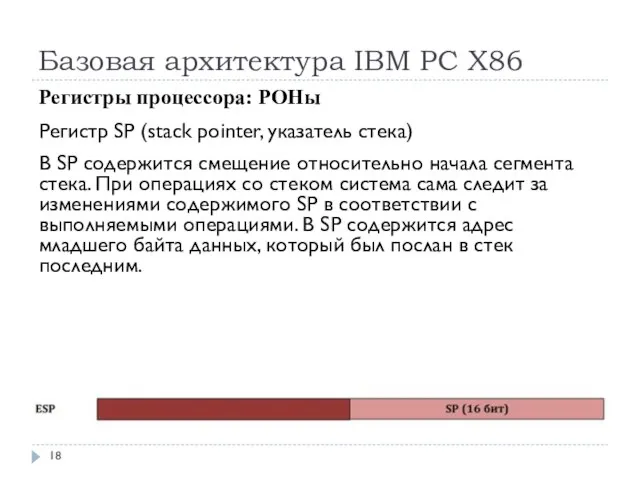

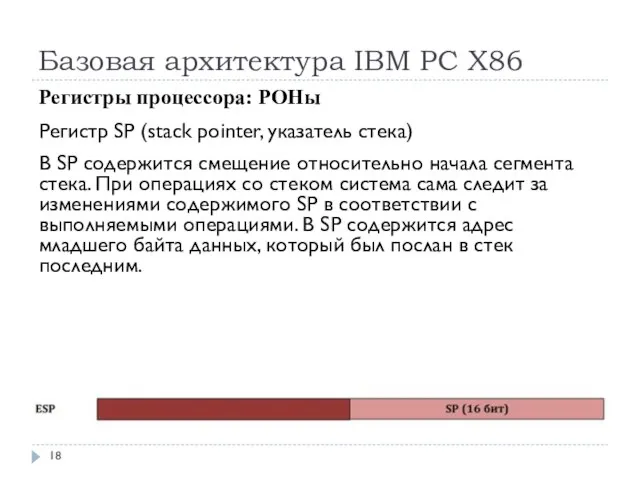

Слайд 18Базовая архитектура IBM PC Х86

Регистры процессора: РОНы

Регистр SP (stack pointer, указатель стека)

В

SP содержится смещение относительно начала сегмента стека. При операциях со стеком система сама следит за изменениями содержимого SP в соответствии с выполняемыми операциями. В SP содержится адрес младшего байта данных, который был послан в стек последним.

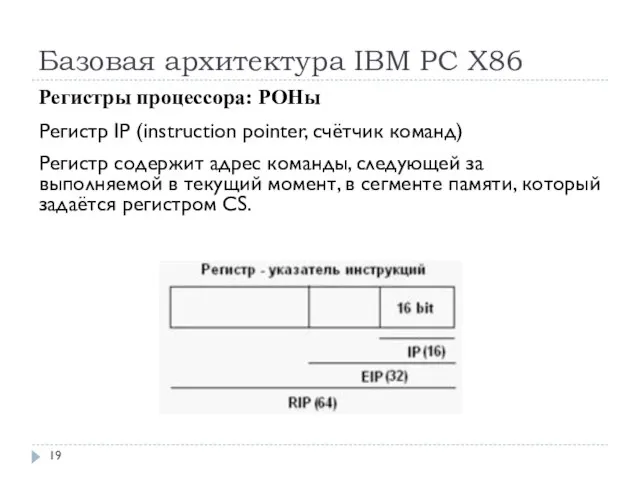

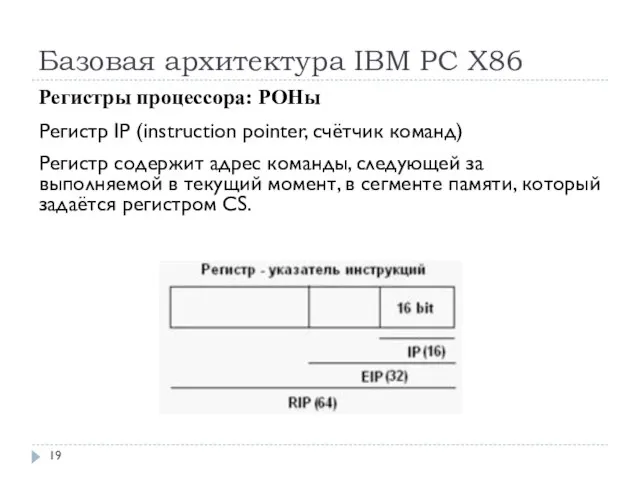

Слайд 19Базовая архитектура IBM PC Х86

Регистры процессора: РОНы

Регистр IP (instruction pointer, счётчик команд)

Регистр

содержит адрес команды, следующей за выполняемой в текущий момент, в сегменте памяти, который задаётся регистром CS.

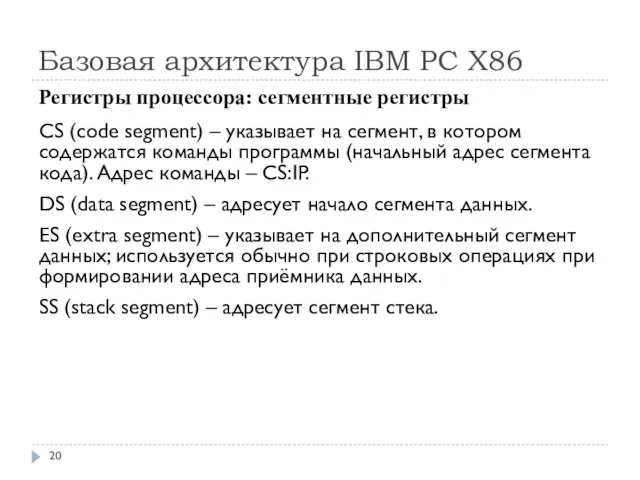

Слайд 20Базовая архитектура IBM PC Х86

Регистры процессора: сегментные регистры

CS (code segment) – указывает

на сегмент, в котором содержатся команды программы (начальный адрес сегмента кода). Адрес команды – CS:IP.

DS (data segment) – адресует начало сегмента данных.

ES (extra segment) – указывает на дополнительный сегмент данных; используется обычно при строковых операциях при формировании адреса приёмника данных.

SS (stack segment) – адресует сегмент стека.

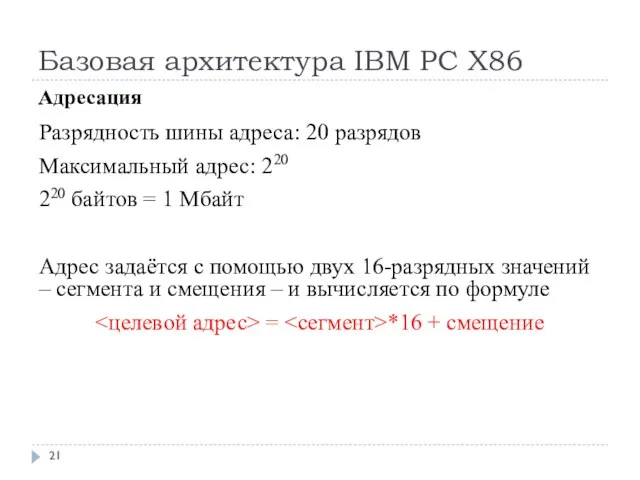

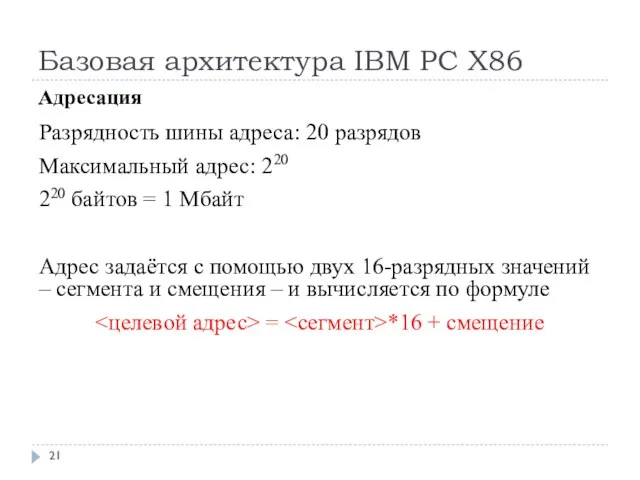

Слайд 21Базовая архитектура IBM PC Х86

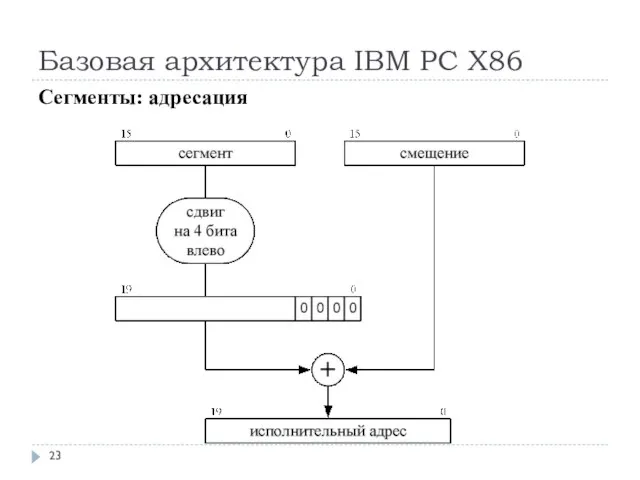

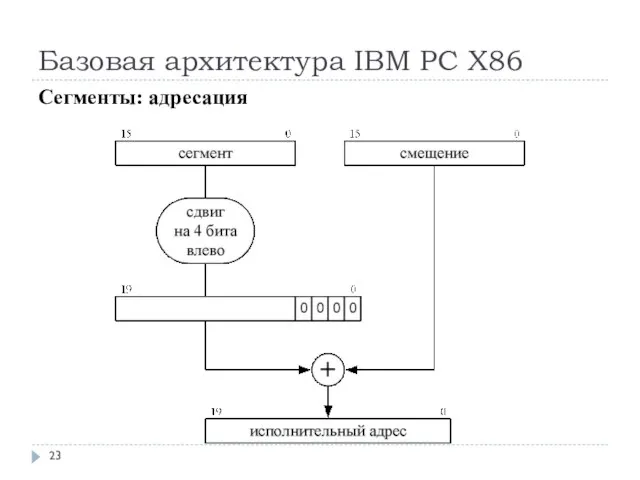

Адресация

Разрядность шины адреса: 20 разрядов

Максимальный адрес: 220

220 байтов

= 1 Мбайт

Адрес задаётся с помощью двух 16-разрядных значений – сегмента и смещения – и вычисляется по формуле

<целевой адрес> = <сегмент>*16 + смещение

Слайд 22Базовая архитектура IBM PC Х86

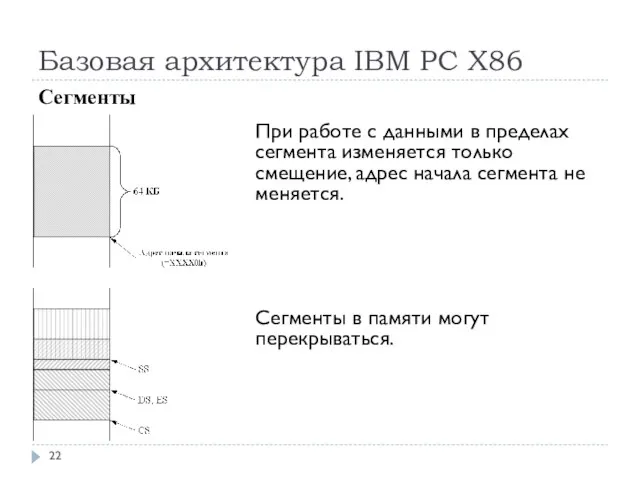

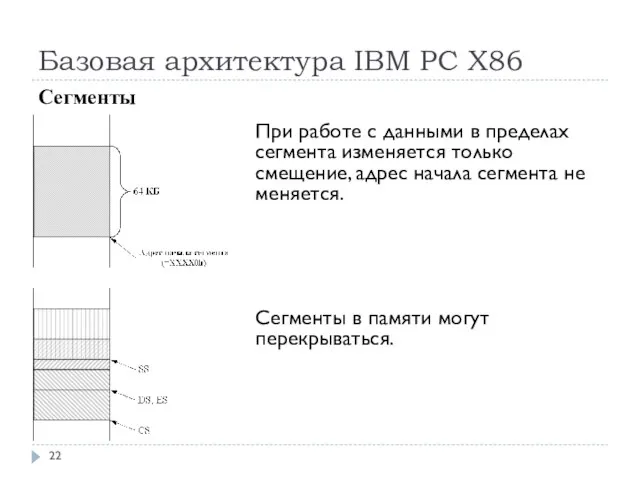

Сегменты

При работе с данными в пределах сегмента изменяется

только смещение, адрес начала сегмента не меняется.

Сегменты в памяти могут перекрываться.

Слайд 23Базовая архитектура IBM PC Х86

Сегменты: адресация

Слайд 24Базовая архитектура IBM PC Х86

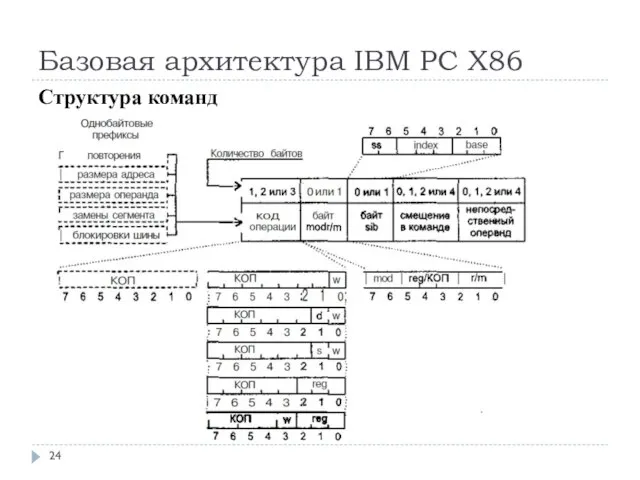

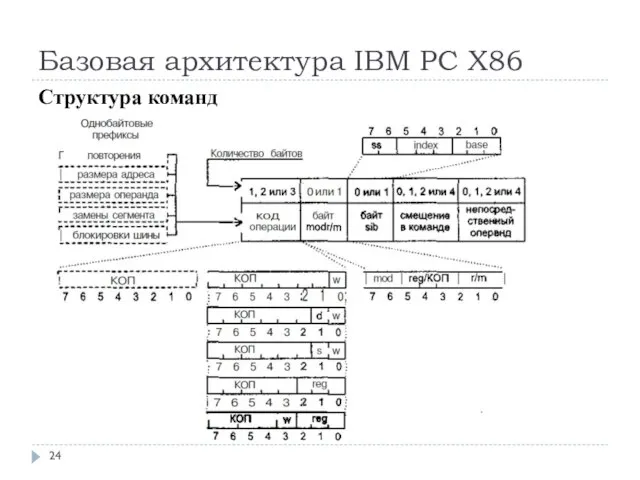

Структура команд

Слайд 25Базовая архитектура IBM PC Х86

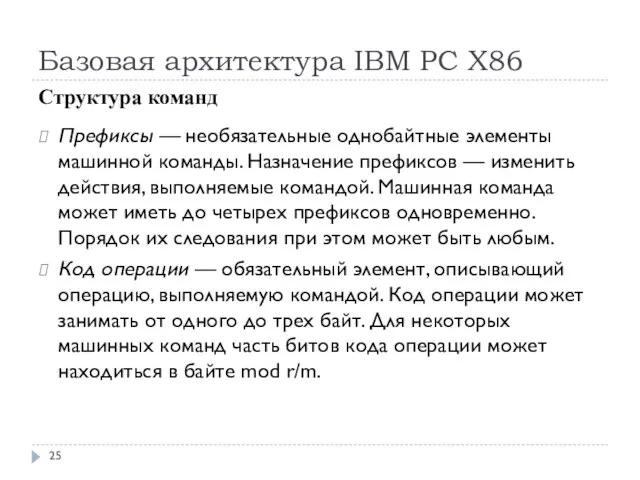

Структура команд

Префиксы — необязательные однобайтные элементы машинной команды.

Назначение префиксов — изменить действия, выполняемые командой. Машинная команда может иметь до четырех префиксов одновременно. Порядок их следования при этом может быть любым.

Код операции — обязательный элемент, описывающий операцию, выполняемую командой. Код операции может занимать от одного до трех байт. Для некоторых машинных команд часть битов кода операции может находиться в байте mod r/m.

Слайд 26Базовая архитектура IBM PC Х86

Структура команд

Байт режима адресации mod r/m, иногда называемый

постбайтом, несет информацию об операндах и режиме адресации. Если операнд находится в памяти, то байт mod r/m определяет компоненты (смещение, базовый и индексный регистры), используемые для вычисления его эффективного адреса.

Байт масштаба, индекса и базы (Scale-Index-Base — sib) используется для расширения возможностей адресации операндов. На наличие байта sib в машинной команде указывает сочетание одного из значений 01 или 10 поля mod и значения поля r/m = 100.

Слайд 27Базовая архитектура IBM PC Х86

Структура команд

Поле смещения в команде — это 8-,

16- или 32-разрядное целое число со знаком, представляющее собой полностью или частично значение эффективного адреса операнда.

Поле непосредственного операнда — необязательное поле, представляющее собой 8-, 16- или 32-разрядный непосредственный операнд.

Слайд 28Базовая архитектура IBM PC Х86

Система команд

Команды пересылки:

а) между регистрами и памятью;

б) между

регистрами и устройствами ввода-вывода.

Команды управления.

Арифметические и логические команды.

Команды манипулирования битами.

Команды для обработки строк.

Команды для поддержки механизма прерываний.

Команды изменения состояния процессора.

Слайд 29Базовая архитектура IBM PC Х86

Система прерываний

Предусмотрены прерывания аппаратные и программные.

Всего в системе

может быть до 255 прерываний.

Для реализации механизма прерываний выделен

1 КБайт оперативной памяти.

Интеллектуальный марафон

Интеллектуальный марафон Музыкальные компьютерные технологии

Музыкальные компьютерные технологии Турнир программистов. 7 класс

Турнир программистов. 7 класс Сказка Курочка ряба

Сказка Курочка ряба Базовые структуры алгоритмов

Базовые структуры алгоритмов Последняя версия 18-11

Последняя версия 18-11 Лабиринт в PowerPoint

Лабиринт в PowerPoint Описание игры Умная сталь-1

Описание игры Умная сталь-1 Знакомство с компьютером

Знакомство с компьютером Разработка системы выделения контуров образов графических изображений

Разработка системы выделения контуров образов графических изображений Подготовка теста в приложении Power Point

Подготовка теста в приложении Power Point Программирование на языке Паскаль

Программирование на языке Паскаль Вставка изображений в Web-страницы

Вставка изображений в Web-страницы Методы математического моделирования

Методы математического моделирования Информационное общество

Информационное общество Рекурсия в С++

Рекурсия в С++ Классы и структуры в C++

Классы и структуры в C++ Любая достаточно развитая технология неотличима от магии. Третий закон Артура Кларка

Любая достаточно развитая технология неотличима от магии. Третий закон Артура Кларка Sample PowerPoint File

Sample PowerPoint File Select boot device Sandisk

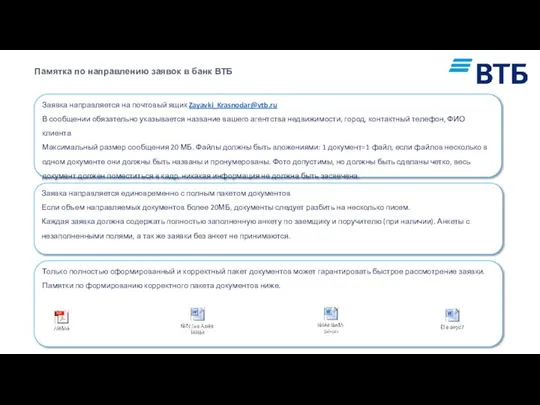

Select boot device Sandisk Направление заявок в банк ВТБ

Направление заявок в банк ВТБ Операционные системы

Операционные системы Подробная инструкция по заполнению заявок

Подробная инструкция по заполнению заявок Популярные образовательные площадки

Популярные образовательные площадки Программные средства визуализации данных

Программные средства визуализации данных Письменные источники информации

Письменные источники информации Управление изменениями

Управление изменениями Лекция 5

Лекция 5