Содержание

- 2. Базовые логические схемы Триггеры Регистры Полусумматор Сумматор Логические элементы ЭВМ

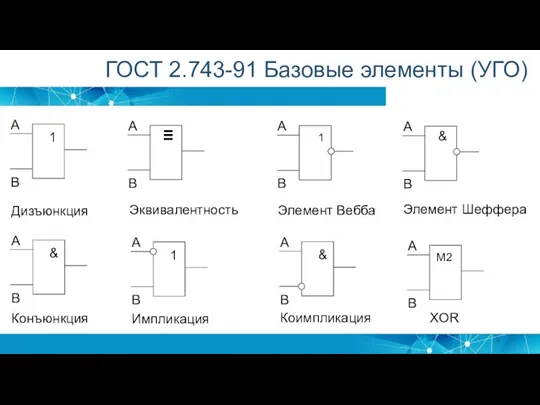

- 3. ГОСТ 2.743-91 Базовые элементы (УГО) XOR 1 А В Импликация & А В Элемент Шеффера &

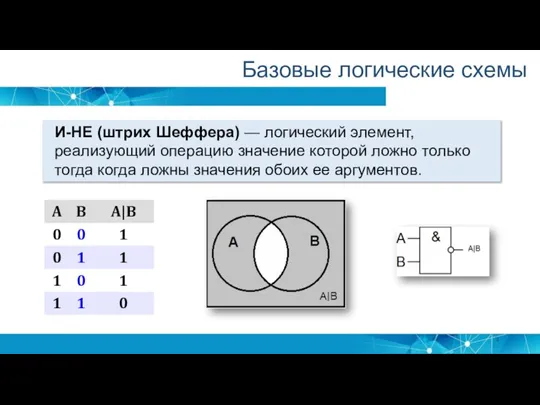

- 4. Базовые логические схемы И-НЕ (штрих Шеффера) — логический элемент, реализующий операцию значение которой ложно только тогда

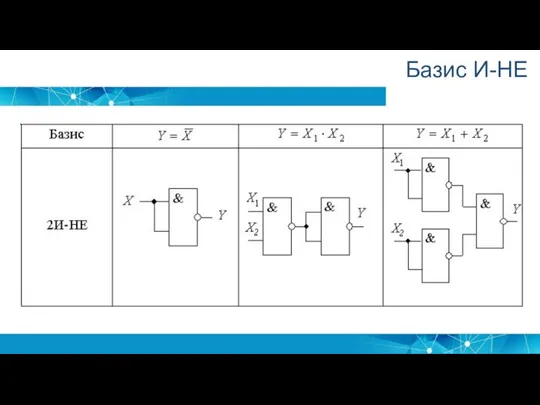

- 5. Базис И-НЕ

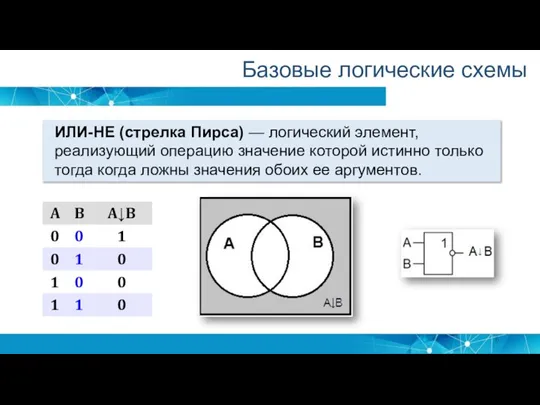

- 6. Базовые логические схемы ИЛИ-НЕ (стрелка Пирса) — логический элемент, реализующий операцию значение которой истинно только тогда

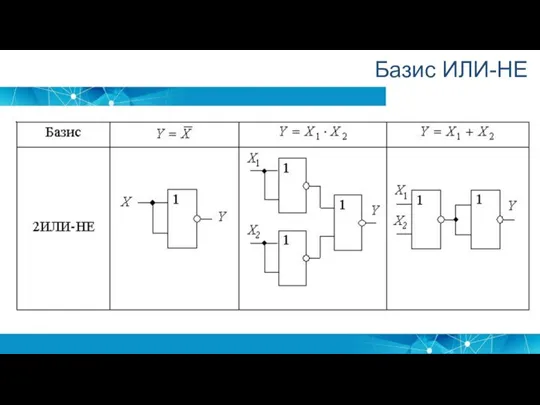

- 7. Базис ИЛИ-НЕ

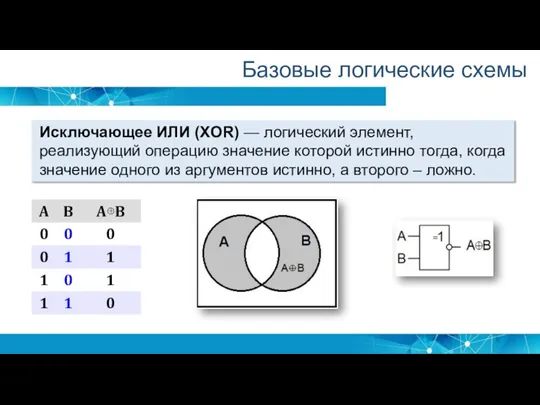

- 8. Базовые логические схемы Исключающее ИЛИ (XOR) — логический элемент, реализующий операцию значение которой истинно тогда, когда

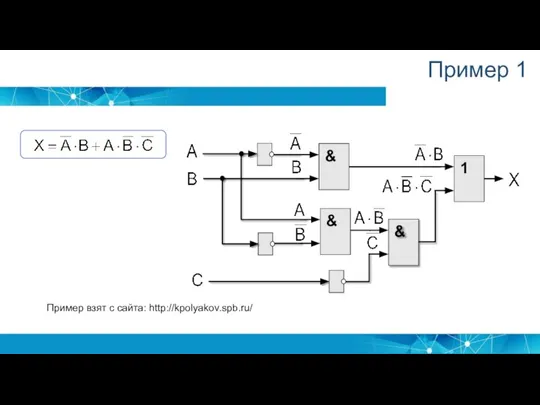

- 9. Пример 1 Пример взят с сайта: http://kpolyakov.spb.ru/

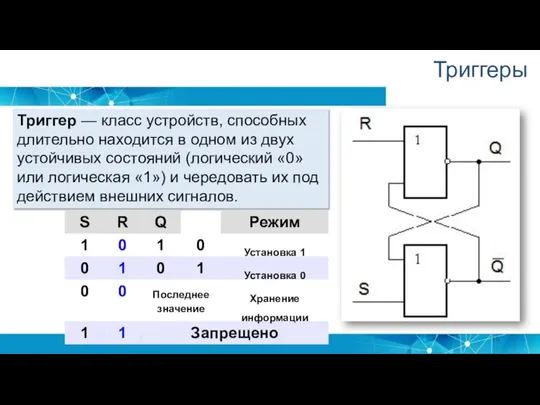

- 10. Триггеры Триггер — класс устройств, способных длительно находится в одном из двух устойчивых состояний (логический «0»

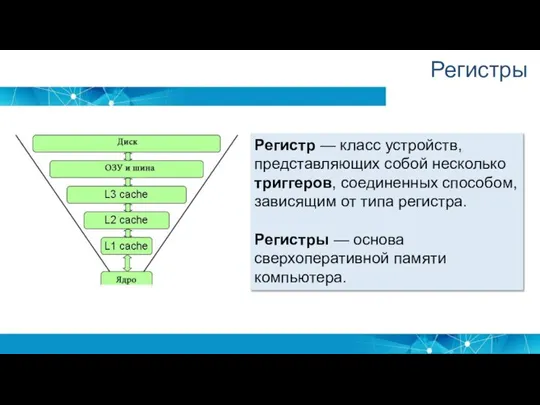

- 11. Регистры Регистр — класс устройств, представляющих собой несколько триггеров, соединенных способом, зависящим от типа регистра. Регистры

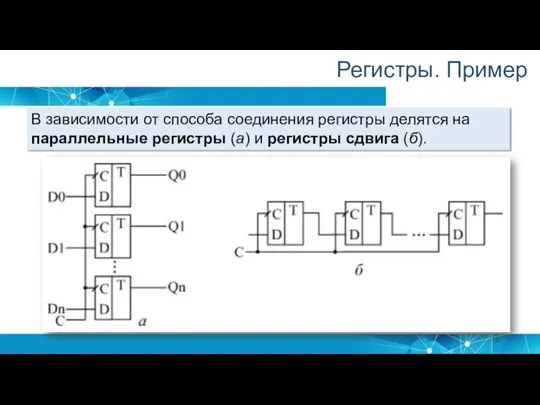

- 12. Регистры. Пример В зависимости от способа соединения регистры делятся на параллельные регистры (а) и регистры сдвига

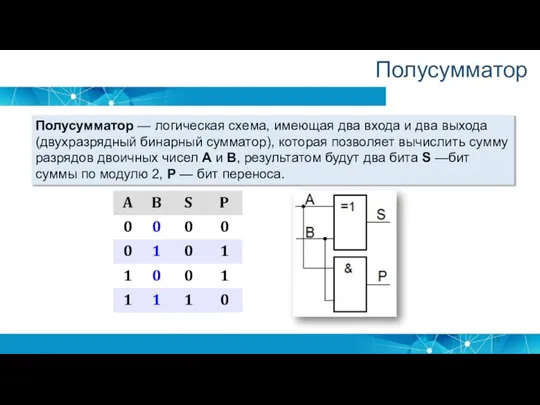

- 13. Полусумматор Полусумматор — логическая схема, имеющая два входа и два выхода (двухразрядный бинарный сумматор), которая позволяет

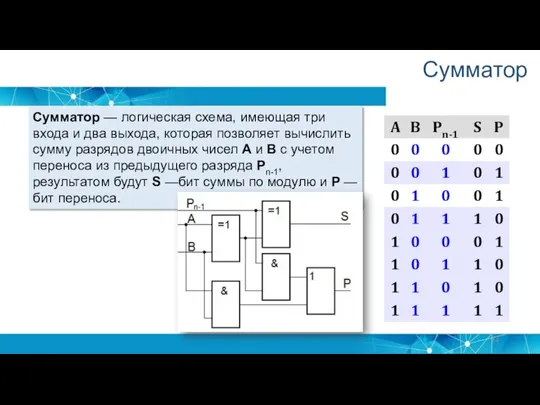

- 14. Сумматор — логическая схема, имеющая три входа и два выхода, которая позволяет вычислить сумму разрядов двоичных

- 15. Спасибо за внимание!

- 16. Уржумов Даниил Владимирович старший преподаватель кафедры информатики ФГБОУ ВО «ПГТУ», г. Йошкар-Ола [email protected] Ипатов Юрий Аркадьевич

- 18. Скачать презентацию

Соотношения между сторонами и углами в прямоугольном треугольнике

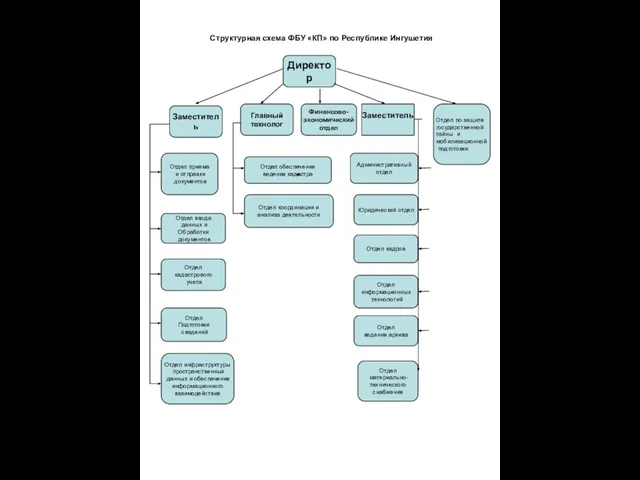

Соотношения между сторонами и углами в прямоугольном треугольнике Директор

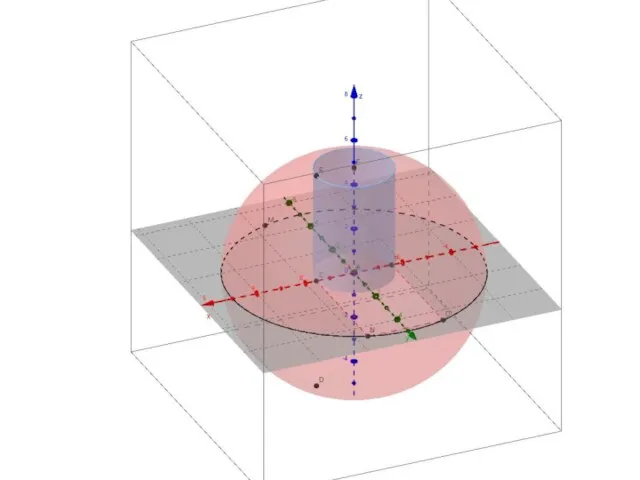

Директор Шар с 3 осями

Шар с 3 осями ОРУЖИЕ ПОБЕДЫ

ОРУЖИЕ ПОБЕДЫ Методы обучения и воспитания

Методы обучения и воспитания Реформирование охраны труда в России - переход к управлению профессиональными рисками в системе управления охраной труда

Реформирование охраны труда в России - переход к управлению профессиональными рисками в системе управления охраной труда Футуризм и Супрематизм, в живописи

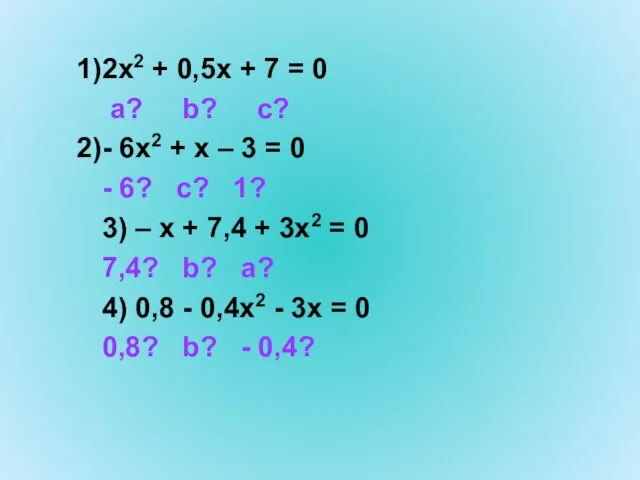

Футуризм и Супрематизм, в живописи 2х2 + 0,5х + 7 = 0 а? b? с? - 6х2 + х – 3 = 0 - 6? с? 1? 3) – х + 7,4 + 3х2 = 0 7,4? b? а? 4) 0,8 - 0,4х2 - 3х = 0 0,8? b? - 0,4?

2х2 + 0,5х + 7 = 0 а? b? с? - 6х2 + х – 3 = 0 - 6? с? 1? 3) – х + 7,4 + 3х2 = 0 7,4? b? а? 4) 0,8 - 0,4х2 - 3х = 0 0,8? b? - 0,4? ТЕПЛОВИЙ БАЛАНС

ТЕПЛОВИЙ БАЛАНС Краны пролётного типа

Краны пролётного типа Web-аналітика: 3 найважливіші цифри

Web-аналітика: 3 найважливіші цифри преза

преза Конституция Российской Федерации. Что такое Конституция?

Конституция Российской Федерации. Что такое Конституция? Виды и формы бизнеса

Виды и формы бизнеса CRI/CRIN

CRI/CRIN Презентация Microsoft PowerPoint

Презентация Microsoft PowerPoint Энергетика и ожирение

Энергетика и ожирение ВИЧ И ПРАВА ЧЕЛОВЕКА

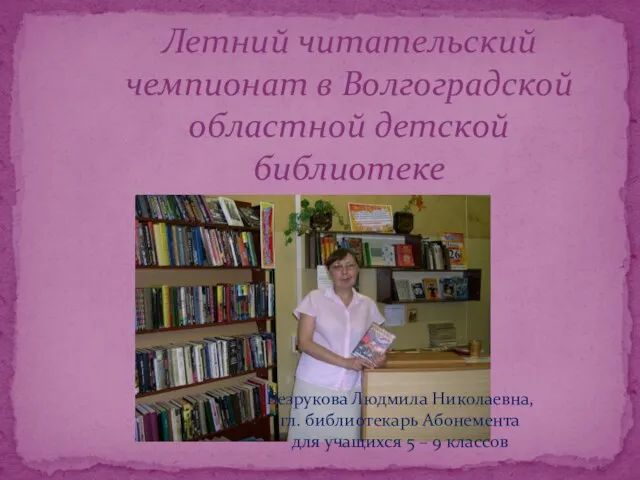

ВИЧ И ПРАВА ЧЕЛОВЕКА Летний читательский чемпионат в Волгоградской областной детской библиотеке

Летний читательский чемпионат в Волгоградской областной детской библиотеке Напишите мне письмо!

Напишите мне письмо! Финансовая грамотность в информационно – библиотечной среде

Финансовая грамотность в информационно – библиотечной среде Презентация на тему Причуды истории (психоактивные вещества)

Презентация на тему Причуды истории (психоактивные вещества) БОЛЬШИЕ ДЕНЬГИ В ВАШЕЙ ЖИЗНИ, СЕТЕВОЙ МАРКЕТИНГ

БОЛЬШИЕ ДЕНЬГИ В ВАШЕЙ ЖИЗНИ, СЕТЕВОЙ МАРКЕТИНГ Использование ассоциаций на уроке немецкого

Использование ассоциаций на уроке немецкого Развитие телекоммуникационной инфраструктуры сферы образования (ТИСО)

Развитие телекоммуникационной инфраструктуры сферы образования (ТИСО) А.С.ПушкинПеснь о вещем Олеге

А.С.ПушкинПеснь о вещем Олеге My land

My land Твардовский "Рассказ танкиста" 5 класс

Твардовский "Рассказ танкиста" 5 класс