Содержание

- 2. Алгебра логики и логические элементы. Для описания логики функционирования аппаратных и программных средств компьютера используется алгебра

- 3. Прежде всего булева алгебра была использована для преобразования релейно- контактных схем. Если имеется электрическая цепь с

- 4. Техническое устройство, реализующее логическую функцию, может рассматриваться просто как логический элемент, внутренняя структура которого не конкретизируется.

- 5. Логические схемы НЕ обычно реализуются на транзисторах, которые не только инвертируют входной сигнал, но и могут

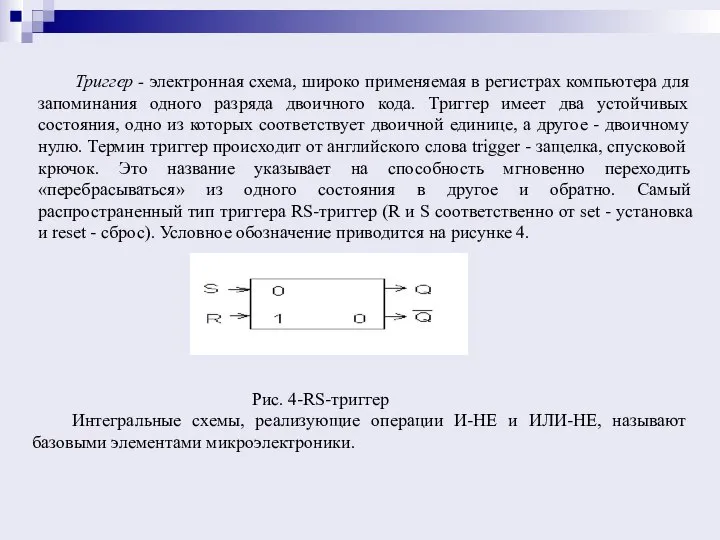

- 6. Триггер - электронная схема, широко применяемая в регистрах компьютера для запоминания одного разряда двоичного кода. Триггер

- 7. Основные параметры логических элементов. Логические элементы характеризуются многими параметрами. Среди них основными являются: коэффициент объединения по

- 8. Узлы компьютера. Построение компьютера ведется по следующей цепочке: элементы -» узлы -» устройства. Узел - это

- 9. Таким образом, выходные сигналы комбинационного аппарата полностью определяются входными сигналами и не зависят от внутреннего состояния

- 10. О понятии «архитектура ЭВМ». «Архитектура ЭВМ - это наиболее общие принципы построения ЭВМ, реализующие программное управление

- 11. . Классическая архитектура ЭВМ и принципы фон Неймана. Основы учения об архитектуре вычислительных машин заложил Джон

- 12. Принцип адресности. Структурно основная память состоит из перенумерованных ячеек; процессору в произвольный момент времени доступна любая

- 13. Основной алгоритм работы процессора: Начало цикла чтение команды из памяти по адресу, записанному в СК увеличение

- 14. Так как команды программы расположены в памяти друг за другом, то тем самым организуется выборка цепочки

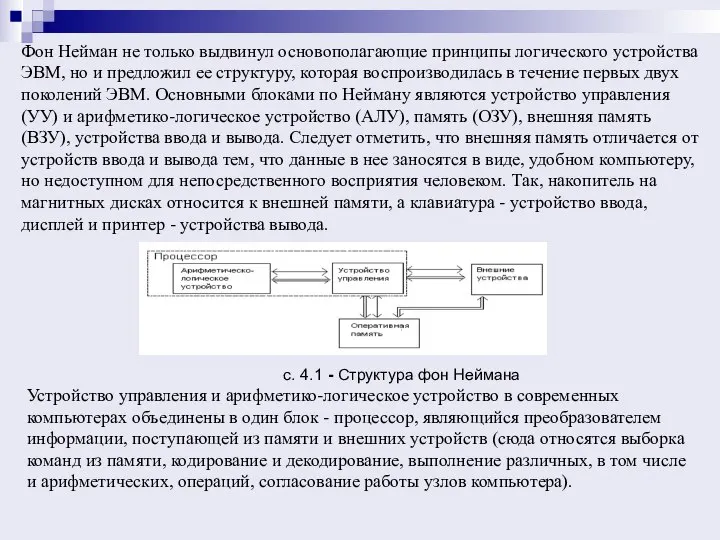

- 15. Фон Нейман не только выдвинул основополагающие принципы логического устройства ЭВМ, но и предложил ее структуру, которая

- 16. Память (ЗУ) хранит информацию (данные) и программы. Запоминающее устройство у современных компьютеров «многоярусно» и включает: оперативное

- 17. В построенной по описанной схеме ЭВМ происходит последовательное считывание команд из памяти и их выполнение. Номер

- 18. Типы архитектур. Основные классические типы архитектур можно определить как: «звезда», иерархическая, магистральная. Архитектура «звезда» - ЦУ

- 19. Периферийные устройства подключаются к аппаратуре компьютера через специальные контроллеры – устройства управления периферийными устройствами. Контроллер –

- 20. Процессор, структура и функционирование. Абстрактное центральное устройство. Перечислим основные понятия и рассмотрим структуру и функции абстрактного

- 21. Регистры – устройства, предназначенные для временного хранения данных ограниченного размера. Важной характеристикой регистра является высокая скорость

- 22. Командный цикл процессора. Цикл выполнения команды может выглядеть следующим образом. 1. В соответствии с содержимым СчАК

- 23. Арифметико-логическое устройство (АЛУ). ArithmeticandLogicalUnit (ALU) - компонента процессора, которая осуществляет арифметические и логические операции. АЛУ обеспечивает

- 24. Помимо арифметического устройства, АЛУ включает и логическое устройство, предназначенное для операций, при осуществлении которых отсутствует перенос

- 25. Системы команд и соответствующие классы процессоров. Основные команды ЭВМ классифицируются: по функциям (по выполняемым операциям), направлению

- 26. Если же нужно дополнительное обращение к памяти, то МП переходит ко второму машинному циклу, который также

- 27. CISC (CompleteInstructionSetComputer) – традиционная архитектура, в которой ЦП использует микропрограммы для выполнения полного набора команд микропроцессора.

- 28. Процессор MISC – процессор, работающий с минимальным набором длинных команд. Увеличение разрядности процессоров привело к идее

- 30. Скачать презентацию

Слайд 2Алгебра логики и логические элементы. Для описания логики функционирования аппаратных и программных

Алгебра логики и логические элементы. Для описания логики функционирования аппаратных и программных

Слайд 3Прежде всего булева алгебра была использована для преобразования релейно- контактных схем. Если

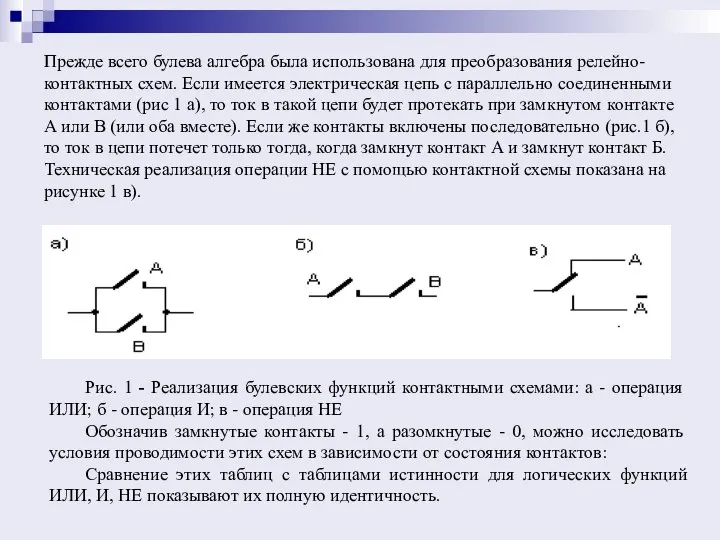

Прежде всего булева алгебра была использована для преобразования релейно- контактных схем. Если

Рис. 1 - Реализация булевских функций контактными схемами: а - операция ИЛИ; б - операция И; в - операция НЕ

Обозначив замкнутые контакты - 1, а разомкнутые - 0, можно исследовать условия проводимости этих схем в зависимости от состояния контактов:

Сравнение этих таблиц с таблицами истинности для логических функций ИЛИ, И, НЕ показывают их полную идентичность.

Слайд 4Техническое устройство, реализующее логическую функцию, может рассматриваться просто как логический элемент, внутренняя

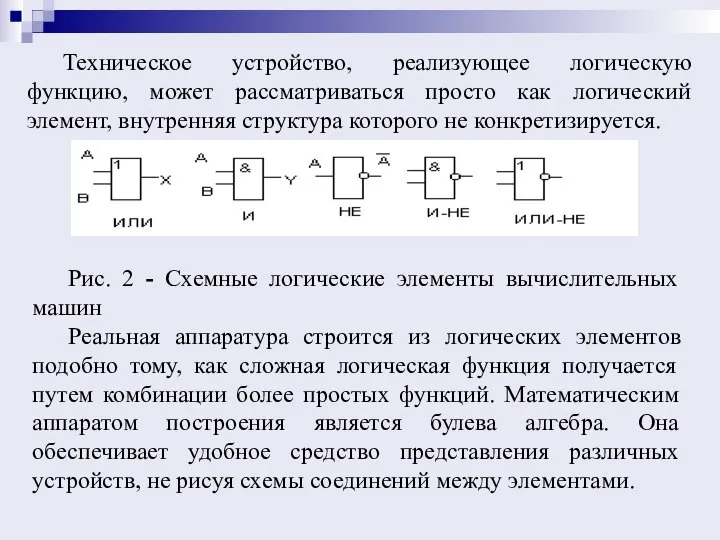

Техническое устройство, реализующее логическую функцию, может рассматриваться просто как логический элемент, внутренняя

Рис. 2 - Схемные логические элементы вычислительных машин

Реальная аппаратура строится из логических элементов подобно тому, как сложная логическая функция получается путем комбинации более простых функций. Математическим аппаратом построения является булева алгебра. Она обеспечивает удобное средство представления различных устройств, не рисуя схемы соединений между элементами.

Слайд 5Логические схемы НЕ обычно реализуются на транзисторах, которые не только инвертируют входной

Логические схемы НЕ обычно реализуются на транзисторах, которые не только инвертируют входной

Слайд 6Триггер - электронная схема, широко применяемая в регистрах компьютера для запоминания одного

Триггер - электронная схема, широко применяемая в регистрах компьютера для запоминания одного

Рис. 4-RS-триггер

Интегральные схемы, реализующие операции И-НЕ и ИЛИ-НЕ, называют базовыми элементами микроэлектроники.

Слайд 7Основные параметры логических элементов.

Логические элементы характеризуются многими параметрами. Среди них основными

Основные параметры логических элементов.

Логические элементы характеризуются многими параметрами. Среди них основными

коэффициент объединения по входу определяет число входов элемента, предназначенных для подачи логических переменных. Элемент с большим числом входов имеет более широкие функциональные возможности.

Нагрузочная способность (коэффициент разветвления по выходу) определяет число входов аналогичных элементов, которое может быть подключено к выводу данного элемента. Чем выше коэффициент, тем меньше число элементов может потребоваться при построении цифрового устройства.

Быстродействие является одним из важнейших его параметров. Оценивается задержкой распространения сигнала от входа к выходу элемента.

Помехоустойчивость определяется максимальным значением помехи, не вызывающей нарушения работы элемента.

Слайд 8Узлы компьютера. Построение компьютера ведется по следующей цепочке: элементы -» узлы -»

Узлы компьютера. Построение компьютера ведется по следующей цепочке: элементы -» узлы -»

Узел - это совокупность функционально связанных между собой элементов. Узлами ЭВМ являются стандартизированные наборы логических элементов, из которых, как из «кирпичиков», набираются схемы, входящие в состав микропроцессоров, блоков памяти, контроллеров внешних устройств и пр.

По способу функционирования узлы разделяются на:

- комбинационные, или узлы, выходные сигналы которых определяются только сигналом на входе, действующим в настоящий момент времени (например, дешифратор). Выходной сигнал дешифратора зависит только от двоичного кода, поданного на вход в настоящий момент времени. Комбинационные узлы называют также автоматами без памяти;

- последовательностные (автоматы с памятью) – это узлы, выходной сигнал которых зависит не только от комбинации входных сигналов, действующих в настоящий момент времени, но и от предыдущего состояния узла (счетчик).

Среди логических узлов ЭВМ широкое распространение получили комбинационные устройства (схемы). Такой автомат в общем случае представляется в виде многополюсника, имеющего R входов m1, m2, ..., mr и l выходов k1,k2,...kl. Поступающая на вход автомата информация задается набором сигналов М (m1, m2, ..., mr)образующим входное слово. При этом в любой дискретный момент времени ti совокупность выходных сигналов – выходное слово К (k1,k2,...kl.) – полностью определяется входным словом М, поступившим в тот же момент времени. При изменении набора входных сигналов М меняется набор выходных сигналов К.

Слайд 9

Таким образом, выходные сигналы комбинационного аппарата полностью определяются входными сигналами и не

Таким образом, выходные сигналы комбинационного аппарата полностью определяются входными сигналами и не

В последовательностных устройствах (или автоматах с памятью) входной сигнал определяется не только набором символов, действующих на входах в данный момент времени, но и внутренним состоянием устройства, а последнее зависит от того, какие наборы действовали на входах во все предшествующие моменты времени в процессе работы устройства. Поэтому о них говорят, что устройства имеют память.

Узлы компьютера по своему функциональному назначению делятся на группы: регистры; дешифраторы; шифраторы; схемы сравнения кодов; электронные счетчики; сумматоры.

Слайд 10 О понятии «архитектура ЭВМ». «Архитектура ЭВМ - это наиболее общие принципы

О понятии «архитектура ЭВМ». «Архитектура ЭВМ - это наиболее общие принципы

Слайд 11.

Классическая архитектура ЭВМ и принципы фон Неймана.

Основы учения об архитектуре вычислительных машин

.

Классическая архитектура ЭВМ и принципы фон Неймана.

Основы учения об архитектуре вычислительных машин

Слайд 12Принцип адресности. Структурно основная память состоит из перенумерованных ячеек; процессору в произвольный

Принцип адресности. Структурно основная память состоит из перенумерованных ячеек; процессору в произвольный

Революционной идеей, является принцип однородности памяти «хранимой программы» и принцип программного управления. Первоначально программа задавалась путем установки перемычек на специальной коммутационной панели. Это было весьма трудоемким занятием: например, для изменения программы машины ENIAC требовалось несколько дней (в то время как собственно расчет не мог продолжаться более нескольких минут - выходили из строя лампы). Нейман первым догадался, что программа состоит из набора команд, и может также храниться в виде набора нулей и единиц, причем в той же самой памяти, что и обрабатываемые ею числа. Отсутствие принципиальной разницы между программой и данными дало возможность ЭВМ самой формировать для себя программу в соответствии с результатами вычислений. На этом принципе основаны методы трансляции – перевода текста программы с языка программирования высокого уровня на язык конкретной машины. Выборка программы из памяти осуществляется с помощью счетчика команд (СК). Этот регистр процессора последовательно увеличивает хранимый в нем адрес очередной команды на длину команды.

Слайд 13Основной алгоритм работы процессора: Начало цикла

чтение команды из памяти по адресу, записанному

Основной алгоритм работы процессора: Начало цикла

чтение команды из памяти по адресу, записанному

увеличение СК на длину прочитанной команды

выполнение прочитанной команды . Конец цикла

Так как команды программы расположены в памяти друг за другом, то тем самым организуется выборка цепочки команд из последовательно расположенных ячеек памяти. Если после выполнения команды следует перейти не к следующей, а к какой-то другой, используются команды условного или безусловного переходов (ветвления), которые заносят в счетчик команд номер ячейки памяти, содержащей следующую команду. Выборка прекращается после достижения и выполнения команды «стоп». Таким образом, процессор исполняет программу автоматически, без вмешательства человека.

Таким образом, в основу построения цифровых вычислительных машин положены принципы: - использование 2-ичной системы счисления в машинной арифметике; адресуемость памяти; хранение данных и программ в общей памяти ЭВМ. Джон фон Нейман описал состав устройств однопроцессорной ЭВМ и состав системы команд процессора. Поэтому классическую архитектуру часто называют «архитектурой фон Неймана»

Слайд 14Так как команды программы расположены в памяти друг за другом, то тем

Так как команды программы расположены в памяти друг за другом, то тем

Слайд 15Фон Нейман не только выдвинул основополагающие принципы логического устройства ЭВМ, но и

Фон Нейман не только выдвинул основополагающие принципы логического устройства ЭВМ, но и

с. 4.1 - Структура фон Неймана

Устройство управления и арифметико-логическое устройство в современных компьютерах объединены в один блок - процессор, являющийся преобразователем информации, поступающей из памяти и внешних устройств (сюда относятся выборка команд из памяти, кодирование и декодирование, выполнение различных, в том числе и арифметических, операций, согласование работы узлов компьютера).

Слайд 16Память (ЗУ) хранит информацию (данные) и программы. Запоминающее устройство у современных компьютеров

Память (ЗУ) хранит информацию (данные) и программы. Запоминающее устройство у современных компьютеров

Слайд 17В построенной по описанной схеме ЭВМ происходит последовательное считывание команд из памяти

В построенной по описанной схеме ЭВМ происходит последовательное считывание команд из памяти

Слайд 18Типы архитектур. Основные классические типы архитектур можно определить как: «звезда», иерархическая, магистральная.

Архитектура

Типы архитектур. Основные классические типы архитектур можно определить как: «звезда», иерархическая, магистральная. Архитектура

Слайд 19Периферийные устройства подключаются к аппаратуре компьютера через специальные контроллеры – устройства управления

Периферийные устройства подключаются к аппаратуре компьютера через специальные контроллеры – устройства управления

Слайд 20Процессор, структура и функционирование. Абстрактное центральное устройство.

Перечислим основные понятия и рассмотрим структуру

Процессор, структура и функционирование. Абстрактное центральное устройство. Перечислим основные понятия и рассмотрим структуру

Слайд 21Регистры – устройства, предназначенные для временного хранения данных ограниченного размера. Важной характеристикой

Регистры – устройства, предназначенные для временного хранения данных ограниченного размера. Важной характеристикой

Слайд 22Командный цикл процессора. Цикл выполнения команды может выглядеть следующим образом.

1. В соответствии

Командный цикл процессора. Цикл выполнения команды может выглядеть следующим образом. 1. В соответствии

Слайд 23Арифметико-логическое устройство (АЛУ). ArithmeticandLogicalUnit (ALU) - компонента процессора, которая осуществляет арифметические и

Арифметико-логическое устройство (АЛУ). ArithmeticandLogicalUnit (ALU) - компонента процессора, которая осуществляет арифметические и

Слайд 24Помимо арифметического устройства, АЛУ включает и логическое устройство, предназначенное для операций, при

Помимо арифметического устройства, АЛУ включает и логическое устройство, предназначенное для операций, при

Слайд 25Системы команд и соответствующие классы процессоров. Основные команды ЭВМ классифицируются: по функциям

Системы команд и соответствующие классы процессоров. Основные команды ЭВМ классифицируются: по функциям

Слайд 26Если же нужно дополнительное обращение к памяти, то МП переходит ко второму

Если же нужно дополнительное обращение к памяти, то МП переходит ко второму

Слайд 27CISC (CompleteInstructionSetComputer) – традиционная архитектура, в которой ЦП использует микропрограммы для выполнения

CISC (CompleteInstructionSetComputer) – традиционная архитектура, в которой ЦП использует микропрограммы для выполнения

Слайд 28Процессор MISC – процессор, работающий с минимальным набором длинных команд. Увеличение разрядности

Процессор MISC – процессор, работающий с минимальным набором длинных команд. Увеличение разрядности

Cпособ переработки твердых бытовых отходов

Cпособ переработки твердых бытовых отходов Видеоуроки

Видеоуроки Визуал

Визуал “ Прорывные проекты АО “ Национальная компания “КазМунайГаз”

“ Прорывные проекты АО “ Национальная компания “КазМунайГаз” SenseMakers. Problems plaguing business conflicts

SenseMakers. Problems plaguing business conflicts Портрет типичного итальянца

Портрет типичного итальянца 8 Марта

8 Марта Фенилкетонурия

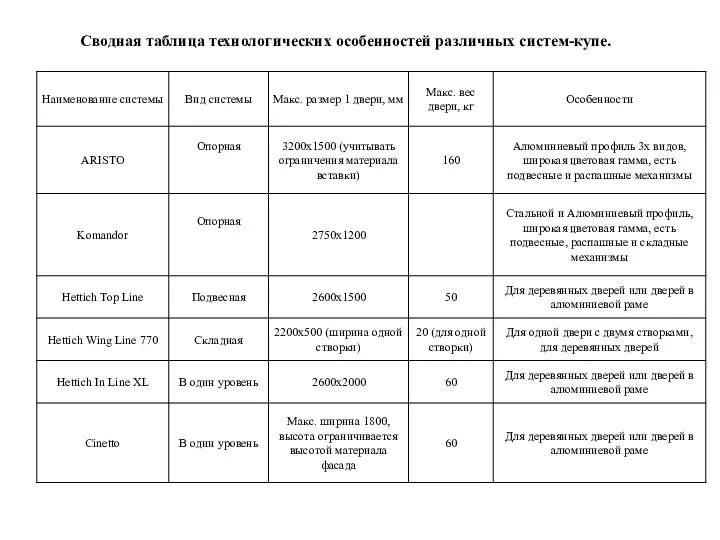

Фенилкетонурия Сводная таблица технологических особенностей различных систем-купе. Наименование системы

Сводная таблица технологических особенностей различных систем-купе. Наименование системы ОСНОВЫ ОБЩЕЙ ТЕХНОЛОГИИ МЕТАЛЛОВ

ОСНОВЫ ОБЩЕЙ ТЕХНОЛОГИИ МЕТАЛЛОВ УРОВНИ ОРГАНИЗАЦИИ ПРОФИЛАКТИЧЕСКОЙ ДЕЯТЕЛЬНОСТИ

УРОВНИ ОРГАНИЗАЦИИ ПРОФИЛАКТИЧЕСКОЙ ДЕЯТЕЛЬНОСТИ Экскурсия в порт города Дуйсбурга

Экскурсия в порт города Дуйсбурга Живопись раннего возрождения. Художественные школы

Живопись раннего возрождения. Художественные школы Презентация на тему: Тихая охота

Презентация на тему: Тихая охота Политика

Политика  CPI - cases

CPI - cases Автомобили скорой медицинской помощи

Автомобили скорой медицинской помощи Аутстаффинг персонала

Аутстаффинг персонала Галицко-Волынское княжество

Галицко-Волынское княжество El proceso de redacción: Planificación del esquema numérico del texto argumentativo

El proceso de redacción: Planificación del esquema numérico del texto argumentativo Современные страховые продукты. Страховая компания Ингосстрах

Современные страховые продукты. Страховая компания Ингосстрах Применение солей в быту

Применение солей в быту Действие уголовного закона во времени и в пространстве

Действие уголовного закона во времени и в пространстве Русский по воскресеньям. Занятие 2. Диктант

Русский по воскресеньям. Занятие 2. Диктант Гандбол

Гандбол Новые монологи из открытого банка. ОГЭ Устная часть

Новые монологи из открытого банка. ОГЭ Устная часть Государство и его признаки

Государство и его признаки Гурбанова О.Н. РНБ. МБА и ДД и преобразование нашего мира

Гурбанова О.Н. РНБ. МБА и ДД и преобразование нашего мира