Содержание

- 2. *The International Technology Roadmap for Semiconductors, edn. 2007 Прогнозируемые и достигнутые параметры логических элементов

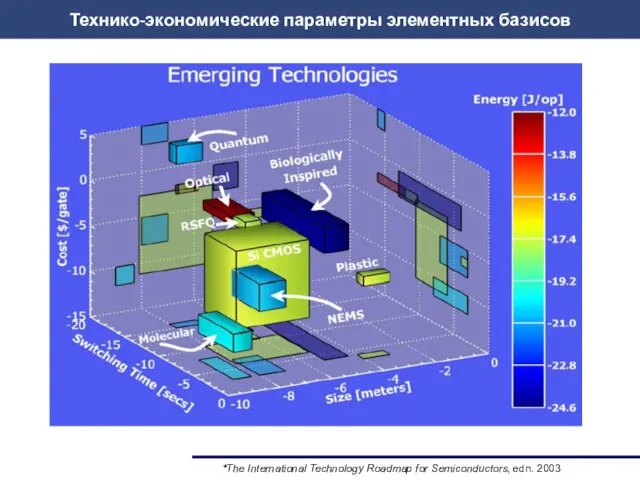

- 3. *The International Technology Roadmap for Semiconductors, edn. 2003 Технико-экономические параметры элементных базисов

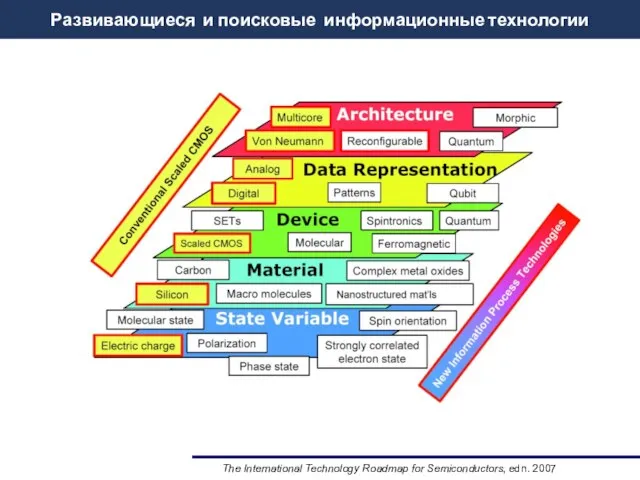

- 4. The International Technology Roadmap for Semiconductors, edn. 2007 Развивающиеся и поисковые информационные технологии

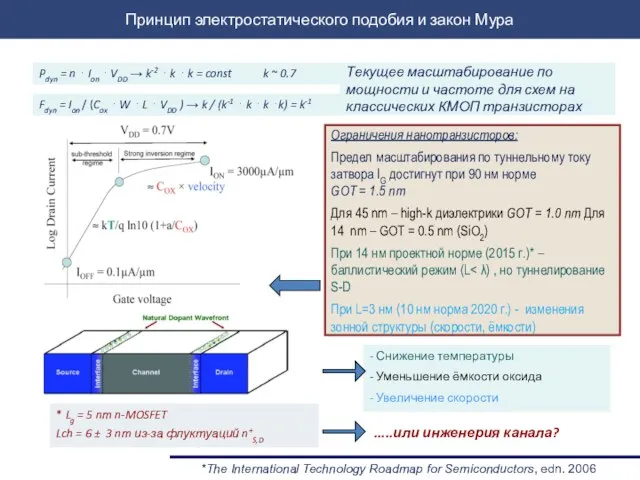

- 5. *The International Technology Roadmap for Semiconductors, edn. 2006 * Lg = 5 nm n-MOSFET Lch =

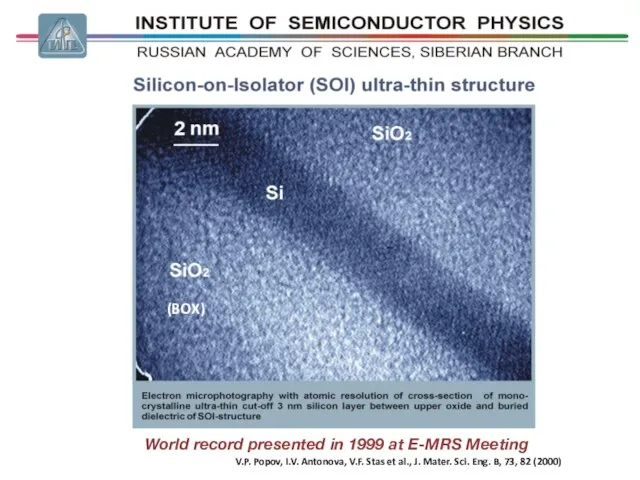

- 6. World record presented in 1999 at E-MRS Meeting V.P. Popov, I.V. Antonova, V.F. Stas et al.,

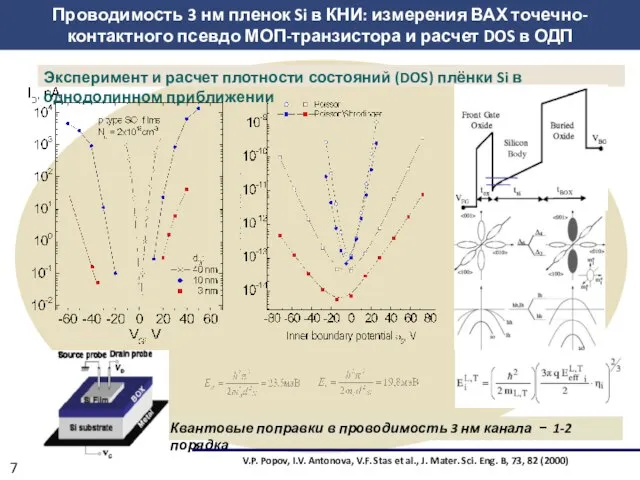

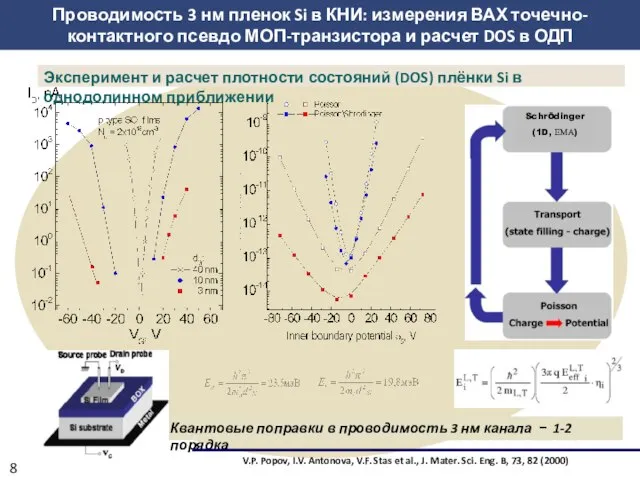

- 7. V.P. Popov, I.V. Antonova, V.F. Stas et al., J. Mater. Sci. Eng. B, 73, 82 (2000)

- 8. V.P. Popov, I.V. Antonova, V.F. Stas et al., J. Mater. Sci. Eng. B, 73, 82 (2000)

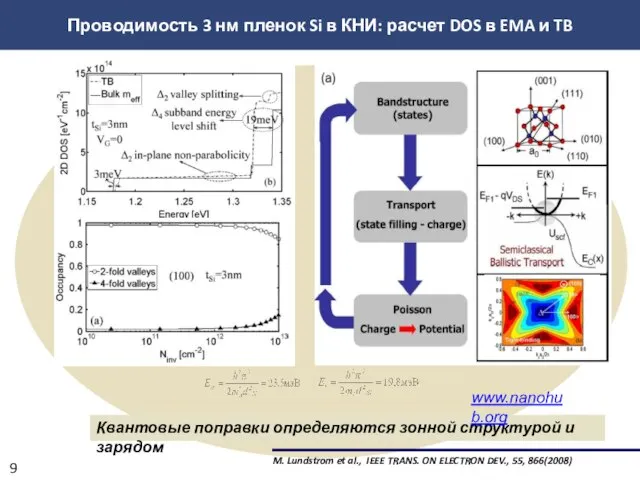

- 9. M. Lundstrom et al., IEEE TRANS. ON ELECTRON DEV., 55, 866(2008) Квантовые поправки определяются зонной структурой

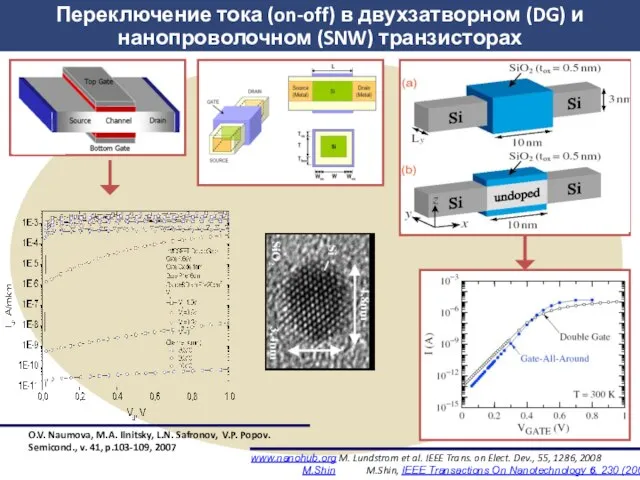

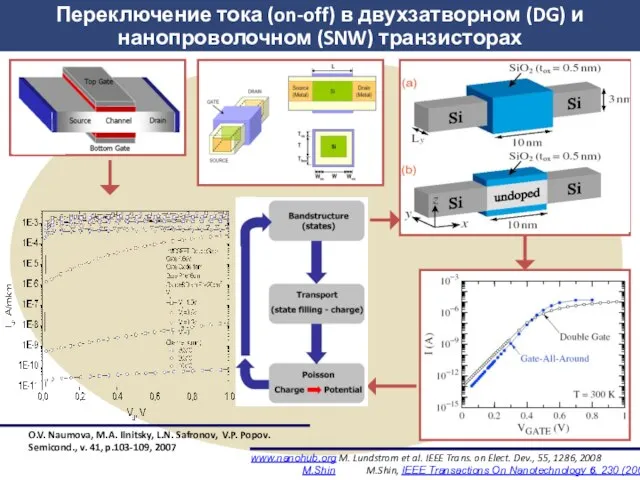

- 10. www.nanohub.org M. Lundstrom et al. IEEE Trans. on Elect. Dev., 55, 1286, 2008 M.Shin M.Shin, IEEE

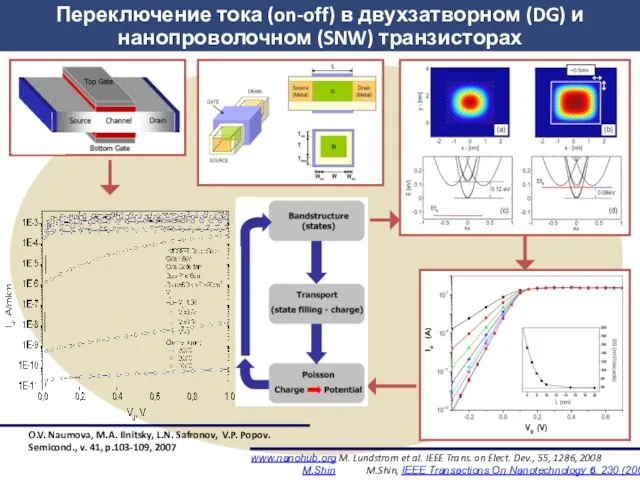

- 11. www.nanohub.org M. Lundstrom et al. IEEE Trans. on Elect. Dev., 55, 1286, 2008 M.Shin M.Shin, IEEE

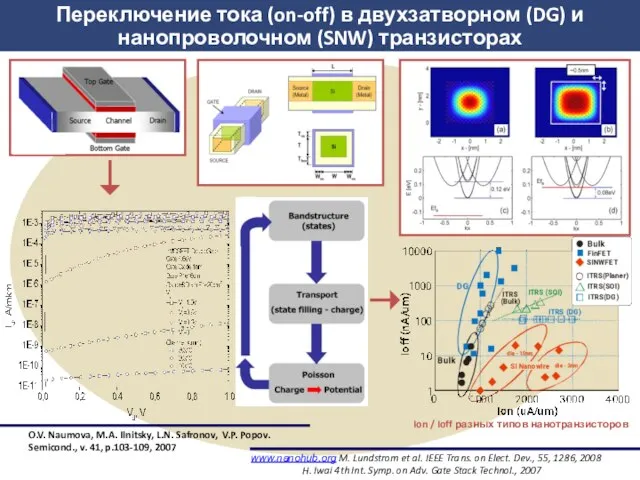

- 12. www.nanohub.org M. Lundstrom et al. IEEE Trans. on Elect. Dev., 55, 1286, 2008 M.Shin M.Shin, IEEE

- 13. www.nanohub.org M. Lundstrom et al. IEEE Trans. on Elect. Dev., 55, 1286, 2008 H. Iwai 4th

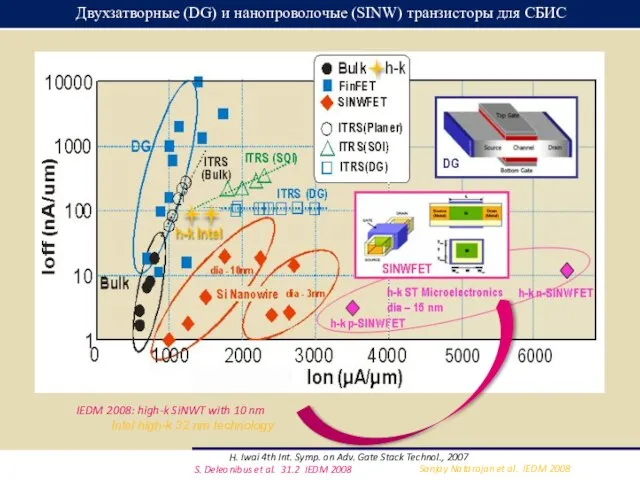

- 14. Intel high-k 32 nm technology with drive currents of 1550 µA/ µm at 100 nA off-current

- 15. Intel high-k 32 nm technology with drive currents of 1550 µA/ µm at 100 nA off-current

- 16. *Совещание по развитию электронной промышленности РФ, сент. 2008 Техпроцессы системообразующей ЭКБ микроэлектроники 187 млрд руб XYZ

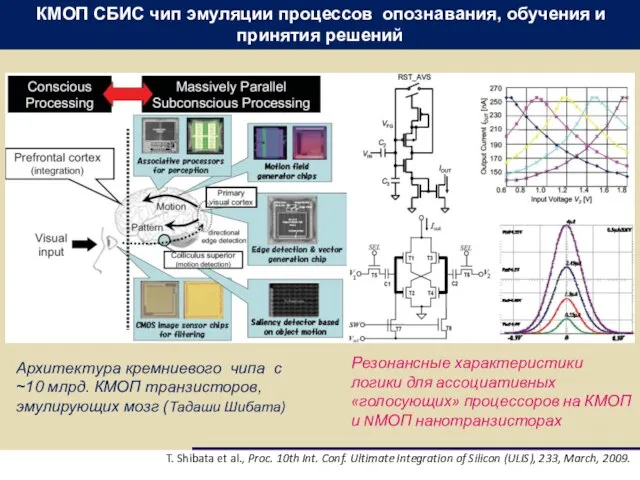

- 17. СБИС СК ПЗУ СБИС МП PCI ОЗУ СБИС ИК Мультиплексный канал п/п п/п RS232 Дискретные сигналы

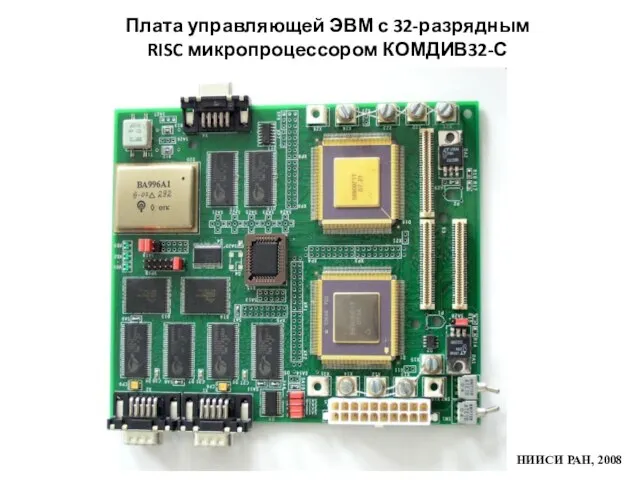

- 18. Плата управляющей ЭВМ с 32-разрядным RISC микропроцессором КОМДИВ32-С НИИСИ РАН, 2008

- 19. 0.18 мкм технология ST Microelectronics 2007г.

- 20. Планы технологического развития «НИИМЭ и Микрон» 2005 г. мкм 2007 г. 2008 г. 2009 г. Фабрика

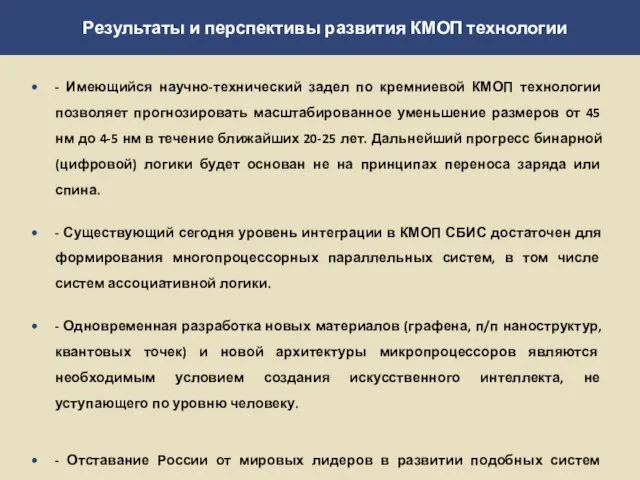

- 21. Результаты и перспективы развития КМОП технологии - Имеющийся научно-технический задел по кремниевой КМОП технологии позволяет прогнозировать

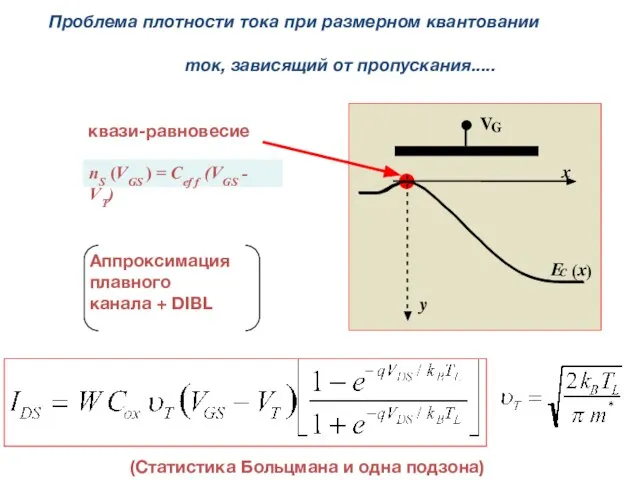

- 22. ток, зависящий от пропускания..... V G x y nS (VGS ) = Cef f (VGS -

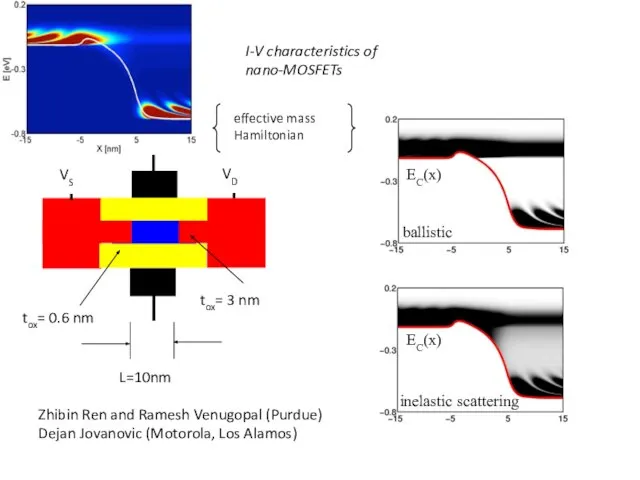

- 23. I-V characteristics of nano-MOSFETs effective mass Hamiltonian VG VD VS L=10nm tox= 0.6 nm tox= 3

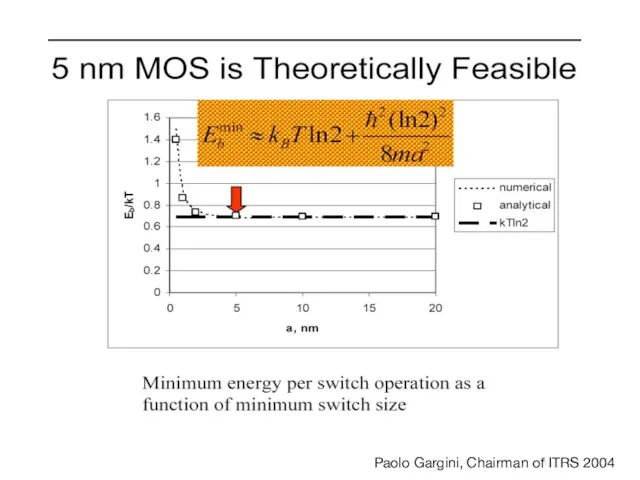

- 24. Paolo Gargini, Chairman of ITRS 2004

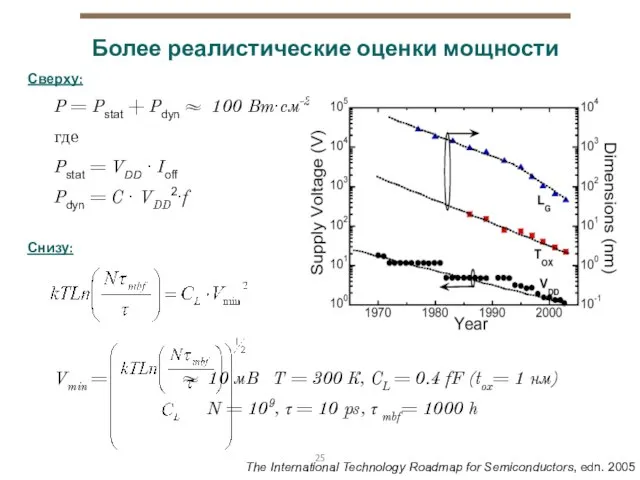

- 25. The International Technology Roadmap for Semiconductors, edn. 2005 P = Pstat + Pdyn ≈ 100 Вт·см-2

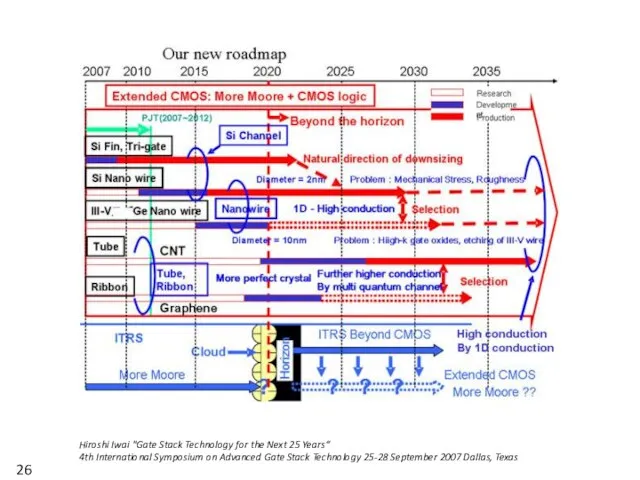

- 26. Hiroshi Iwai "Gate Stack Technology for the Next 25 Years“ 4th International Symposium on Advanced Gate

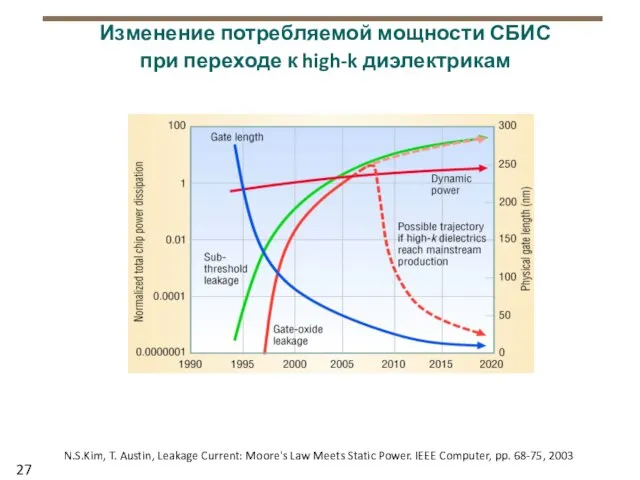

- 27. Изменение потребляемой мощности СБИС при переходе к high-k диэлектрикам N.S.Kim, T. Austin, Leakage Current: Moore's Law

- 29. Скачать презентацию

Улучшая качество повседневной жизни В нашем беспокойном, стрессовом и суетливом мире потребители уделяют огромное внимание качес

Улучшая качество повседневной жизни В нашем беспокойном, стрессовом и суетливом мире потребители уделяют огромное внимание качес Основы рекламной деятельности

Основы рекламной деятельности Марафон ГТО

Марафон ГТО Модуль II “Управление маркетинговой деятельностью”

Модуль II “Управление маркетинговой деятельностью” Рекламная кампания для препарата «Амизон» «ГРИПП. Не дорисовал рекламу»

Рекламная кампания для препарата «Амизон» «ГРИПП. Не дорисовал рекламу» Бонусная программа Приведи друга-2019

Бонусная программа Приведи друга-2019 Практические приемы работы по формированию гендерной идентичности

Практические приемы работы по формированию гендерной идентичности Правовое государство

Правовое государство Пиксельное окрашивание волос

Пиксельное окрашивание волос примеры теплопередачи в быту и технике

примеры теплопередачи в быту и технике Хлеб – всему голова

Хлеб – всему голова Презентация на тему Биометрические технологии

Презентация на тему Биометрические технологии  Русские пряники. Приготовление печатного пряника

Русские пряники. Приготовление печатного пряника Пятый поток

Пятый поток Circassian ornament черкесский адыгский орнамент Circassian motive Çerkes sebebi тхыпхъэ тхыпхьэ

Circassian ornament черкесский адыгский орнамент Circassian motive Çerkes sebebi тхыпхъэ тхыпхьэ Коварные Е

Коварные Е Отчет о выполнении работ по благоустройству общественной территории

Отчет о выполнении работ по благоустройству общественной территории Куб эмоций как средство создания условий для положительного психологического комфорта между воспитанниками ДОУ

Куб эмоций как средство создания условий для положительного психологического комфорта между воспитанниками ДОУ Мама-солнышко мое

Мама-солнышко мое Африка 10 класс

Африка 10 класс Современный урок русского языка

Современный урок русского языка Рекомендации родителям по укреплению здоровья детей

Рекомендации родителям по укреплению здоровья детей Изображение характера животных на рисунке (2 класс)

Изображение характера животных на рисунке (2 класс) Пушкин Песнь о вещем Олеге

Пушкин Песнь о вещем Олеге Что такое FOHOW +? Сетевой маркетинг

Что такое FOHOW +? Сетевой маркетинг Магнитное поле в веществе

Магнитное поле в веществе Стипендиальное обеспечение

Стипендиальное обеспечение  Профилактика суицидального поведения у подростков

Профилактика суицидального поведения у подростков