Содержание

- 2. use without knowledge of system of commands is absolutely impossible, after all the Assembler language represents

- 3. and where to place result (if it is necessary). The code of command can borrow from

- 4. Definition of a position of operands is made by a command code. And there are different

- 5. can consist in adding number 6 to contents of any internal register of the processor. This

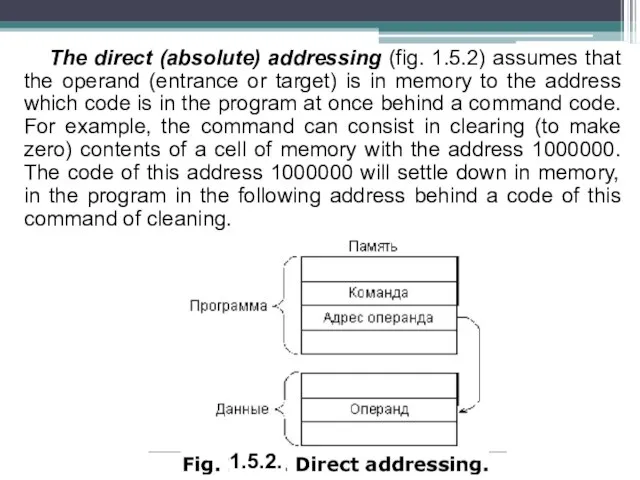

- 6. The direct (absolute) addressing (fig. 1.5.2) assumes that the operand (entrance or target) is in memory

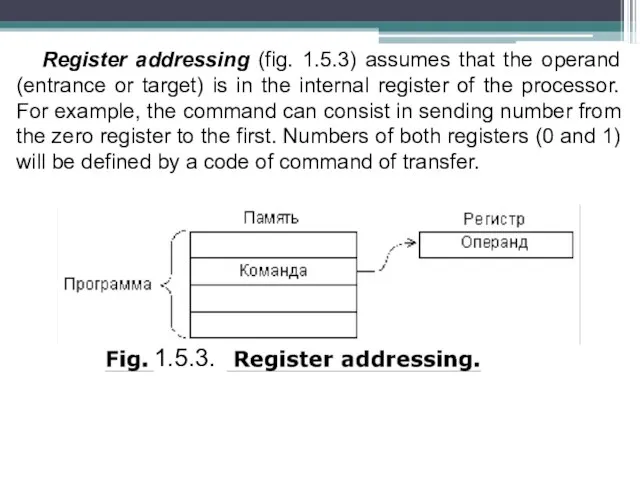

- 7. Register addressing (fig. 1.5.3) assumes that the operand (entrance or target) is in the internal register

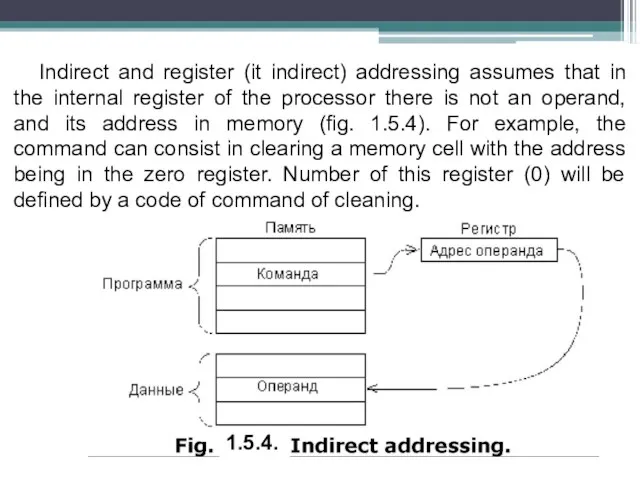

- 8. Indirect and register (it indirect) addressing assumes that in the internal register of the processor there

- 9. Less often two more methods of addressing meet. Autoincremental addressing is very close to indirect addressing,

- 10. From other widespread methods of addressing it is possible to mention index methods which assume for

- 11. 2.3.1.2. Memory segmentation Speaking about addressing, it is impossible to bypass a question of the memory

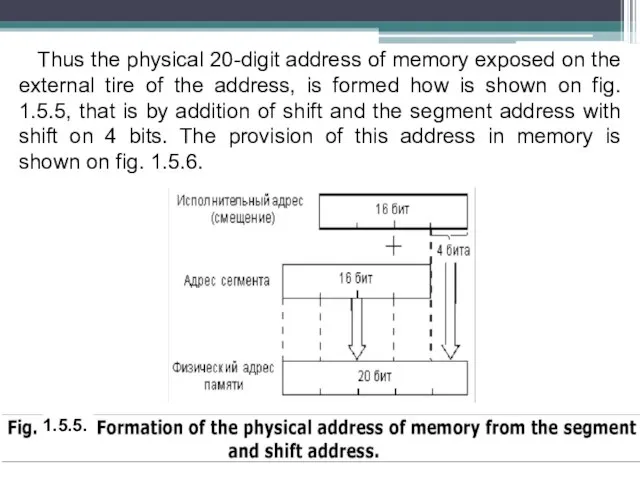

- 12. Thus the physical 20-digit address of memory exposed on the external tire of the address, is

- 13. 1.5.6.

- 14. The segment can begin only on 16-byte limit of memory (as the address of the beginning

- 15. 1.5.7.

- 16. The base (initial) address of segments, and the codes of selectors defining addresses in memory on

- 17. 1.5.8.

- 18. The memory address (the physical address) is calculated in three stages. At first the so-called effective

- 19. Then the special block of segmentation calculates the 32-bit linear address which represents the sum of

- 20. 2.3.1.3. Addressing of bytes and words Many processors having word length 16 or 32, are capable

- 21. 1.5.9.

- 22. At the appeal to the whole word (with contents 2А5Е) the processor exposes the address 23420.

- 23. 2.3.2. Processor registers As it was already mentioned, internal registers of the processor represent scratch-pad memory

- 24. In the 16-digit MC68000 processor of Motorola firm there were 19 registers: 16-digit register of a

- 25. • the register AX — multiplication, division, an exchange with input-output devices (input and output command);

- 26. 1.5.10.

- 27. In principle, all these segments can and be blocked for optimum use of space of memory.

- 28. The last register FLAGS — is the register of a condition of the processor (PSW). From

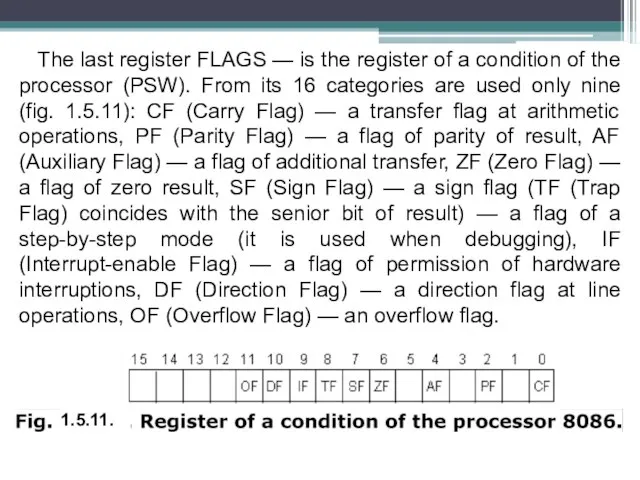

- 29. Bits of the register of a condition are established or cleared depending on result of execution

- 30. accumulator as he surely participates in multiplication and division commands, and also only through it it

- 32. Скачать презентацию

Слайд 2use without knowledge of system of commands is absolutely impossible, after all

use without knowledge of system of commands is absolutely impossible, after all

For this reason in this chapter we will consider the main types of commands which are available for the majority of processors, and features of their application.

Each command, chosen (read) of memory the processor, defines algorithm of behavior of the processor on the next some steps. The code of command speaks about what operation should be executed to the processor and with what operands (that is codes of data) where to take initial information for command execution

Слайд 3and where to place result (if it is necessary). The code of

and where to place result (if it is necessary). The code of

2.3.1. Addressing of operands

The most part of commands of the processor works with codes of data (operands). One commands demand entrance operands (one or two), others give out target operands (one operand is more often). Entrance operands are called still as operands sources, and days off are called as operands receivers. All these codes of operands (entrance and target) should settle down somewhere. They can be in internal registers of the processor (the most convenient and fast option). They can settle down in system memory (the most widespread option). At last, they can be in input-output devices (the most exceptional case).

Слайд 4Definition of a position of operands is made by a command code.

Definition of a position of operands is made by a command code.

2.3.1.1. Addressing methods

The quantity of methods of addressing in various processors can be from 4 to 16. Let's consider a little typical addressing methods of the operands used now in the majority of microprocessors.

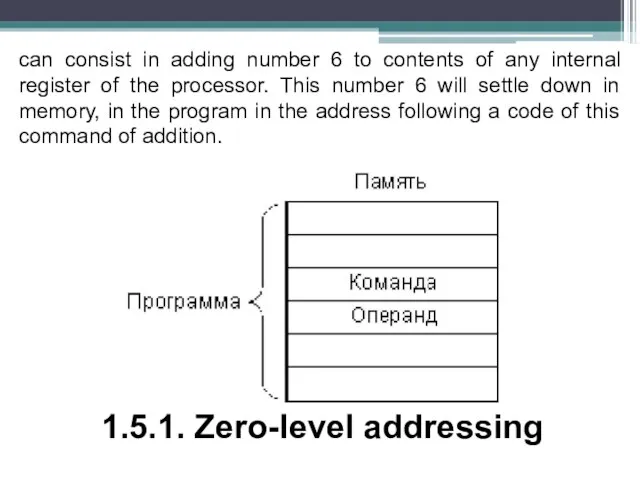

Zero-level addressing (fig. 1.5.1) assumes that the operand (entrance) is in memory directly behind a command code. The operand usually represents a constant which should be sent somewhere, to something to add etc. For example, the command

Слайд 5can consist in adding number 6 to contents of any internal register

can consist in adding number 6 to contents of any internal register

1.5.1. Zero-level addressing

Слайд 6The direct (absolute) addressing (fig. 1.5.2) assumes that the operand (entrance or

The direct (absolute) addressing (fig. 1.5.2) assumes that the operand (entrance or

1.5.2.

Слайд 7Register addressing (fig. 1.5.3) assumes that the operand (entrance or target) is

Register addressing (fig. 1.5.3) assumes that the operand (entrance or target) is

1.5.3.

Слайд 8Indirect and register (it indirect) addressing assumes that in the internal register

Indirect and register (it indirect) addressing assumes that in the internal register

1.5.4.

Слайд 9Less often two more methods of addressing meet.

Autoincremental addressing is very close

Less often two more methods of addressing meet.

Autoincremental addressing is very close

Autodecremental addressing works probably on autoincremental, but only contents of the chosen register decrease by unit or on two before command execution. This addressing is also convenient when processing data files. Sharing of autoincremental and autodecremental addressings allows to organize memory of push-down type.

Слайд 10From other widespread methods of addressing it is possible to mention index

From other widespread methods of addressing it is possible to mention index

Let's note that the choice of this or that method of addressing substantially defines time of command execution. The fastest addressing — is register as she doesn't demand additional cycles of an exchange on the highway. If addressing demands the appeal to memory, time of command execution will increase at the expense of duration of necessary cycles of the appeal to memory. It is clear that the more internal registers at the processor, the more often and more freely it is possible to apply register addressing, and with that the system as a whole quicker will work.

Слайд 112.3.1.2. Memory segmentation

Speaking about addressing, it is impossible to bypass a question

2.3.1.2. Memory segmentation

Speaking about addressing, it is impossible to bypass a question

In the Intel 8086 processor segmentation of memory is organized as follows.

All memory of system is represented not in the form of continuous space, and in the form of several pieces — given size segments (on 64 Kb) which situation in space of memory can be changed a program way.

For storage of codes of addresses of memory separate registers, and pairs of registers are used not:

• the segment register defines the address of the beginning of a segment (that is the provision of a segment in memory);

• the index register (the shift register) defines the provision of the working address in a segment.

Слайд 12Thus the physical 20-digit address of memory exposed on the external tire

Thus the physical 20-digit address of memory exposed on the external tire

1.5.5.

Слайд 131.5.6.

1.5.6.

Слайд 14The segment can begin only on 16-byte limit of memory (as the

The segment can begin only on 16-byte limit of memory (as the

Let's note that segmentation introduction, first of all, is connected with that internal registers of the processor 16-digit, and the physical address of memory 20-digit (the 16-digit address allows to use memory only in 64 Kb that is obviously not enough). In the MC68000 processor which has appeared at the same time of Motorola firm internal registers 32-bit therefore there problems of segmentation of memory don't arise.

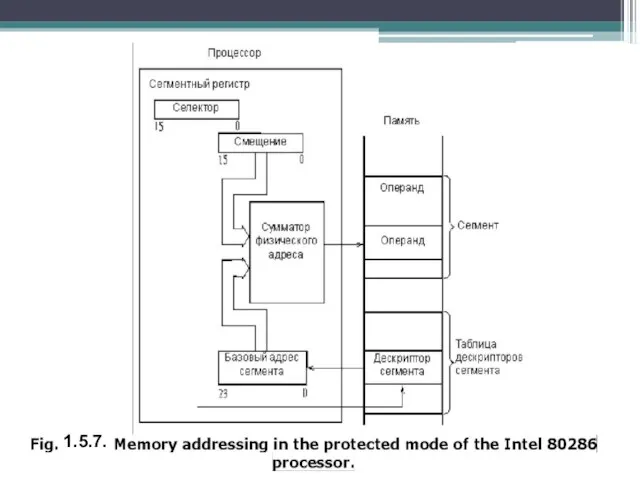

More difficult methods of segmentation of memory are applied also. For example, in the Intel 80286 processor in the so-called protected mode the address of memory is calculated according to fig. 1.5.7.

Слайд 151.5.7.

1.5.7.

Слайд 16The base (initial) address of segments, and the codes of selectors defining

The base (initial) address of segments, and the codes of selectors defining

Thus, on the adder calculating the physical address of memory, contents of the segment register, as in the previous case, and the base address of a segment from the table of descriptors move not.

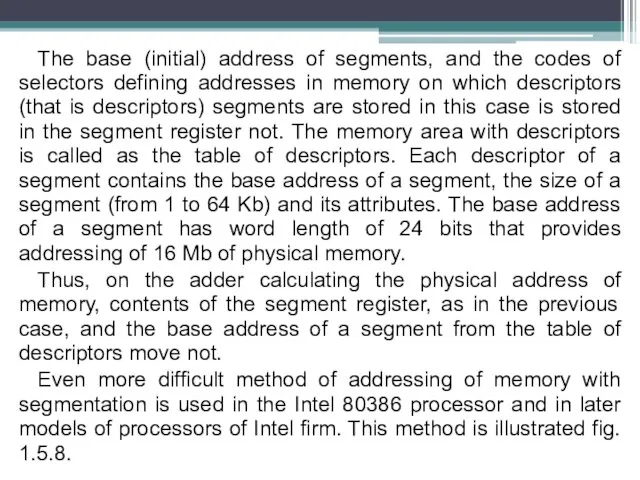

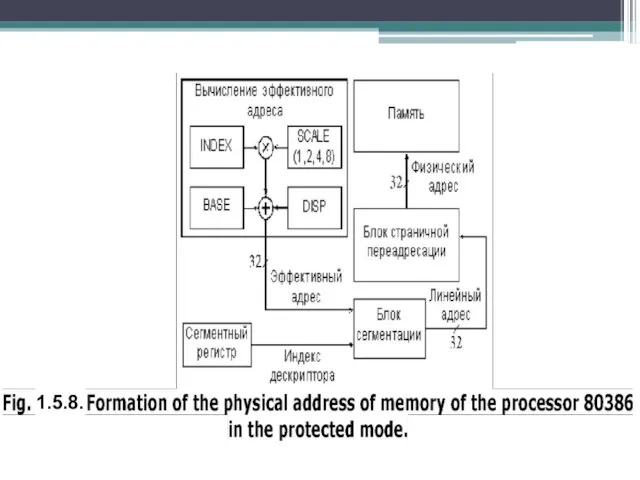

Even more difficult method of addressing of memory with segmentation is used in the Intel 80386 processor and in later models of processors of Intel firm. This method is illustrated fig. 1.5.8.

Слайд 171.5.8.

1.5.8.

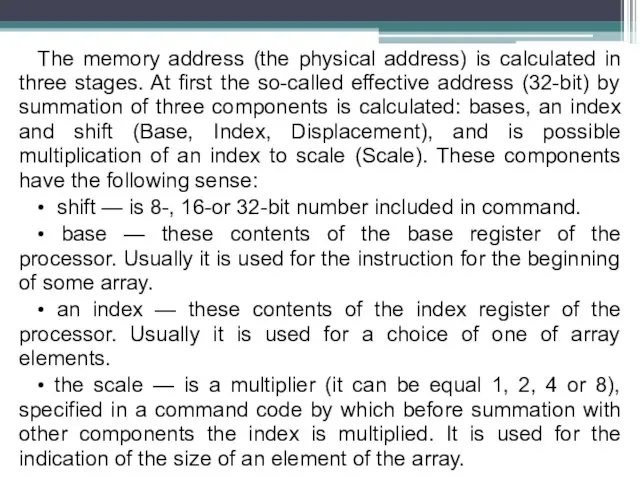

Слайд 18The memory address (the physical address) is calculated in three stages. At

The memory address (the physical address) is calculated in three stages. At

• shift — is 8-, 16-or 32-bit number included in command.

• base — these contents of the base register of the processor. Usually it is used for the instruction for the beginning of some array.

• an index — these contents of the index register of the processor. Usually it is used for a choice of one of array elements.

• the scale — is a multiplier (it can be equal 1, 2, 4 or 8), specified in a command code by which before summation with other components the index is multiplied. It is used for the indication of the size of an element of the array.

Слайд 19Then the special block of segmentation calculates the 32-bit linear address which

Then the special block of segmentation calculates the 32-bit linear address which

In any case segmentation allows to allocate in memory one or several segments for data and one or several segments for programs. Transition from one segment to another is reduced only to change of contents of the segment register. Sometimes it happens very conveniently. But for the programmer to work with the segmented memory it is usually more difficult, than with the continuous, not segmented memory as it is necessary to watch borders of segments, behind their description, switching etc.

Слайд 202.3.1.3. Addressing of bytes and words

Many processors having word length 16 or

2.3.1.3. Addressing of bytes and words

Many processors having word length 16 or

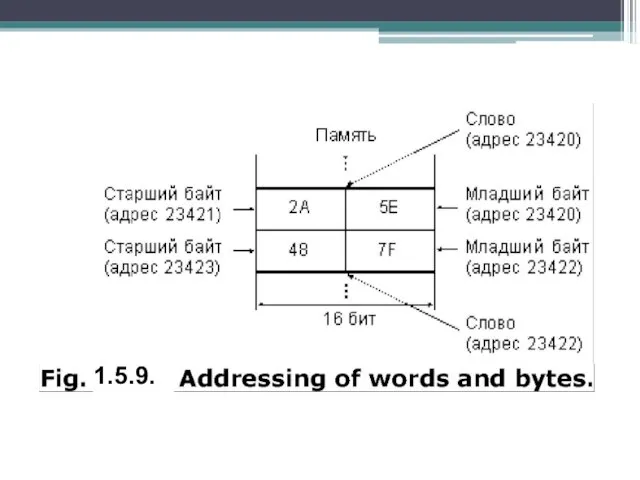

So, in case of 16-digit processors all words in memory (16-digit) have even addresses. And the bytes entering into these words, can have both even addresses, and odd.

For example, let the 16-digit cell of memory has the address 23420, and the code 2А5Е is stored in it (fig. 1.5.9).

Слайд 211.5.9.

1.5.9.

Слайд 22At the appeal to the whole word (with contents 2А5Е) the processor

At the appeal to the whole word (with contents 2А5Е) the processor

For distinction of byte and nice cycles of an exchange for highways in the tire of management the special signal of a byte exchange is provided. For work with bytes special commands are entered into system of commands of the processor or methods of byte addressing are provided.

Слайд 232.3.2. Processor registers

As it was already mentioned, internal registers of the processor

2.3.2. Processor registers

As it was already mentioned, internal registers of the processor

For example, in the 16-digit T-11 processor of DEC firm there were 8 registers of general purpose (RON) and one register of a condition. All registers had on 16 categories. From registers of general purpose one was taken away under the counter of commands, another — under the stack index. All other registers of general purpose are completely interchangeable, that is have universal appointment, can store both data, and addresses (indexes), indexes etc. The most admissible memory size for this processor made 64 Kb (the memory address 16-digit).

Слайд 24In the 16-digit MC68000 processor of Motorola firm there were 19 registers:

In the 16-digit MC68000 processor of Motorola firm there were 19 registers:

In the 16-digit Intel 8086 processor which base in the line of the processors used in personal computers, became realized essentially other approach. Each register of this processor has the special appointment, and replace each other registers can only partially or can't in general. Let's stop on features of this processor in more detail.

The processor 8086 has 14 registers word length on 16 bits. From them four registers (AX, BX, CX, DX) — is registers of data, each of which besides storage of operands and results of operations has also the specific appointment:

Слайд 25• the register AX — multiplication, division, an exchange with input-output devices

• the register AX — multiplication, division, an exchange with input-output devices

• the register BX — the base register in address calculations;

• the register CX — the counter of cycles;

• the register DX — definition of the address of input-output.

For registers of data there is a possibility of separate use of both bytes (for example, for the register AX they have AL designations the-junior byte and AH — the senior byte).

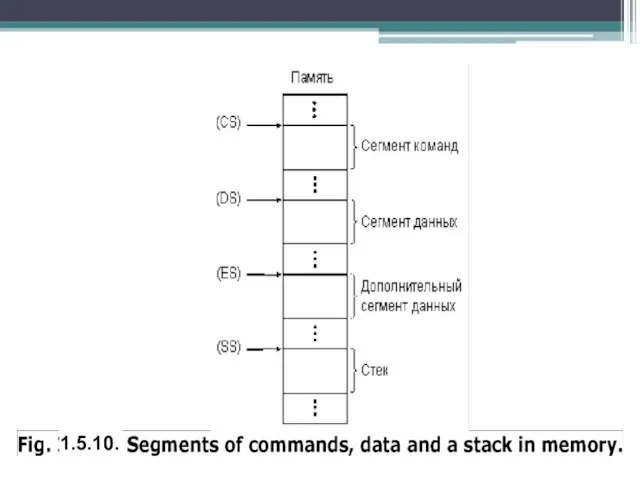

The following four internal registers of the processor — it is segment registers, each of which defines the provision of one of working segments (fig. 1.5.10):

• the register CS (Code Segment) corresponds to a segment of the commands executed at present;

• the register DS (Data Segment) corresponds to a segment of data with which the processor works;

• the register ES (Extra Segment) corresponds to an additional segment of data;

• the register SS (Stack Segment) corresponds to a stack segment.

Слайд 261.5.10.

1.5.10.

Слайд 27In principle, all these segments can and be blocked for optimum use

In principle, all these segments can and be blocked for optimum use

The following five registers of the processor (SP — Stack Pointer, BP — Base Pointer, SI — Source Index, DI — Destination Index, IP — Instruction Pointer) serve as indexes (that is define shift within a segment). For example, the counter of commands of the processor is formed by pair of registers CS and IP, and the stack index — pair of registers SP and SS. The registers SI, are used by DI in line operations, that is at serial processing of several cells of memory by one command.

Слайд 28The last register FLAGS — is the register of a condition of

The last register FLAGS — is the register of a condition of

1.5.11.

Слайд 29Bits of the register of a condition are established or cleared depending

Bits of the register of a condition are established or cleared depending

In many processors the special register called by the accumulator (that is with the store) is allocated. Thus, as a rule, only this register accumulator can participate in all operations, only through it interaction with input-output devices can be made. Sometimes in it the result of any executed command (in this case speak even about "storage" architecture of the processor) is located. For example, in the processor 8086 AH it is possible to consider the register of data as a peculiar

Слайд 30accumulator as he surely participates in multiplication and division commands, and also

accumulator as he surely participates in multiplication and division commands, and also

Ада Якушева

Ада Якушева Неотложная терапия анафилактическихреакций

Неотложная терапия анафилактическихреакций Управлениепроблемными активами

Управлениепроблемными активами Несоответствие уровня развития коммуникативной компетенции учащихся с требованиями ФГОС

Несоответствие уровня развития коммуникативной компетенции учащихся с требованиями ФГОС Основные образцы вооружения ВС

Основные образцы вооружения ВС Презентация на тему Основные формулы для синуса и косинуса

Презентация на тему Основные формулы для синуса и косинуса Координация работ по реформе технического регулирования и стандартизации в нефтегазовом комплексеМежотраслевым советом по техн

Координация работ по реформе технического регулирования и стандартизации в нефтегазовом комплексеМежотраслевым советом по техн «Правовое воспитание детей дошкольного возраста»

«Правовое воспитание детей дошкольного возраста» Потребности в кадрах для инновационной деятельности

Потребности в кадрах для инновационной деятельности «ДОСТУПНОСТЬ»

«ДОСТУПНОСТЬ» Санкт-Петербургский Офис Представительство Европейской Коммиссии в России

Санкт-Петербургский Офис Представительство Европейской Коммиссии в России Туристические маршруты Красноярского края

Туристические маршруты Красноярского края Договор перевозки Договор перевозки – это договор, по которому одна сторона (перевозчик) обязуется доставить вверенный ему друго

Договор перевозки Договор перевозки – это договор, по которому одна сторона (перевозчик) обязуется доставить вверенный ему друго Норвегия

Норвегия Предварительное расследование и его формы. Тема 10

Предварительное расследование и его формы. Тема 10 Итоги работы педколлектива гимназии за 2007-2008 учебный год и перспективы развития гимназии в новом учебном году

Итоги работы педколлектива гимназии за 2007-2008 учебный год и перспективы развития гимназии в новом учебном году МКДОУ д/сад с.Верхний Булай

МКДОУ д/сад с.Верхний Булай 626 О, как рвётся душа

626 О, как рвётся душа Продолжительность жизни человека

Продолжительность жизни человека Выход

Выход Государственная служба в США

Государственная служба в США Образ солнца в русской поэзии

Образ солнца в русской поэзии Проектная работа из глины «Черепашка»

Проектная работа из глины «Черепашка» Образная сила искусства

Образная сила искусства Международный день защиты детей

Международный день защиты детей КОНЦЕПЦИЯ ДЕМОНСТРАЦИОННЫХ ПРОЕКТОВ по внедрению на местном уровне комплексного подхода к управлению жилищным фондом

КОНЦЕПЦИЯ ДЕМОНСТРАЦИОННЫХ ПРОЕКТОВ по внедрению на местном уровне комплексного подхода к управлению жилищным фондом Структура содержание международного договора купли-продажи

Структура содержание международного договора купли-продажи Адаптация человека и функциональное состояние

Адаптация человека и функциональное состояние