Содержание

- 2. ЛИТЕРАТУРА Микропроцессорные информационно-управляющие системы железнодорожного транспорта/А.В.Горелик, В.Ю.Горелик, А.Е.Ермаков, О.П.Ермакова. М.: РОАТ – 2011 г. 230 с.

- 3. Положительные свойства релейных систем 1. Высокая устойчивость к электромагнитным помехам (особенно возникающим при грозовых явлениях) и

- 4. Проблемы релейных систем 1. Большой износ технических средств 2. Медленное внедрение современных технических средств и технологий:

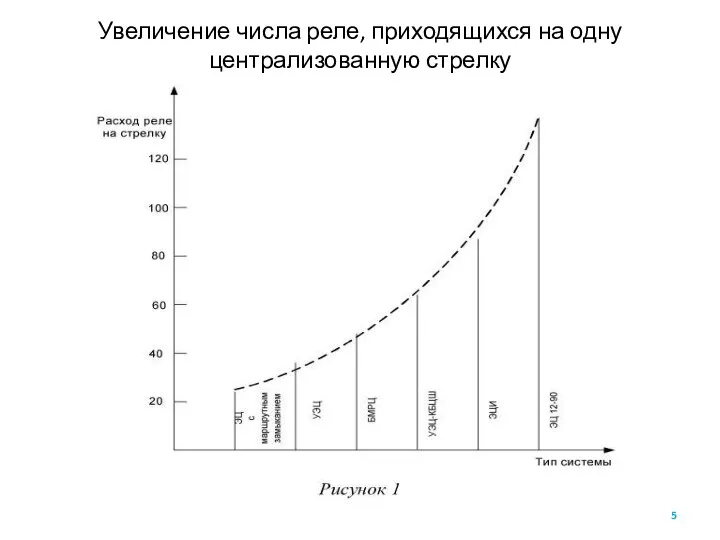

- 5. Увеличение числа реле, приходящихся на одну централизованную стрелку

- 6. Эффективность микропроцессорных СЖАТ Сокращение площадей служебно-технических помещений – размещение необходимой аппаратуры в малогабаритных компоновочных шкафах или

- 7. Проблемы внедрения МПИУС на сети железных дорог Основные причины, усложняющие внедрение новых микропроцессорных систем: - значительная

- 8. Микро-ЭВМ – основа информационно-управляющей системы МИКРОПРОЦЕССОР - самостоятельное или входящее в состав микро-ЭВМ устройство обработки информации,

- 9. МИКРОПРОЦЕССОРНАЯ СИСТЕМА – множество микропроцессорных элементов, находящихся в отношениях и связях друг с другом, образующих определенную

- 10. параллельный порт ввода – вывода; последовательный порт ввода – вывода; преобразователь напряжение – код (АЦП); преобразователь

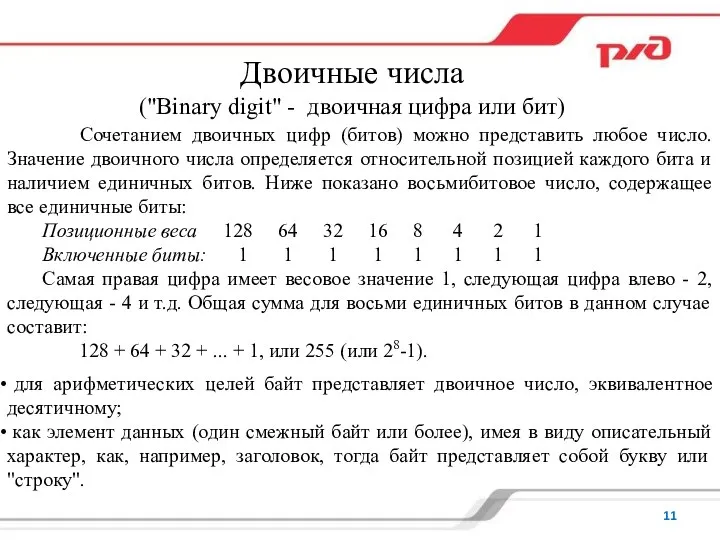

- 11. Двоичные числа ("Binary digit" - двоичная цифра или бит) Сочетанием двоичных цифр (битов) можно представить любое

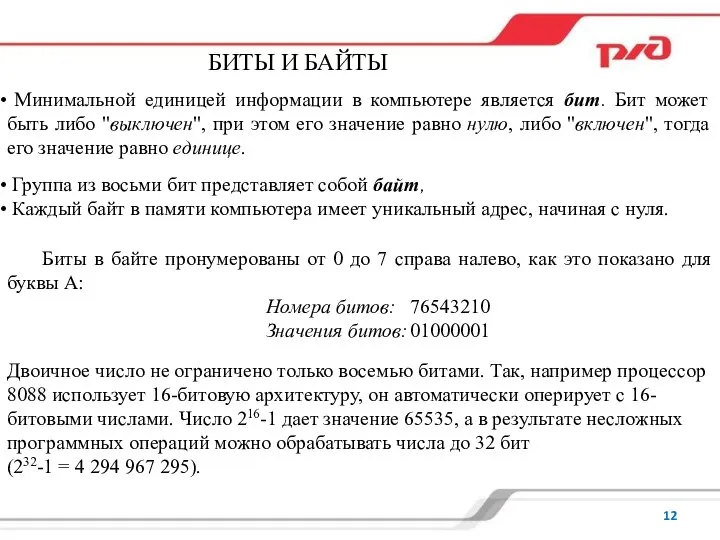

- 12. БИТЫ И БАЙТЫ Минимальной единицей информации в компьютере является бит. Бит может быть либо "выключен", при

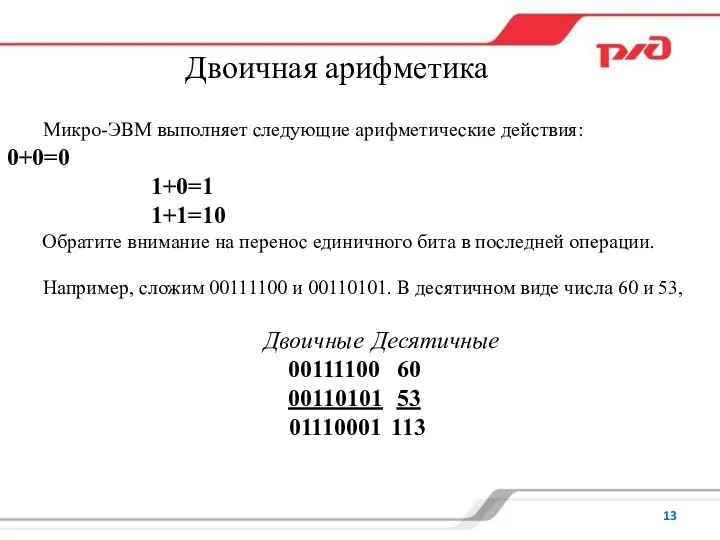

- 13. Двоичная арифметика Микро-ЭВМ выполняет следующие арифметические действия: 0+0=0 1+0=1 1+1=10 Обратите внимание на перенос единичного бита

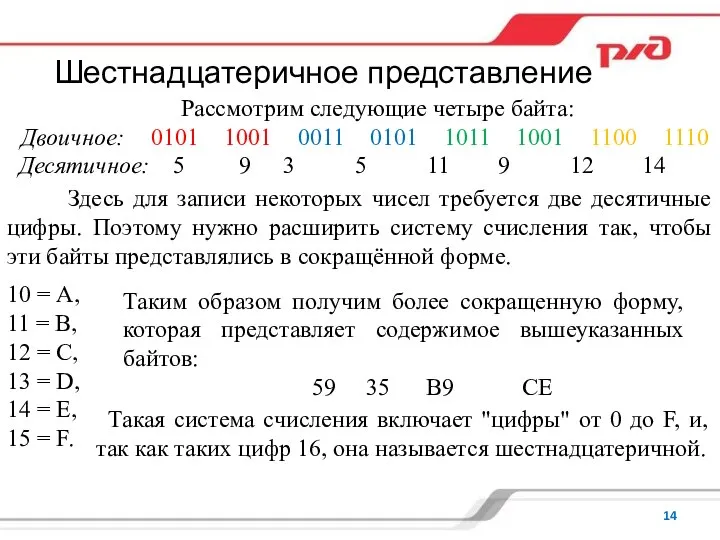

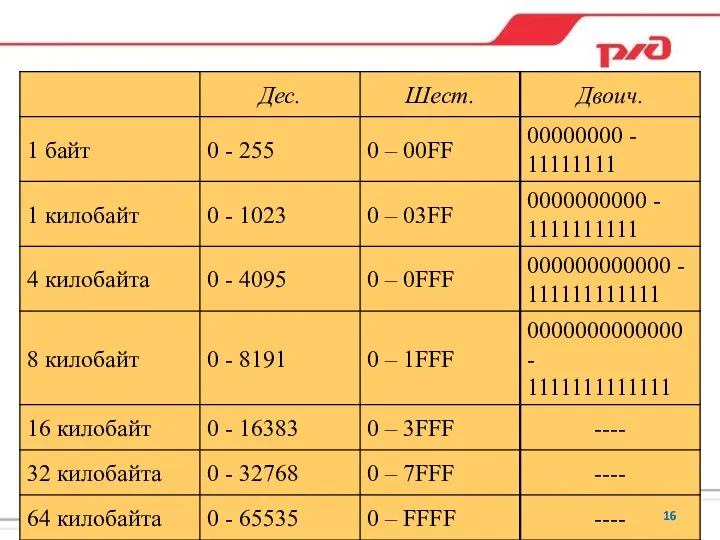

- 14. Шестнадцатеричное представление Рассмотрим следующие четыре байта: Двоичное: 0101 1001 0011 0101 1011 1001 1100 1110 Десятичное:

- 15. Шестнадцатеричное представление Таблица

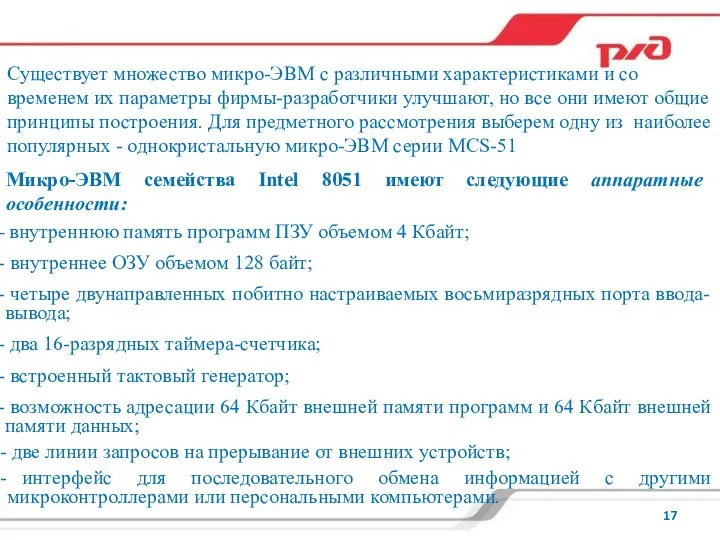

- 17. Существует множество микро-ЭВМ с различными характеристиками и со временем их параметры фирмы-разработчики улучшают, но все они

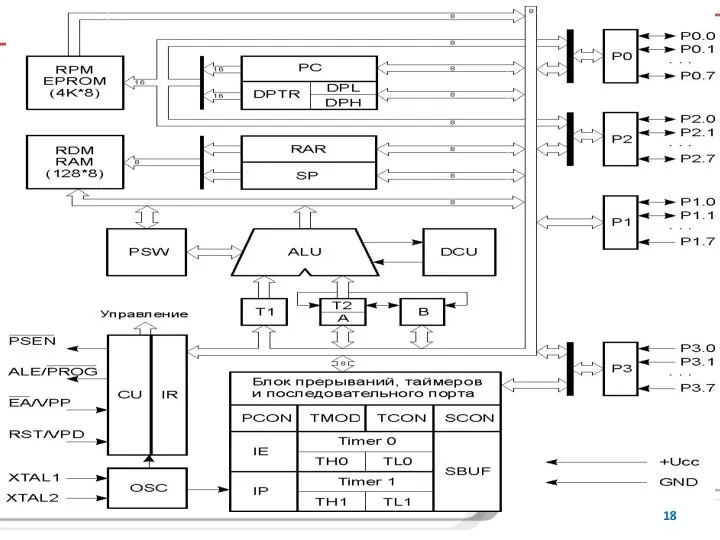

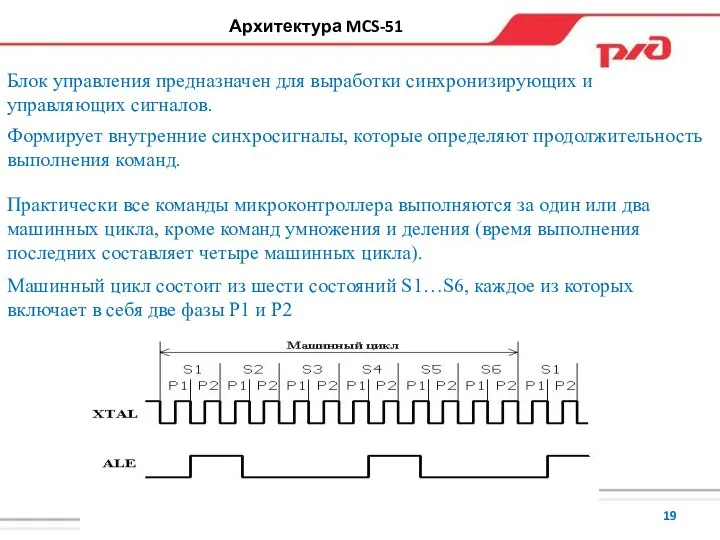

- 19. Архитектура MCS-51 Блок управления предназначен для выработки синхронизирующих и управляющих сигналов. Формирует внутренние синхросигналы, которые определяют

- 20. Длительность каждой фазы равна периоду следования синхроимпульсов, который задается частотой кварцевого резонатора, подключаемого к выводам XTAL1

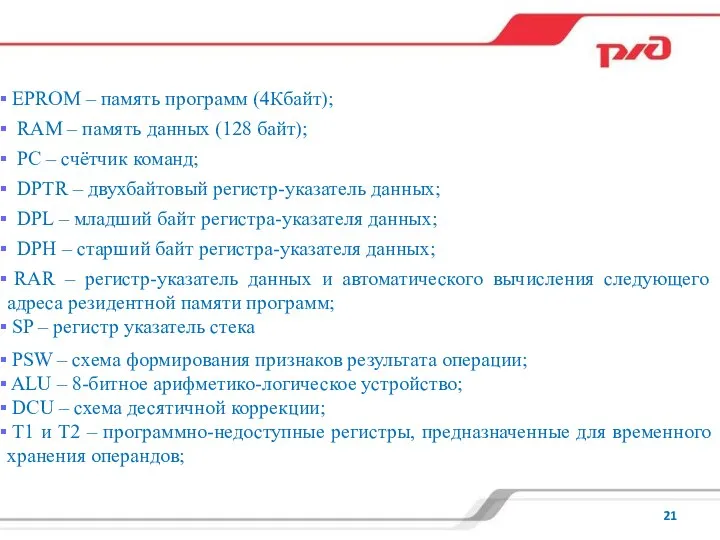

- 21. EPROM – память программ (4Кбайт); RAM – память данных (128 байт); PC – счётчик команд; DPTR

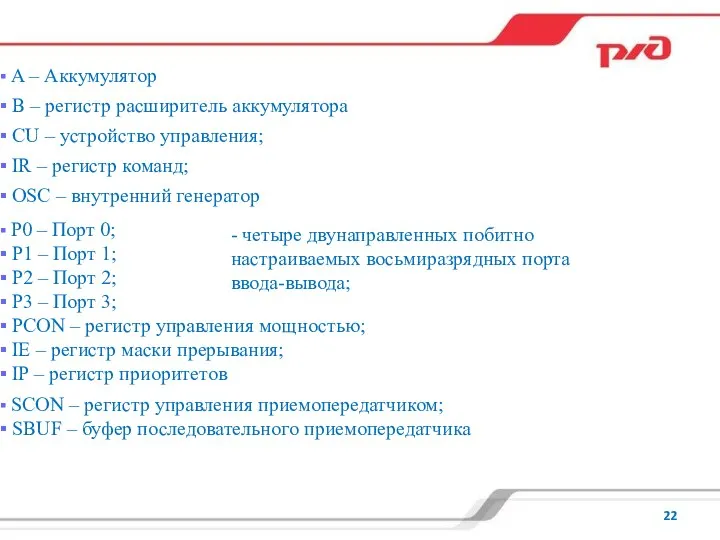

- 22. A – Аккумулятор B – регистр расширитель аккумулятора CU – устройство управления; IR – регистр команд;

- 23. TMOD – регистр режимов таймеров счетчиков; TCON – регистр управления статуса таймеров; TIMER0 – таймер 0;

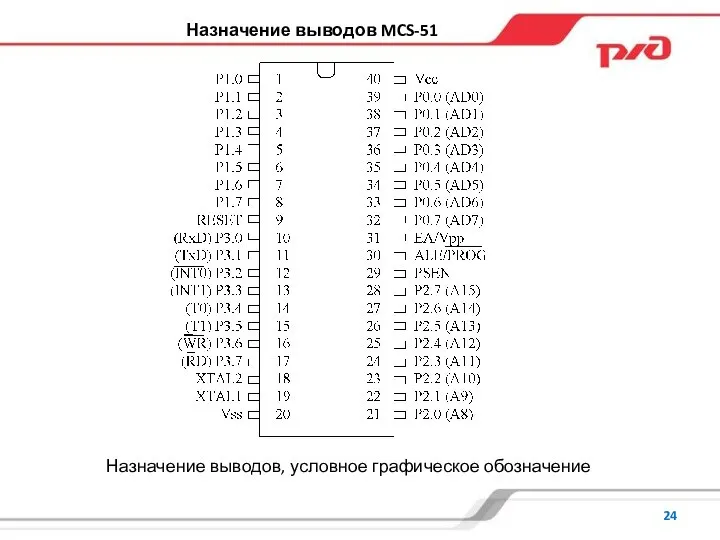

- 24. Назначение выводов MCS-51 Назначение выводов, условное графическое обозначение

- 25. Vss – потенциал общего провода ("земли"); Vcc – основное напряжение питания +5 В; XTAL1, XTAL2 –

- 26. P2 – восьми битный двунаправленный порт, аналогичный Р1; кроме того, выводы этого порта используются для выдачи

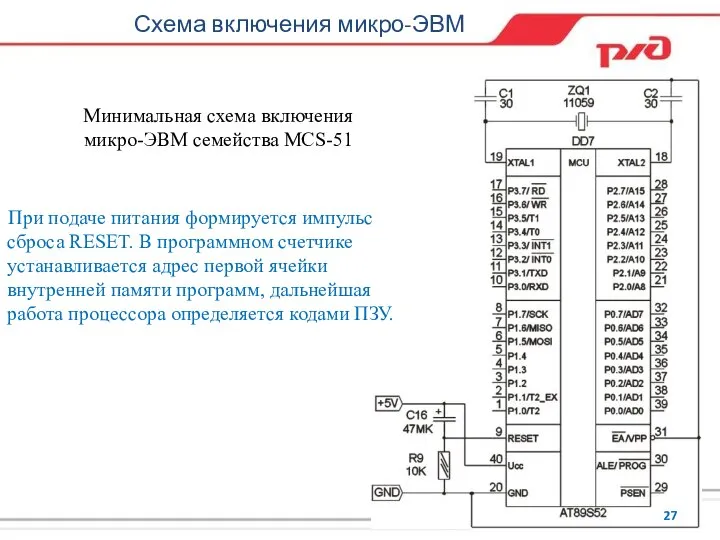

- 27. Схема включения микро-ЭВМ При подаче питания формируется импульс сброса RESET. В программном счетчике устанавливается адрес первой

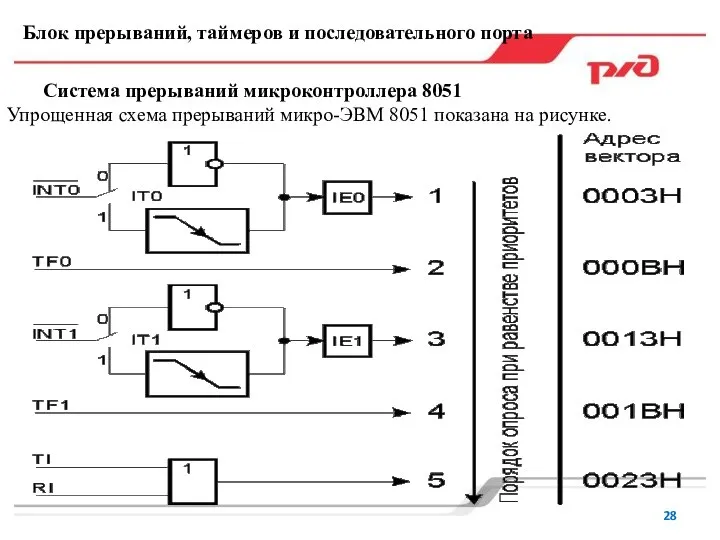

- 28. Блок прерываний, таймеров и последовательного порта Система прерываний микроконтроллера 8051 Упрощенная схема прерываний микро-ЭВМ 8051 показана

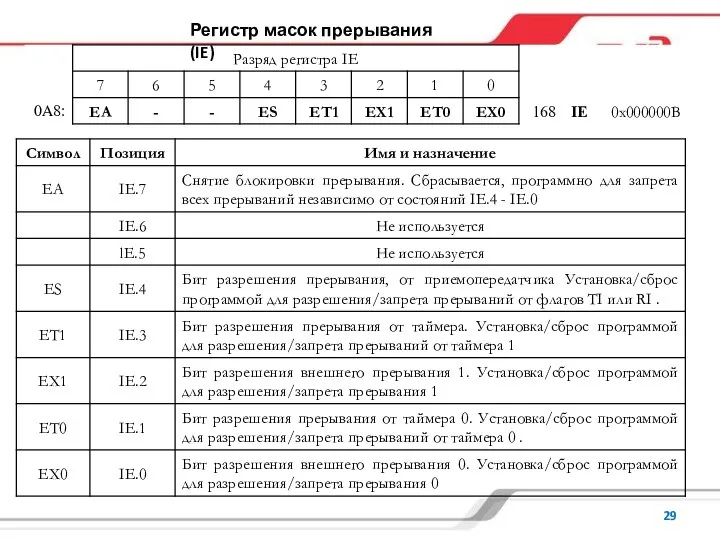

- 29. Регистр масок прерывания (IE)

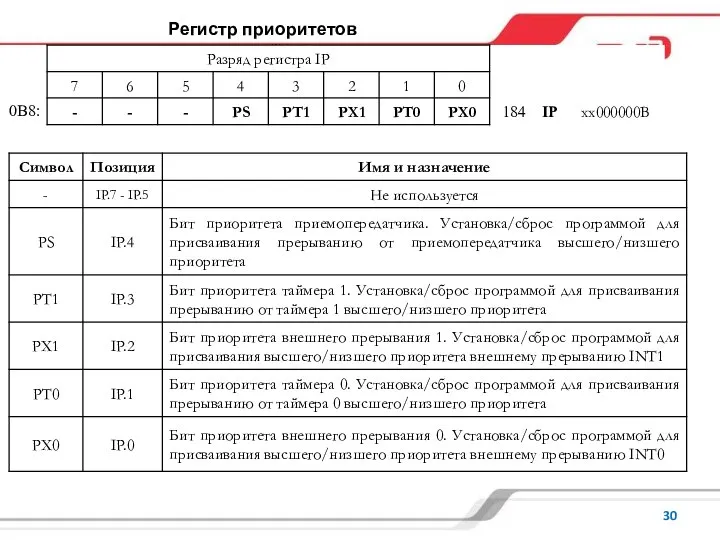

- 30. Регистр приоритетов прерываний (IP)

- 31. Особенности обслуживания прерываний Система прерываний формирует аппаратный вызов соответствующей подпрограммы обслуживания, если она не заблокирована одним

- 32. Таймеры / счетчики микро-ЭВМ семейства 8051 В базовых моделях семейства имеются два программируемых 16-битных таймера/счетчика (T/C0

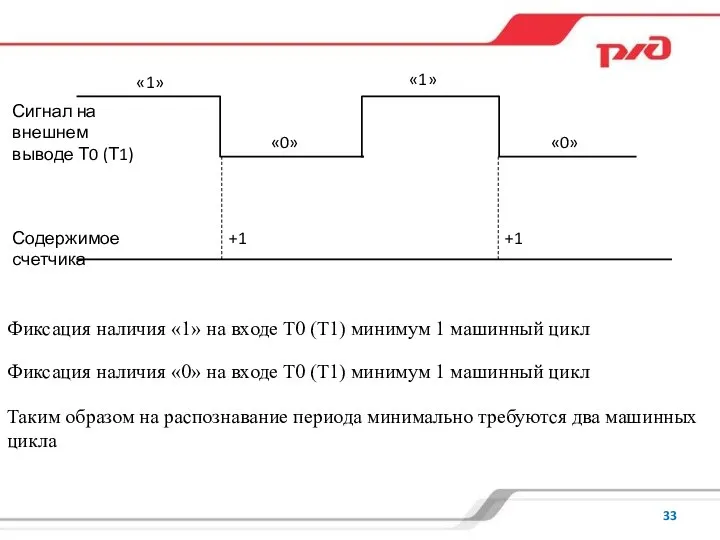

- 33. «1» «0» +1 +1 Сигнал на внешнем выводе Т0 (Т1) Содержимое счетчика «1» «0» Фиксация наличия

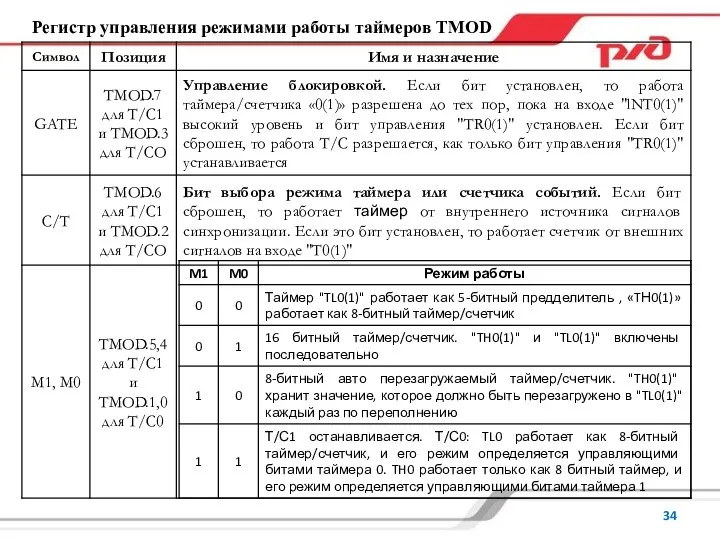

- 34. Регистр управления режимами работы таймеров TMOD

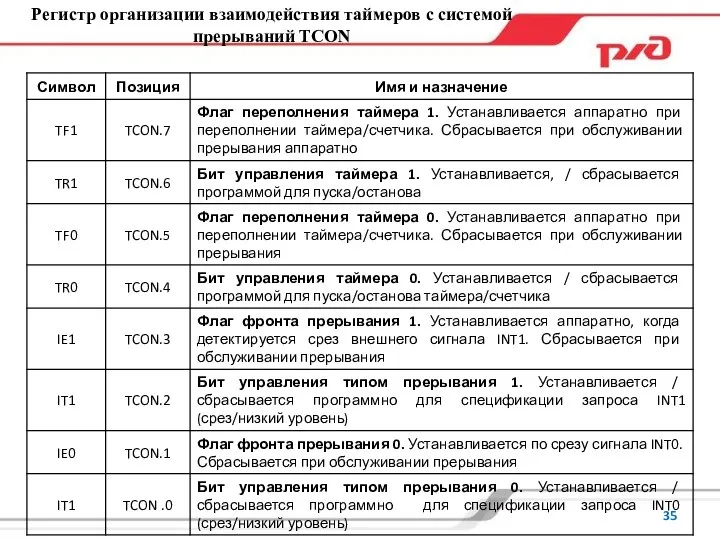

- 35. Регистр организации взаимодействия таймеров с системой прерываний TCON

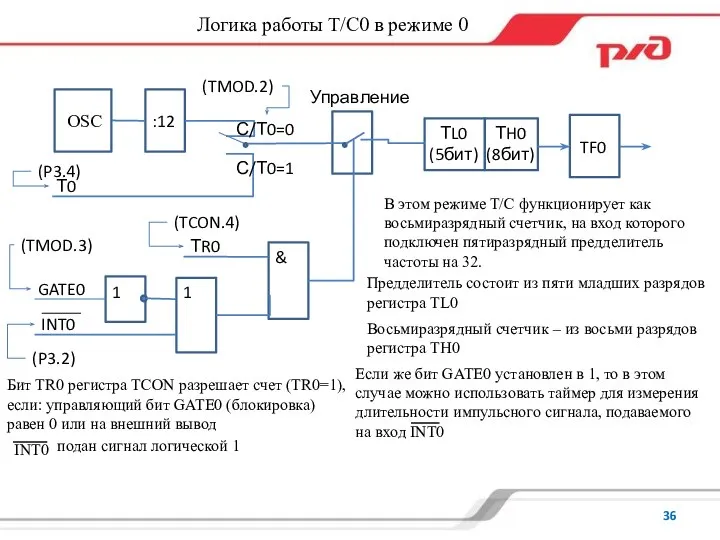

- 36. Логика работы Т/С0 в режиме 0 В этом режиме Т/C функционирует как восьмиразрядный счетчик, на вход

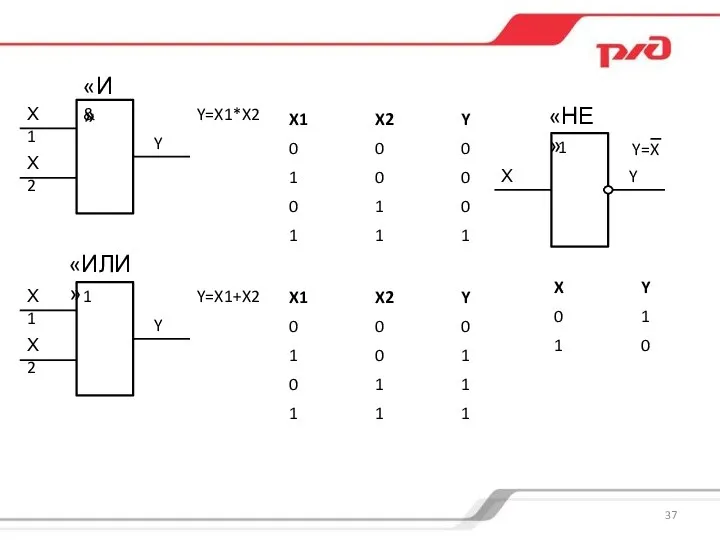

- 37. & Х1 Х2 Y Y=X1*X2 1 Х1 Х2 Y Y=X1+X2 «И» «ИЛИ» 1 Х Y Y=X

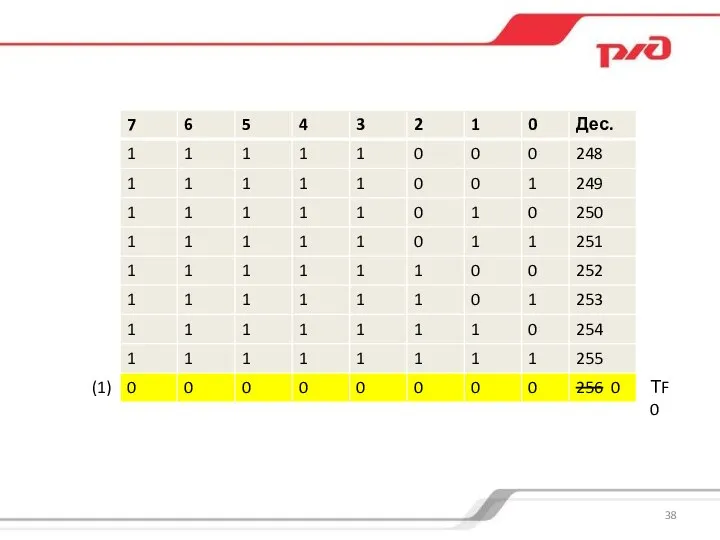

- 38. (1) ТF0

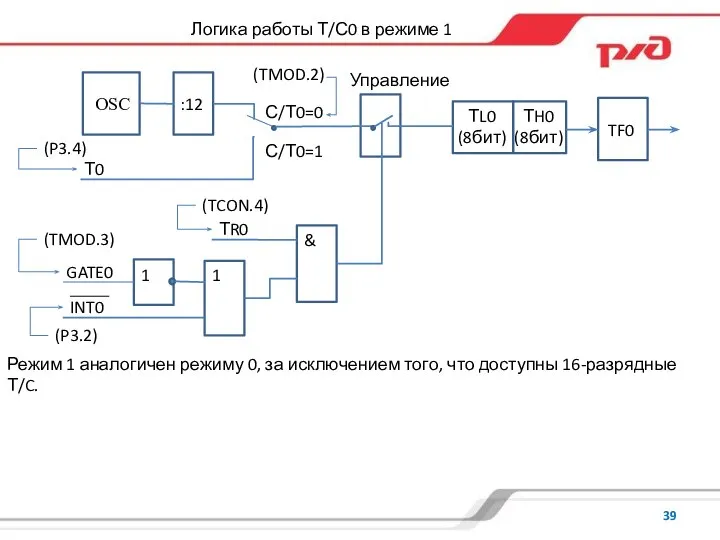

- 39. Логика работы Т/С0 в режиме 1 Режим 1 аналогичен режиму 0, за исключением того, что доступны

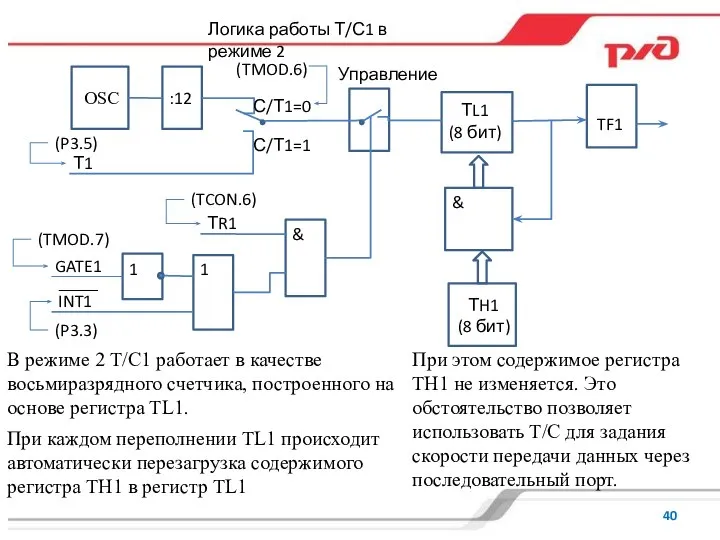

- 40. Логика работы Т/С1 в режиме 2 В режиме 2 Т/C1 работает в качестве восьмиразрядного счетчика, построенного

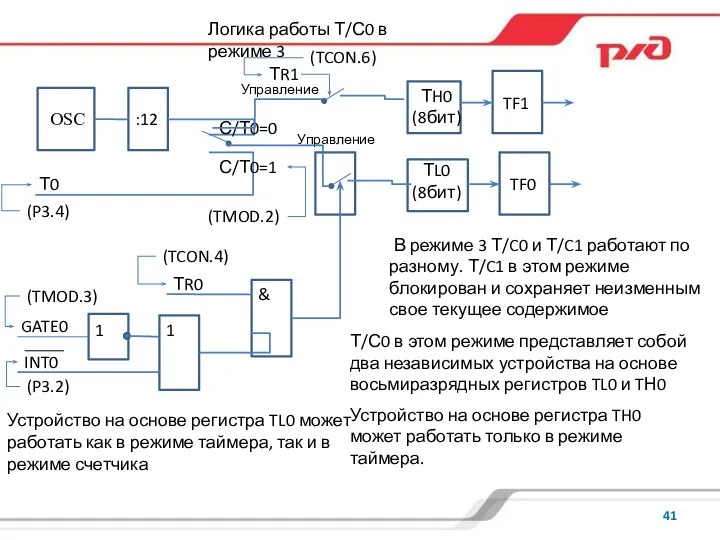

- 41. Логика работы Т/С0 в режиме 3 В режиме 3 Т/C0 и Т/C1 работают по разному. Т/C1

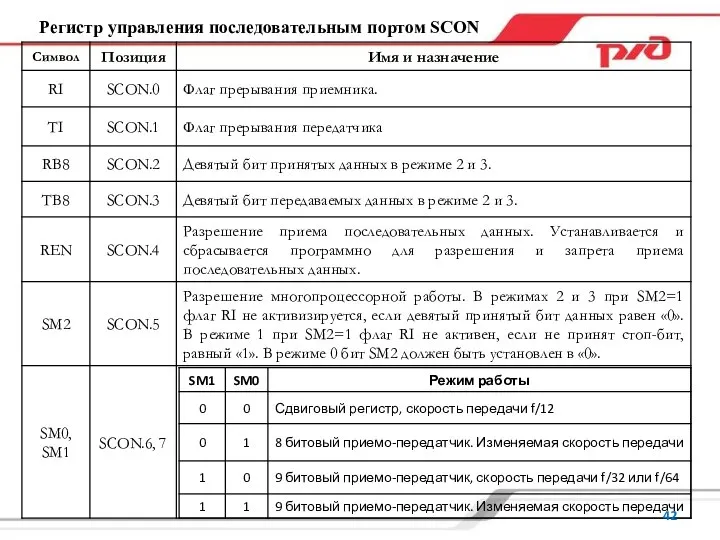

- 42. Регистр управления последовательным портом SCON

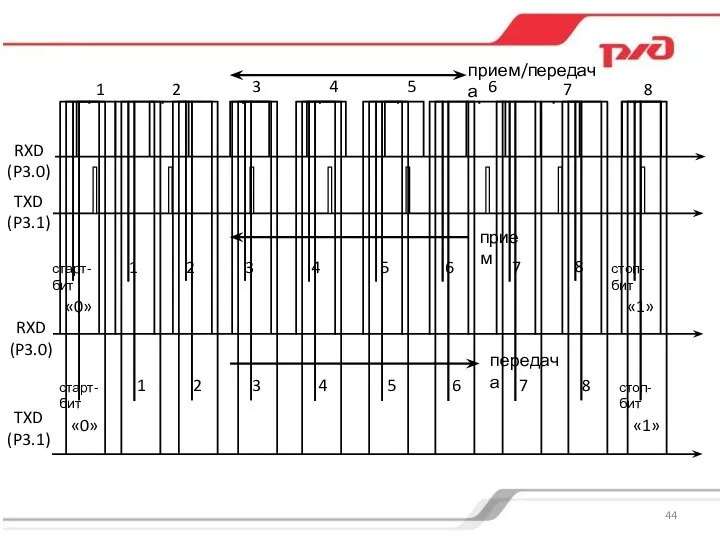

- 43. Блок последовательного интерфейса Блок последовательного интерфейса предназначен для организации ввода/вывода информации по последовательному каналу Последовательный интерфейс

- 44. RXD (P3.0) 1 2 3 4 5 6 7 8 TXD (P3.1) RXD (P3.0) 1 2

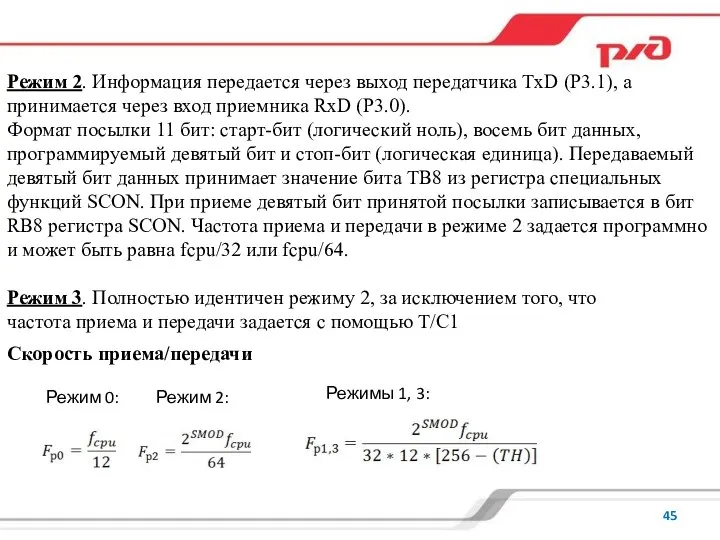

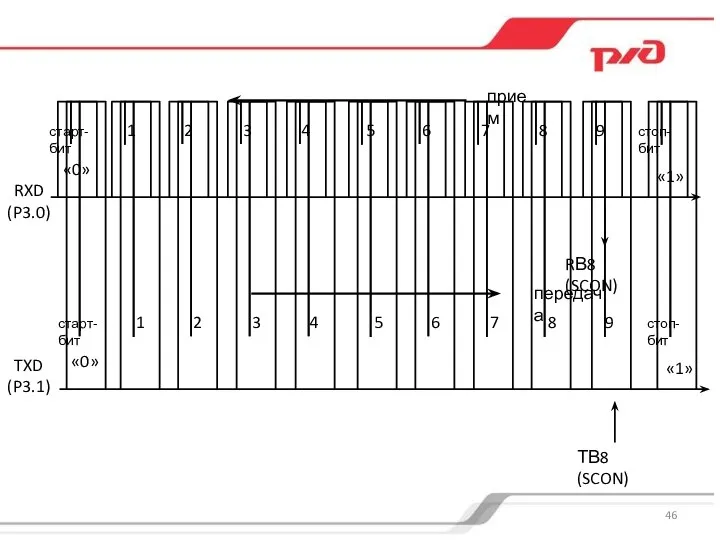

- 45. Режим 2. Информация передается через выход передатчика TxD (Р3.1), а принимается через вход приемника RxD (Р3.0).

- 46. RXD (P3.0) 1 2 3 4 5 6 7 8 TXD (P3.1) старт-бит «0» стоп-бит «1»

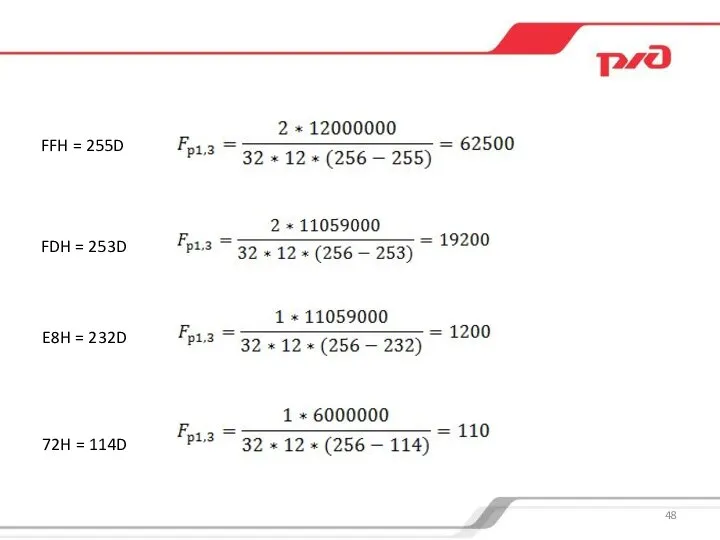

- 47. В таблице приведен ряд стандартных скоростей последовательного обмена и то, как они могут быть реализованы с

- 48. FFH = 255D FDH = 253D E8H = 232D 72H = 114D

- 49. Интерфейсы последовательного ввода вывода информации Электрические интерфейсы RS-232, RS-422, RS-423 (V.10), RS-485, токовая петля Последовательные интерфейсы

- 50. При этом обеспечивается полудуплексный режим связи, то есть, приемник и передатчик могут работать одновременно Недостаток этого

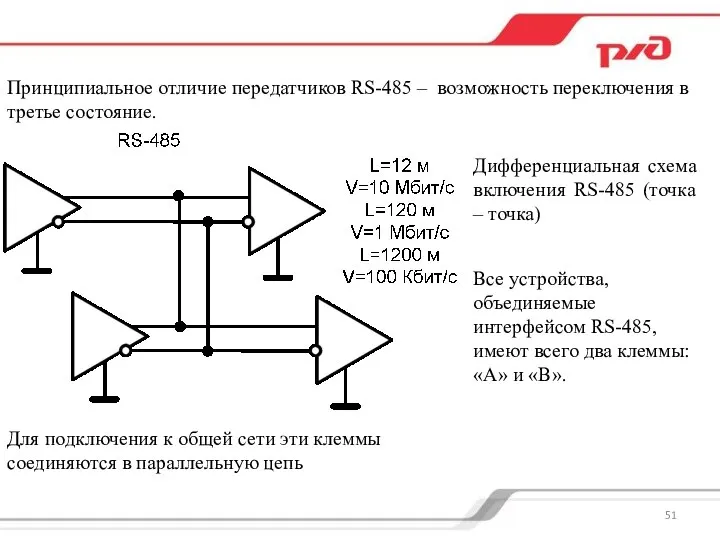

- 51. Принципиальное отличие передатчиков RS-485 – возможность переключения в третье состояние. Дифференциальная схема включения RS-485 (точка –

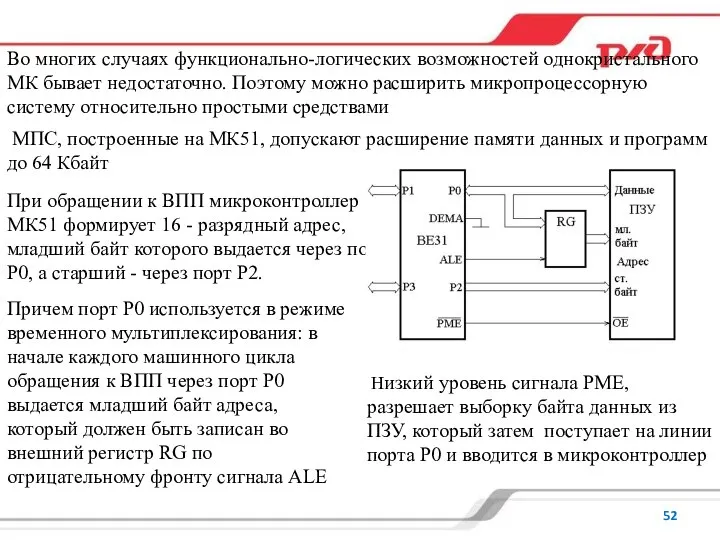

- 52. Во многих случаях функционально-логических возможностей однокристального МК бывает недостаточно. Поэтому можно расширить микропроцессорную систему относительно простыми

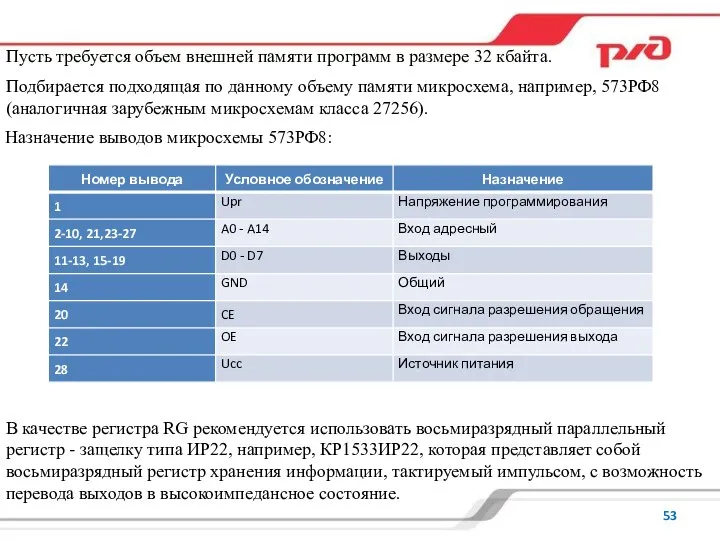

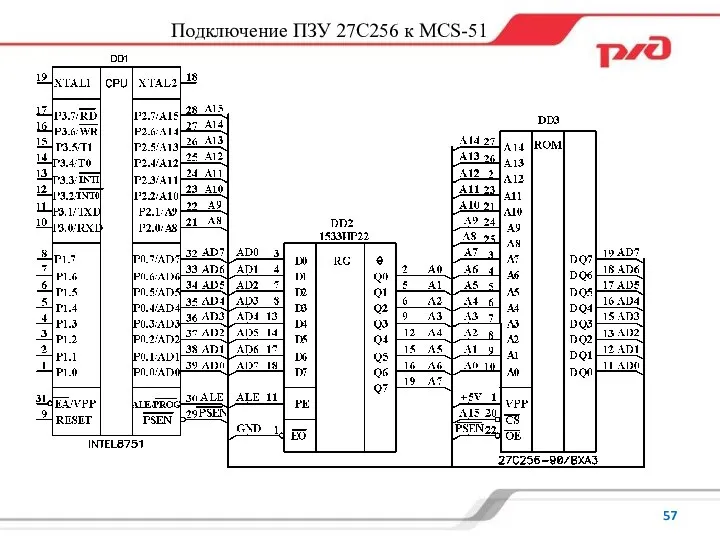

- 53. Пусть требуется объем внешней памяти программ в размере 32 кбайта. Подбирается подходящая по данному объему памяти

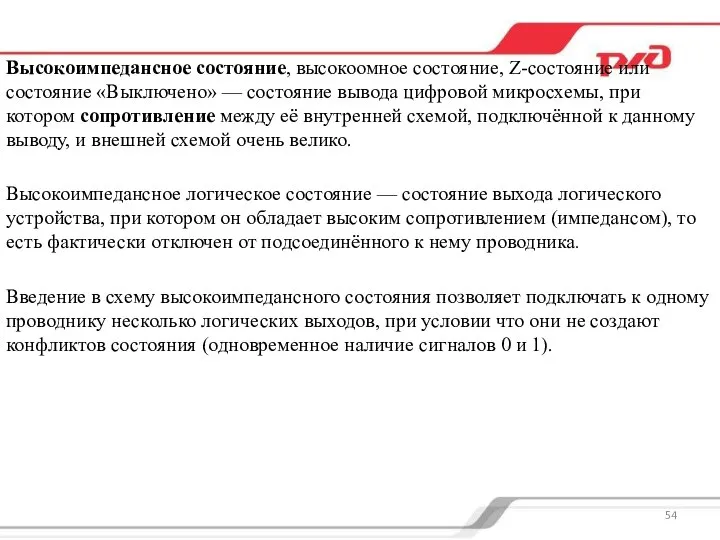

- 54. Высокоимпедансное состояние, высокоомное состояние, Z-состояние или состояние «Выключено» — состояние вывода цифровой микросхемы, при котором сопротивление

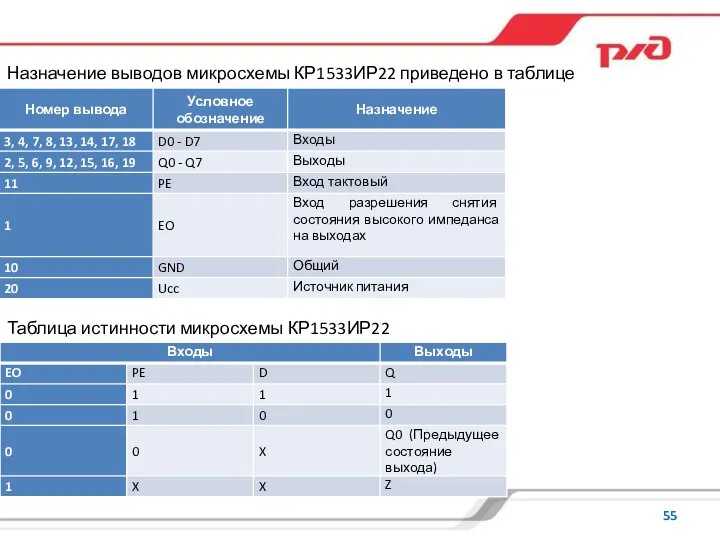

- 55. Назначение выводов микросхемы КР1533ИР22 приведено в таблице Таблица истинности микросхемы КР1533ИР22

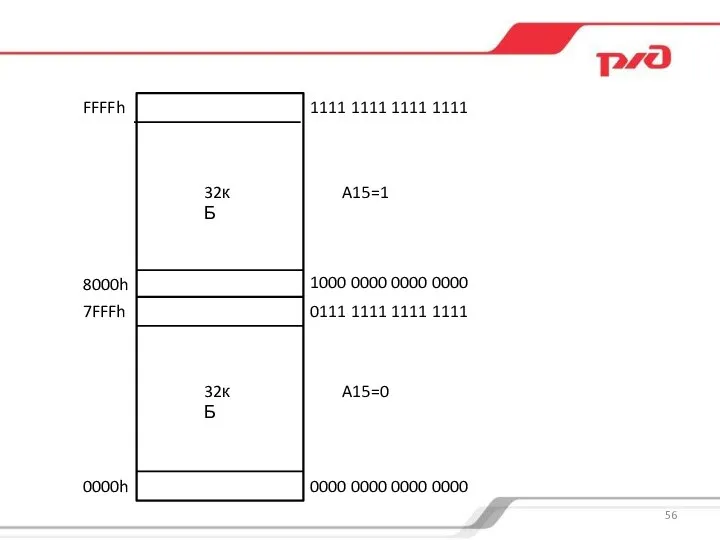

- 56. 0000h 7FFFh 8000h FFFFh 0000 0000 0000 0000 0111 1111 1111 1111 1000 0000 0000 0000

- 57. Подключение ПЗУ 27С256 к MCS-51

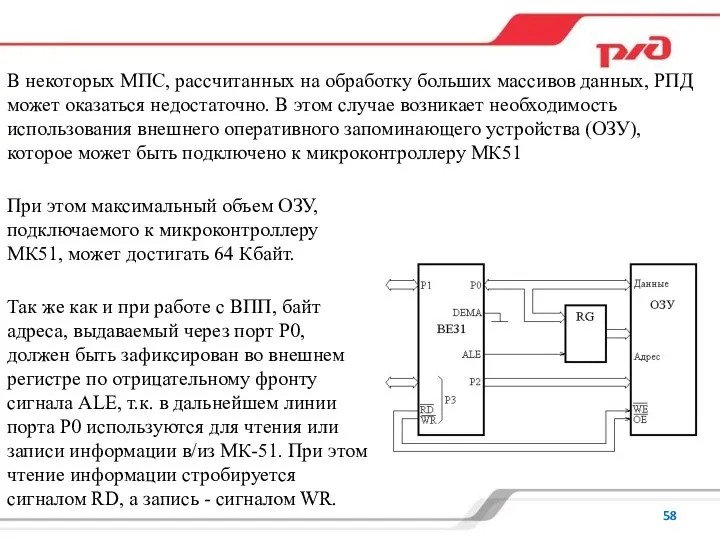

- 58. В некоторых МПС, рассчитанных на обработку больших массивов данных, РПД может оказаться недостаточно. В этом случае

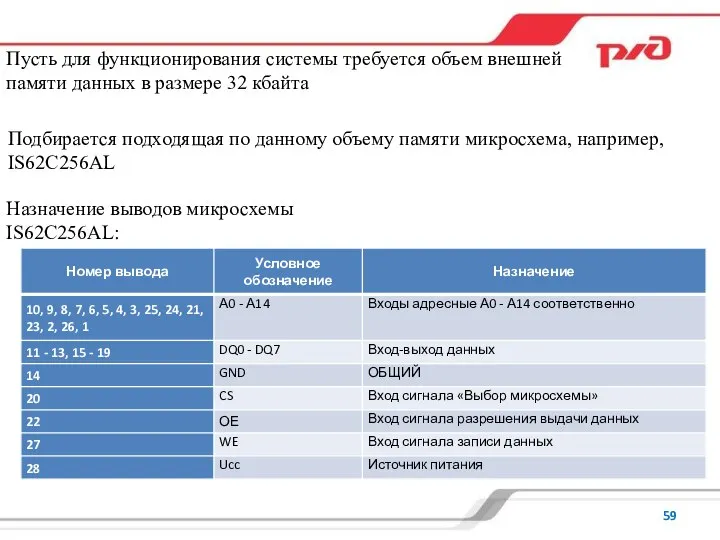

- 59. Пусть для функционирования системы требуется объем внешней памяти данных в размере 32 кбайта Подбирается подходящая по

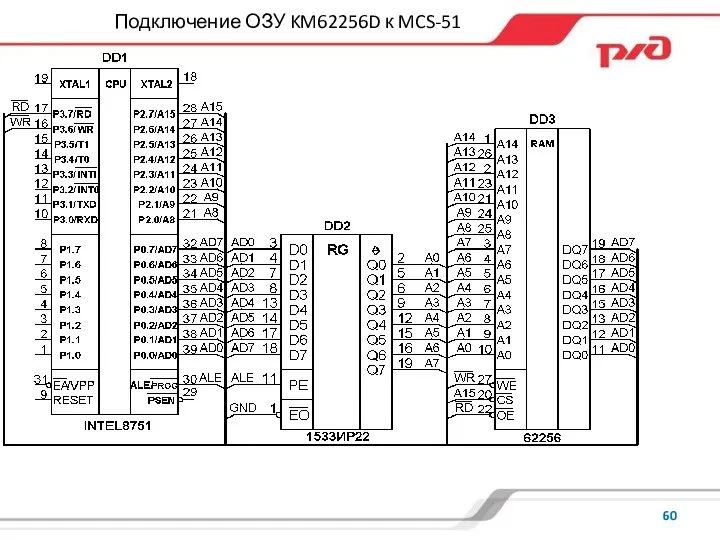

- 60. Подключение ОЗУ KM62256D к MCS-51

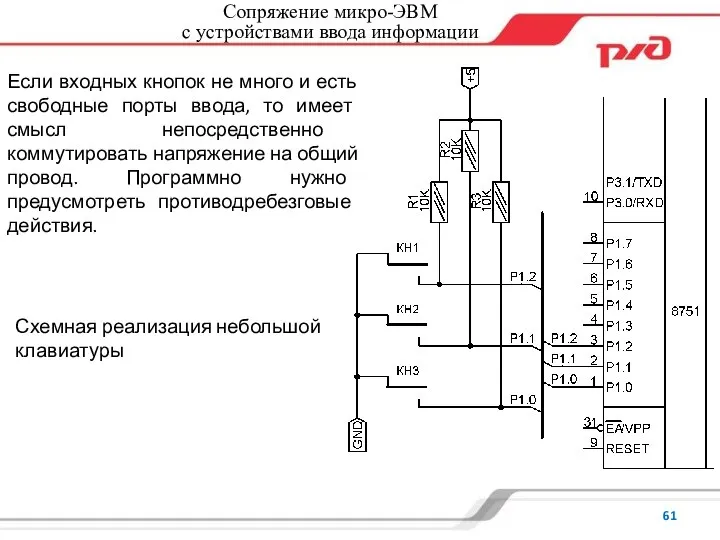

- 61. Сопряжение микро-ЭВМ с устройствами ввода информации Если входных кнопок не много и есть свободные порты ввода,

- 62. Устранение дребезга контактов При работе МК с датчиками, имеющими механические или электромеханические контакты (кнопки, клавиши, реле,

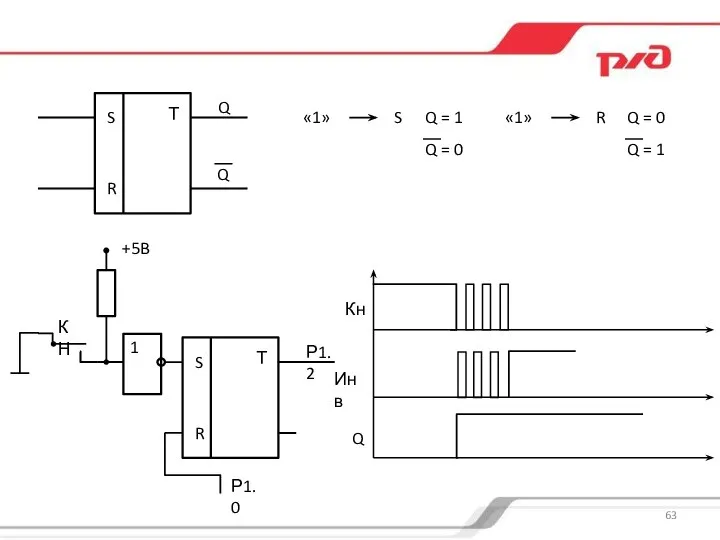

- 63. Т Т S R Q Q «1» S Q = 1 Q = 0 «1» R

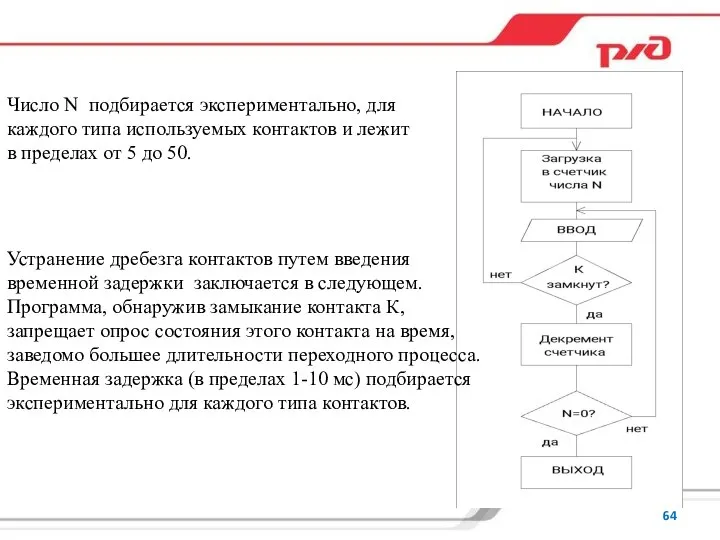

- 64. Число N подбирается экспериментально, для каждого типа используемых контактов и лежит в пределах от 5 до

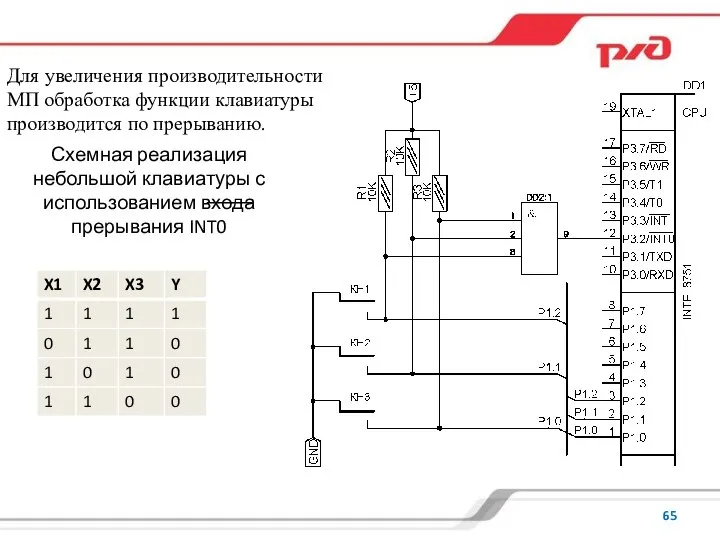

- 65. Для увеличения производительности МП обработка функции клавиатуры производится по прерыванию. Схемная реализация небольшой клавиатуры с использованием

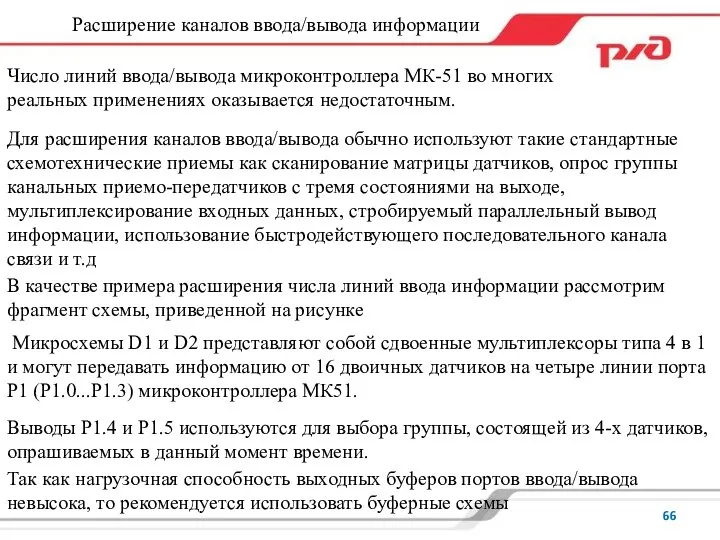

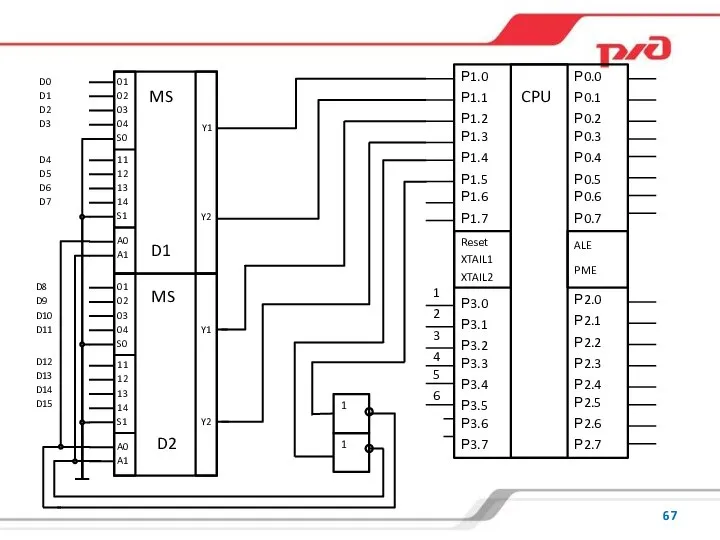

- 66. Расширение каналов ввода/вывода информации Число линий ввода/вывода микроконтроллера МК-51 во многих реальных применениях оказывается недостаточным. В

- 67. MS D1 D2

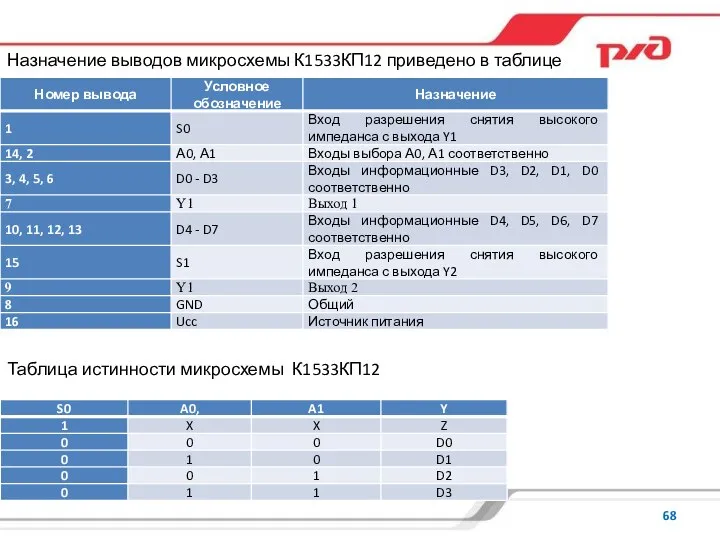

- 68. Назначение выводов микросхемы К1533КП12 приведено в таблице Таблица истинности микросхемы К1533КП12

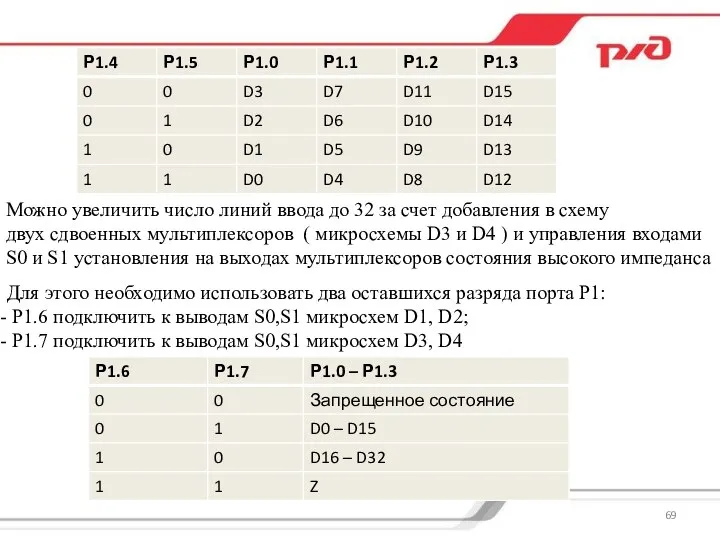

- 69. Можно увеличить число линий ввода до 32 за счет добавления в схему двух сдвоенных мультиплексоров (

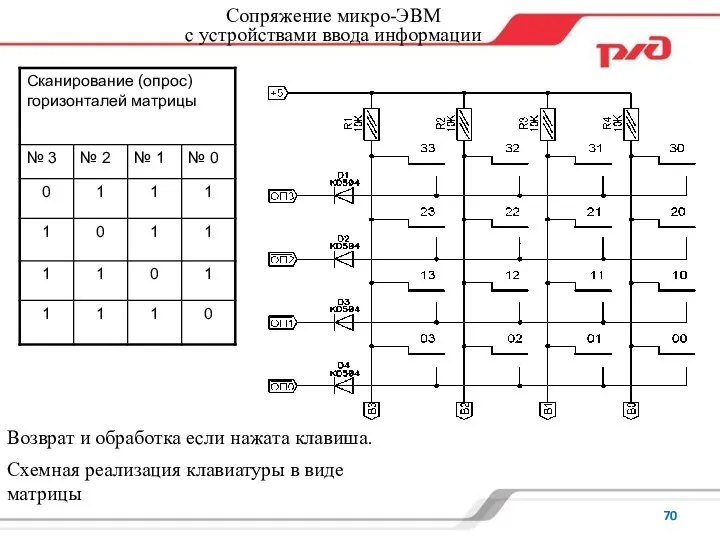

- 70. Сопряжение микро-ЭВМ с устройствами ввода информации Возврат и обработка если нажата клавиша. Схемная реализация клавиатуры в

- 71. Диоды предназначены для защиты токового ключа порта от замыкания на другие линии опроса в случае одновременного

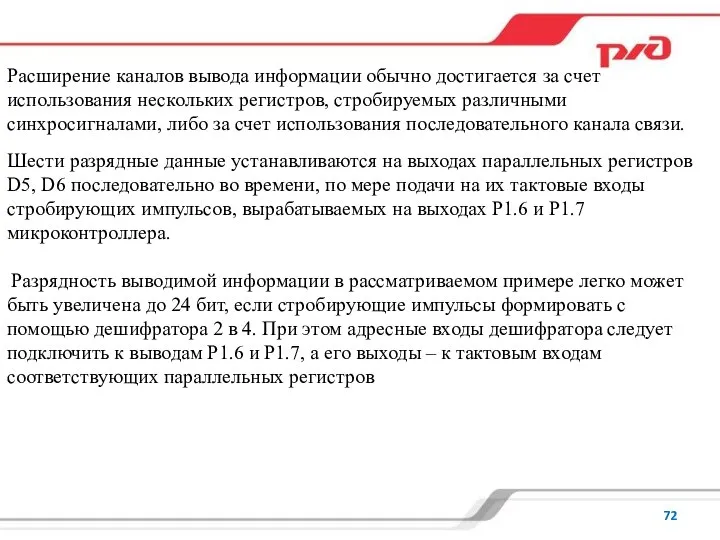

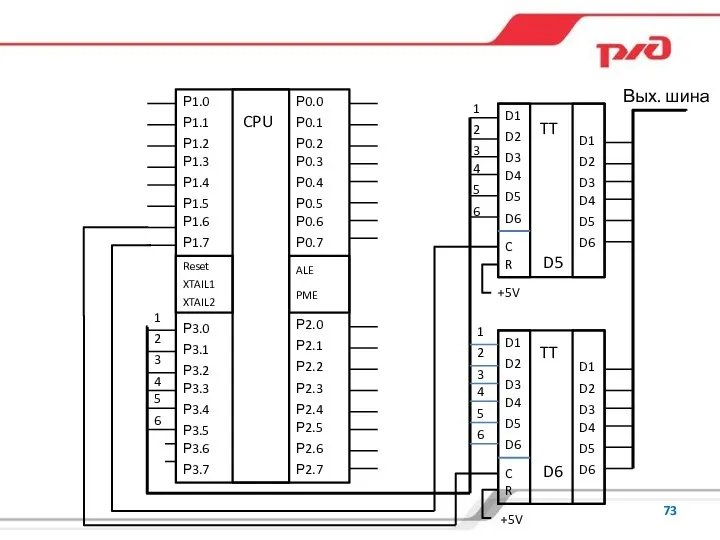

- 72. Расширение каналов вывода информации обычно достигается за счет использования нескольких регистров, стробируемых различными синхросигналами, либо за

- 73. Вых. шина D5 D6

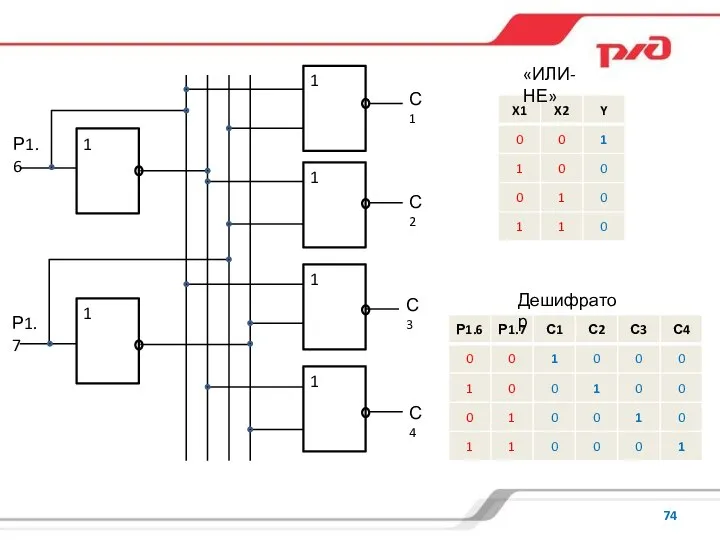

- 74. 1 1 1 1 1 1 С1 С2 С3 С4 Р1.6 Р1.7 «ИЛИ-НЕ» Дешифратор

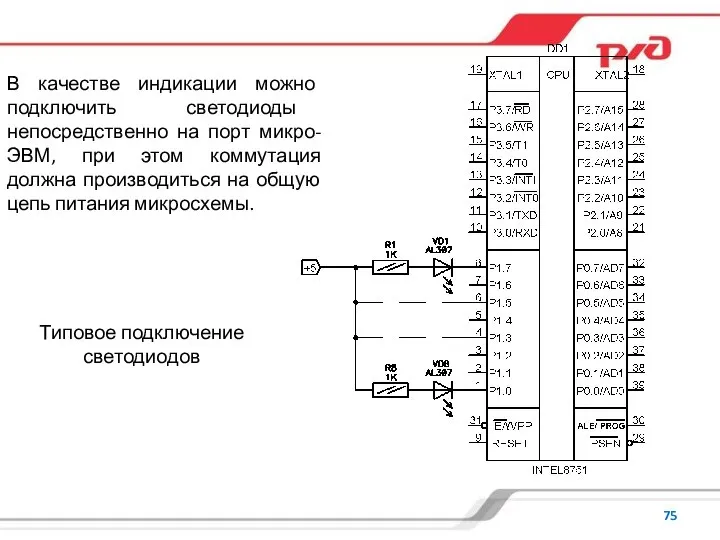

- 75. В качестве индикации можно подключить светодиоды непосредственно на порт микро-ЭВМ, при этом коммутация должна производиться на

- 76. Использование мощных транзисторов с коэффициентом передачи тока более 700 даёт возможность коммутации цепи током до нескольких

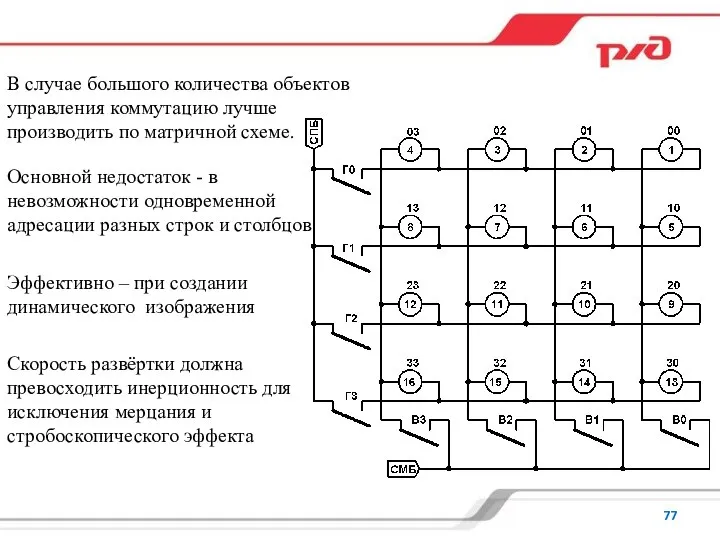

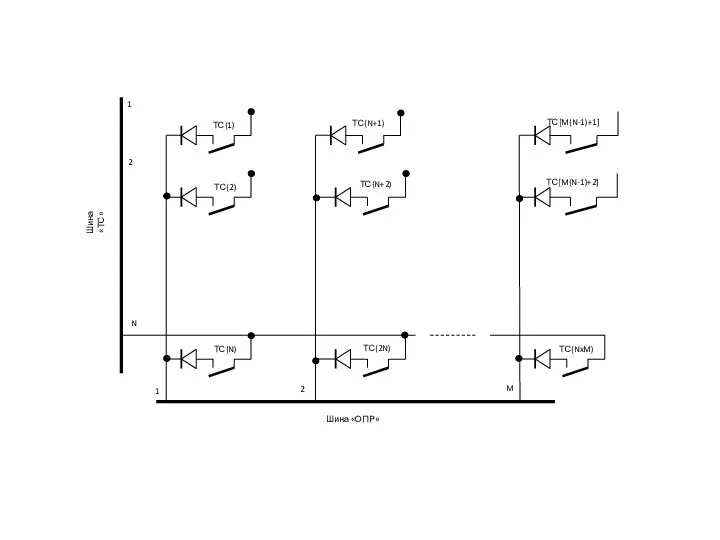

- 77. В случае большого количества объектов управления коммутацию лучше производить по матричной схеме. Основной недостаток - в

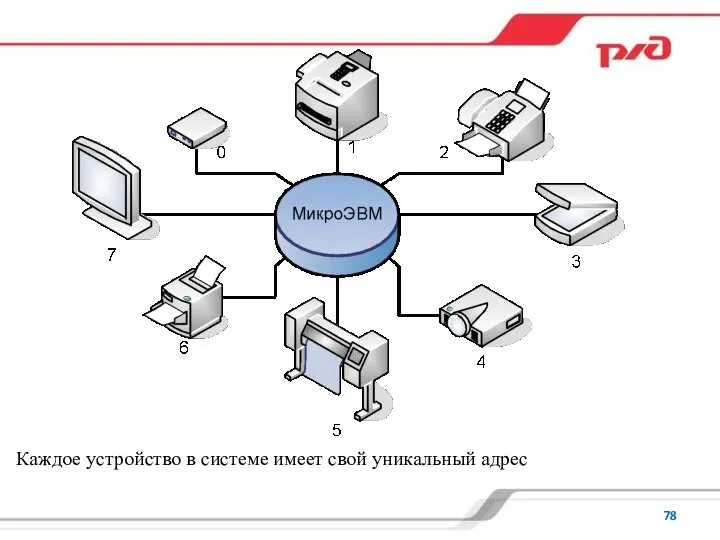

- 78. Каждое устройство в системе имеет свой уникальный адрес

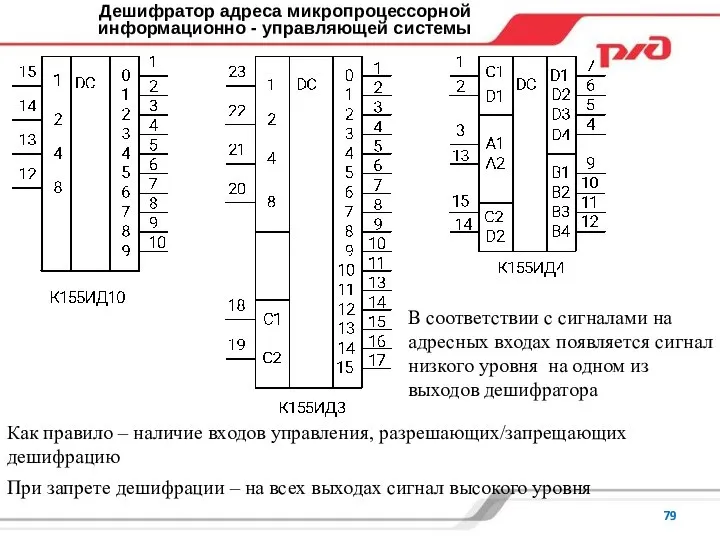

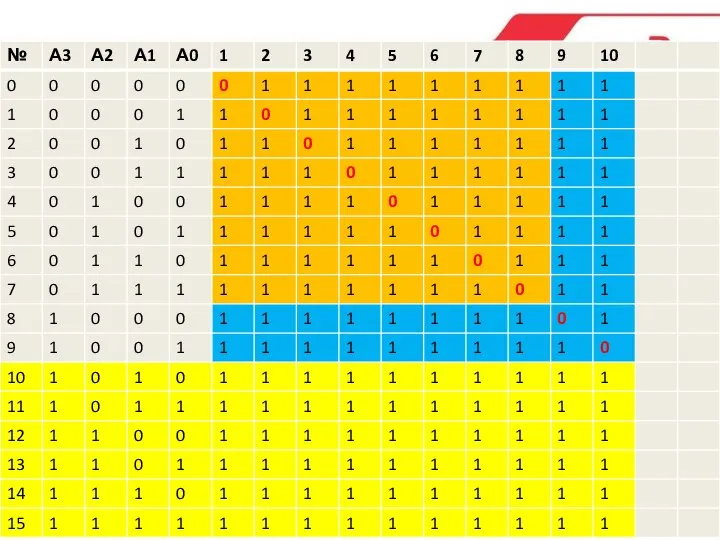

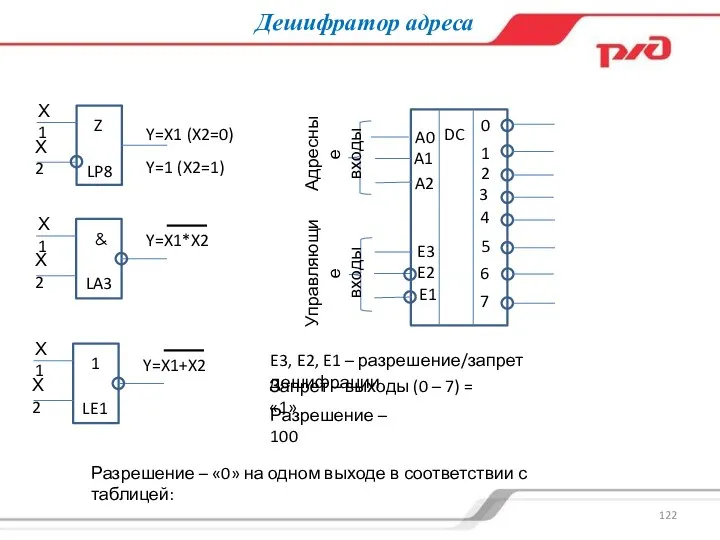

- 79. Дешифратор адреса микропроцессорной информационно - управляющей системы В соответствии с сигналами на адресных входах появляется сигнал

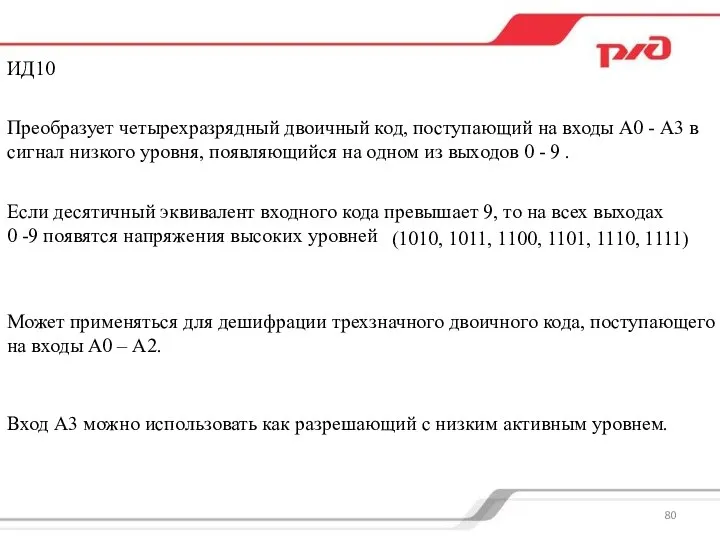

- 80. ИД10 Преобразует четырехразрядный двоичный код, поступающий на входы А0 - А3 в сигнал низкого уровня, появляющийся

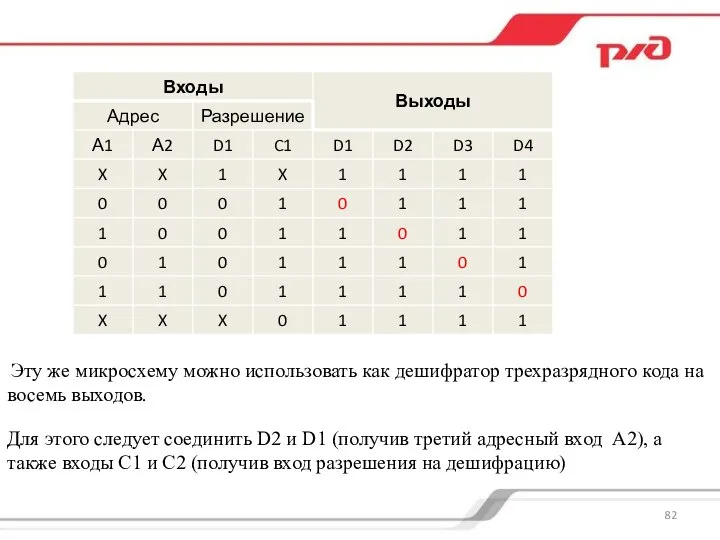

- 82. Эту же микросхему можно использовать как дешифратор трехразрядного кода на восемь выходов. Для этого следует соединить

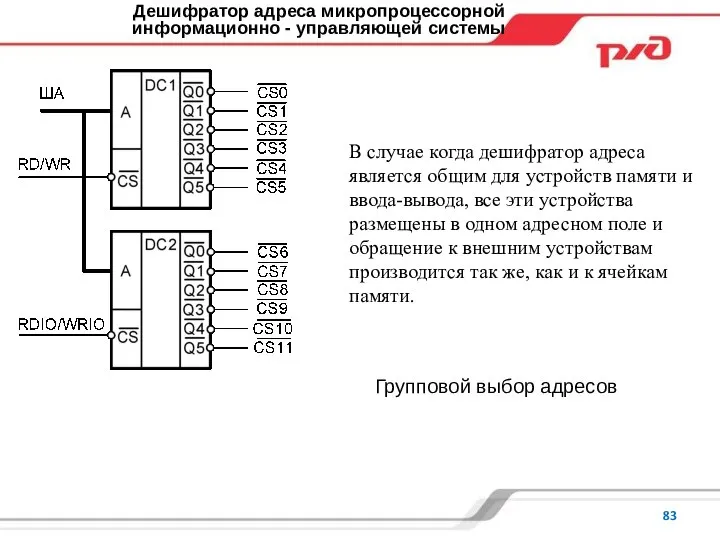

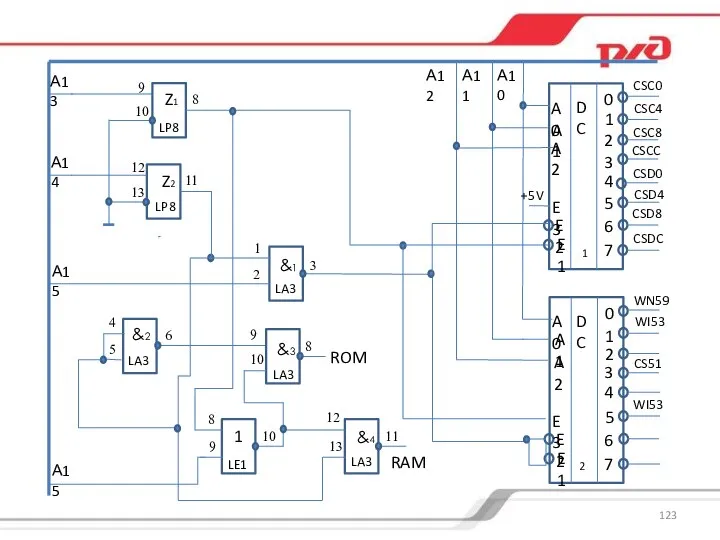

- 83. Дешифратор адреса микропроцессорной информационно - управляющей системы В случае когда дешифратор адреса является общим для устройств

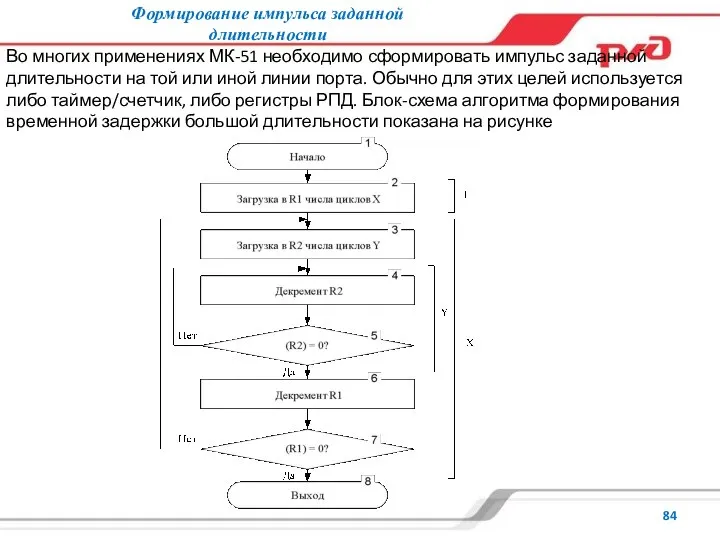

- 84. Во многих применениях МК-51 необходимо сформировать импульс заданной длительности на той или иной линии порта. Обычно

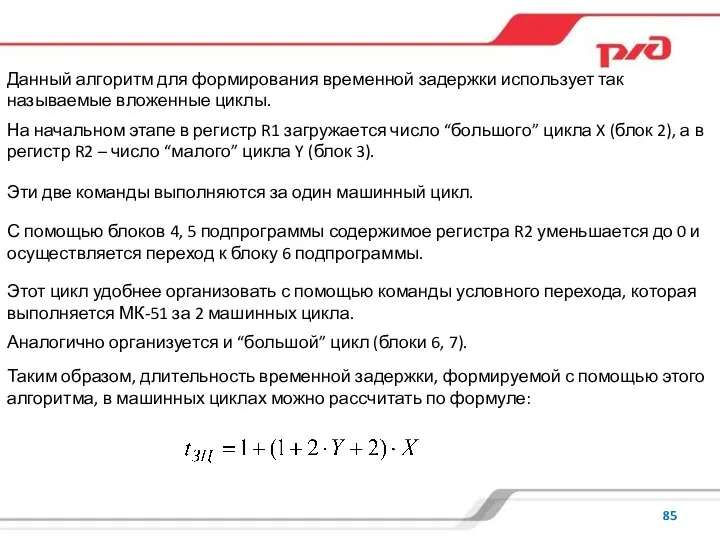

- 85. Данный алгоритм для формирования временной задержки использует так называемые вложенные циклы. На начальном этапе в регистр

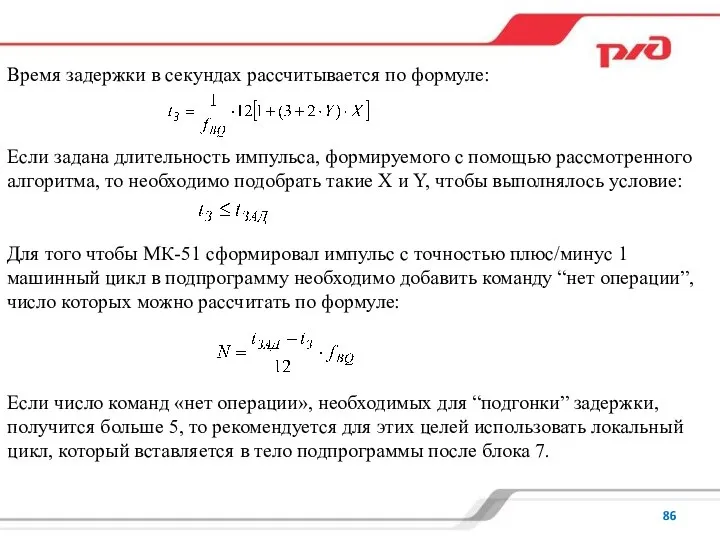

- 86. Время задержки в секундах рассчитывается по формуле: Если задана длительность импульса, формируемого с помощью рассмотренного алгоритма,

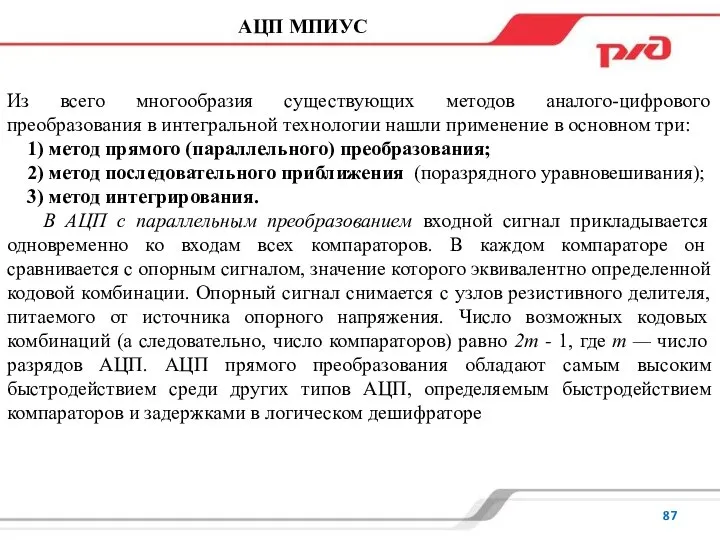

- 87. АЦП МПИУС Из всего многообразия существующих методов аналого-цифрового преобразования в интегральной технологии нашли применение в основном

- 88. Недостатком их является необходимость в большом количестве компараторов. Так, для 8-разрядного АЦП требуется 255 компараторов. Это

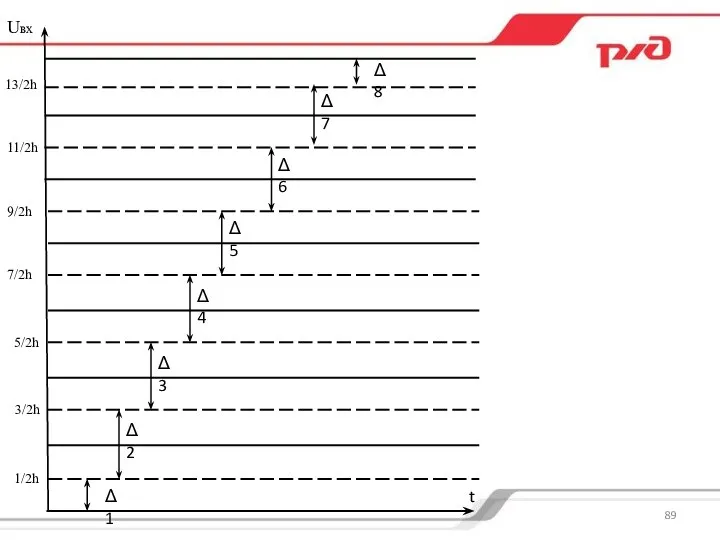

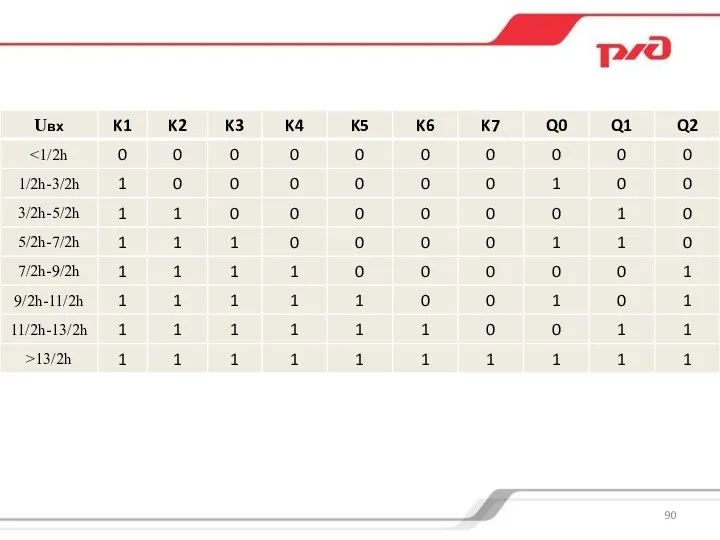

- 89. Uвх 13/2h 11/2h 9/2h 7/2h 5/2h 3/2h 1/2h Δ1 Δ6 Δ7 Δ8 Δ4 Δ5 Δ3 Δ2

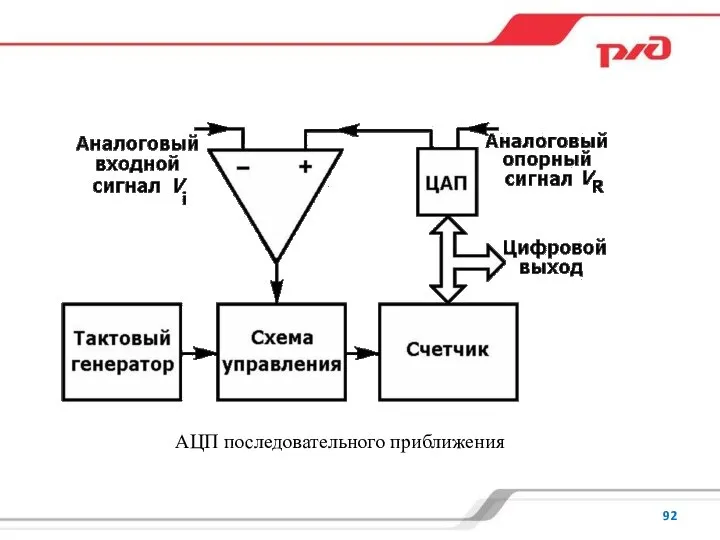

- 91. АЦП последовательного приближения состоит из следующих узлов: 1. Компаратор. Он сравнивает входную величину и текущее значение

- 92. АЦП последовательного приближения

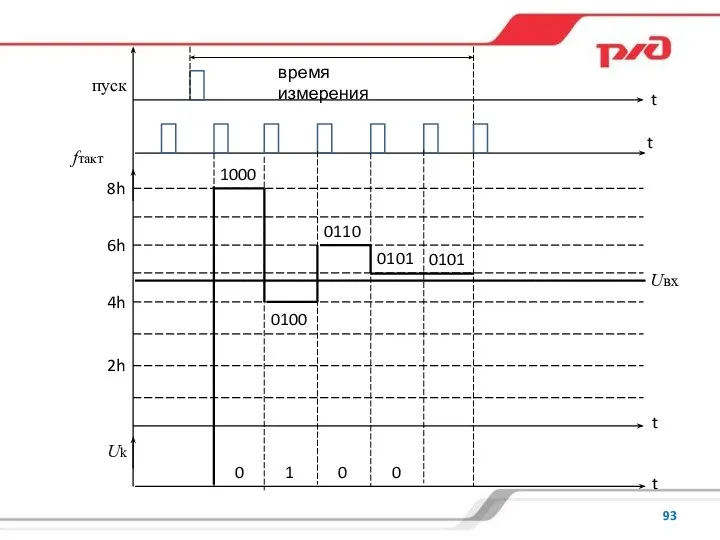

- 93. пуск fтакт 2h 4h 6h 8h Uвх Uk t t t t время измерения 1000 0100

- 94. Наиболее простыми по структуре среди интегрирующих преобразователей являются АЦП с преобразованием напряжения в частоту, построенные на

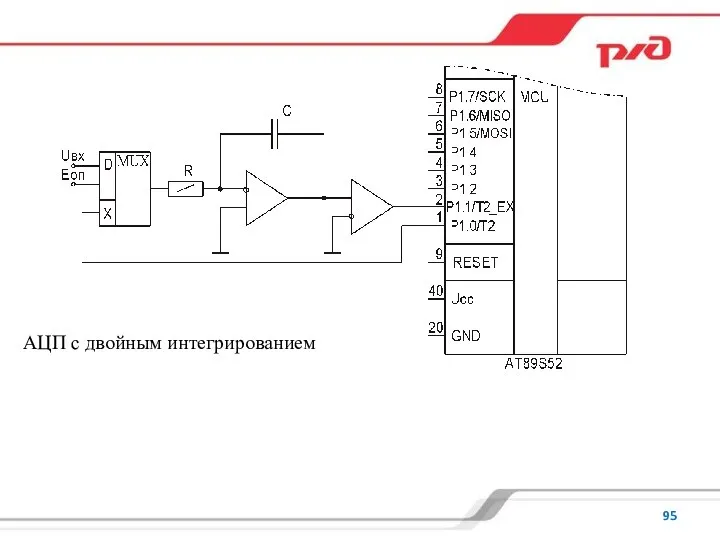

- 95. АЦП с двойным интегрированием

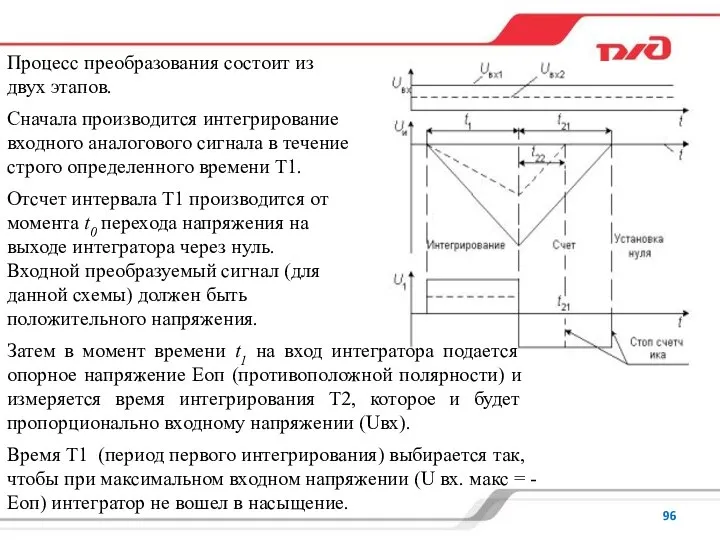

- 96. Процесс преобразования состоит из двух этапов. Сначала производится интегрирование входного аналогового сигнала в течение строго определенного

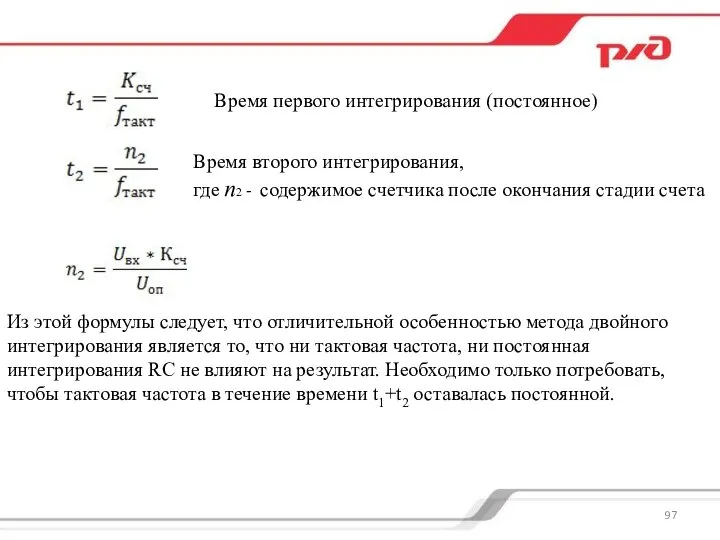

- 97. Время первого интегрирования (постоянное) Время второго интегрирования, где n2 - содержимое счетчика после окончания стадии счета

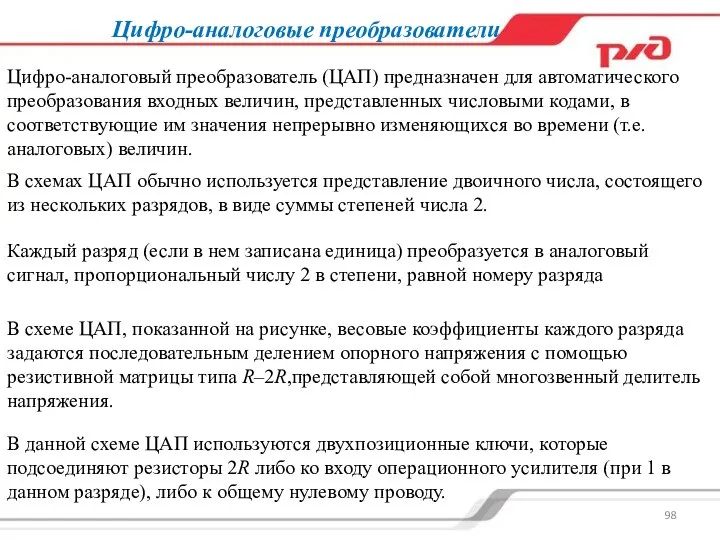

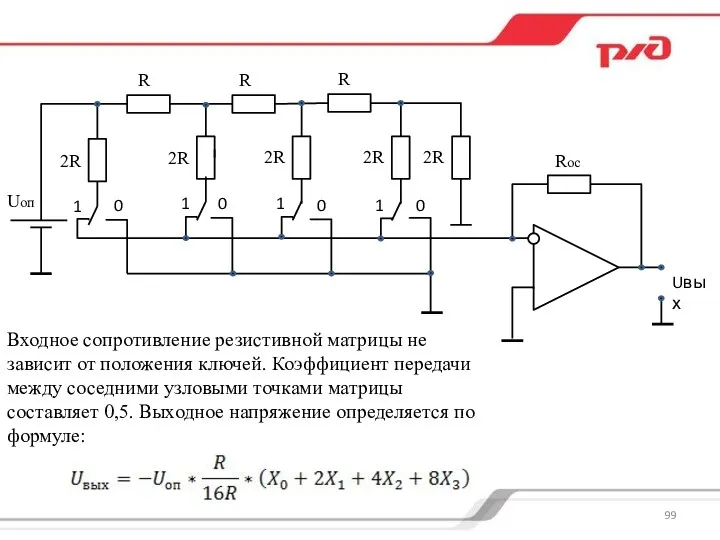

- 98. Цифро-аналоговые преобразователи Цифро-аналоговый преобразователь (ЦАП) предназначен для автоматического преобразования входных величин, представленных числовыми кодами, в соответствующие

- 99. Uвых R Roc R R 2R 2R 2R 2R 2R 0 0 0 0 1 1

- 100. Классификация микропроцессорных информационно-управляющих систем на железнодорожном транспорте К основным таким системам относятся: автоматизированные системы управления и

- 101. Основные преимущества микропроцессорных систем 1. Более высокий уровень надежности 2. Наличие встроенного диагностического контроля состояния аппаратных

- 102. Обеспечение безопасности в микропроцессорных информационно-управляющих системах Недостатки полупроводниковой элементной базы по сравнению с релейной : 1.

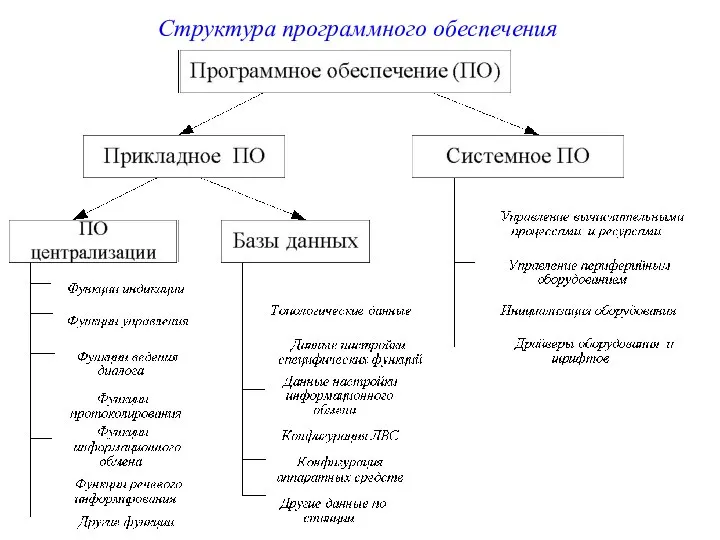

- 103. Структура программного обеспечения

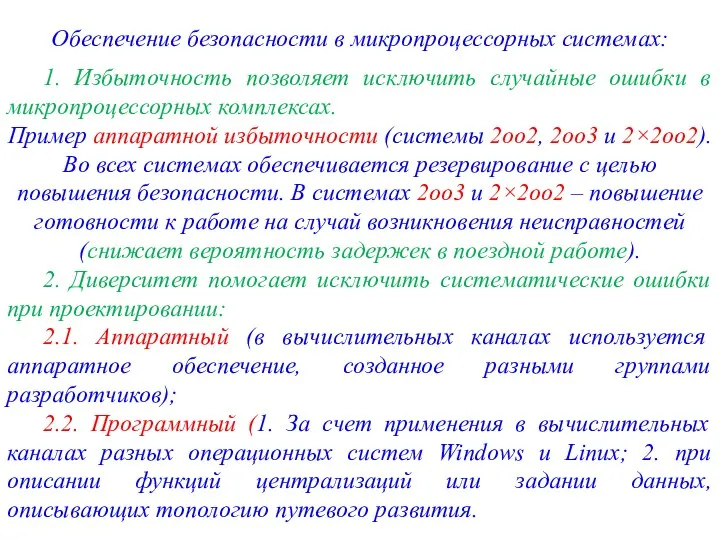

- 104. Обеспечение безопасности в микропроцессорных системах: 1. Избыточность позволяет исключить случайные ошибки в микропроцессорных комплексах. Пример аппаратной

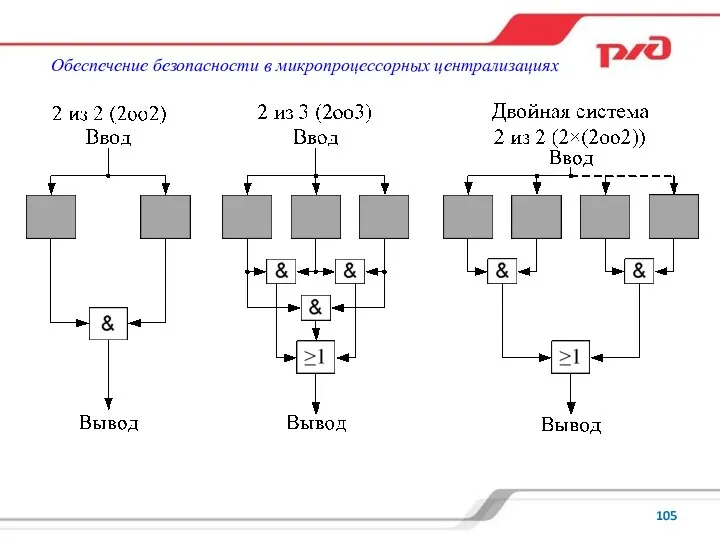

- 105. Обеспечение безопасности в микропроцессорных централизациях

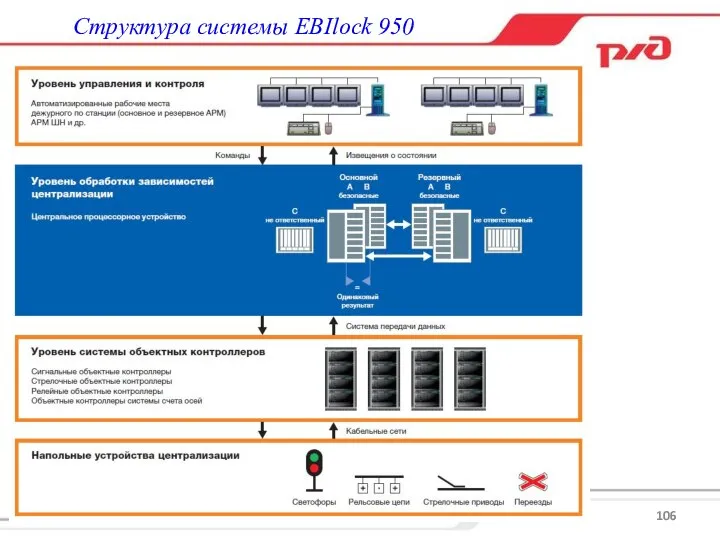

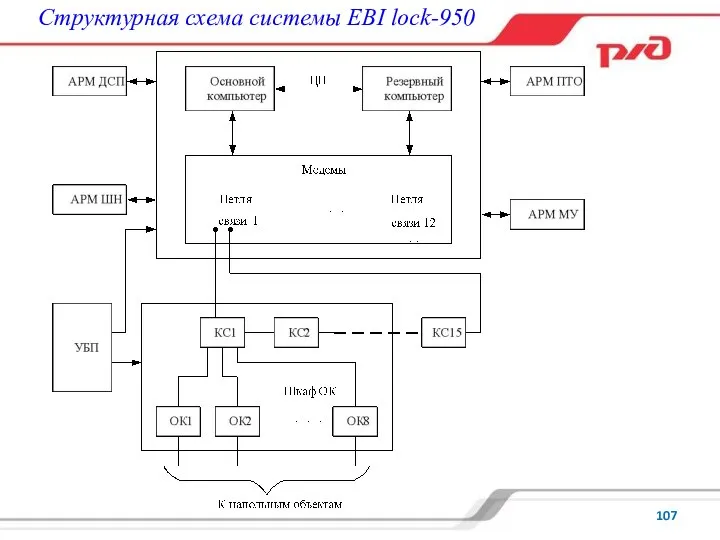

- 106. Структура системы EBIlock 950

- 107. Структурная схема системы EBI lock-950

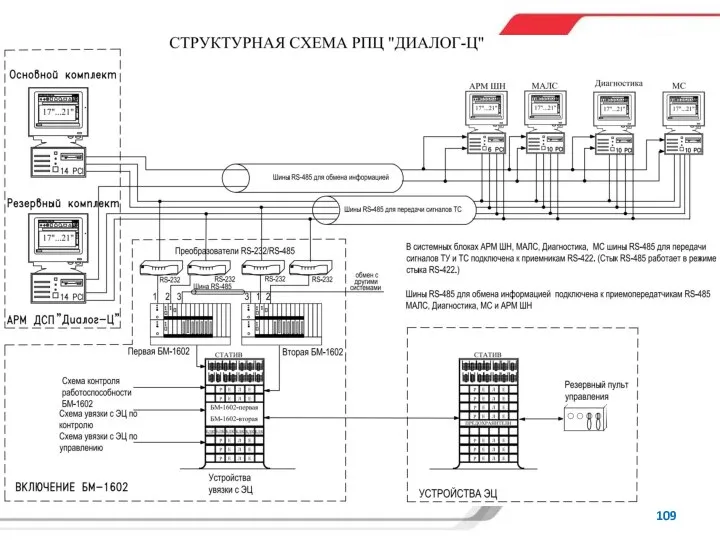

- 108. Одним из перспективных направлений перехода на компьютерные средства в устройствах станционной автоматики является применение релейно-компьютерных или

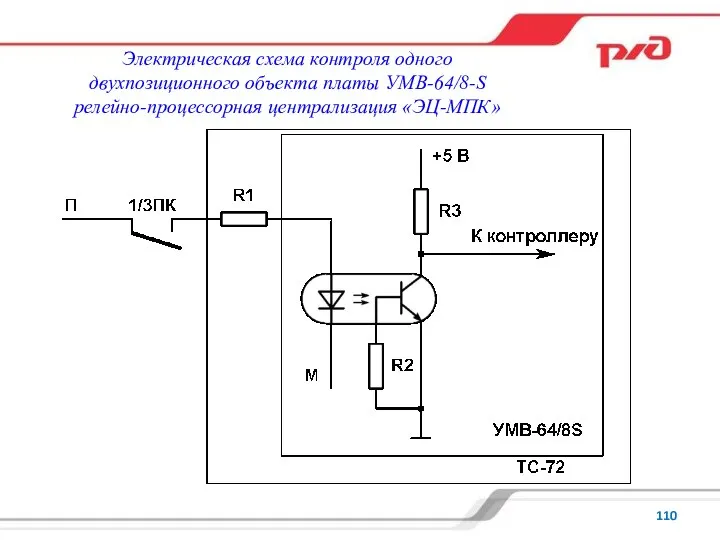

- 110. Электрическая схема контроля одного двухпозиционного объекта платы УМВ-64/8-S релейно-процессорная централизация «ЭЦ-МПК»

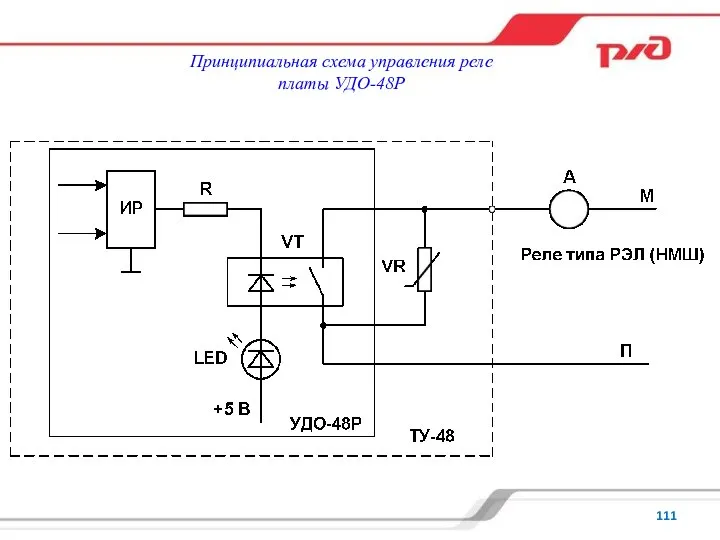

- 111. Принципиальная схема управления реле платы УДО-48P

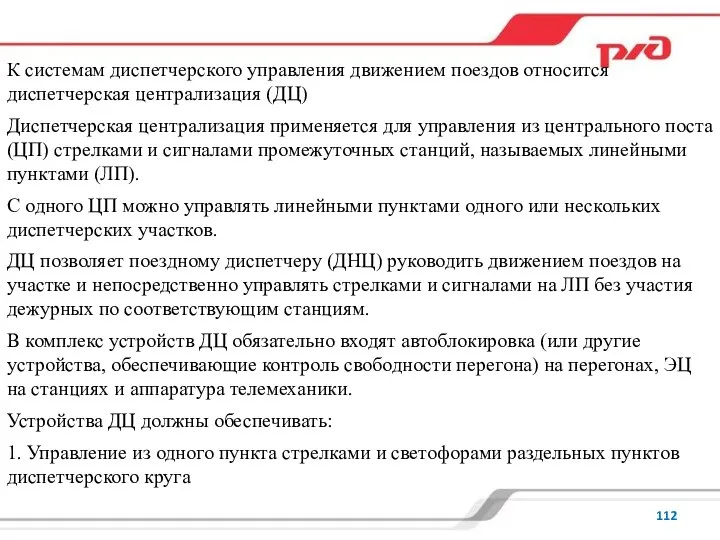

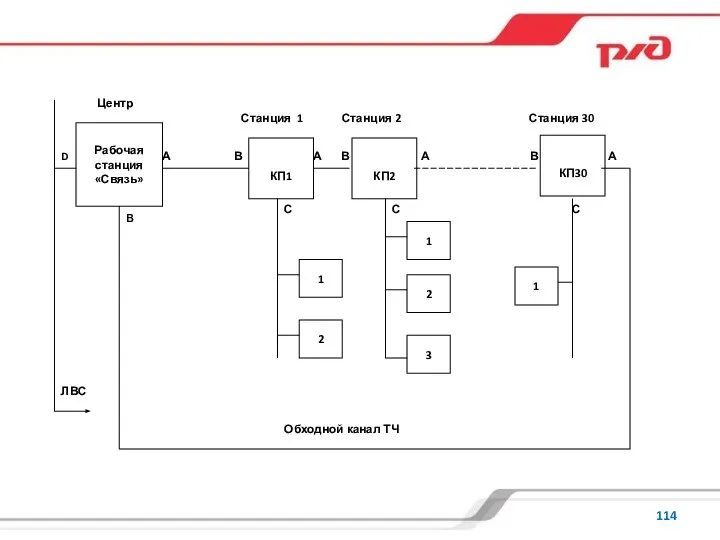

- 112. К системам диспетчерского управления движением поездов относится диспетчерская централизация (ДЦ) Диспетчерская централизация применяется для управления из

- 113. 2. Контроль положения и свободности стрелок и изолированных участков, занятости перегонов и путей на станциях, индикацию

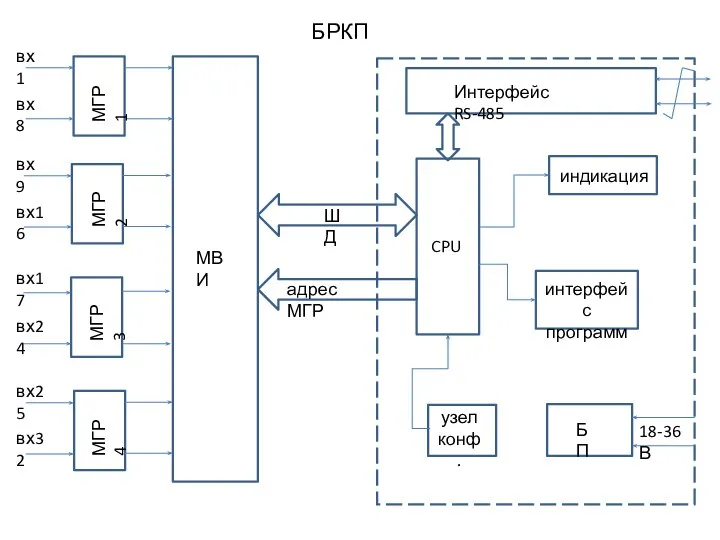

- 116. БРКП МГР 1 МГР 2 МГР 3 МГР 4 МВИ вх1 вх8 вх9 вх16 вх17 вх24

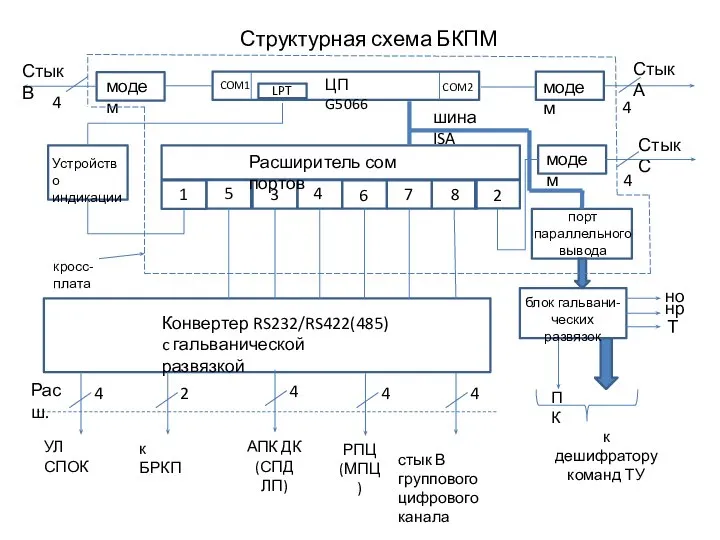

- 117. Структурная схема БКПМ ЦП G5066 COM1 COM2 модем модем модем Стык В 4 4 Стык А

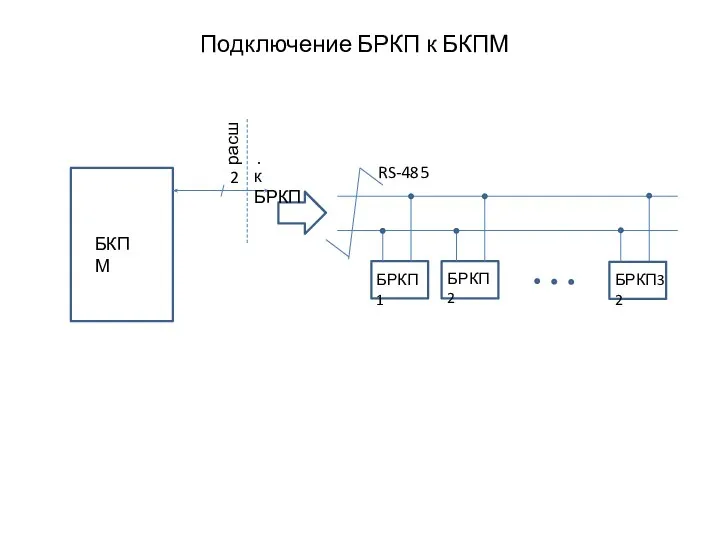

- 118. Подключение БРКП к БКПМ 2 БКПМ расш. RS-485 БРКП1 БРКП2 БРКП32 к БРКП

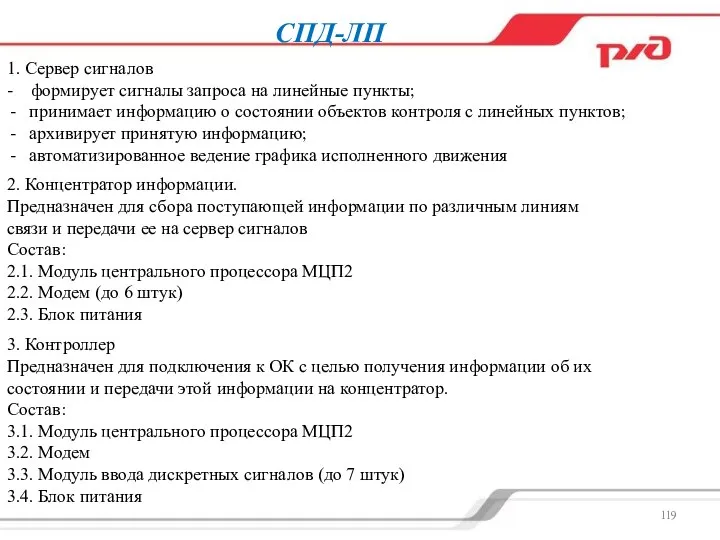

- 119. СПД-ЛП 1. Сервер сигналов - формирует сигналы запроса на линейные пункты; принимает информацию о состоянии объектов

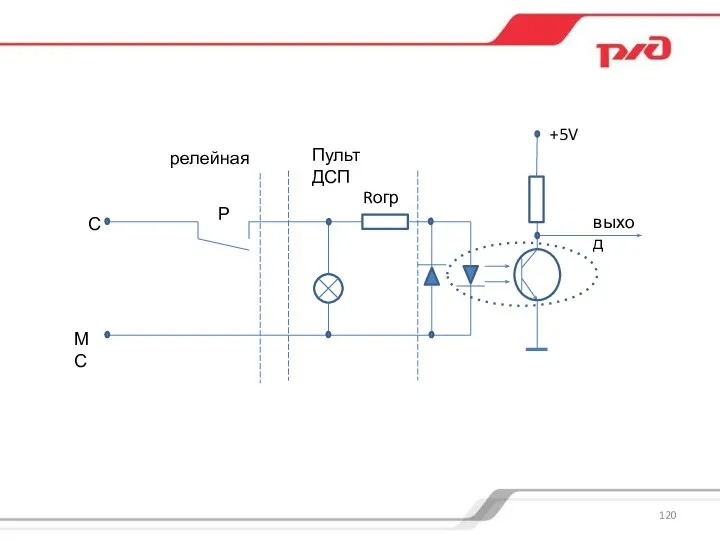

- 120. Р С МС релейная Пульт ДСП Rогр +5V выход

- 121. МЦП-2

- 122. Дешифратор адреса Х1 Х2 Z Y=X1 (X2=0) Y=1 (X2=1) Х1 Х2 & Y=X1*X2 Х1 Х2 1

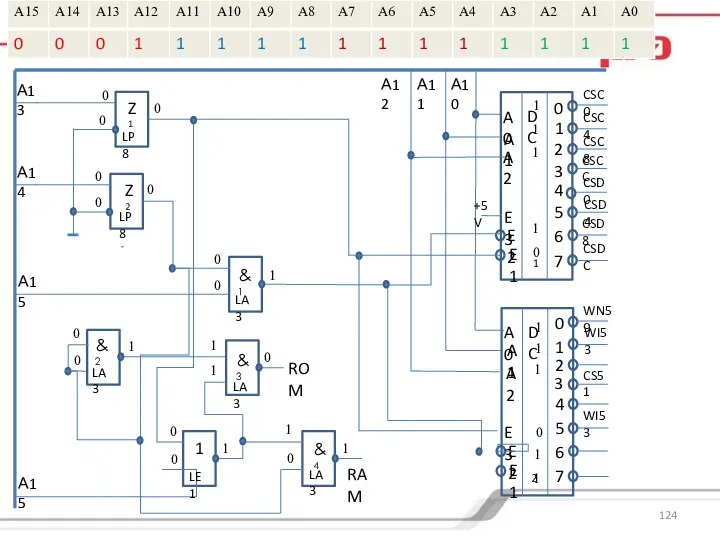

- 124. 1 1 1 1 1 1 1 0 0 1 1

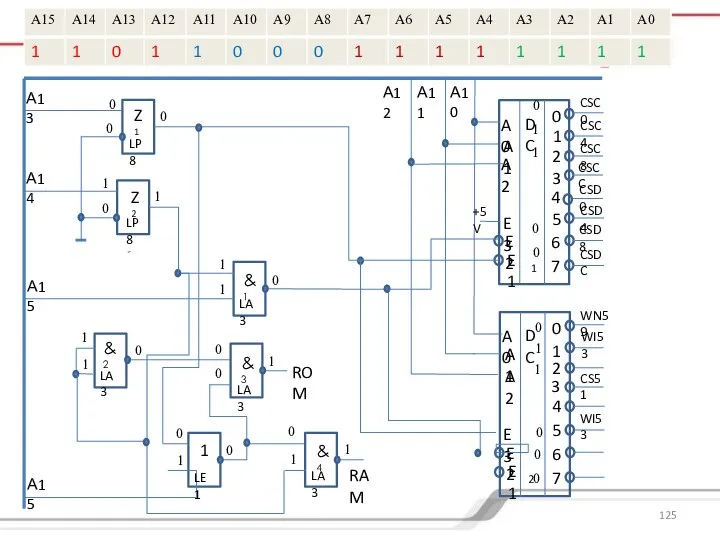

- 125. 0 1 1 0 1 1 0 0 0 0 0

- 127. Скачать презентацию

Негроидная раса

Негроидная раса  otnositelnost_dvizheniya

otnositelnost_dvizheniya Тайна природы света

Тайна природы света Учебная езда

Учебная езда Методики определения психологических состояний детей в детском саду

Методики определения психологических состояний детей в детском саду Имя числительное

Имя числительное Мир Информации

Мир Информации Системная динамика рыбы

Системная динамика рыбы Краны пролётного типа

Краны пролётного типа Тема 4. Право и государство.

Тема 4. Право и государство. Презентация волонтерства

Презентация волонтерства Уход и содержание хомячков

Уход и содержание хомячков Основные положения гражданского права Российской Федерации

Основные положения гражданского права Российской Федерации Основные структурные элементы системы государственного управления. Лекция № 4

Основные структурные элементы системы государственного управления. Лекция № 4 Электрические машины. Введение

Электрические машины. Введение Презентация на тему Облака 2 класс

Презентация на тему Облака 2 класс Натюрморт из предметов холодных цветов

Натюрморт из предметов холодных цветов Презентация на тему Абхазия

Презентация на тему Абхазия Произведения для оркестра М.И.Глинки

Произведения для оркестра М.И.Глинки Презентация на тему Физико-математическое кафе

Презентация на тему Физико-математическое кафе Новый 2015 год

Новый 2015 год Формирование информационно - коммуникационной компетентности участников образовательного процесса как условие получения соврем

Формирование информационно - коммуникационной компетентности участников образовательного процесса как условие получения соврем Лекция 3

Лекция 3 Основы геронтологии

Основы геронтологии  My incredible 3 day trip to

My incredible 3 day trip to  Сработанность и сплочённость коллектива

Сработанность и сплочённость коллектива Презентация на тему Слуховой анализатор (8 класс)

Презентация на тему Слуховой анализатор (8 класс) Дон в X-XII веках. Печенеги и половцы

Дон в X-XII веках. Печенеги и половцы