Обзор маршрутов проектирования прикладного программного обеспечения для ПЛИС/ASIC/SoC на основе языков С/С++

Содержание

- 2. Исследовательский центр СПбГУ ИТМО «Технологии автоматного программирования» Задачи обзора Сравнить маршруты проектирования ПЛИС/ASIC/SoC и показать их

- 3. Исследовательский центр СПбГУ ИТМО «Технологии автоматного программирования» Маршруты проектирования ПЛИС/ASIC/SoC Традиционный нисходящий маршрут проектирования Маршрут с

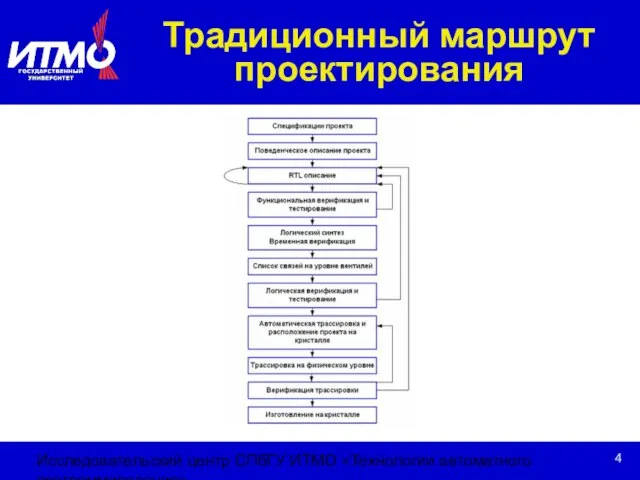

- 4. Исследовательский центр СПбГУ ИТМО «Технологии автоматного программирования» Традиционный маршрут проектирования

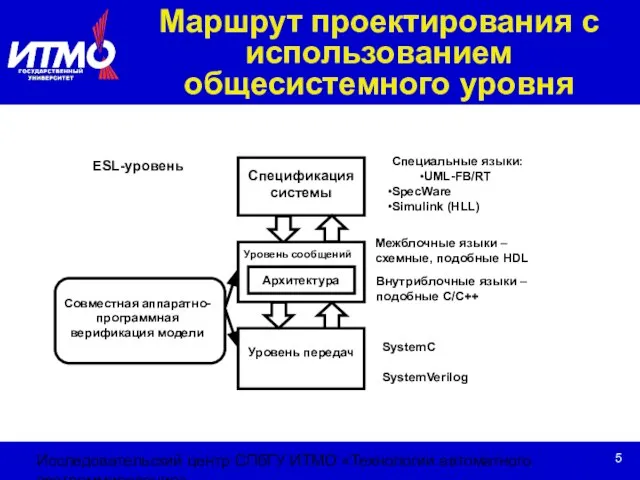

- 5. Исследовательский центр СПбГУ ИТМО «Технологии автоматного программирования» Маршрут проектирования с использованием общесистемного уровня Специальные языки: UML-FB/RT

- 6. Исследовательский центр СПбГУ ИТМО «Технологии автоматного программирования» Устраняется разрыв между алгоритмическим описанием системы и RTL-описанием Основная

- 7. Исследовательский центр СПбГУ ИТМО «Технологии автоматного программирования» Разработка библиотек на С/С++: SystemC и Cynlib Разработка специальных

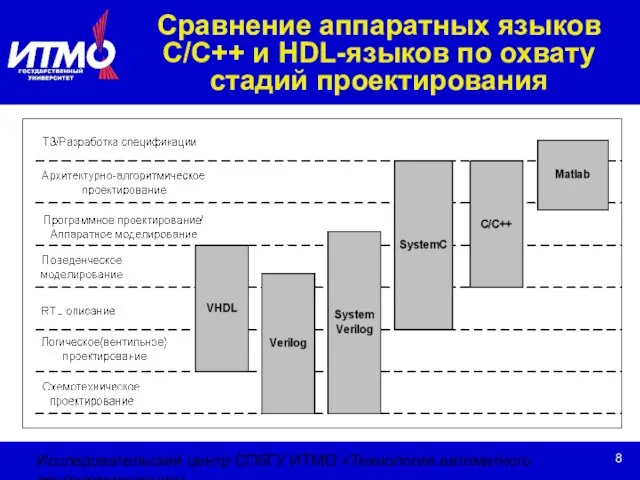

- 8. Исследовательский центр СПбГУ ИТМО «Технологии автоматного программирования» Сравнение аппаратных языков С/С++ и HDL-языков по охвату стадий

- 9. Исследовательский центр СПбГУ ИТМО «Технологии автоматного программирования» Этапы проектирования с использованием автоматного программирования: Использование UniMod для

- 10. Исследовательский центр СПбГУ ИТМО «Технологии автоматного программирования» Выводы Значительными преимуществами обладает маршрут проектирования на общесистемном уровне

- 11. Исследовательский центр СПбГУ ИТМО «Технологии автоматного программирования» Заключение Внедрение автоматического синтеза ПЛИС/ASIC/SoC непосредственно из C-описаний может

- 13. Скачать презентацию

Общественно-активная школа: эффективность и качество.

Общественно-активная школа: эффективность и качество. 197368

197368 С какво свързваш древногръцкото облекло?

С какво свързваш древногръцкото облекло? Презентация на тему Экономика и ее роль в обществе

Презентация на тему Экономика и ее роль в обществе Фотоальбом. Велосипеди

Фотоальбом. Велосипеди Узорочья Севера

Узорочья Севера Цветы для моей семьи

Цветы для моей семьи Открытые горные работы, их элементы и терминология

Открытые горные работы, их элементы и терминология Бизнес инсайт. Продуктивность как система

Бизнес инсайт. Продуктивность как система Где летит птица?

Где летит птица? Итоги 1 полугодия 2010-2011 уч.года

Итоги 1 полугодия 2010-2011 уч.года Творческий проект Кукла своими руками

Творческий проект Кукла своими руками Буквы О-Ё после шипящих и Ц

Буквы О-Ё после шипящих и Ц Формы взаимодействия с семьей (из опыта работы)

Формы взаимодействия с семьей (из опыта работы) КОММУНИКАТИВНАЯ ПОЛИТИКА ХОЛДИНГОВ

КОММУНИКАТИВНАЯ ПОЛИТИКА ХОЛДИНГОВ Государственное регулирование цен на лекарственные средства на региональном уровне и проблемы, возникающие в рамках действующег

Государственное регулирование цен на лекарственные средства на региональном уровне и проблемы, возникающие в рамках действующег Презентация прочитанной книги

Презентация прочитанной книги Филиал ООО компания Тензор. Сфера торгов

Филиал ООО компания Тензор. Сфера торгов Рекуперативный воздухонагреватель, с использованием жидких горючих отходов.

Рекуперативный воздухонагреватель, с использованием жидких горючих отходов. Интерактивно-аналитический онлайн-сервиса Калькулятор процедур

Интерактивно-аналитический онлайн-сервиса Калькулятор процедур Элла Фицджеральд - выдающаяся джазовая певица, актриса 1917-1996

Элла Фицджеральд - выдающаяся джазовая певица, актриса 1917-1996 Места на направление Товароведение

Места на направление Товароведение Праця неповнолітніх

Праця неповнолітніх Прямолинейное распространение света

Прямолинейное распространение света Документовед он-лайн сервис оформления документов Документы для регистрации общества с ограниченной ответственностью за 15 минут.

Документовед он-лайн сервис оформления документов Документы для регистрации общества с ограниченной ответственностью за 15 минут. Как правильно оформить презентацию и web-сайт?

Как правильно оформить презентацию и web-сайт? Капитализм XVIII века. Промышленный переворот в Англии

Капитализм XVIII века. Промышленный переворот в Англии Работать с молодёжью: как?

Работать с молодёжью: как?