Слайд 2Иерархии памяти

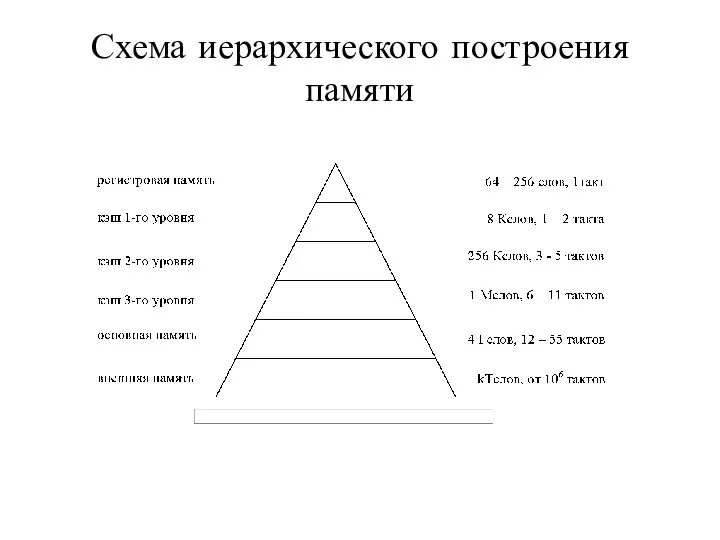

Идея иерархической (многоуровневой) организации памяти заключается в использовании на одном компьютере

нескольких уровней памяти, которые характеризуются разным временем доступа к памяти и объемом памяти. (Время доступа к памяти это время между операциями чтения/записи, которые выполняются по случайным адресам.) Основой для иерархической организации памяти служит принцип локальности ссылок во времени и в пространстве.

Локальность во времени состоит в том, что процессор многократно использует одни и те же команды и данные.

Локальность в пространстве состоит в том, что если программе нужен доступ к слову с адресом A, то скорее всего, следующие ссылки будут к адресам, расположенным по близости с адресом A.

Из свойства локальности ссылок следует, что в типичном вычислении обращения к памяти концентрируются вокруг небольшой области адресного пространства и более того, выборка идет по последовательным адресам. Время доступа к иерархически организованной памяти уменьшается благодаря следующему

сокращению количества обращений к оперативной памяти

совмещению обработки текущего фрагмента программы и пересылки данных из основной памяти в буферную память.

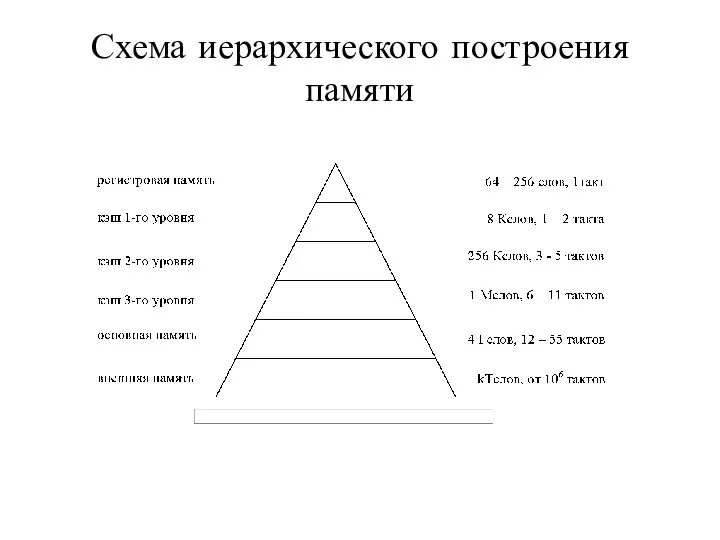

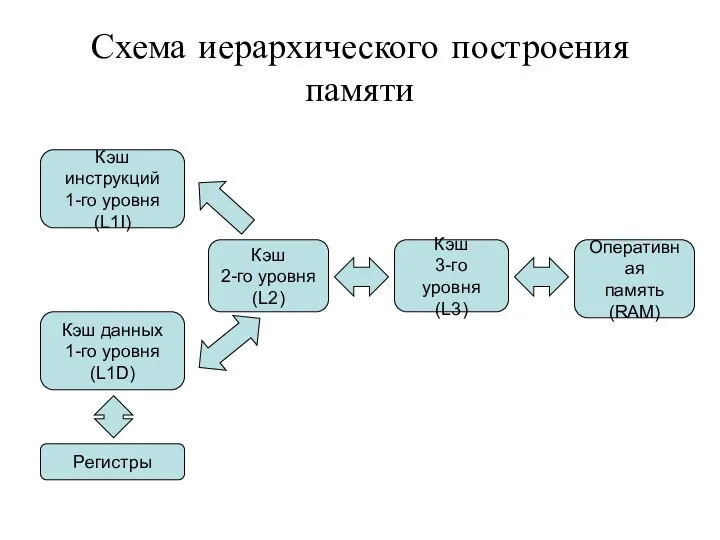

Слайд 3Схема иерархического построения памяти

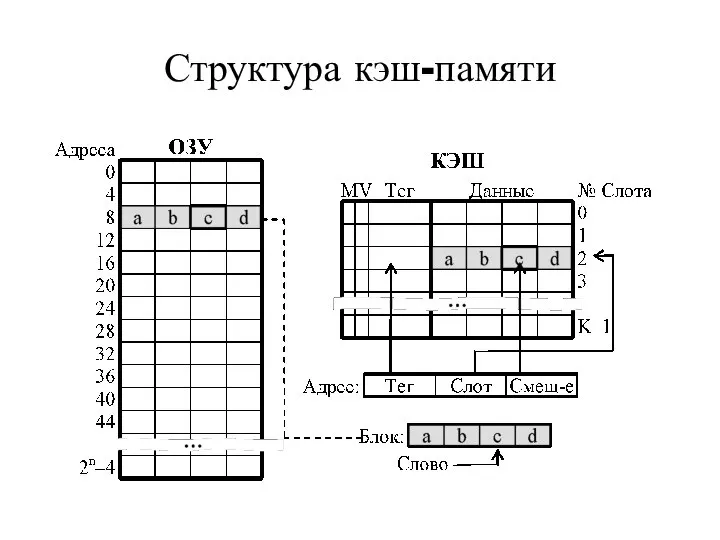

Слайд 5Организация кэш-памяти

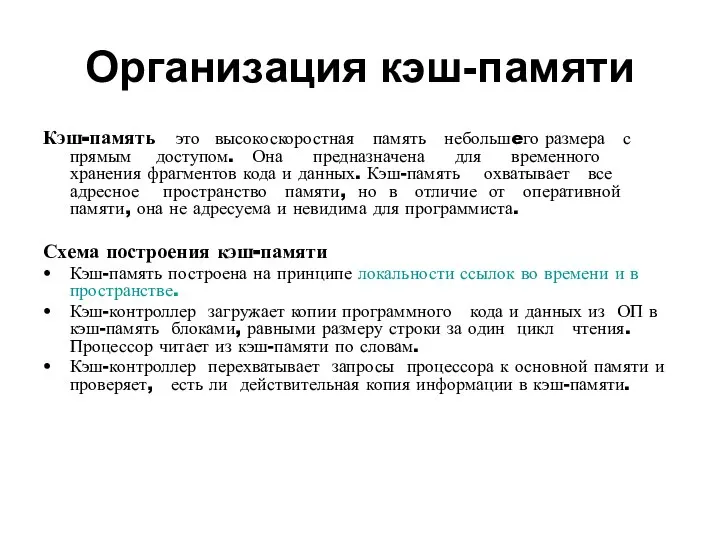

Кэш-память это высокоскоростная память небольшeго размера с прямым доступом. Она предназначена

для временного хранения фрагментов кода и данных. Кэш-память охватывает все адресное пространство памяти, но в отличие от оперативной памяти, она не адресуема и невидима для программиста.

Схема построения кэш-памяти

Кэш-память построена на принципе локальности ссылок во времени и в пространстве.

Кэш-контроллер загружает копии программного кода и данных из ОП в кэш-память блоками, равными размеру строки за один цикл чтения. Процессор читает из кэш-памяти по словам.

Кэш-контроллер перехватывает запросы процессора к основной памяти и проверяет, есть ли действительная копия информации в кэш-памяти.

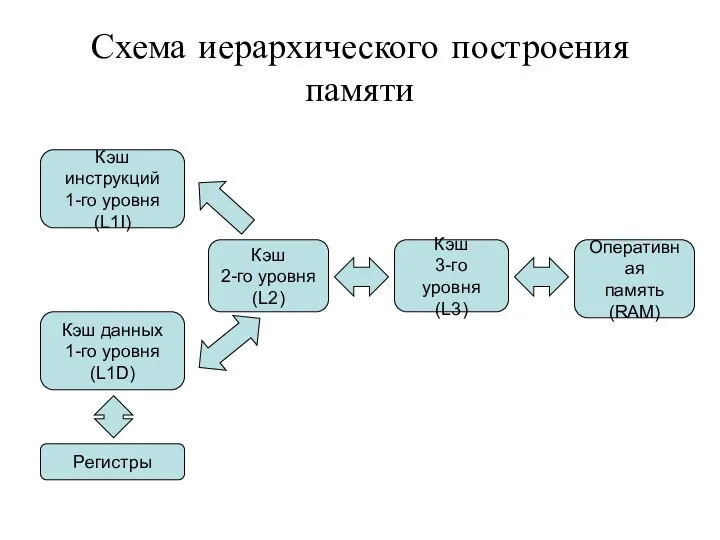

Слайд 7Схема иерархического построения памяти

Оперативная

память

(RAM)

Кэш

3-го уровня

(L3)

Кэш

2-го уровня

(L2)

Кэш инструкций

1-го уровня

(L1I)

Кэш данных

1-го

Слайд 8Организация кэш-памяти

Когда контроллер помещает данные в кэш- память?

Загрузка по требованию

(on demand).

Спекулятивная загрузка (speculative load). Алгоритм предполагает помещать данные в кэш-память задолго до того, как к ним произойдет реальное обращение. У кэш-контроллера есть несколько алгоритмов, которые указывают, какие ячейки памяти потребуются процессору в ближайшее

время.

Слайд 9Организация кэш-памяти

Когда контроллер выполняет поиск данных в памяти?

после фиксации

промаха (сквозной просмотр).

одновременно с поиском блока в кэш-памяти, в случае кэш-попадания, обращение к оперативной памяти прерывается (отложенный просмотр).

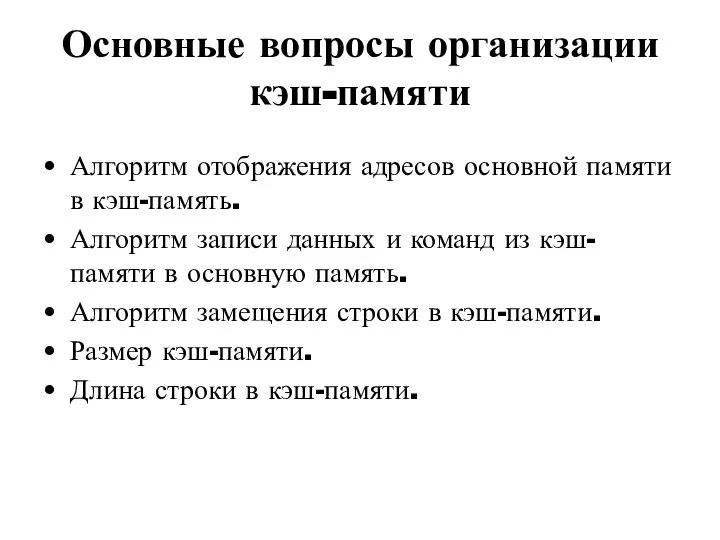

Слайд 10Основные вопросы организации кэш-памяти

Алгоритм отображения адресов основной памяти в кэш-память.

Алгоритм записи данных

и команд из кэш-памяти в основную память.

Алгоритм замещения строки в кэш-памяти.

Размер кэш-памяти.

Длина строки в кэш-памяти.

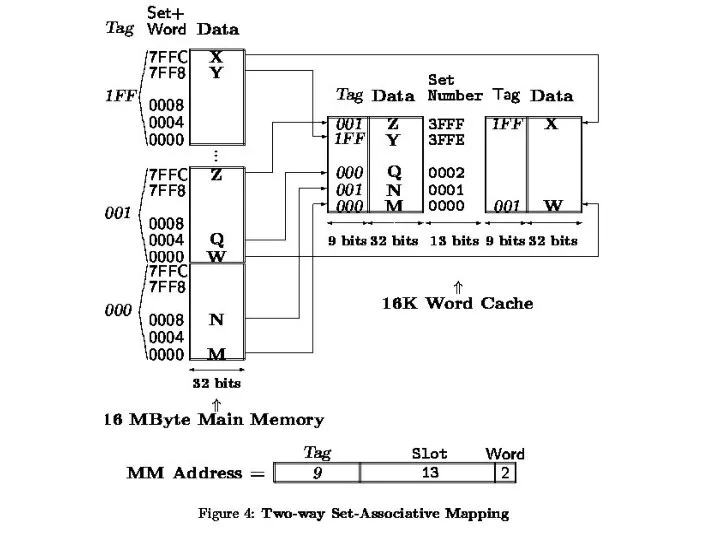

Слайд 11Алгоритмы отображения

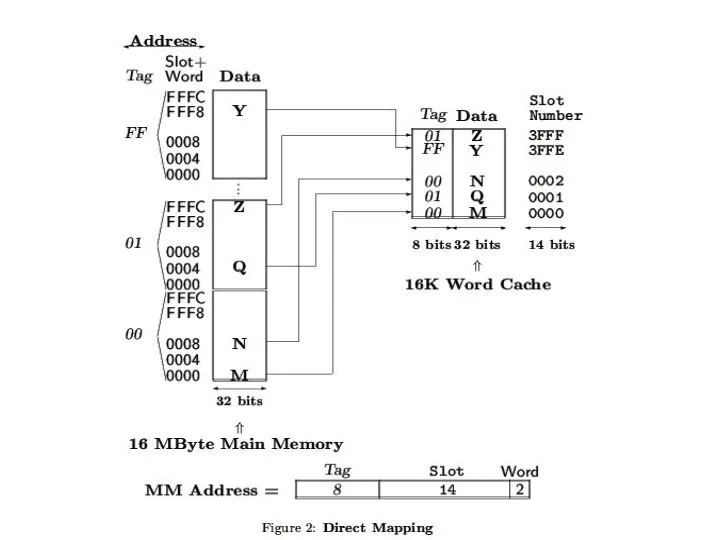

Прямой (direct mapping).

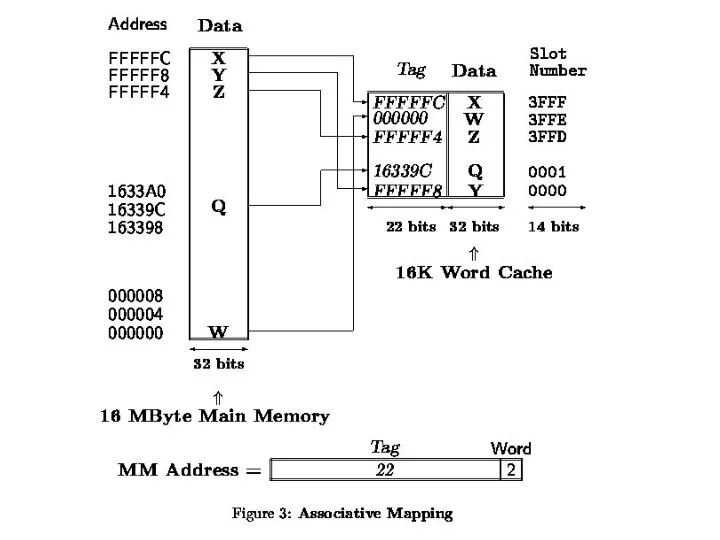

Ассоциативный (full associative mapping).

Множественно-ассоциативный (set-associative mapping).

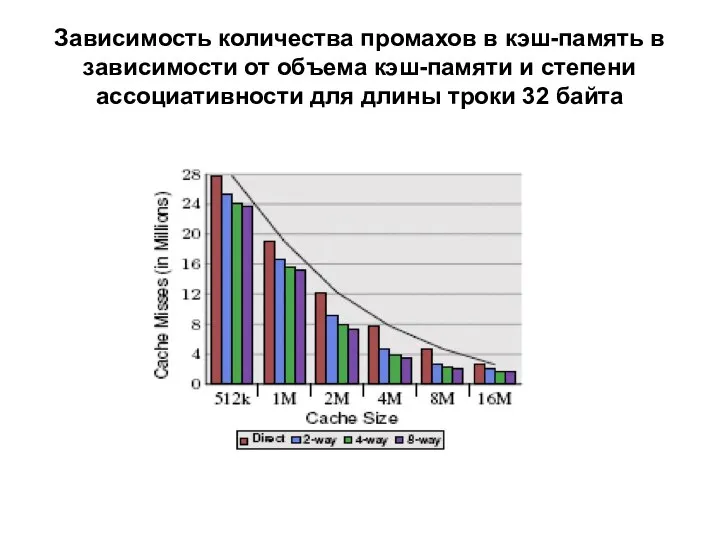

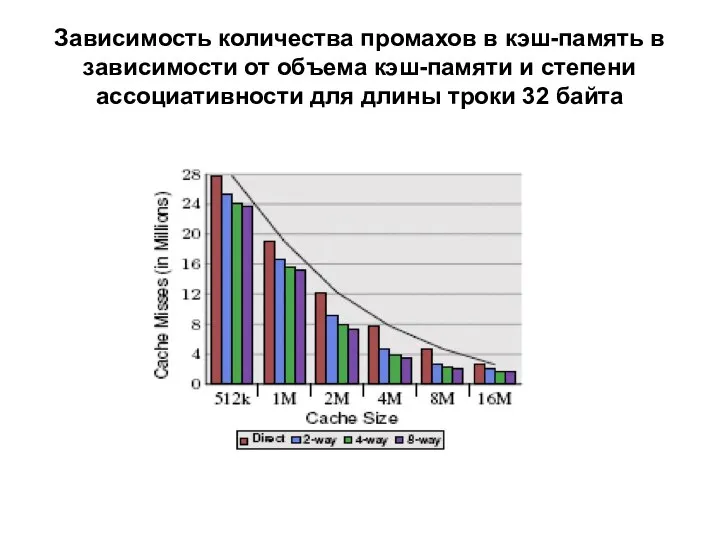

Слайд 14Зависимость количества промахов в кэш-память в зависимости от объема кэш-памяти и степени

ассоциативности для длины троки 32 байта

Слайд 16Алгоритмы записи

Сквозная запись (Write Through (WT)).

Сквозная запись с буферизацией (Write Combining).

Обратная

запись (Write Back (WB)).

Слайд 17Протокол MESI

M (Modified)– данные в строке модифицированы, но не переписаны в ОП.

Данные достоверны только в данной кэш-памяти.

E (Exclusive)-- данные в строке совпадают с аналогичной строкой в ОП, но отсутствуют в других кэшах.

S (Shared) – данные строки кэш-памяти не совпадают с данными аналогичной строкой в ОП и могут присутствовать в другой кэш-памяти.

I (Invalid) – строка не содержит достоверных данных.

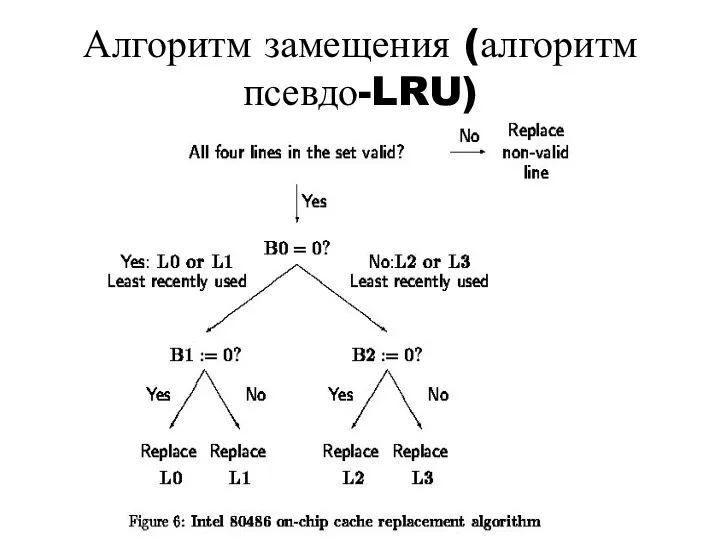

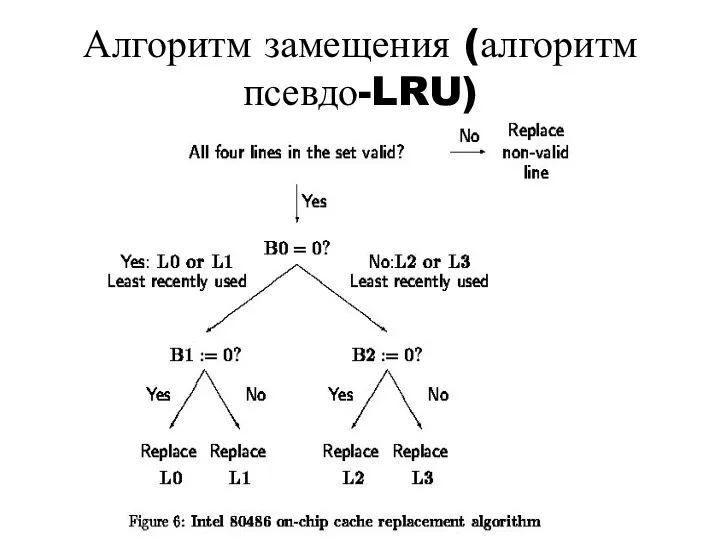

Слайд 18Алгоритм замещения (алгоритм псевдо-LRU)

Слайд 19Каким должен быть размер линии кэш-памяти?

Размер линии должен быть как минимум в

ширину канала памяти

Большой размер

-- Более эффективное использование канала памяти при последовательном доступе

-- Позволяет уменьшать “ассоциативность” кэша и количество линий

Маленький размер

-- Более эффективное использование канала памяти при произвольном доступе

-- Заполнение можно делать за одну транзакцию к памяти

Н. М. Карамзин и Симбирск

Н. М. Карамзин и Симбирск Федеральный государственный образовательный стандарт дошкольного образования от 17.10.2013 № 1155

Федеральный государственный образовательный стандарт дошкольного образования от 17.10.2013 № 1155 [Название]

[Название] Презентация на тему Образование в Японии

Презентация на тему Образование в Японии Междисциплинарная интеграция с использованием информационных технологий.

Междисциплинарная интеграция с использованием информационных технологий. МИФ или РЕАЛЬНОСТЬ?

МИФ или РЕАЛЬНОСТЬ? Исследователь и творец: какой он? ( 3 Межрегиональная конференция «Организация исследовательской деятельности детей и молодёжи: п

Исследователь и творец: какой он? ( 3 Межрегиональная конференция «Организация исследовательской деятельности детей и молодёжи: п Турция

Турция Нас ждет глобальное потепление! Льды растают и затопят низменные участки земли

Нас ждет глобальное потепление! Льды растают и затопят низменные участки земли Сказки М.Е. Салтыкова-Щедрина.

Сказки М.Е. Салтыкова-Щедрина. Умножение на 4

Умножение на 4 Загадка смерти Александра I

Загадка смерти Александра I Тушь Extreme Fashion

Тушь Extreme Fashion МАСТЕР-КЛАСС Критериально-ориентированное педагогическое тестирование Модуль № 2. Внутренняя экспертизатестов

МАСТЕР-КЛАСС Критериально-ориентированное педагогическое тестирование Модуль № 2. Внутренняя экспертизатестов Australian financial services consulting company (fintech)

Australian financial services consulting company (fintech) Афиши к спектаклю по драме А. Островского Гроза

Афиши к спектаклю по драме А. Островского Гроза Мастер - класс по нетрадиционным техникам рисования

Мастер - класс по нетрадиционным техникам рисования 1 сентября – День знаний

1 сентября – День знаний Физика и искусство

Физика и искусство Автомобильная промышленность

Автомобильная промышленность Арт менеджмент

Арт менеджмент  Бакалаврская работа. Анализ проектного финансирования как средства стимулирования экономического роста региона

Бакалаврская работа. Анализ проектного финансирования как средства стимулирования экономического роста региона Диагностика электоральной ситуации перед выборами в Государственную Думу РФПо заказу РЦОИТ при ЦИК РФ

Диагностика электоральной ситуации перед выборами в Государственную Думу РФПо заказу РЦОИТ при ЦИК РФ РОЛЬ КАРТОГРАФИИ В РАЗВИТИИ ОБЩЕСТВА

РОЛЬ КАРТОГРАФИИ В РАЗВИТИИ ОБЩЕСТВА о картофеле

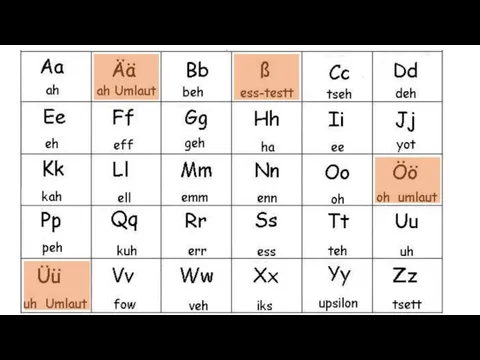

о картофеле алфавит + звуки

алфавит + звуки Нарезание резьбы

Нарезание резьбы INFECTION CONTROL IN ICU

INFECTION CONTROL IN ICU