Содержание

- 2. Литература «Выполнение междисциплинарного задания в цепочке дисциплин «Языки описания цифровых схем и систем», «Лингвистические средства САПР»,

- 3. Алфавит. Представление чисел. 0 – логический ноль; 1 – логическая единица; Z – высокий импеданс; X

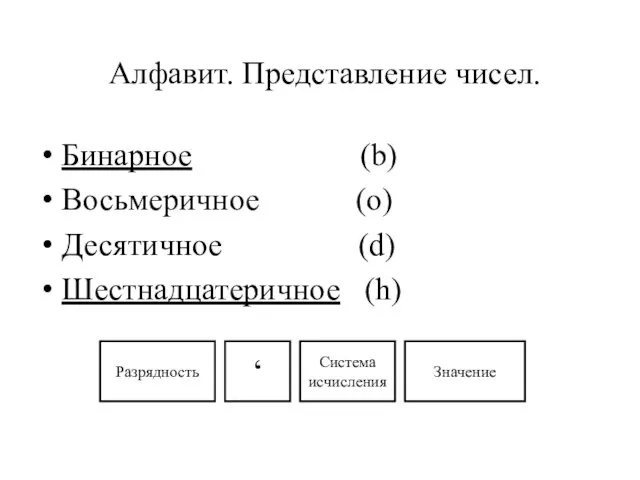

- 4. Алфавит. Представление чисел. Бинарное (b) Восьмеричное (o) Десятичное (d) Шестнадцатеричное (h) Разрядность ‘ Система исчисления Значение

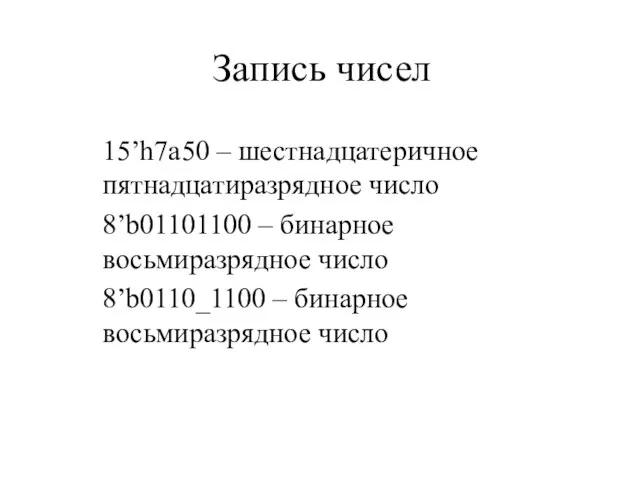

- 5. Запись чисел 15’h7a50 – шестнадцатеричное пятнадцатиразрядное число 8’b01101100 – бинарное восьмиразрядное число 8’b0110_1100 – бинарное восьмиразрядное

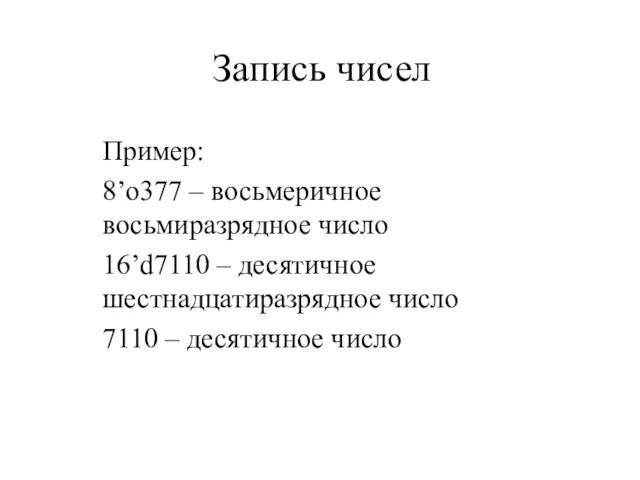

- 6. Запись чисел Пример: 8’o377 – восьмеричное восьмиразрядное число 16’d7110 – десятичное шестнадцатиразрядное число 7110 – десятичное

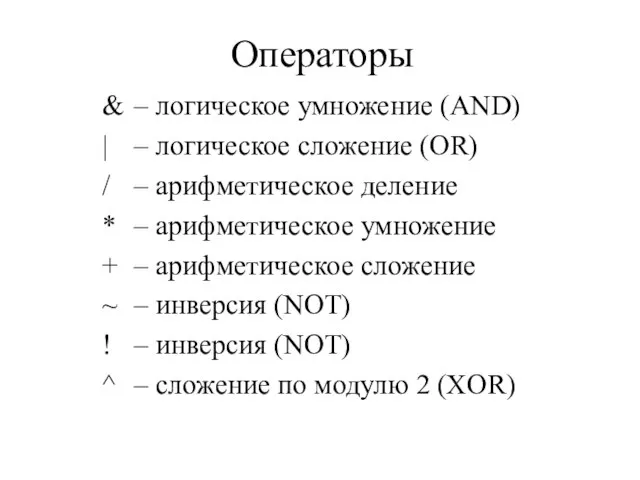

- 7. Операторы & – логическое умножение (AND) | – логическое сложение (OR) / – арифметическое деление *

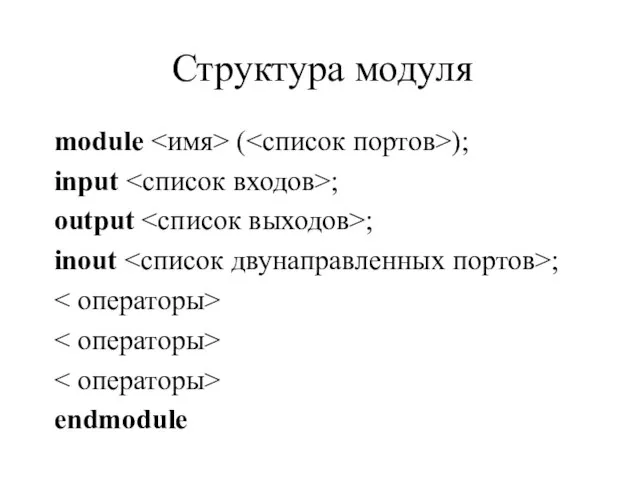

- 8. Структура модуля module ( ); input ; output ; inout ; endmodule

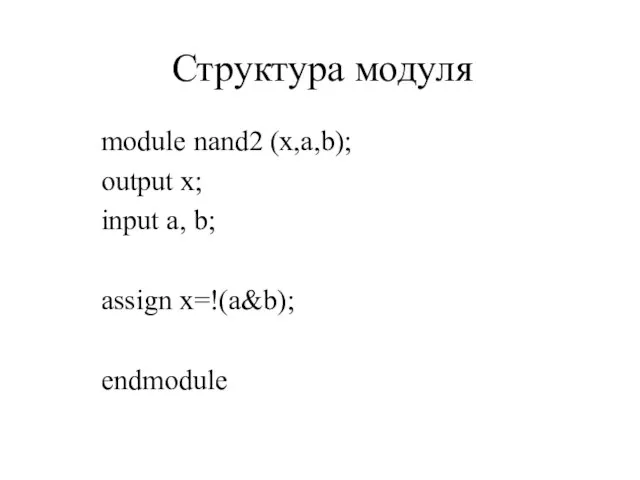

- 9. Структура модуля module nand2 (x,a,b); output x; input a, b; assign x=!(a&b); endmodule

- 10. Переменные wire Значение переменной меняется сразу же после изменения какого- либо аргумента. Используется для описания комбинационной

- 11. Переменные wire Используется только в составе конструкции “assign”. wire a, b, c; assign c = !(a

- 12. Переменные reg Присвоение нового значения переменной происходит после выполнения указанных условий. Используется для описания как комбинационной

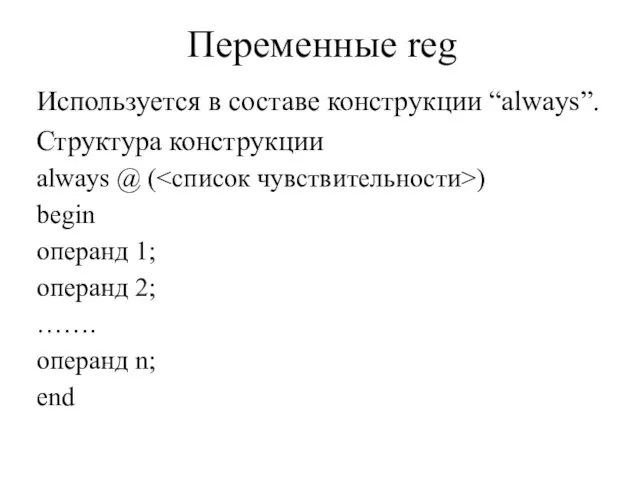

- 13. Переменные reg Используется в составе конструкции “always”. Структура конструкции always @ ( ) begin операнд 1;

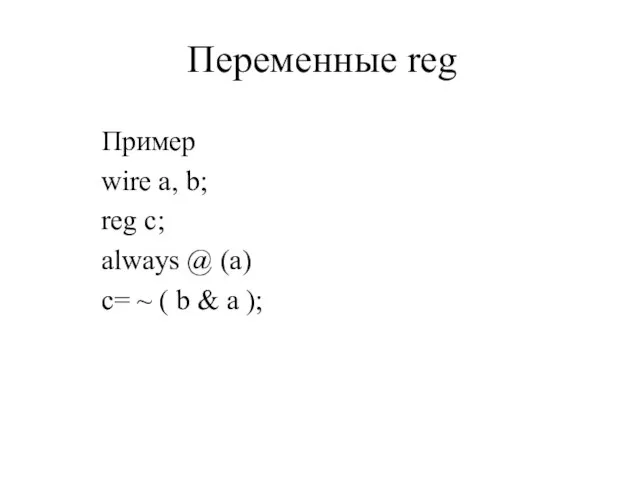

- 14. Переменные reg Пример wire a, b; reg c; always @ (a) c= ~ ( b &

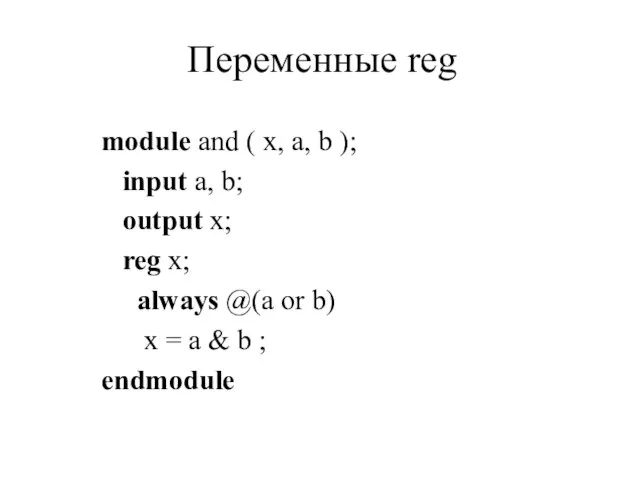

- 15. Переменные reg module and ( x, a, b ); input a, b; output x; reg x;

- 16. Уровни абстракции – поведенческий ( behavioral ); – вентильный ( gate ); – уровень регистровых передач

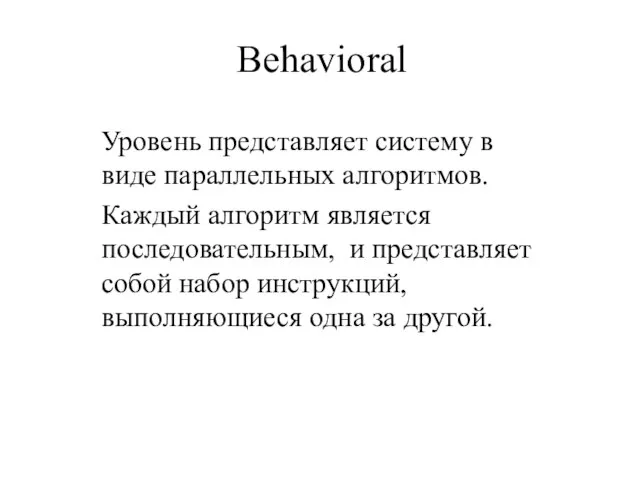

- 17. Behavioral Уровень представляет систему в виде параллельных алгоритмов. Каждый алгоритм является последовательным, и представляет собой набор

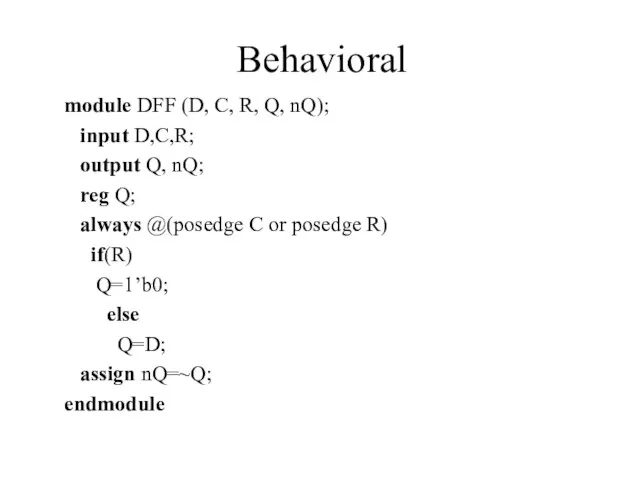

- 18. Behavioral module DFF (D, C, R, Q, nQ); input D,C,R; output Q, nQ; reg Q; always

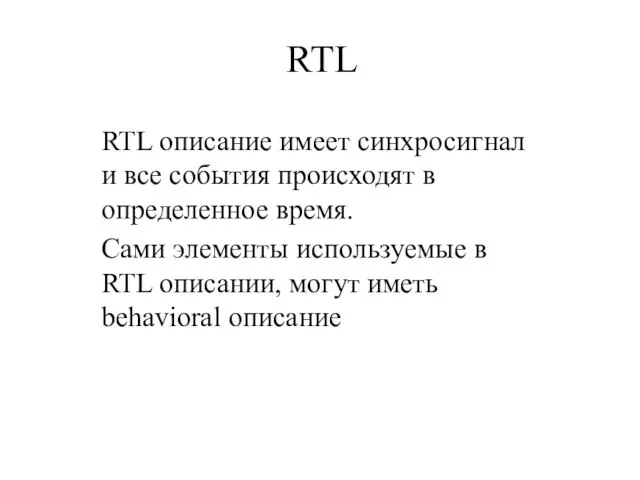

- 19. RTL RTL описание имеет синхросигнал и все события происходят в определенное время. Сами элементы используемые в

- 20. RTL module D_REG (D, C, R, Q); input C, R; input [7:0] D; output [7:0] Q;

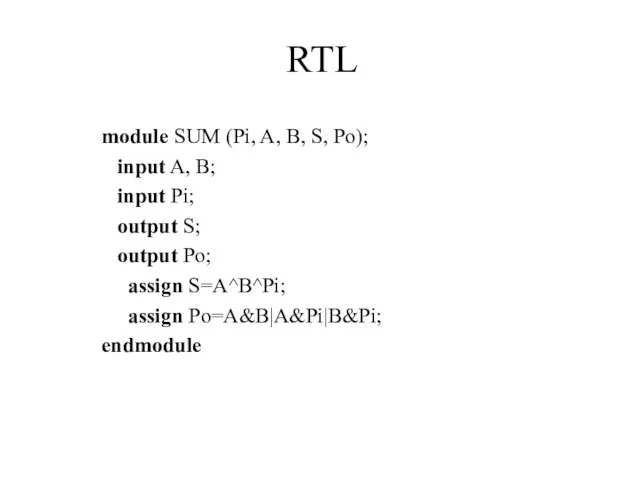

- 21. RTL module SUM (Pi, A, B, S, Po); input A, B; input Pi; output S; output

- 22. RTL `include “../SUM.v” module SUMM (Pi, A, B, S, Po); input [7:0] A, B; input Pi;

- 23. RTL `include “../SUMM.v” `include “../D_REG.v” module COUNT (C,R,Q); input C,R; output [7:0] Q; wire [7:0] D;

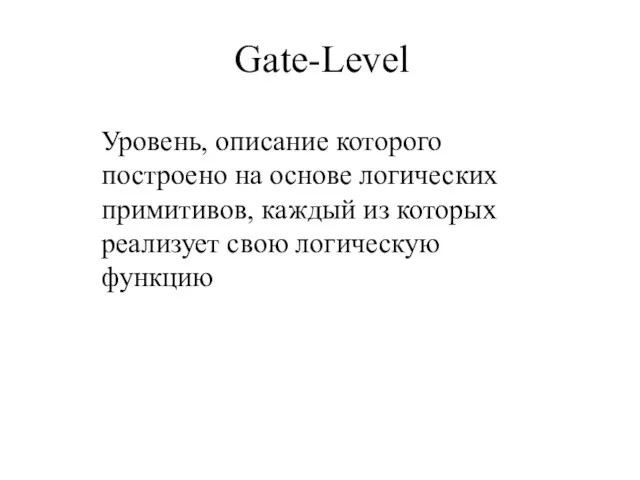

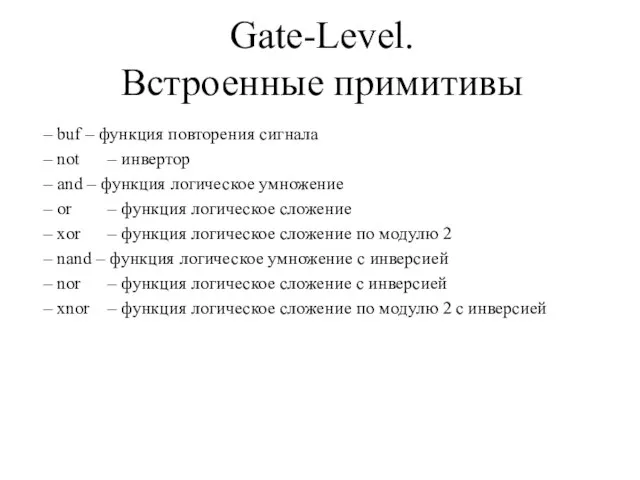

- 24. Gate-Level Уровень, описание которого построено на основе логических примитивов, каждый из которых реализует свою логическую функцию

- 25. Gate-Level. Встроенные примитивы – buf – функция повторения сигнала – not – инвертор – and –

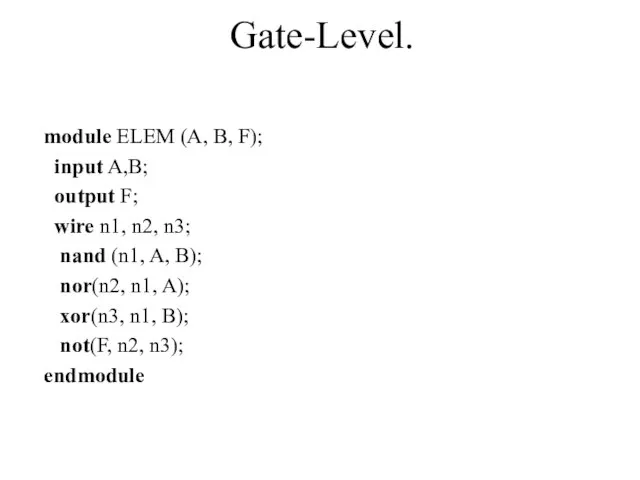

- 26. Gate-Level. module ELEM (A, B, F); input A,B; output F; wire n1, n2, n3; nand (n1,

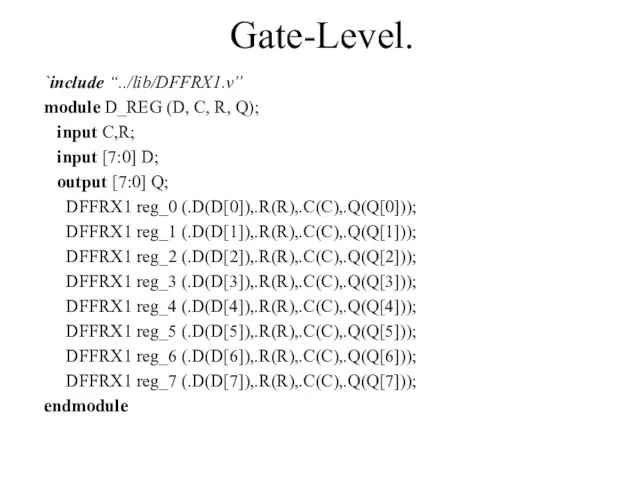

- 27. Gate-Level. `include “../lib/DFFRX1.v” module D_REG (D, C, R, Q); input C,R; input [7:0] D; output [7:0]

- 29. Скачать презентацию

![RTL module D_REG (D, C, R, Q); input C, R; input [7:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/380649/slide-19.jpg)

![RTL `include “../SUM.v” module SUMM (Pi, A, B, S, Po); input [7:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/380649/slide-21.jpg)

![RTL `include “../SUMM.v” `include “../D_REG.v” module COUNT (C,R,Q); input C,R; output [7:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/380649/slide-22.jpg)

Кино. Пираты Карибского моря

Кино. Пираты Карибского моря Nancy Langton and Stephen P. Robbins

Nancy Langton and Stephen P. Robbins Презентация на тему Использование информационных технологий на уроках химии

Презентация на тему Использование информационных технологий на уроках химии  КАЛЕНДАРЬЗНАМЕНАТЕЛЬНЫХ ДАТ (НА МАРТ 2012 ГОДА)

КАЛЕНДАРЬЗНАМЕНАТЕЛЬНЫХ ДАТ (НА МАРТ 2012 ГОДА) Психические познавательные процессы человека

Психические познавательные процессы человека Пресмыкающиеся

Пресмыкающиеся Медтодологія і організація наукових досліджень в освіті

Медтодологія і організація наукових досліджень в освіті Ведение пациентов с ВИЧ и вирусом гепатита С коинфекцией. Что нового? Мединар АМСЗ (совместно с компанией МСД Фармасьютикалс), 19 д

Ведение пациентов с ВИЧ и вирусом гепатита С коинфекцией. Что нового? Мединар АМСЗ (совместно с компанией МСД Фармасьютикалс), 19 д Звезды качества

Звезды качества Нормативный аспект организации работы по благоустройству территории образовательного учреждения

Нормативный аспект организации работы по благоустройству территории образовательного учреждения Математика на шахматной доске

Математика на шахматной доске Трансформаторы тока и напряжения

Трансформаторы тока и напряжения Умножение одночленов. Возведение одночленов в степень.

Умножение одночленов. Возведение одночленов в степень. Автор: Копытина Н.А., учитель информатики Г(О)ОУ НПО ПУ № 17 с. Хлевное Хлевенского района Липецкой области

Автор: Копытина Н.А., учитель информатики Г(О)ОУ НПО ПУ № 17 с. Хлевное Хлевенского района Липецкой области Итоги воспитательной работы за I полугодие 2010 – 2011 учебного года

Итоги воспитательной работы за I полугодие 2010 – 2011 учебного года Леттеринг и его виды

Леттеринг и его виды Магия струн

Магия струн Способы хранения мяса

Способы хранения мяса Амангелді

Амангелді « Коллективизация сельского хозяйства и ее результаты. Цена рывка.»

« Коллективизация сельского хозяйства и ее результаты. Цена рывка.» Синхроный двигатель

Синхроный двигатель Игровая зависимость

Игровая зависимость Энергосбережение для собственников

Энергосбережение для собственников Пейзаж

Пейзаж Презентация на тему Профессии 2 класс

Презентация на тему Профессии 2 класс Презентация на тему Какая бывает промышленность

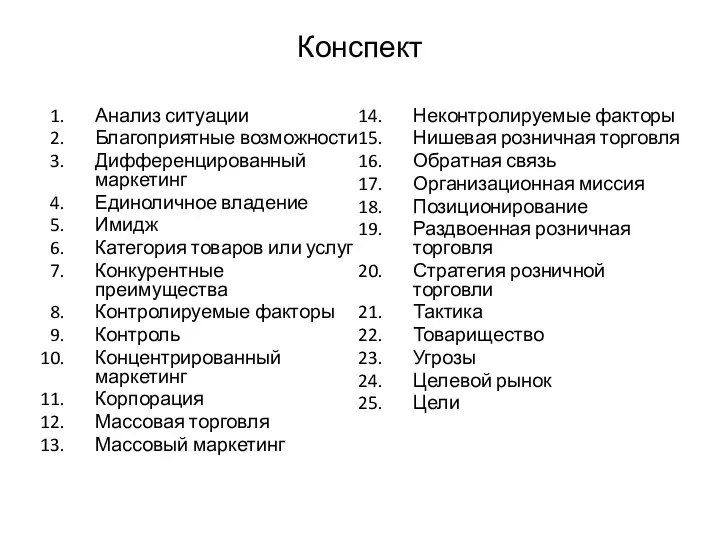

Презентация на тему Какая бывает промышленность Конспект. Анализ ситуации

Конспект. Анализ ситуации Синдром дефицита внимания и гиперактивности (СДВГ)

Синдром дефицита внимания и гиперактивности (СДВГ)