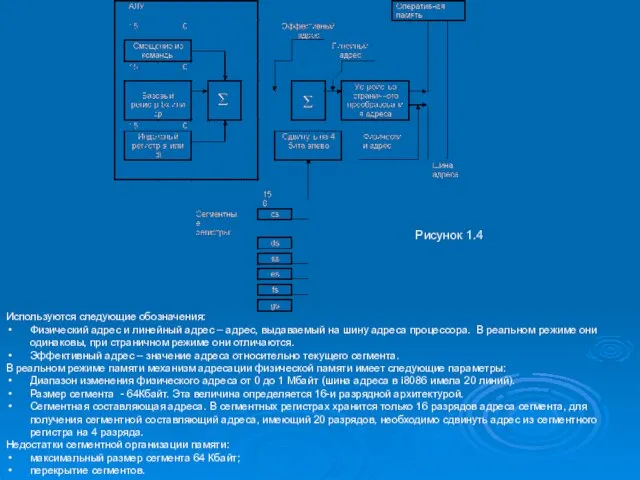

адреса процессора. В реальном режиме они одинаковы, при страничном режиме они отличаются.

Эффективный адрес – значение адреса относительно текущего сегмента.

В реальном режиме памяти механизм адресации физической памяти имеет следующие параметры:

Диапазон изменения физического адреса от 0 до 1 Мбайт (шина адреса в i8086 имела 20 линий).

Размер сегмента - 64Кбайт. Эта величина определяется 16-и разрядной архитектурой.

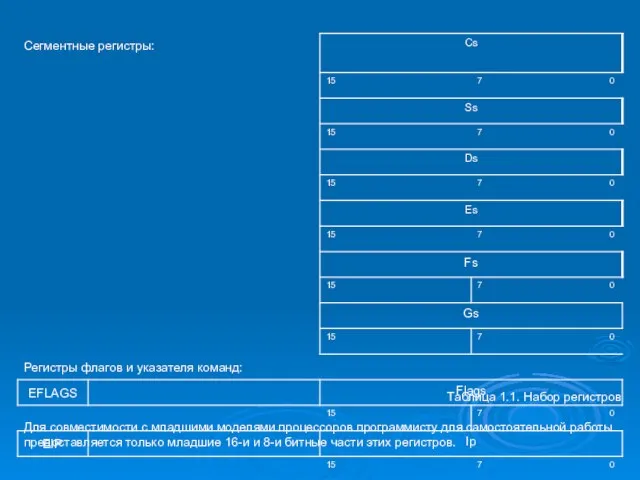

Сегментная составляющая адреса. В сегментных регистрах хранится только 16 разрядов адреса сегмента, для получения сегментной составляющий адреса, имеющий 20 разрядов, необходимо сдвинуть адрес из сегментного регистра на 4 разряда.

Недостатки сегментной организации памяти:

максимальный размер сегмента 64 Кбайт;

перекрытие сегментов.

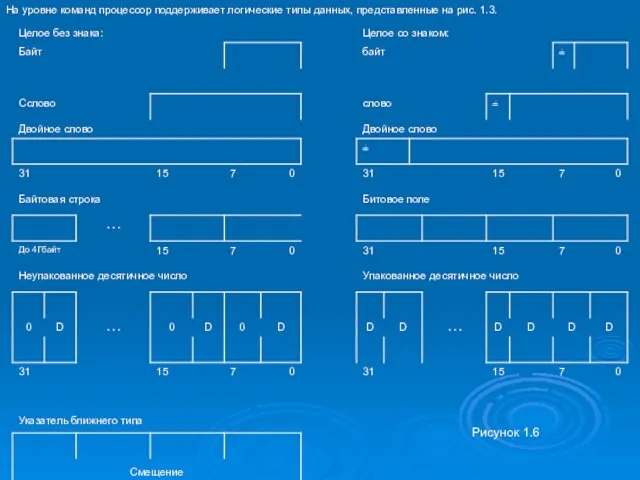

Рисунок 1.4

Pascal Работа с числовыми данными Целочисленные переменные

Pascal Работа с числовыми данными Целочисленные переменные 2_Презентация_теор_мат+

2_Презентация_теор_мат+ Использование игровых упражнений для коррекции и активизации познавательной деятельности

Использование игровых упражнений для коррекции и активизации познавательной деятельности Звено 2 Звено 1 и звено 3 Тестирование за компьютером.

Звено 2 Звено 1 и звено 3 Тестирование за компьютером. Презентация на тему Правописание безударных гласных в слове

Презентация на тему Правописание безударных гласных в слове ВСК Страховой дом. Согласование актов в ЛКА. Акты в личном кабинете агента

ВСК Страховой дом. Согласование актов в ЛКА. Акты в личном кабинете агента «Толерантность»

«Толерантность» Задачи на проценты 8 класс

Задачи на проценты 8 класс О ходе строительства Федерального высокотехнологичного центра медицинской радиологии в г. Димитровграде ФМБА РОССИИ Докладчик: Р

О ходе строительства Федерального высокотехнологичного центра медицинской радиологии в г. Димитровграде ФМБА РОССИИ Докладчик: Р Чернобыльский заповедник

Чернобыльский заповедник Создание единого информационного пространства розничной сети

Создание единого информационного пространства розничной сети Превратим Васюки в Нью-Москву

Превратим Васюки в Нью-Москву Профсоюз. Сотрудничество более 20 лет

Профсоюз. Сотрудничество более 20 лет Форматирование – создание физической и логической структуры диска

Форматирование – создание физической и логической структуры диска Тема урока:

Тема урока: Строение клетки

Строение клетки Моя родословная 2 класс

Моя родословная 2 класс Портрет. Великие портретисты

Портрет. Великие портретисты Отчет по проделанной работе

Отчет по проделанной работе Проект№2 дистанционное обучение за и против

Проект№2 дистанционное обучение за и против Русский язык – один из развитых языков мира.

Русский язык – один из развитых языков мира. Представление методической темы: Общие методические рекомендации к решению задач по генетике.

Представление методической темы: Общие методические рекомендации к решению задач по генетике. Бенчмаркетинг: основные понятия и процесс реализации

Бенчмаркетинг: основные понятия и процесс реализации Теория менеджмента

Теория менеджмента Буквы О, А на конце наречий с приставками из, до, с, за, на, в

Буквы О, А на конце наречий с приставками из, до, с, за, на, в Серебряный браслет

Серебряный браслет Образование единого государства – России. Иван III

Образование единого государства – России. Иван III Система работы по физике с использованием ИКТ.Опыт работы на сайте Физика.ру

Система работы по физике с использованием ИКТ.Опыт работы на сайте Физика.ру