Содержание

- 2. Введение Подсистемы ЭВМ: Память: Кэш, Виртуальная память Системная шина Подсистема прерываний Система ввода-вывода Большинство из этих

- 3. Вычислительная машина с одной шиной

- 4. Шинная организация ЭВМ Системная шина обеспечивает простой и гибкий механизм взаимодействия между подсистемами ЭВМ. Для обеспечения

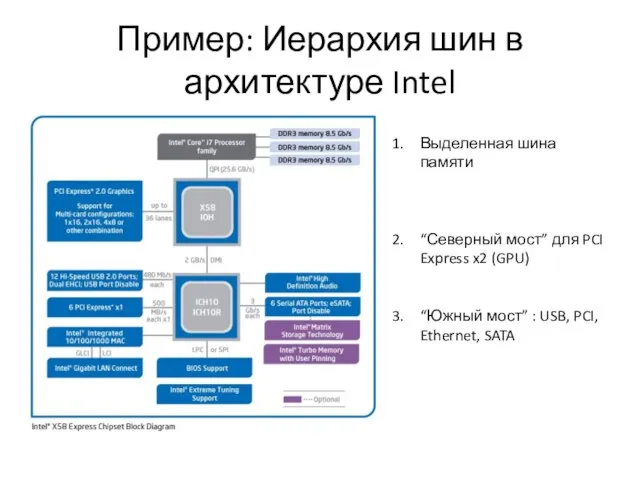

- 5. Пример: Иерархия шин в архитектуре Intel Выделенная шина памяти “Северный мост” для PCI Express x2 (GPU)

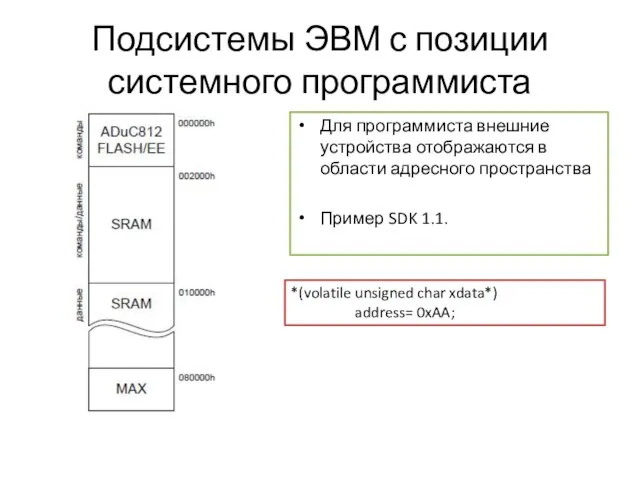

- 6. Подсистемы ЭВМ с позиции системного программиста Для программиста внешние устройства отображаются в области адресного пространства Пример

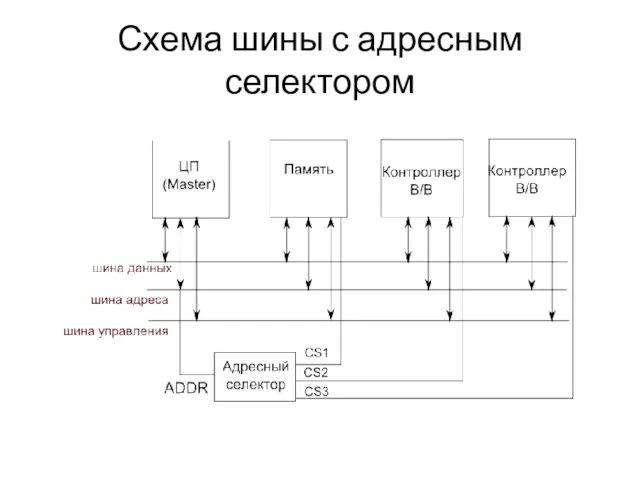

- 7. Схема шины с адресным селектором

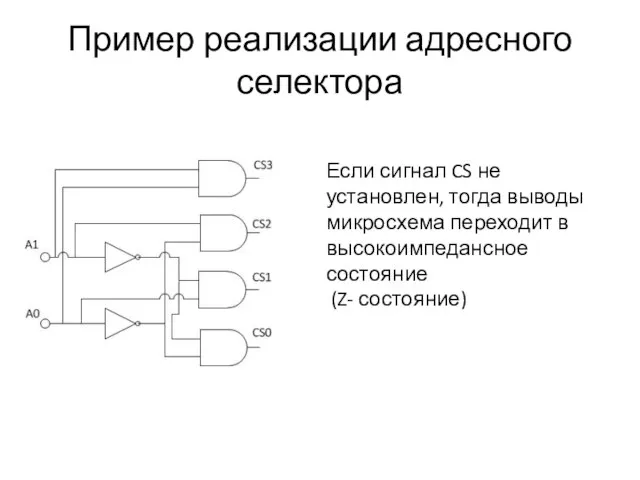

- 8. Пример реализации адресного селектора Если сигнал CS не установлен, тогда выводы микросхема переходит в высокоимпедансное состояние

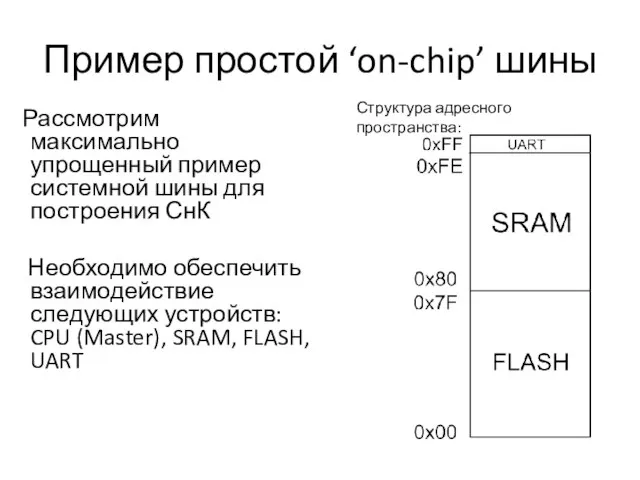

- 9. Пример простой ‘on-chip’ шины Рассмотрим максимально упрощенный пример системной шины для построения СнК Необходимо обеспечить взаимодействие

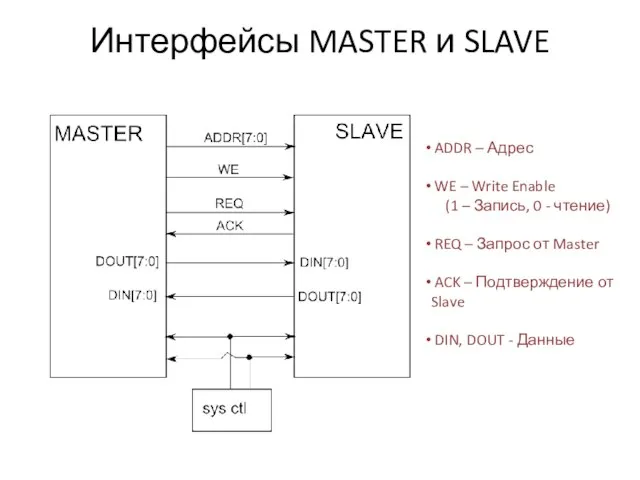

- 10. Интерфейсы MASTER и SLAVE ADDR – Адрес WE – Write Enable (1 – Запись, 0 -

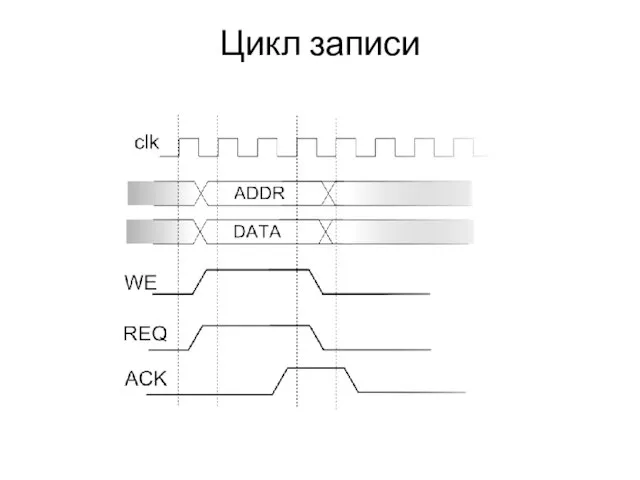

- 11. Цикл записи

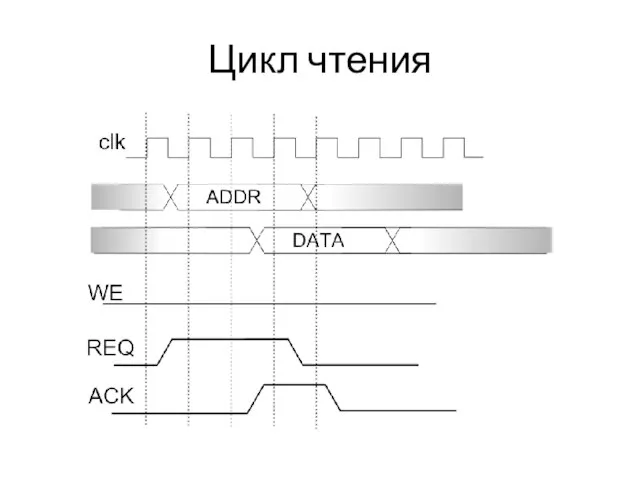

- 12. Цикл чтения

- 13. Структурная схема шины

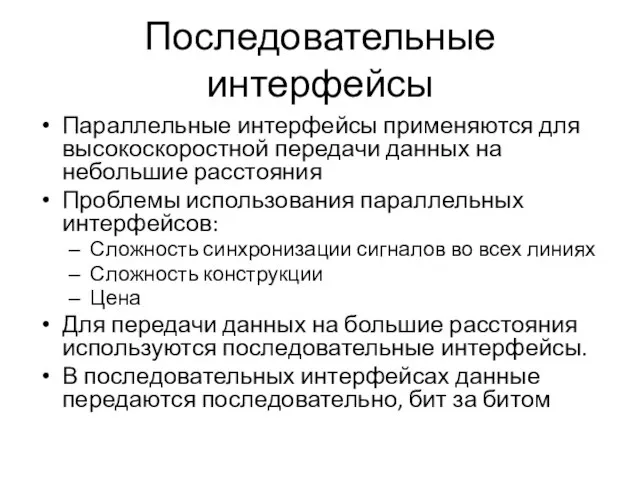

- 14. Последовательные интерфейсы Параллельные интерфейсы применяются для высокоскоростной передачи данных на небольшие расстояния Проблемы использования параллельных интерфейсов:

- 15. Синхронные и асинхронные последовательные интерфейсы Синхронные: PS/2 SPI I2C … Асинхронные: UART USB Ethernet ... В

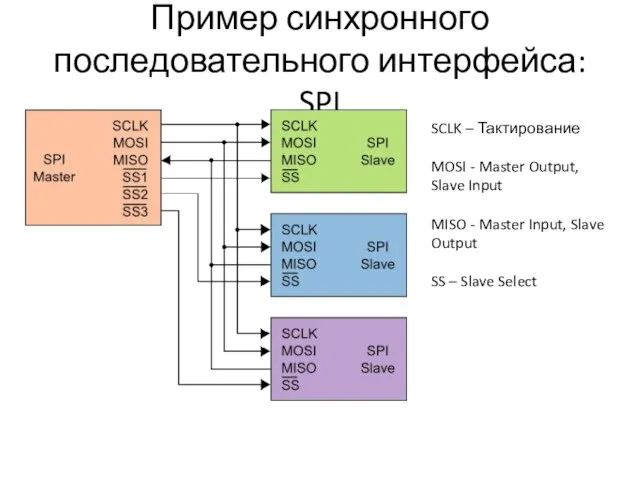

- 16. Пример синхронного последовательного интерфейса: SPI SCLK – Тактирование MOSI - Master Output, Slave Input MISO -

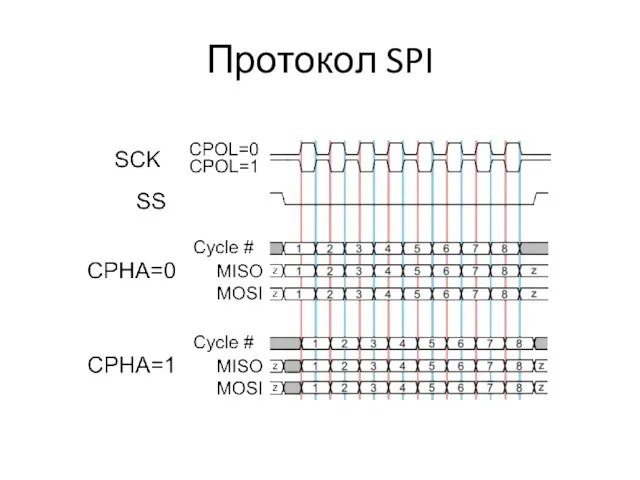

- 17. Протокол SPI

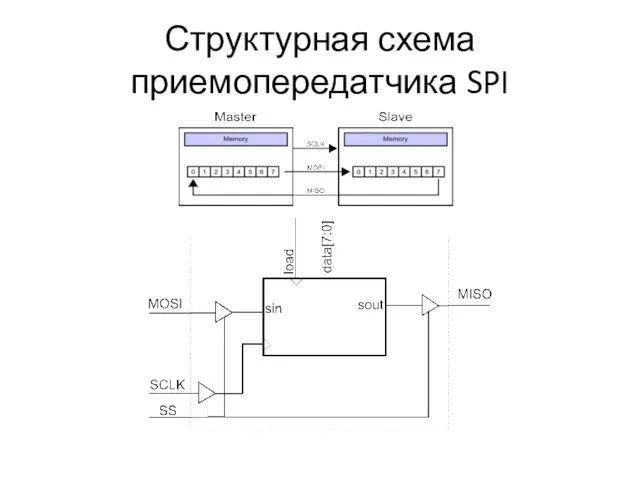

- 18. Структурная схема приемопередатчика SPI

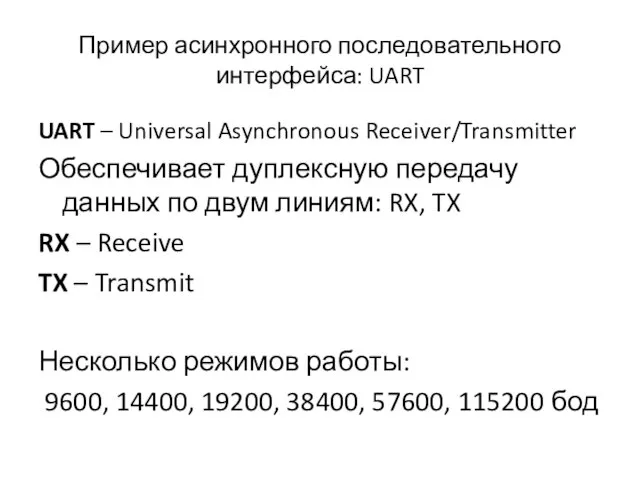

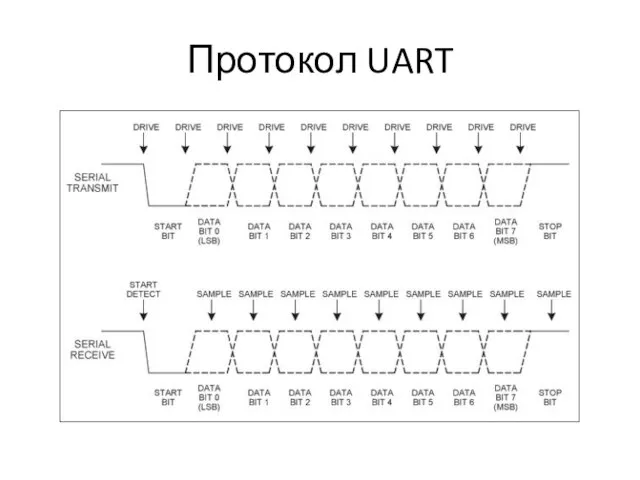

- 19. Пример асинхронного последовательного интерфейса: UART UART – Universal Asynchronous Receiver/Transmitter Обеспечивает дуплексную передачу данных по двум

- 20. Протокол UART

- 21. Структурная схема UART

- 22. Структурная схема UART (раздельный приемник и передатчик)

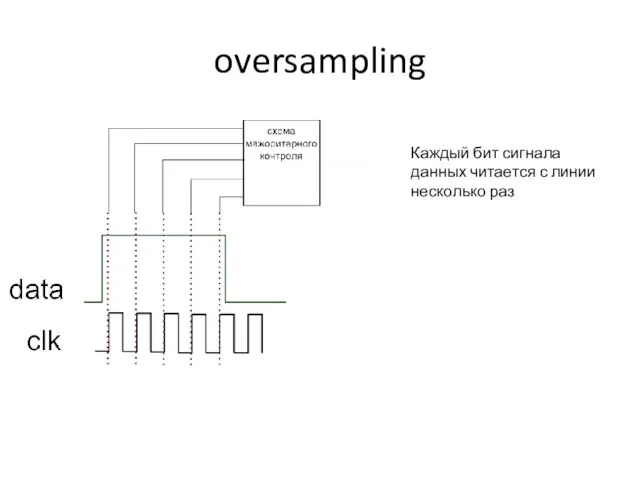

- 23. oversampling Каждый бит сигнала данных читается с линии несколько раз

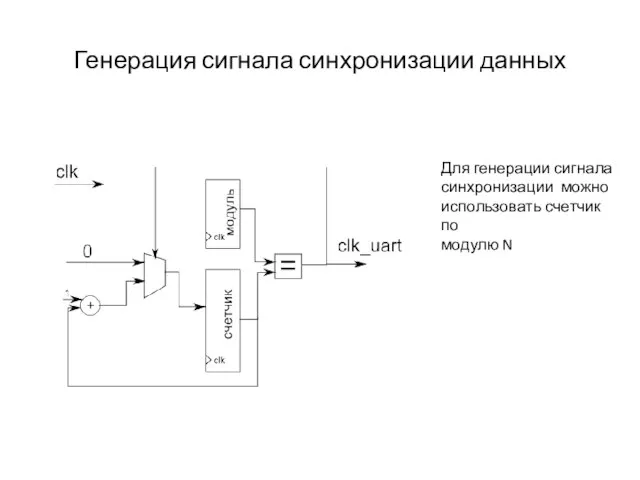

- 24. Генерация сигнала синхронизации данных Для генерации сигнала синхронизации можно использовать счетчик по модулю N

- 26. Скачать презентацию

Агрикола. Удобрения, грунты

Агрикола. Удобрения, грунты Магнарус. Время отдохнуть душой

Магнарус. Время отдохнуть душой РСК

РСК Tall or high

Tall or high Иван Андреевич Крылов: творческое наследие баснописца

Иван Андреевич Крылов: творческое наследие баснописца Отработка навыков практической стрельбы из пневматической винтовки

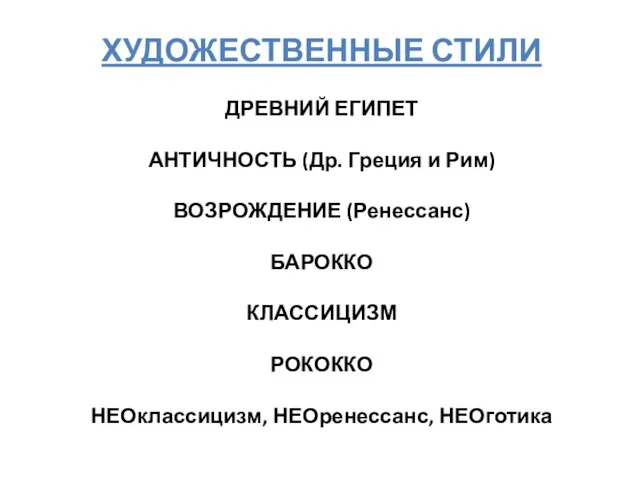

Отработка навыков практической стрельбы из пневматической винтовки Художественные стили. Виды и жанры искусства

Художественные стили. Виды и жанры искусства Этика делового общения по телефону

Этика делового общения по телефону Презентация на тему интерактивная доска

Презентация на тему интерактивная доска Правопорушення в мультфільмах

Правопорушення в мультфільмах Технология. Проволока и способы её получения. Изделия из проволоки

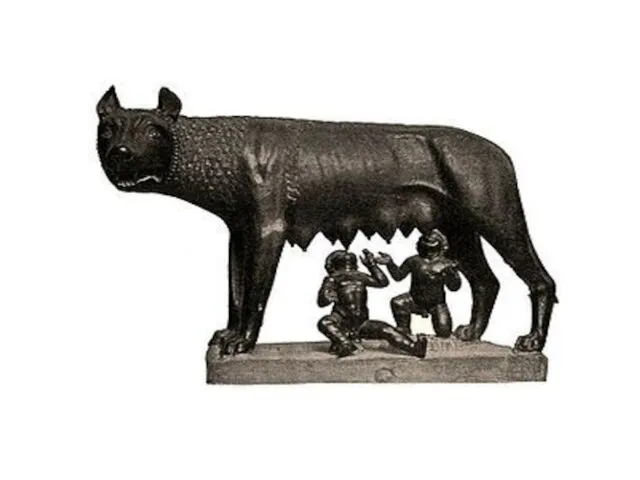

Технология. Проволока и способы её получения. Изделия из проволоки Вид на Аппиеву дорогу, самая значимая из античных общественных дорог Рима. Дорога, проложенная в 312 году до н. э. при цензоре Аппии Кл

Вид на Аппиеву дорогу, самая значимая из античных общественных дорог Рима. Дорога, проложенная в 312 году до н. э. при цензоре Аппии Кл Дополнительное образование 5 - 9 классы

Дополнительное образование 5 - 9 классы Вместе против террора

Вместе против террора Музей Михайловской СОШ

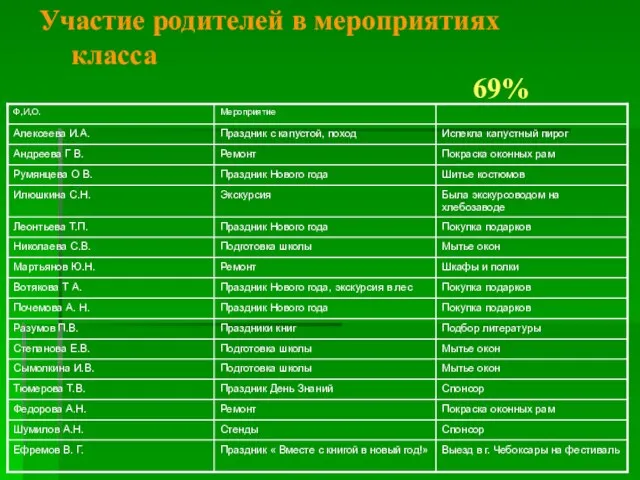

Музей Михайловской СОШ Участие родителей в мероприятиях класса 69%

Участие родителей в мероприятиях класса 69% Основы управления

Основы управления Прямая и обратная пропорциональные зависимости

Прямая и обратная пропорциональные зависимости Методология моделирования потоков данных DFD

Методология моделирования потоков данных DFD ProДеньги. Учимся составлять бюджет. Планируем финансовые потоки

ProДеньги. Учимся составлять бюджет. Планируем финансовые потоки «О итогах деятельности администрации Павловского района по модернизации образования в 2011 году»

«О итогах деятельности администрации Павловского района по модернизации образования в 2011 году» Современный состав Архивного фонда РФ и его классификации

Современный состав Архивного фонда РФ и его классификации Теории эмоций

Теории эмоций Основные требования к трафарету

Основные требования к трафарету ОСНОВЫ КОНСТИТУЦИОННОГО ПРАВА

ОСНОВЫ КОНСТИТУЦИОННОГО ПРАВА Российский Федерализм и межнациональные отношения

Российский Федерализм и межнациональные отношения  Теории периодизации развития психики

Теории периодизации развития психики Разработка сервиса для поддержки принятия решения при оценке производственных прототипов

Разработка сервиса для поддержки принятия решения при оценке производственных прототипов