Слайд 2HDL – Hardware Description Language

HDL используются для концептуальной разработки цифровых интегральных схем.

Наиболее

распространенные HDL:

Verilog

VHDL

Слайд 3Абстракция Дизайна

HDL позволяют иерархически описать систему как совокупность блоков (черных ящиков), имеющих

внешние интерфейсы.

Блок может быть описан как состоящий из составных блоков.

Абстрагирование позволяет скудному человеческому мозгу иметь дело с очень сложными системами.

Слайд 4Абстракция Описания

HDL позволяет описывать систему с различными уровнями детализации.

Обычно разработка ведется сверху

вниз, путем последовательного уточнения дизайна.

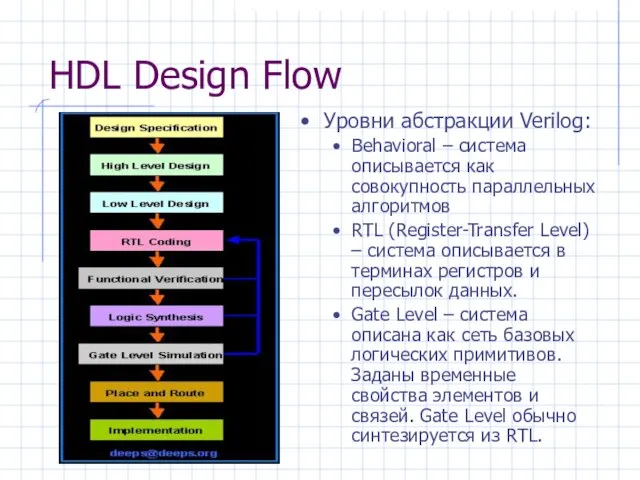

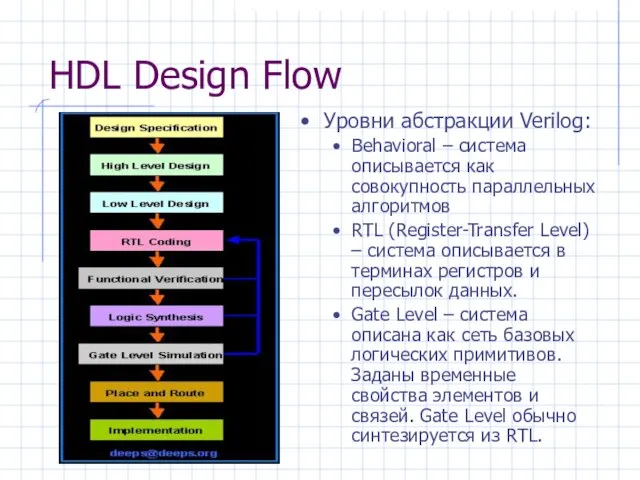

Слайд 5HDL Design Flow

Уровни абстракции Verilog:

Behavioral – система описывается как совокупность параллельных алгоритмов

RTL

(Register-Transfer Level) – система описывается в терминах регистров и пересылок данных.

Gate Level – система описана как сеть базовых логических примитивов. Заданы временные свойства элементов и связей. Gate Level обычно синтезируется из RTL.

Слайд 6Simulation (Моделирование)

Программа на Verilog может быть промоделирована.

Обычно моделирование осуществляется в тестовом окружении

(test bench).

Используя встроенные функции, в процессе моделирования можно выполнять вывод данных на экран или собирать трассу интересующих сигналов.

Слайд 7PLI – Programming Language Interface

Описание Verilog и VHDL включает также C-интерфейс, позволяющий

программному коду на языке C выполняться во время моделирования Verilog-программы.

PLI позволяет получить полную информацию о структуре и состоянии системы.

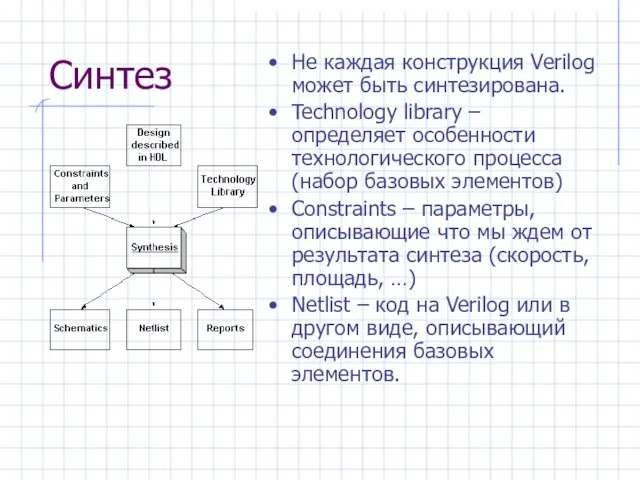

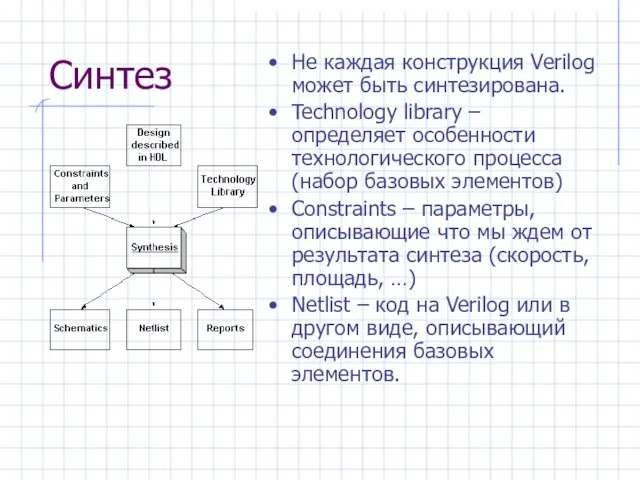

Слайд 8Синтез

Не каждая конструкция Verilog может быть синтезирована.

Technology library – определяет особенности технологического

процесса (набор базовых элементов)

Constraints – параметры, описывающие что мы ждем от результата синтеза (скорость, площадь, …)

Netlist – код на Verilog или в другом виде, описывающий соединения базовых элементов.

Слайд 11Маска

Маска – стеклянная пластина, покрытая хромом, на которой вытравлен «рисунок» соответствующего слоя,

в соответствии с библиотекой технологии и синтезированной сетью.

Длина световой волны, используемой при проецировании на подложку (wafer – вафля) – важная характеристика технологического процесса.

Слайд 12FPGA – Field Programmable Gate Array

Устройство, позволяющее запрограммировать логику своей работы.

Представляет из

себя регулярную структуру из базовых логических блоков (CLB), блоков ввода/вывода, матрицы соединений.

Дорого при массовом использовании, выгодно при мелкосерийном производстве и прототипировании.

Презентация на тему Правописание проверяемых букв согласных в корне слова

Презентация на тему Правописание проверяемых букв согласных в корне слова  Социальное служение Русской Православной Церкви

Социальное служение Русской Православной Церкви Отчёт по учебно-производственной практике. Специальность Ресторанное дело и гостиничный бизнес

Отчёт по учебно-производственной практике. Специальность Ресторанное дело и гостиничный бизнес Биологическое действие радиоактивных излучений. Защита организмов от них.

Биологическое действие радиоактивных излучений. Защита организмов от них. Дидактические игры как одна из активных форм обучения

Дидактические игры как одна из активных форм обучения На закате человеческой цивилизации появилась надежда…И была эта надежда в Московском институте открытого образования

На закате человеческой цивилизации появилась надежда…И была эта надежда в Московском институте открытого образования Окская тропа - 2018

Окская тропа - 2018 Математическое описание случайных явлений

Математическое описание случайных явлений Блины на масленницу

Блины на масленницу CMMI® for Acquisition: новая модель - для кого и зачем?

CMMI® for Acquisition: новая модель - для кого и зачем? Спорт, ребята, очень нужен

Спорт, ребята, очень нужен Положительные стороны занятий в секции спортивного ориентирования

Положительные стороны занятий в секции спортивного ориентирования Отраслевая структура мирового хозяйства. Воздействие НТР

Отраслевая структура мирового хозяйства. Воздействие НТР Презентация на тему угольная кислота и её соли 9 класс

Презентация на тему угольная кислота и её соли 9 класс  Вязание крючком

Вязание крючком 14 сентября 2011 да

14 сентября 2011 да Музей живой воды

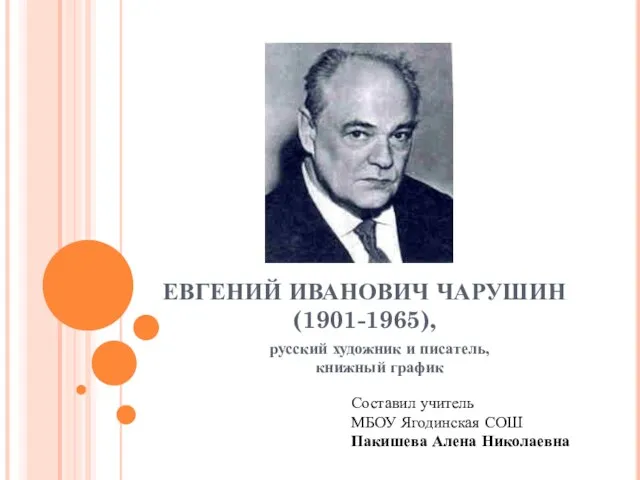

Музей живой воды ЕВГЕНИЙ ИВАНОВИЧ ЧАРУШИН (1901-1965)

ЕВГЕНИЙ ИВАНОВИЧ ЧАРУШИН (1901-1965) Центр развития ребенка детский сад №1834

Центр развития ребенка детский сад №1834 ОАО МЕТРОВАГОНМАШ

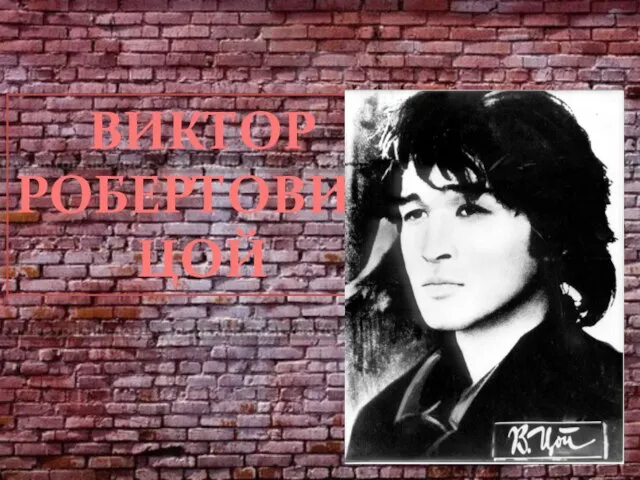

ОАО МЕТРОВАГОНМАШ Виктор Робертович Цой

Виктор Робертович Цой The Origins of English

The Origins of English  The observations of star formation regions by RT-22 PRAO ASC LPI - water maser sources survey. Lekht E.E. (1), Samodurov V.A. (2), Tolmachev A.M. (2) (1) Sternberg Astron.Inst. of MSU(2) PRAO ASC LPI

The observations of star formation regions by RT-22 PRAO ASC LPI - water maser sources survey. Lekht E.E. (1), Samodurov V.A. (2), Tolmachev A.M. (2) (1) Sternberg Astron.Inst. of MSU(2) PRAO ASC LPI Петербург – город мастеров кисти и резца

Петербург – город мастеров кисти и резца Домашняя Масленица

Домашняя Масленица Презентация

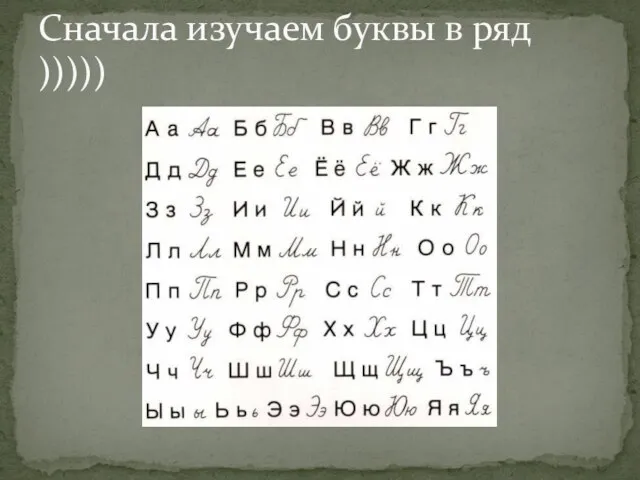

Презентация Сначала изучаем буквы в ряд )))))

Сначала изучаем буквы в ряд ))))) Современное стрелковое оружие

Современное стрелковое оружие