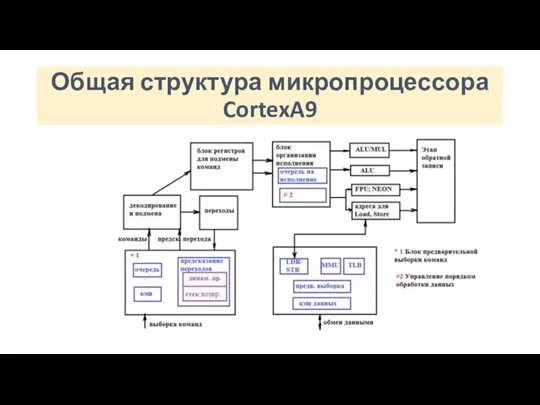

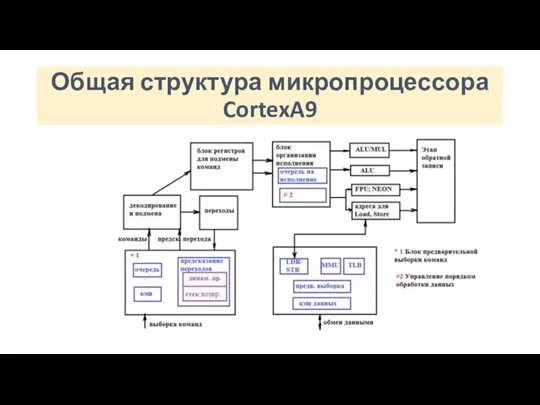

Слайд 2Общая структура микропроцессора CortexA9

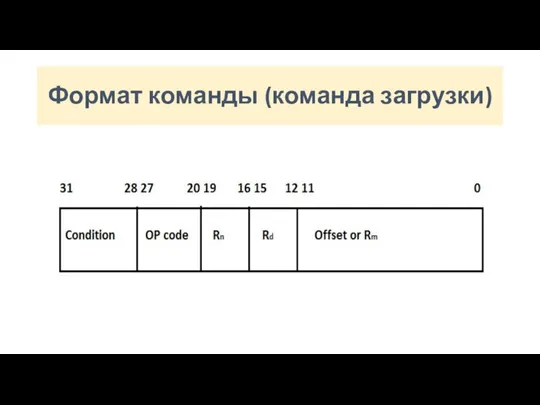

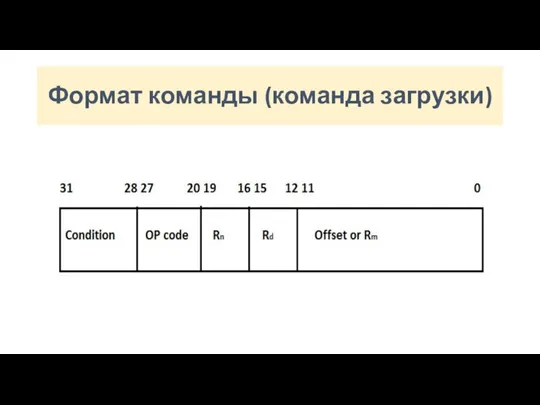

Слайд 5Формат команды (команда загрузки)

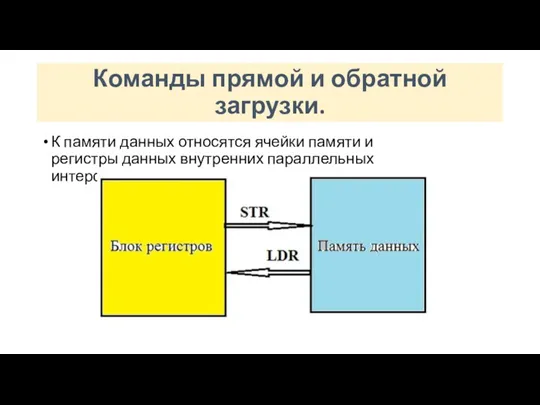

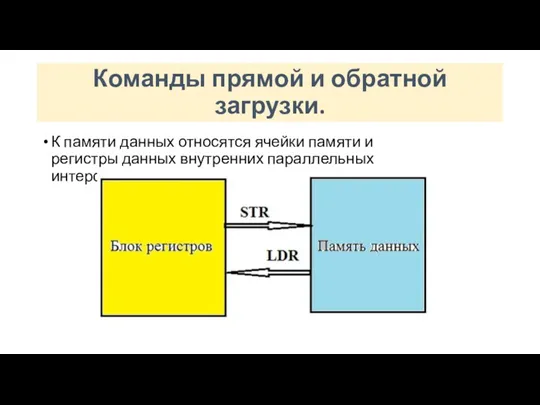

Слайд 7Команды прямой и обратной загрузки.

К памяти данных относятся ячейки памяти и регистры

данных внутренних параллельных интерфейсов.

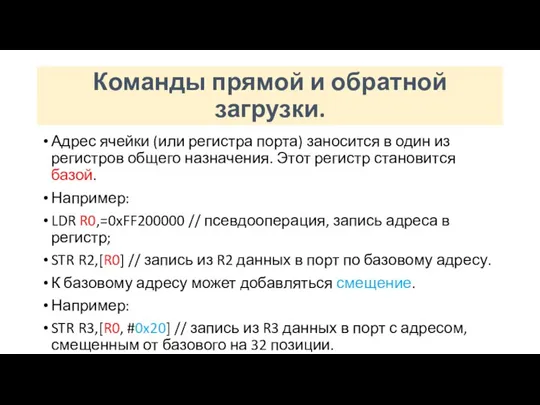

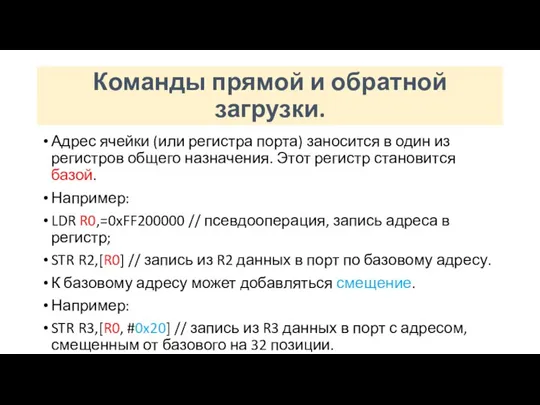

Слайд 8Команды прямой и обратной загрузки.

Адрес ячейки (или регистра порта) заносится в один

из регистров общего назначения. Этот регистр становится базой.

Например:

LDR R0,=0xFF200000 // псевдооперация, запись адреса в регистр;

STR R2,[R0] // запись из R2 данных в порт по базовому адресу.

К базовому адресу может добавляться смещение.

Например:

STR R3,[R0, #0x20] // запись из R3 данных в порт с адресом, смещенным от базового на 32 позиции.

Слайд 9Команды прямой и обратной загрузки.

При записи STR R3,[R0, #0x20] – состояние базы

![Команды прямой и обратной загрузки. При записи STR R3,[R0, #0x20] – состояние](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/960108/slide-8.jpg)

не меняется.

При записи STR R3,[R0, #0x20]! – состояние изменяется на 32 единицы до копирования содержимого R3 в порт.

При записи STR R3,[R0], #0x20 – состояние изменяется на 32 единицы после копирования содержимого R3 в порт.

Адрес точки назначения при всех трех записях будет одинаковый!

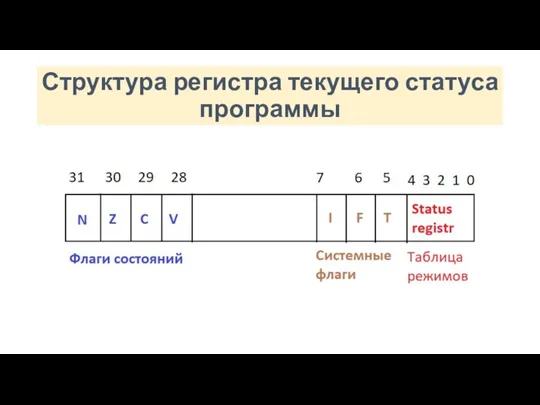

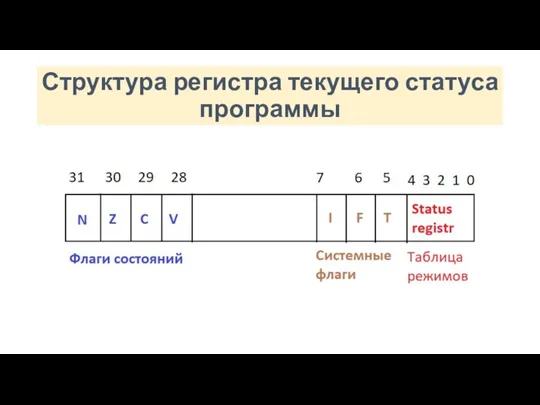

Слайд 10Структура регистра текущего статуса программы

![Команды прямой и обратной загрузки. При записи STR R3,[R0, #0x20] – состояние](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/960108/slide-8.jpg)

Поиск информации

Поиск информации Bondder Landing page-Scroll down script

Bondder Landing page-Scroll down script Типы инфографики

Типы инфографики Обзор современных языков программирования. Базовые понятия. 1 занятие. Программирование на Python

Обзор современных языков программирования. Базовые понятия. 1 занятие. Программирование на Python Программа Photomath

Программа Photomath Передача информации в компьютерных сетях Аппаратное и программное обеспечение работы глобальной сети 9-3

Передача информации в компьютерных сетях Аппаратное и программное обеспечение работы глобальной сети 9-3 Устройство компьютера. Обобщение материала

Устройство компьютера. Обобщение материала ЛОГИЧЕСКИЙ ТИП ДАННЫХ В ПАСКАЛЕ

ЛОГИЧЕСКИЙ ТИП ДАННЫХ В ПАСКАЛЕ Презентация на тему Программы и файлы (5 класс)

Презентация на тему Программы и файлы (5 класс)  Рисуем радугу

Рисуем радугу ЛЕКЦИЯ_1_Основы_облачных_технологий

ЛЕКЦИЯ_1_Основы_облачных_технологий Информационные технологии. Информатизация общества

Информационные технологии. Информатизация общества Компьютерные сети

Компьютерные сети Ускорение прогресса

Ускорение прогресса Правила общения в сети Интернет

Правила общения в сети Интернет Основные этапы проектирования реляционной База данных

Основные этапы проектирования реляционной База данных Аналитическая бизнес-справка на ЮЛ

Аналитическая бизнес-справка на ЮЛ Универсальная битва полов

Универсальная битва полов Динамические структуры данных (язык Си)

Динамические структуры данных (язык Си) Компьютерная графика

Компьютерная графика Сберкласс

Сберкласс Основы языка HTML

Основы языка HTML Інформаційна технологія

Інформаційна технологія Моя профессия программирование в компьютерных системах

Моя профессия программирование в компьютерных системах Введение, классификация сетей. Лекция 1

Введение, классификация сетей. Лекция 1 Пакет подготовки презентаций Microsoft Power Point

Пакет подготовки презентаций Microsoft Power Point Компьютерные программы, используемые при автоматизации работы парикмахерских и салонов красоты

Компьютерные программы, используемые при автоматизации работы парикмахерских и салонов красоты Реализация типового сервиса вопросов и ответов

Реализация типового сервиса вопросов и ответов