Содержание

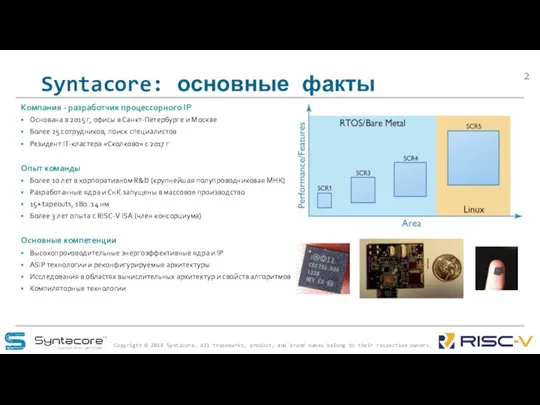

- 2. Syntacore: основные факты Компания - разработчик процессорного IP Основана в 2015 г, офисы в Санкт-Петербурге и

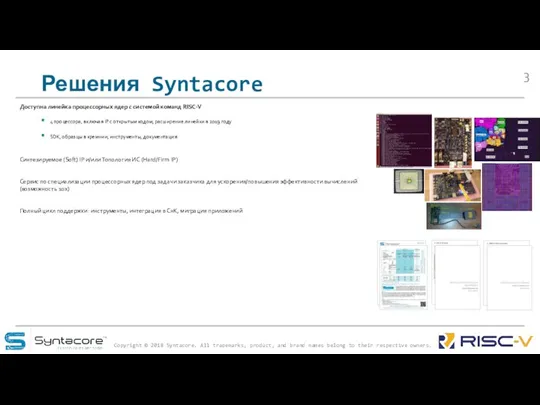

- 3. Решения Syntacore Доступна линейка процессорных ядер с системой команд RISC-V 4 процессора, включая IP с открытым

- 4. Что такое RISC-V RISC-V - это качественный, современный, открытый и свободный стандарт на набор команд процессора

- 5. Консорциум RISC-V (RISC-V Foundation) Copyright © 2018 Syntacore. All trademarks, product, and brand names belong to

- 6. Принципы организации консорциума Основан в августе 2015 как некоммерческая организация, Устав утвержден в декабре 2016 Цель

- 7. Отличительные черты RISC-V ISA Простота Существенно меньше, чем другие коммерческие ISA Разработана с чистого листа, отсутствие

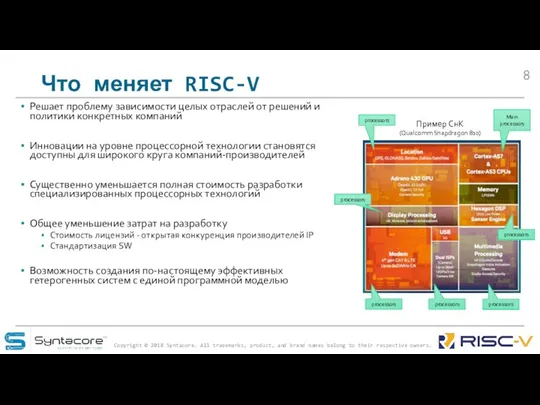

- 8. Что меняет RISC-V Решает проблему зависимости целых отраслей от решений и политики конкретных компаний Инновации на

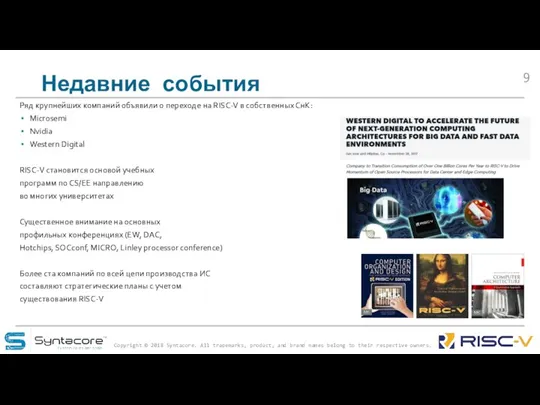

- 9. Недавние события Ряд крупнейших компаний объявили о переходе на RISC-V в собственных СнК: Microsemi Nvidia Western

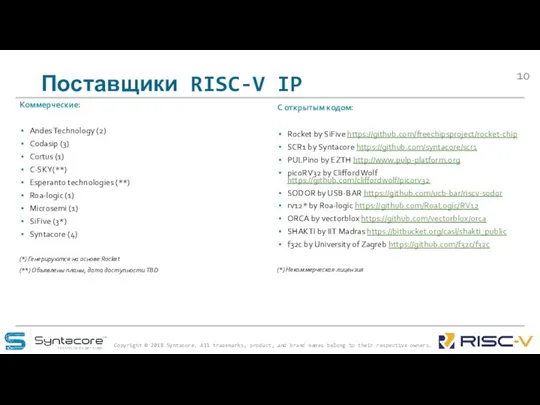

- 10. Поставщики RISC-V IP Коммерческие: Andes Technology (2) Codasip (3) Cortus (1) C-SKY(**) Esperanto technologies (**) Roa-logic

- 11. Национальные программы Индия: выбрала RISC-V национальным стандартом на ISA элементной базы США: агентство DARPA указывает RISC-V

- 12. Дополнительные ресурсы по RISC-V Foundation: https://riscv.org/ Specifications: https://riscv.org/specifications/ GitHub: https://github.com/riscv Mailing Lists: http://riscv.org/mailing-lists Open-source SCR1 core:

- 14. Скачать презентацию

Исследование звукосимволизма с помощью Word Embedding

Исследование звукосимволизма с помощью Word Embedding Новые и интересные возможности и грабли. Семинар-тренинг

Новые и интересные возможности и грабли. Семинар-тренинг Условный оператор в языке программирования Pascal

Условный оператор в языке программирования Pascal Информационные технологии в менеджменте

Информационные технологии в менеджменте Всероссийская образовательная акция Урок цифры — 2020. Нейросети и коммуникации

Всероссийская образовательная акция Урок цифры — 2020. Нейросети и коммуникации Автоматизированные системы обработки информации

Автоматизированные системы обработки информации Zombie Hunt. Play

Zombie Hunt. Play Носители информации

Носители информации Analysis of debugging process

Analysis of debugging process Программирование на языке Python

Программирование на языке Python Мультиязычный интернет-каталог с автоматическим наполнением номенклатуры

Мультиязычный интернет-каталог с автоматическим наполнением номенклатуры Внешние модели данных

Внешние модели данных Кибербезопасность и хакинг

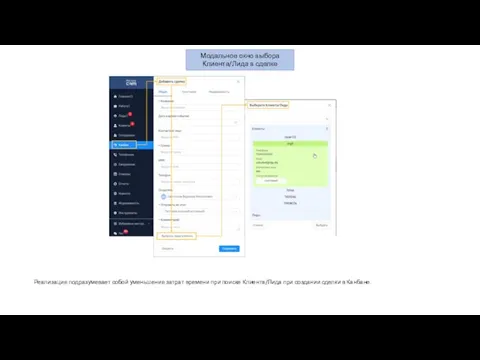

Кибербезопасность и хакинг Модальное окно выбора

Модальное окно выбора Лариса Гуляева. В контакте

Лариса Гуляева. В контакте Взаимодействия прикладной программы и программы с потенциально опасными последствиями

Взаимодействия прикладной программы и программы с потенциально опасными последствиями Построение таблицы трассировки для ветвящегося процесса

Построение таблицы трассировки для ветвящегося процесса Работа в Trello, средства коммуникации, запись экрана

Работа в Trello, средства коммуникации, запись экрана Анализ и сбор информации

Анализ и сбор информации РНКО Единая касса

РНКО Единая касса Участие в разработке информационных систем для Александровской больницы города Астрахани

Участие в разработке информационных систем для Александровской больницы города Астрахани Программное средство обмена текстовой и мультимедийной информации

Программное средство обмена текстовой и мультимедийной информации Проблематика отзывных площадок

Проблематика отзывных площадок Работа редактора с композицией медиатекста

Работа редактора с композицией медиатекста Организация хранения информации в компьютере. Файлы и папки

Организация хранения информации в компьютере. Файлы и папки Медиагруппа МАктион-МЦФЭР

Медиагруппа МАктион-МЦФЭР Что такое компьютер?

Что такое компьютер? Презентация на тему Язык разметки гипертекста HTML

Презентация на тему Язык разметки гипертекста HTML