Содержание

- 2. Aug-23 ENEE 644 Outline What is Technology Mapping? Technology Mapping Algorithms Technology Mapping as Graph Covering

- 3. Aug-23 ENEE 644 Technology Mapping Technology mapping is the phase of logic synthesis when gates are

- 4. Aug-23 ENEE 644 Technology Mapping Algorithms Basic Requirements: Provide high quality solutions (circuits). Adapt to different

- 5. Aug-23 ENEE 644 Outline What is Technology Mapping? Technology Mapping Algorithms Technology Mapping as Graph Covering

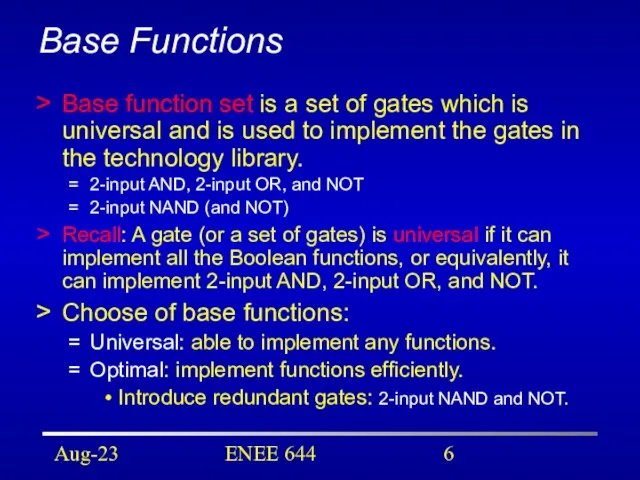

- 6. Aug-23 ENEE 644 Base Functions Base function set is a set of gates which is universal

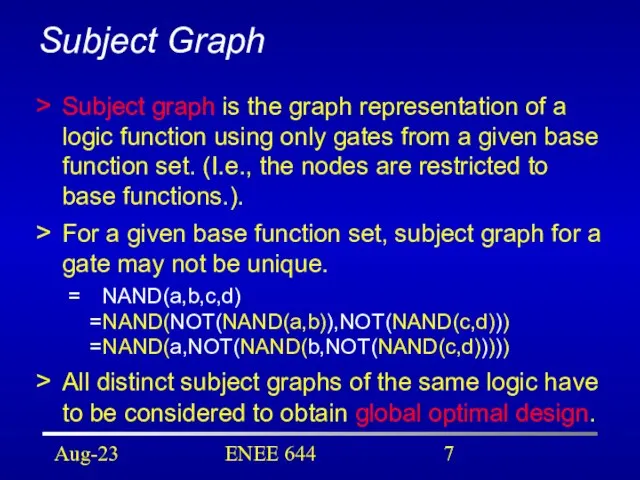

- 7. Aug-23 ENEE 644 Subject Graph Subject graph is the graph representation of a logic function using

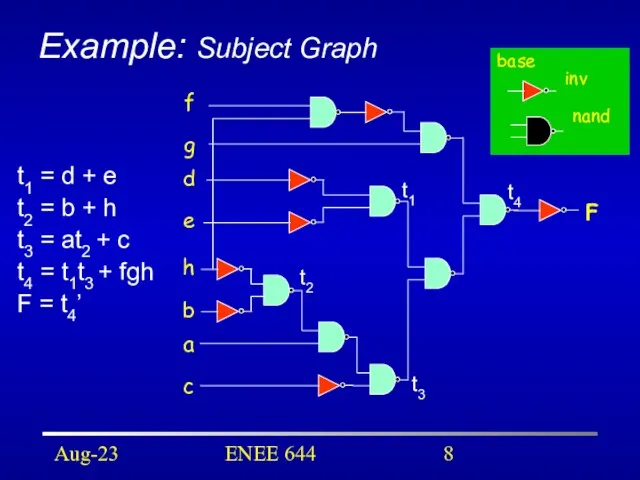

- 8. Aug-23 ENEE 644 Example: Subject Graph t1 = d + e t2 = b + h

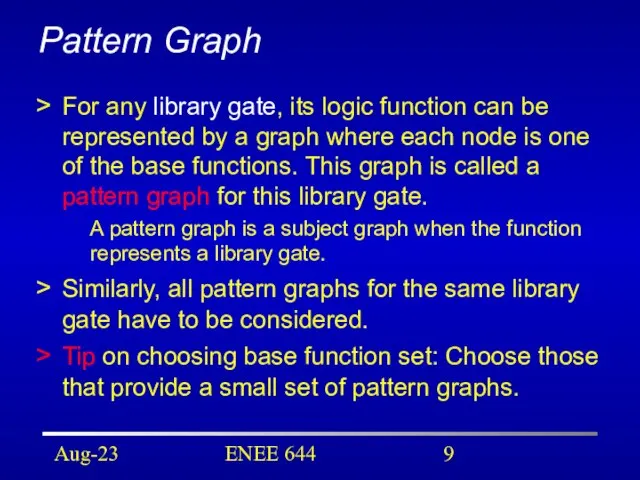

- 9. Aug-23 ENEE 644 Pattern Graph For any library gate, its logic function can be represented by

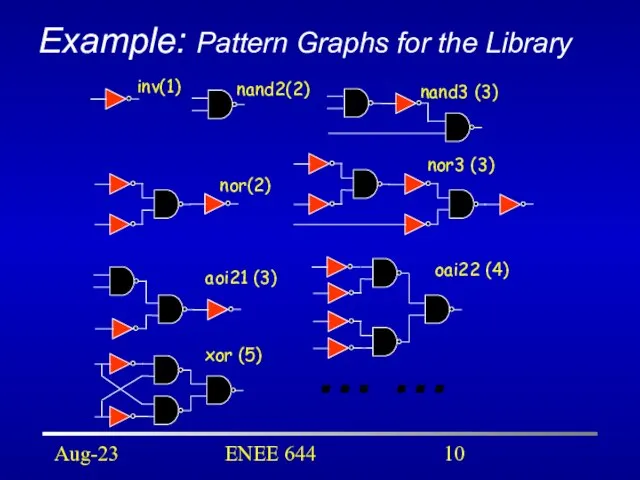

- 10. Aug-23 ENEE 644 Example: Pattern Graphs for the Library inv(1) nand3 (3) oai22 (4) nor(2) nor3

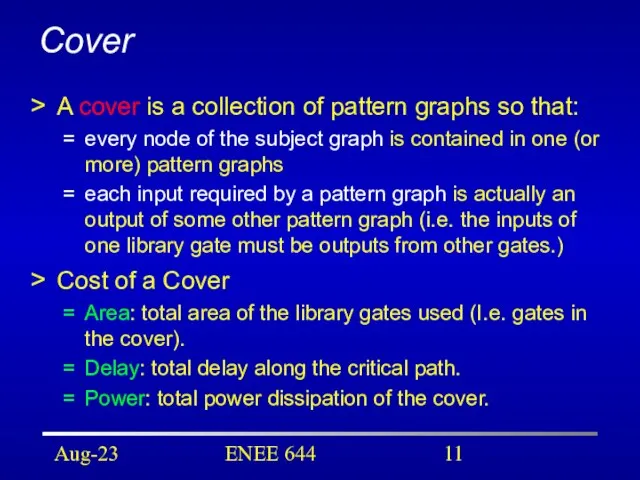

- 11. Aug-23 ENEE 644 Cover A cover is a collection of pattern graphs so that: every node

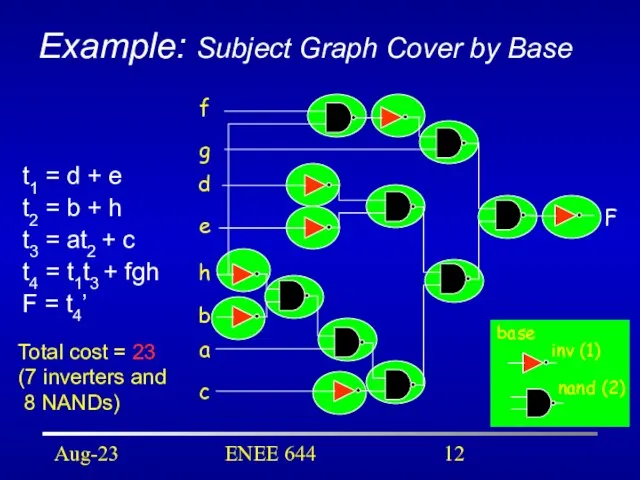

- 12. Aug-23 ENEE 644 Example: Subject Graph Cover by Base F f g d e h b

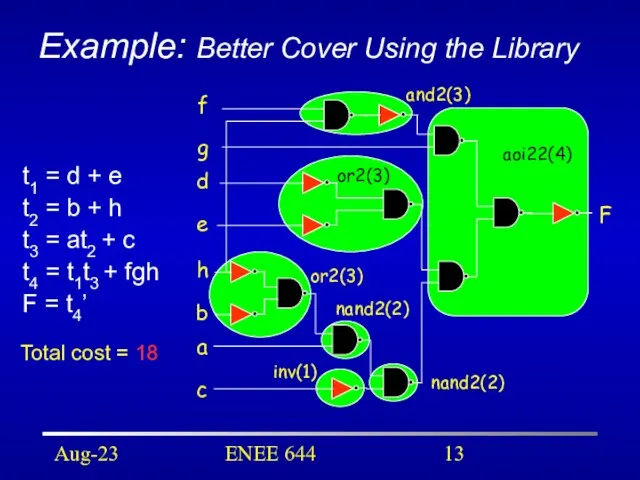

- 13. Aug-23 ENEE 644 Example: Better Cover Using the Library F f g d e h b

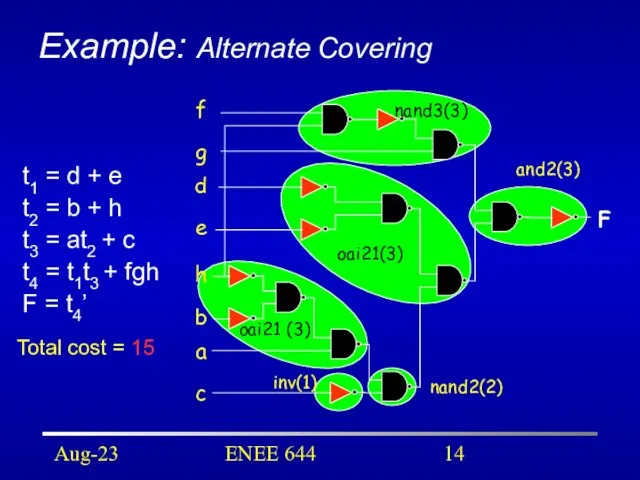

- 14. Aug-23 ENEE 644 Example: Alternate Covering F f g d e h b a c nand3(3)

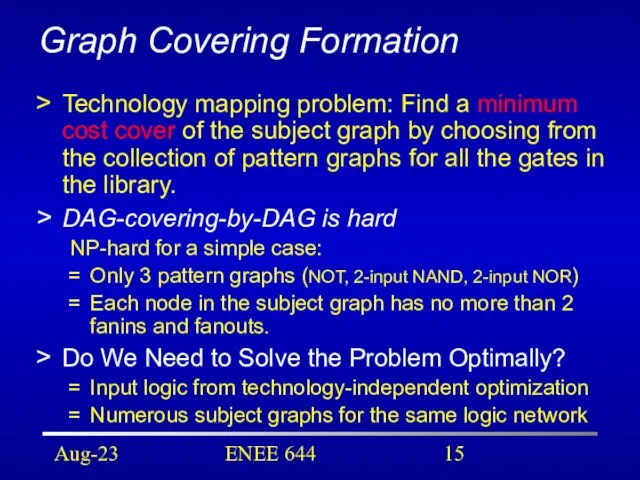

- 15. Aug-23 ENEE 644 Graph Covering Formation Technology mapping problem: Find a minimum cost cover of the

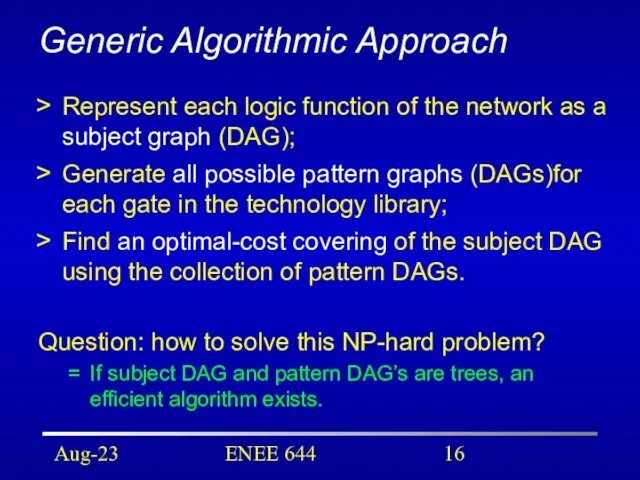

- 16. Aug-23 ENEE 644 Generic Algorithmic Approach Represent each logic function of the network as a subject

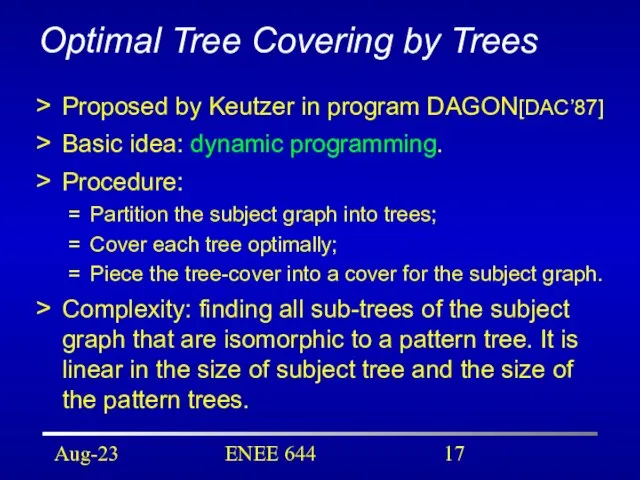

- 17. Aug-23 ENEE 644 Optimal Tree Covering by Trees Proposed by Keutzer in program DAGON[DAC’87] Basic idea:

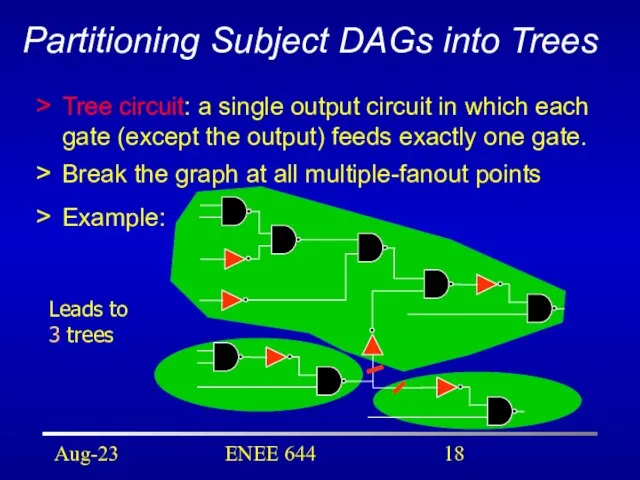

- 18. Aug-23 ENEE 644 Partitioning Subject DAGs into Trees Tree circuit: a single output circuit in which

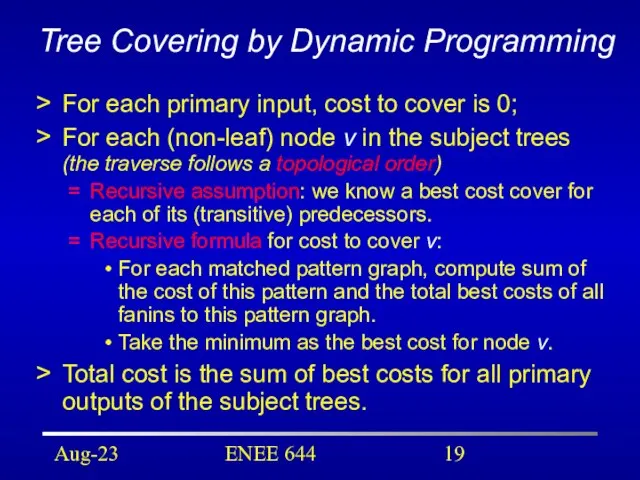

- 19. Aug-23 ENEE 644 Tree Covering by Dynamic Programming For each primary input, cost to cover is

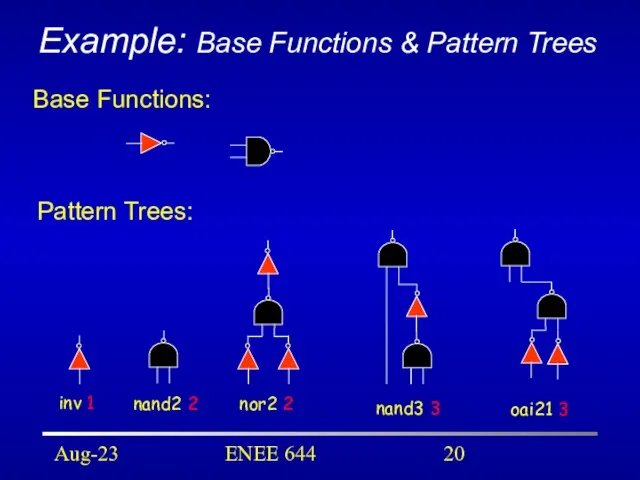

- 20. Aug-23 ENEE 644 Example: Base Functions & Pattern Trees inv 1 nand3 3 oai21 3 nor2

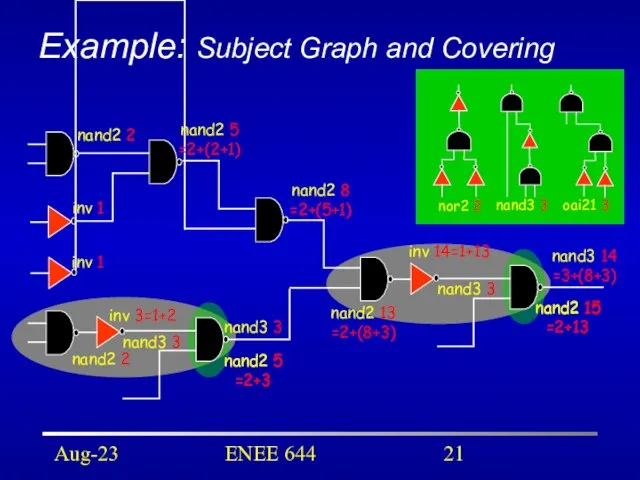

- 21. Aug-23 ENEE 644 Example: Subject Graph and Covering inv 3=1+2 nand2 5 =2+(2+1) nand2 8 =2+(5+1)

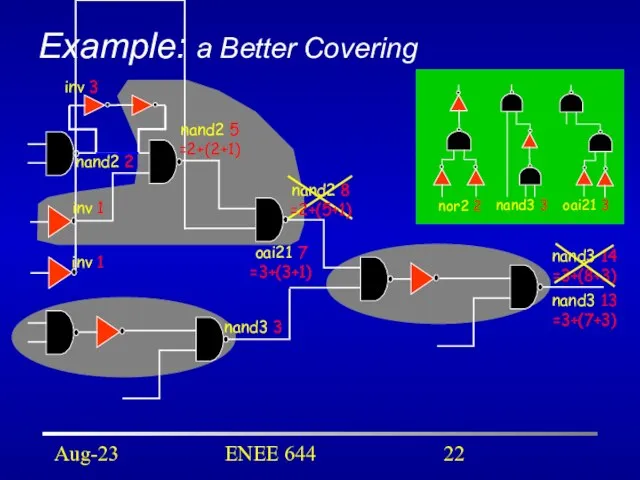

- 22. Aug-23 ENEE 644 Example: a Better Covering nand2 5 =2+(2+1) nand2 8 =2+(5+1) nand3 3 nand3

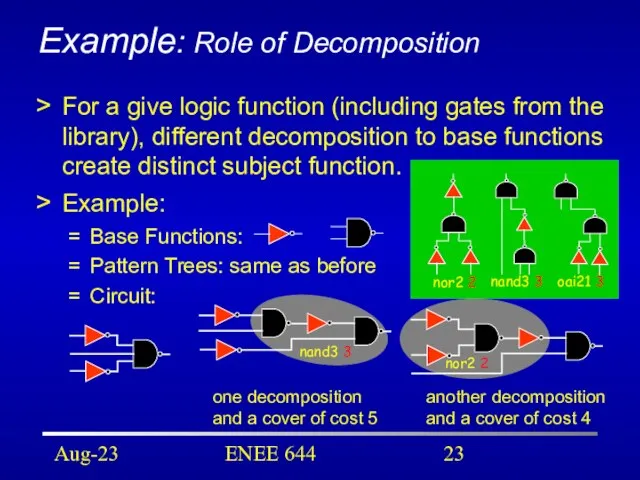

- 23. Aug-23 ENEE 644 Example: Role of Decomposition For a give logic function (including gates from the

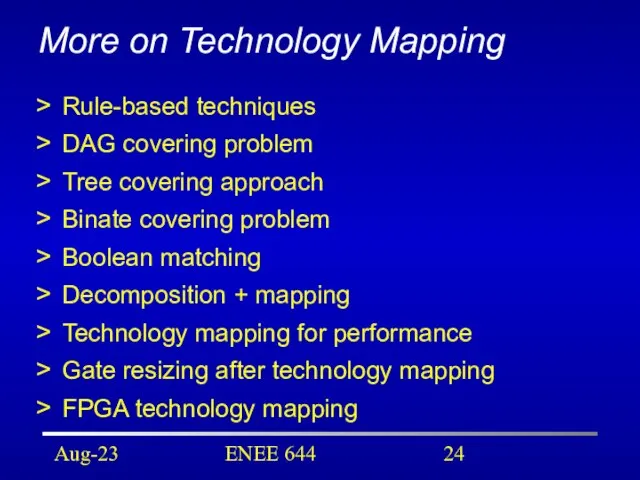

- 24. Aug-23 ENEE 644 More on Technology Mapping Rule-based techniques DAG covering problem Tree covering approach Binate

- 26. Скачать презентацию

Одномерные массивы. Алгоритмы поиска элемента массива

Одномерные массивы. Алгоритмы поиска элемента массива Система управления автоматическими звонками

Система управления автоматическими звонками Цифровые технологии в дизайне

Цифровые технологии в дизайне 9__string

9__string OOP’s Using JAVA Module 2

OOP’s Using JAVA Module 2 Хронометраж для соревнований

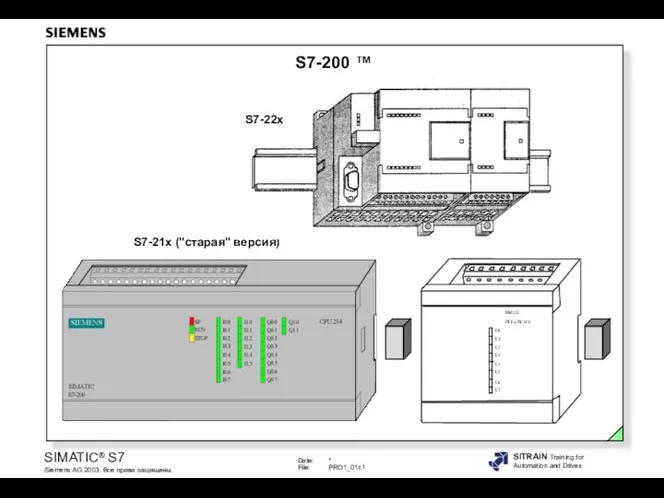

Хронометраж для соревнований S7-21x (старая версия)

S7-21x (старая версия) BookArt Родное небо. Онлайн-курс по социальному проектированию

BookArt Родное небо. Онлайн-курс по социальному проектированию Моделирование урока использованием ЦОР и компьютерных технологий

Моделирование урока использованием ЦОР и компьютерных технологий Научно-производственная фирма. Распределенная обработка информации

Научно-производственная фирма. Распределенная обработка информации Прикладное программное обеспечение

Прикладное программное обеспечение Портфолио Войтович Анны

Портфолио Войтович Анны Моделирование функциональных и вычислительных задач

Моделирование функциональных и вычислительных задач Обработка текстовых величин

Обработка текстовых величин Использование в работе учителя начальных классов информационно образовательной среды Учи.ру

Использование в работе учителя начальных классов информационно образовательной среды Учи.ру Ядро ОС. Компоненты ОС. Принципы построения ОС

Ядро ОС. Компоненты ОС. Принципы построения ОС Оформление проекта

Оформление проекта Версии программы AutoCAD. Изменения логотипа. Использование. Отличия от Adobe Illustrator

Версии программы AutoCAD. Изменения логотипа. Использование. Отличия от Adobe Illustrator Операторы графики

Операторы графики Архитектура персонального компьютера

Архитектура персонального компьютера Информатика высокого полета

Информатика высокого полета Создание зарплатной ведомости в Интернет-банкинге (корпоративный)

Создание зарплатной ведомости в Интернет-банкинге (корпоративный) Жизнь online

Жизнь online Class Object

Class Object Текстовая информация

Текстовая информация Проект Фотокнига

Проект Фотокнига Системы счисления

Системы счисления Referense news

Referense news