Содержание

- 2. Литература: 1. Скляр Б., «Цифровая связь. Теоретические основы и практическое применение», «Вильямс», Москва, Санкт-Петербург, Киев, 2003.

- 3. Содержание курса: 2 Введение в ПОР. Основные теоретические вопросы проектирования ПОР. Реализация на жесткой и программируемой

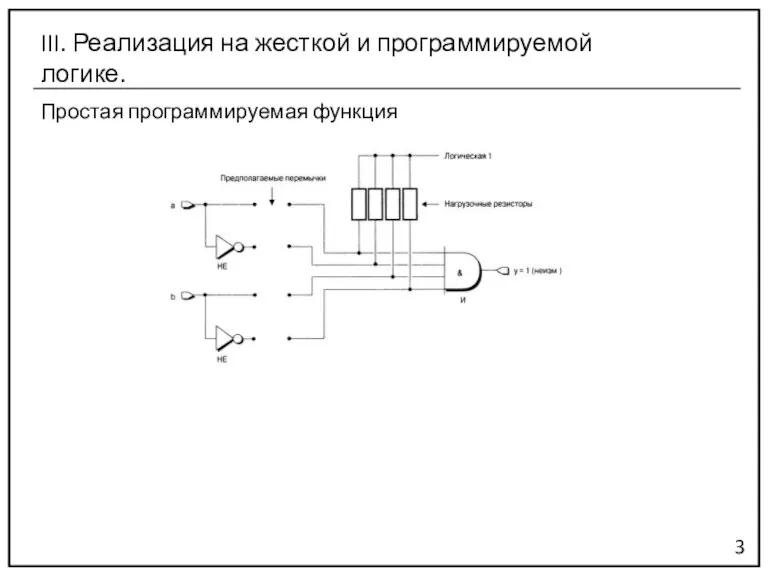

- 4. Простая программируемая функция 3 III. Реализация на жесткой и программируемой логике.

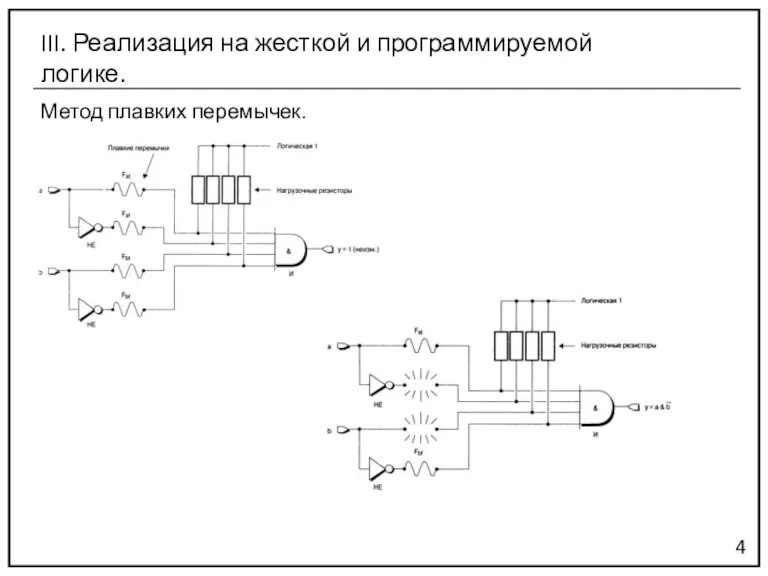

- 5. Метод плавких перемычек. 4 III. Реализация на жесткой и программируемой логике.

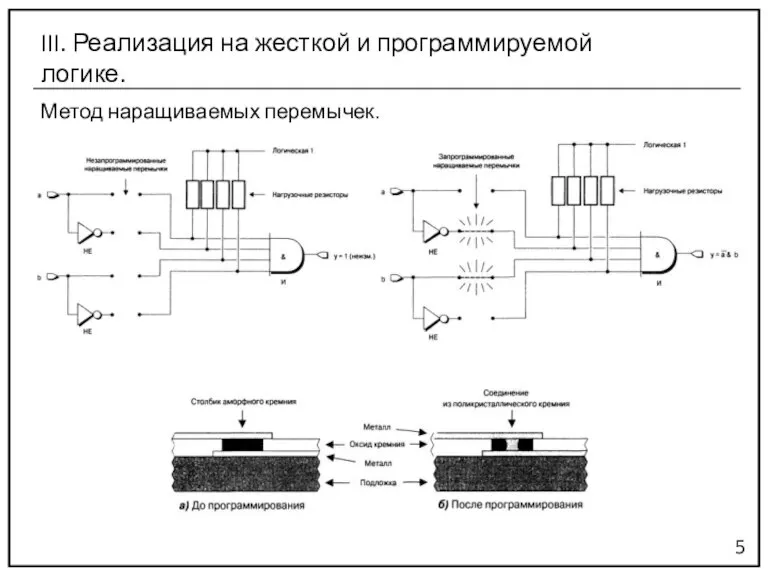

- 6. Метод наращиваемых перемычек. 5 III. Реализация на жесткой и программируемой логике.

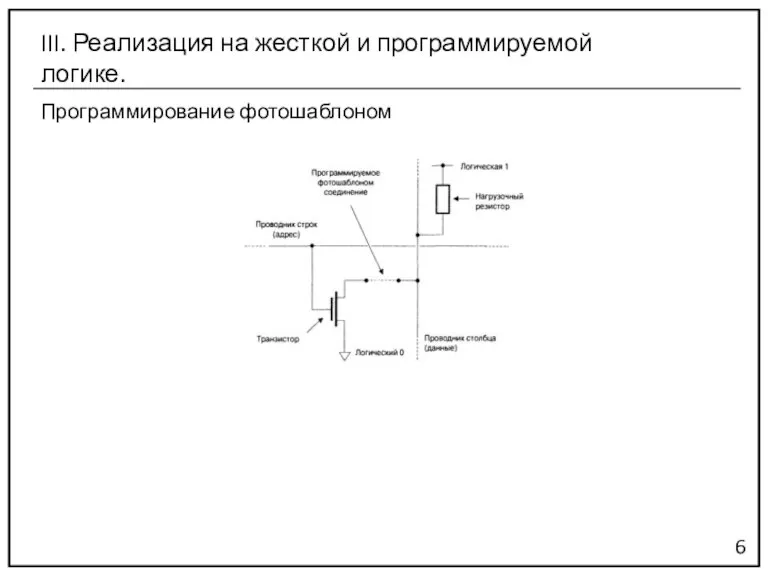

- 7. Программирование фотошаблоном 6 III. Реализация на жесткой и программируемой логике.

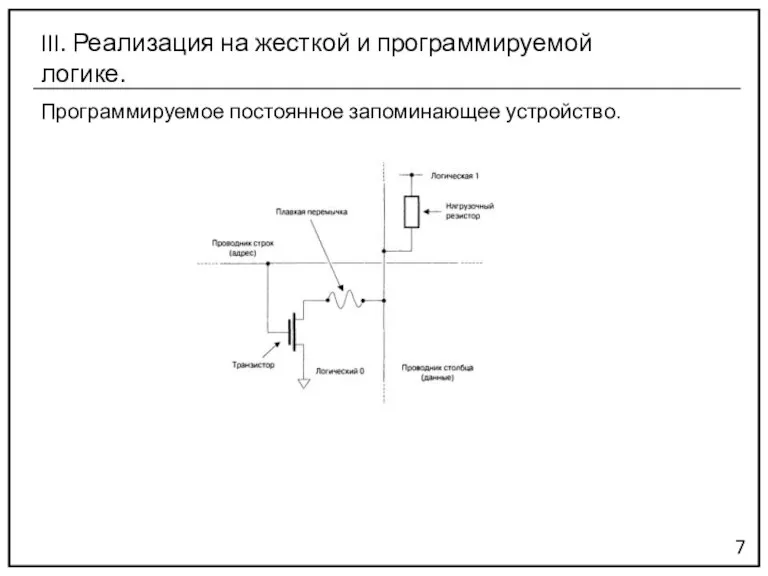

- 8. Программируемое постоянное запоминающее устройство. 7 III. Реализация на жесткой и программируемой логике.

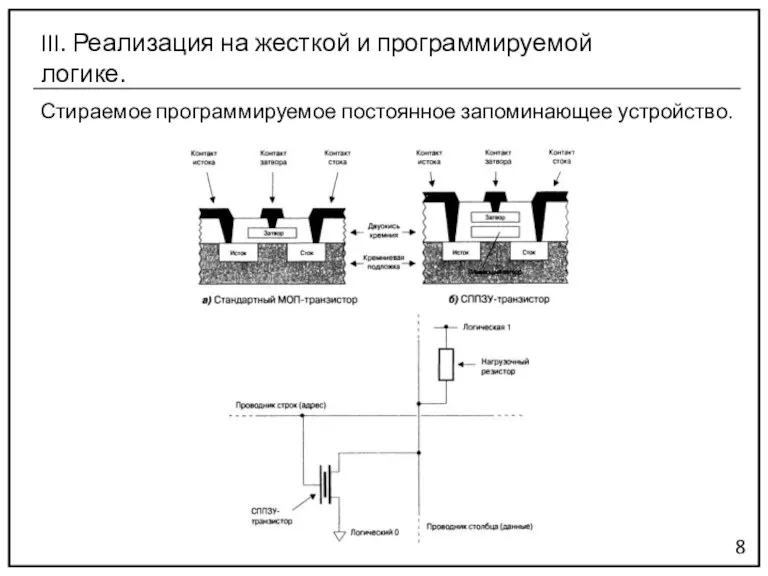

- 9. Стираемое программируемое постоянное запоминающее устройство. 8 III. Реализация на жесткой и программируемой логике.

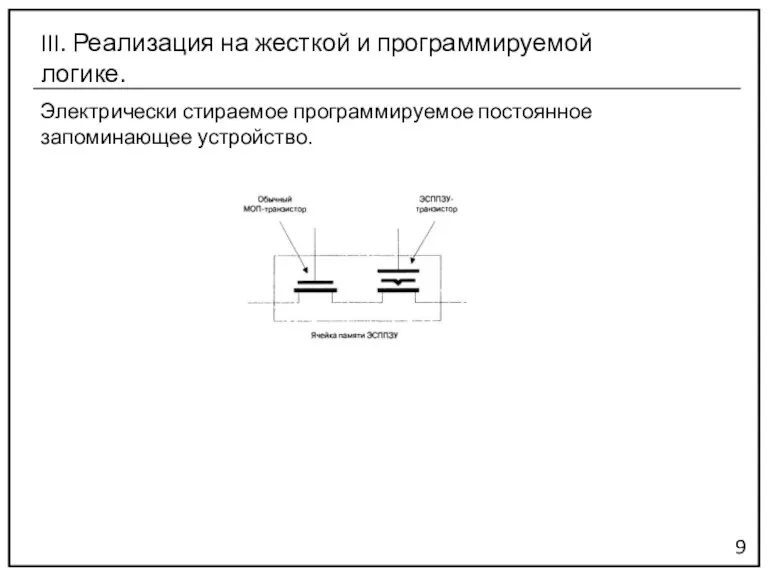

- 10. Электрически стираемое программируемое постоянное запоминающее устройство. 9 III. Реализация на жесткой и программируемой логике.

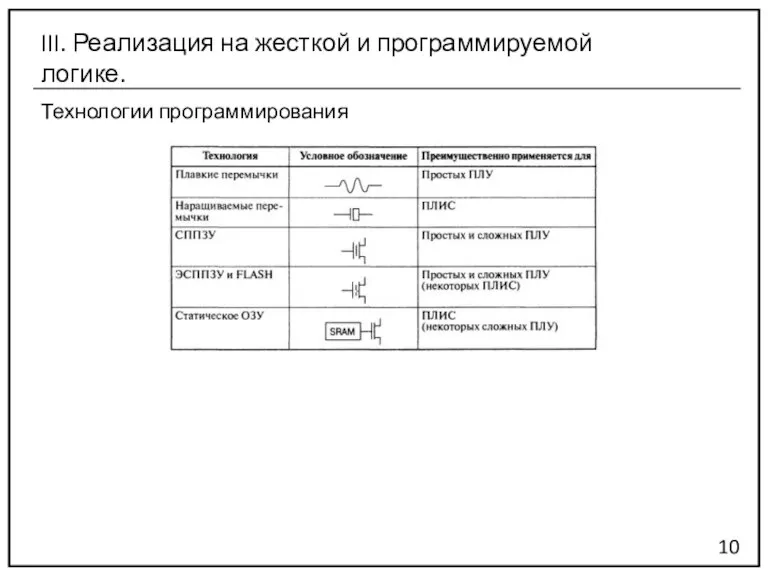

- 11. Технологии программирования 10 III. Реализация на жесткой и программируемой логике.

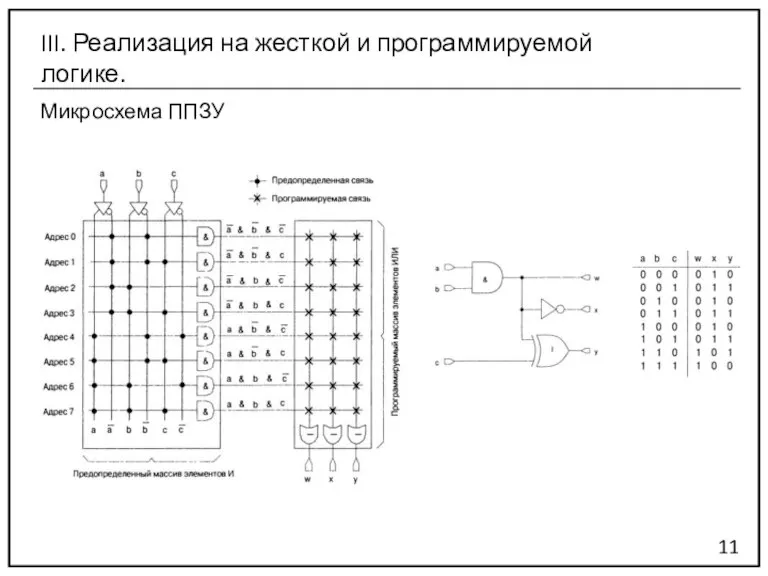

- 12. Микросхема ППЗУ 11 III. Реализация на жесткой и программируемой логике.

- 13. Микросхема ППЗУ 12 III. Реализация на жесткой и программируемой логике.

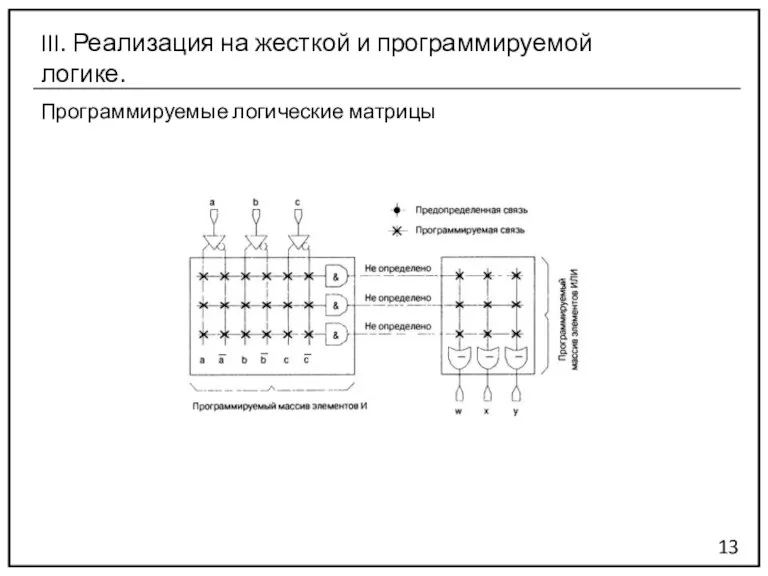

- 14. Программируемые логические матрицы 13 III. Реализация на жесткой и программируемой логике.

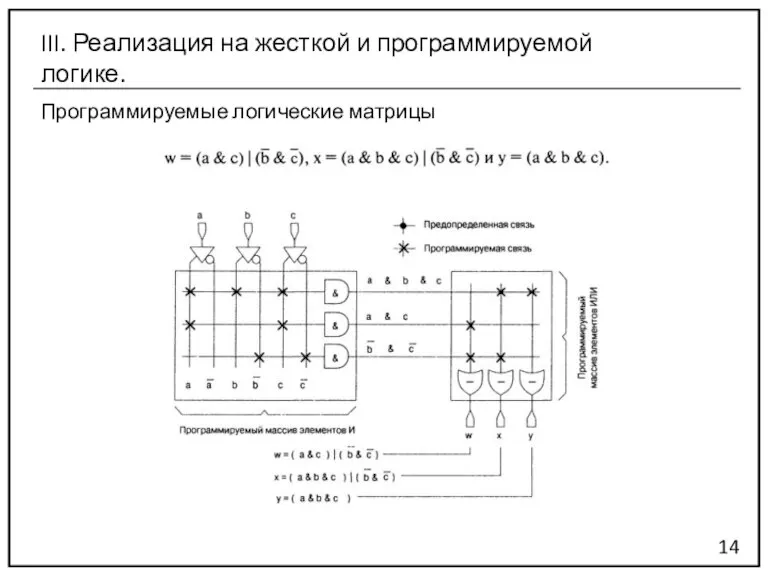

- 15. Программируемые логические матрицы 14 III. Реализация на жесткой и программируемой логике.

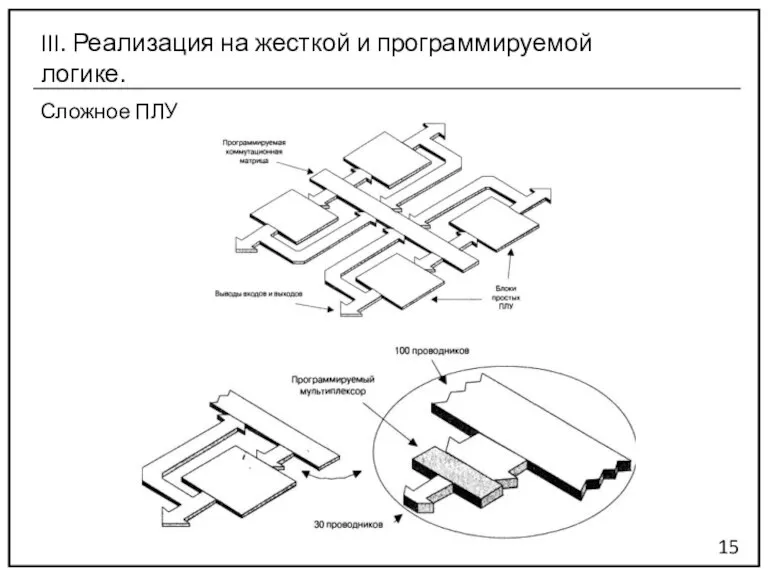

- 16. Сложное ПЛУ 15 III. Реализация на жесткой и программируемой логике.

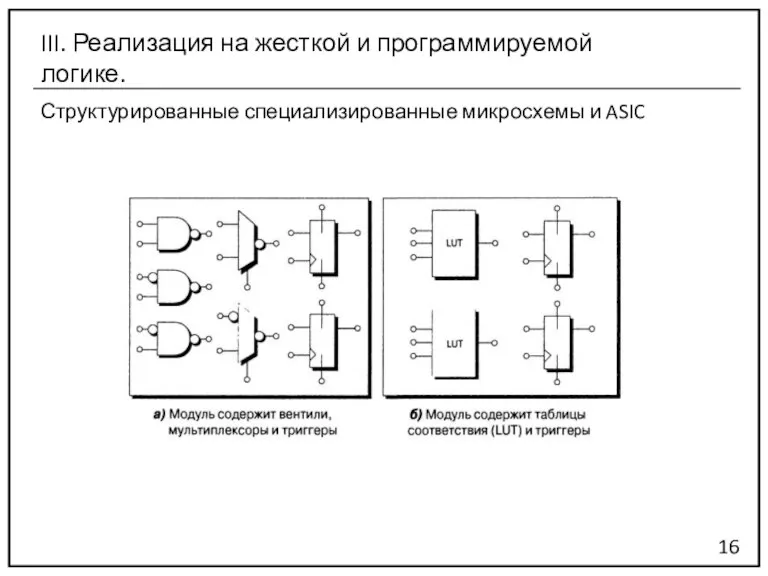

- 17. Структурированные специализированные микросхемы и ASIC 16 III. Реализация на жесткой и программируемой логике.

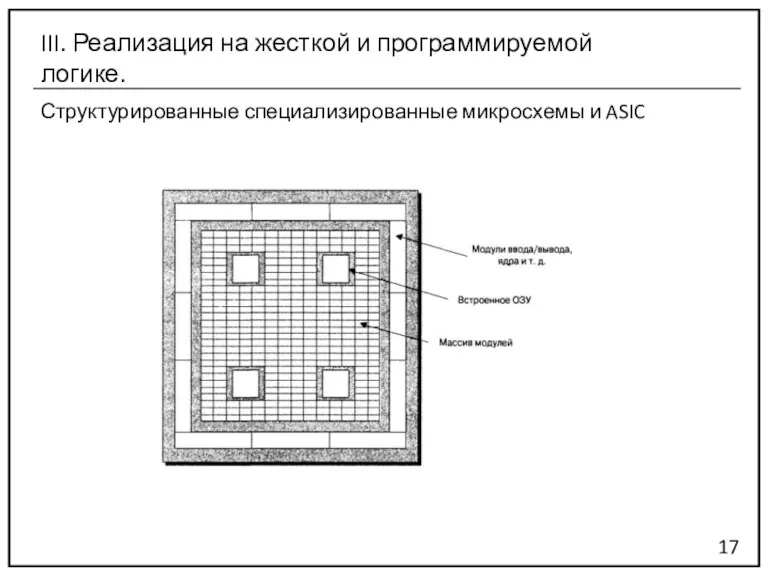

- 18. Структурированные специализированные микросхемы и ASIC 17 III. Реализация на жесткой и программируемой логике.

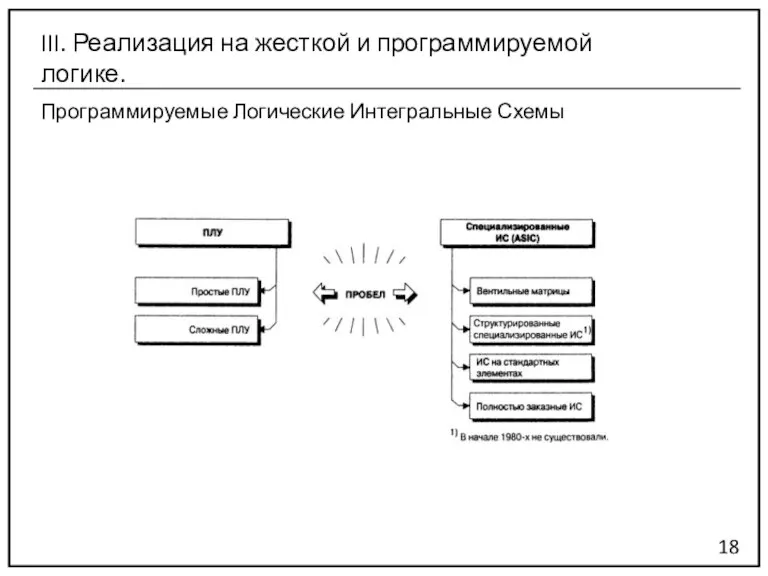

- 19. Программируемые Логические Интегральные Схемы 18 III. Реализация на жесткой и программируемой логике.

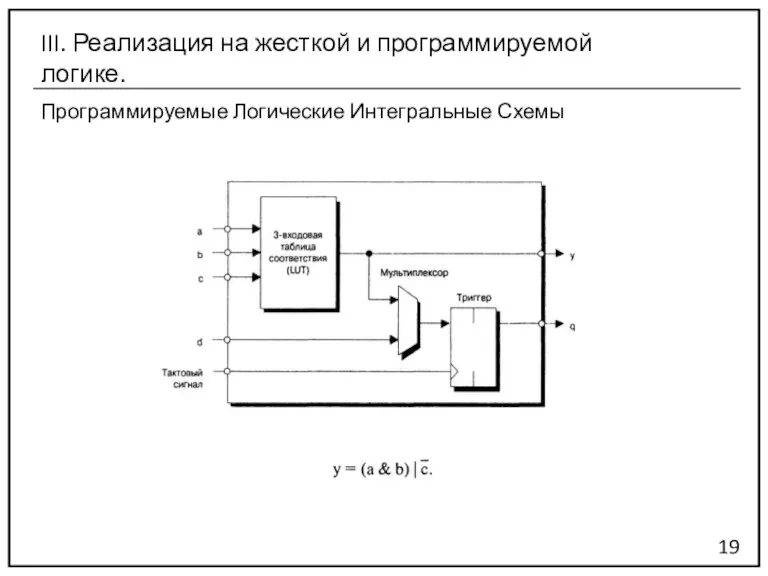

- 20. Программируемые Логические Интегральные Схемы 19 III. Реализация на жесткой и программируемой логике.

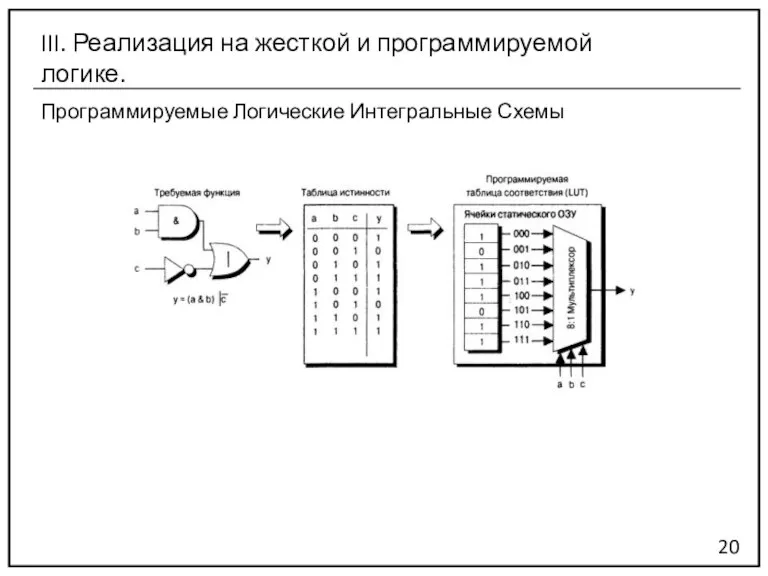

- 21. Программируемые Логические Интегральные Схемы 20 III. Реализация на жесткой и программируемой логике.

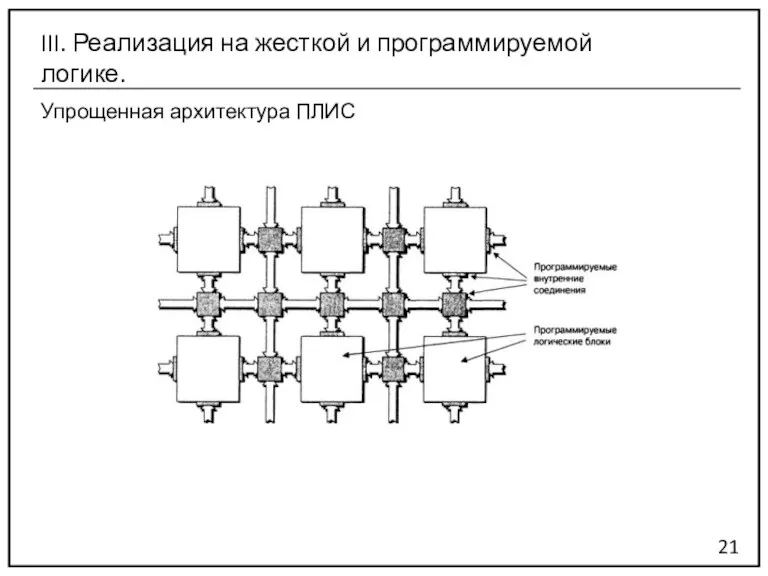

- 22. Упрощенная архитектура ПЛИС 21 III. Реализация на жесткой и программируемой логике.

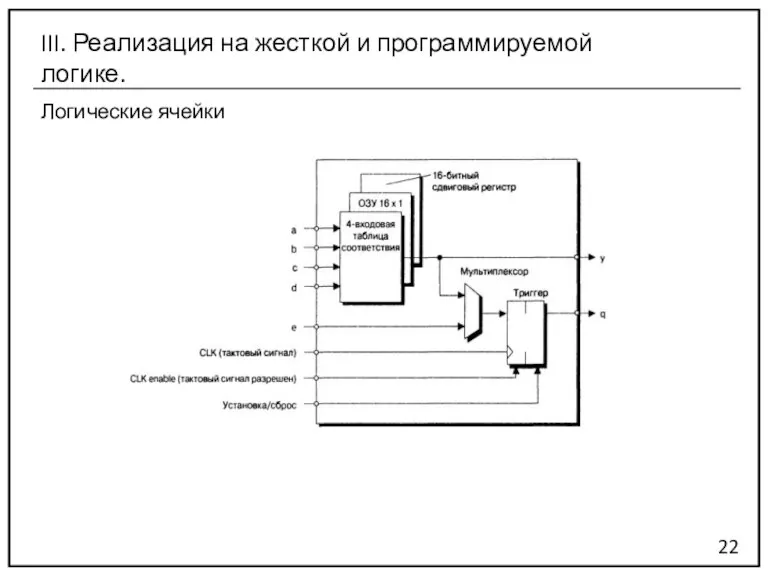

- 23. Логические ячейки 22 III. Реализация на жесткой и программируемой логике.

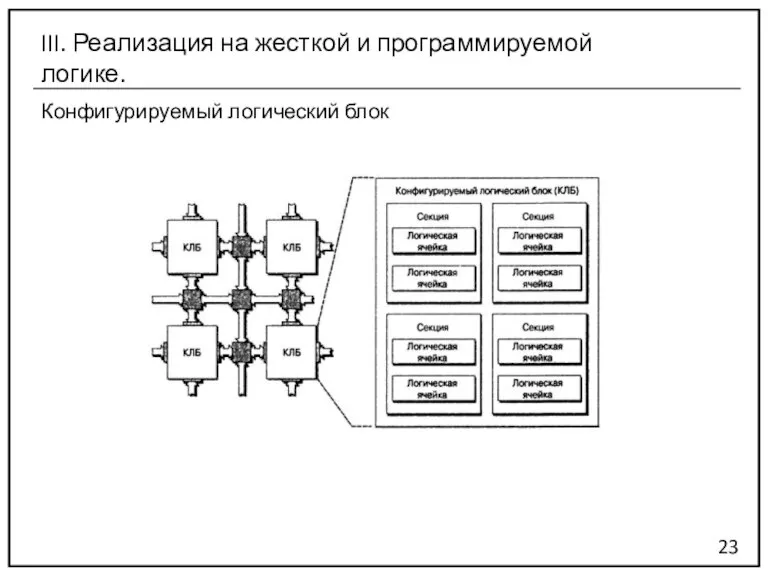

- 24. Конфигурируемый логический блок 23 III. Реализация на жесткой и программируемой логике.

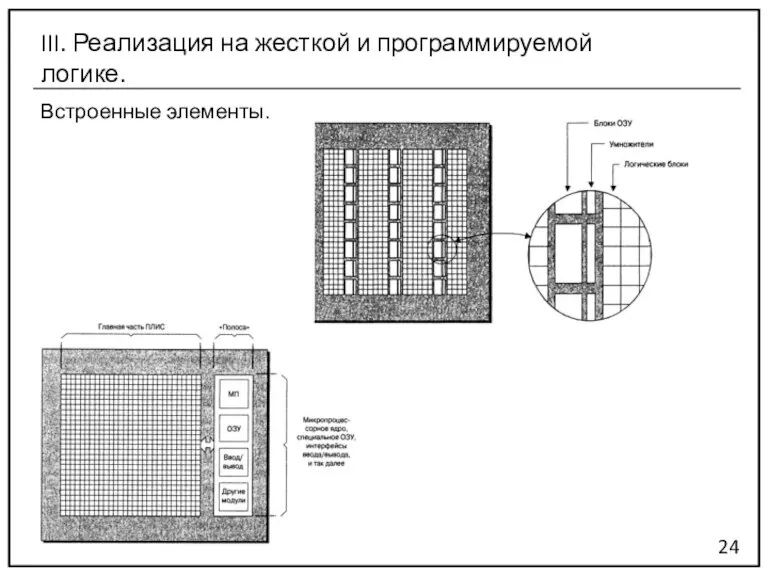

- 25. Встроенные элементы. 24 III. Реализация на жесткой и программируемой логике.

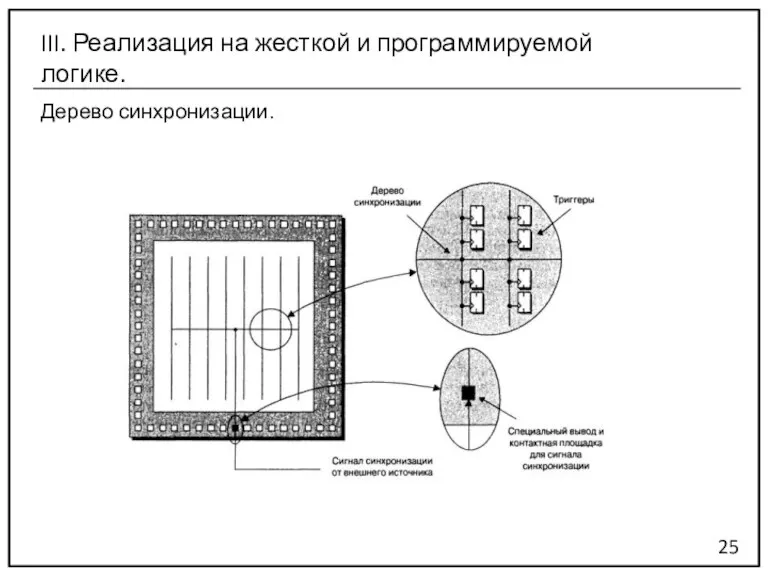

- 26. Дерево синхронизации. 25 III. Реализация на жесткой и программируемой логике.

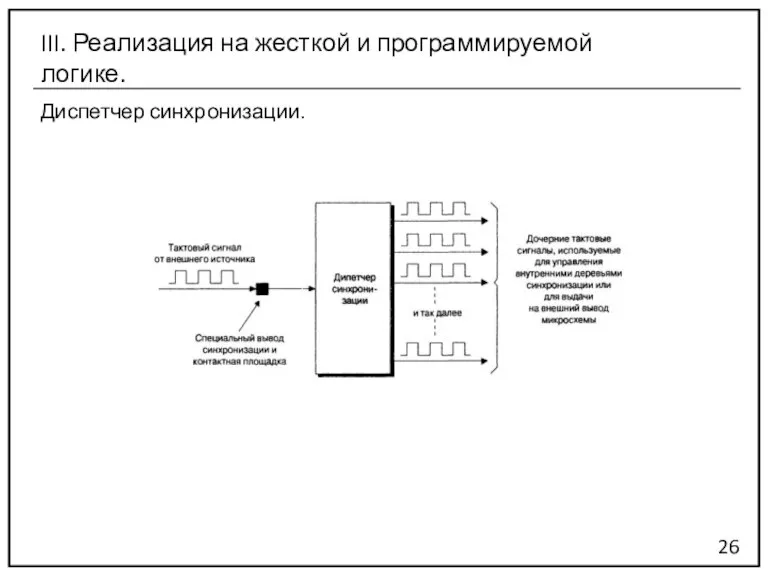

- 27. Диспетчер синхронизации. 26 III. Реализация на жесткой и программируемой логике.

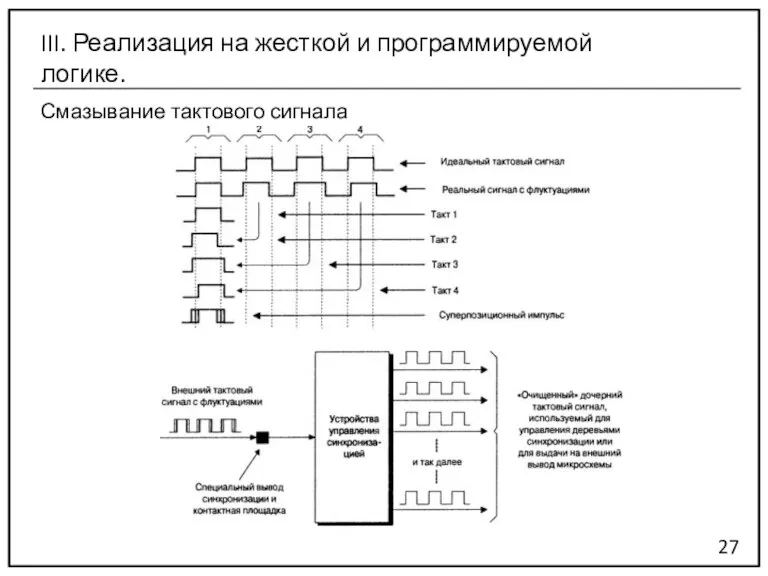

- 28. Смазывание тактового сигнала 27 III. Реализация на жесткой и программируемой логике.

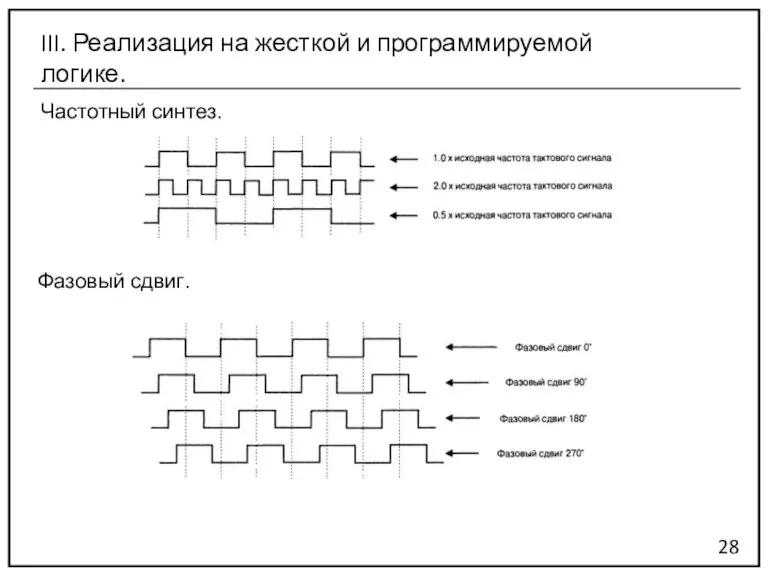

- 29. Частотный синтез. 28 III. Реализация на жесткой и программируемой логике. Фазовый сдвиг.

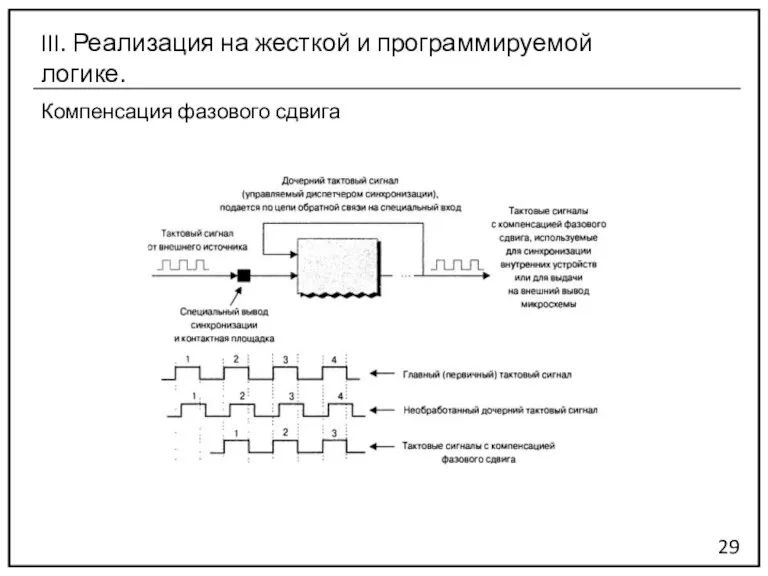

- 30. Компенсация фазового сдвига 29 III. Реализация на жесткой и программируемой логике.

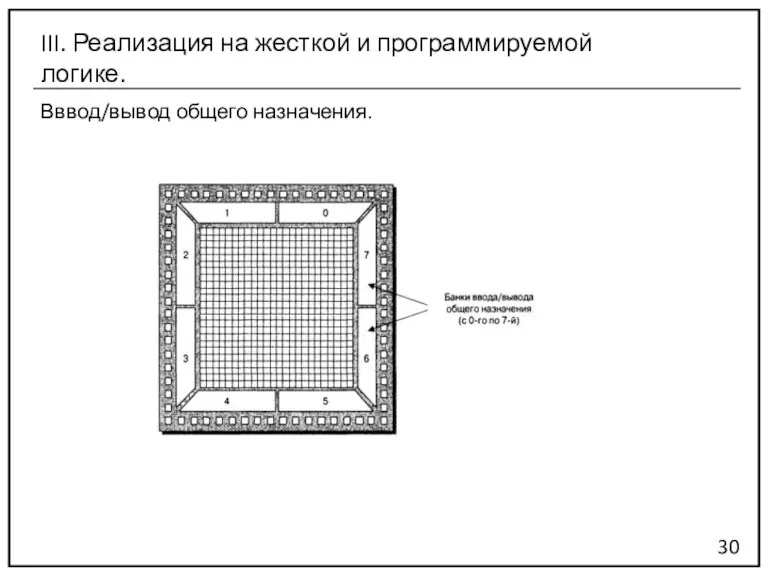

- 31. Вввод/вывод общего назначения. 30 III. Реализация на жесткой и программируемой логике.

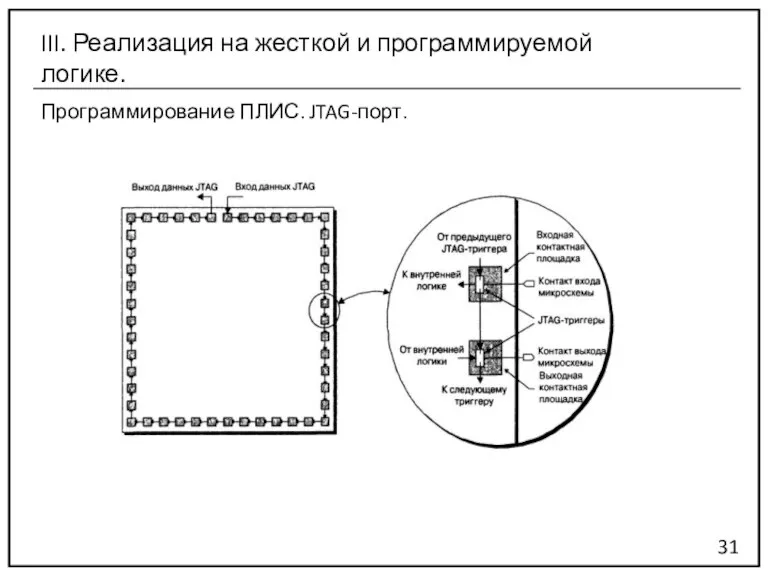

- 32. Программирование ПЛИС. JTAG-порт. 31 III. Реализация на жесткой и программируемой логике.

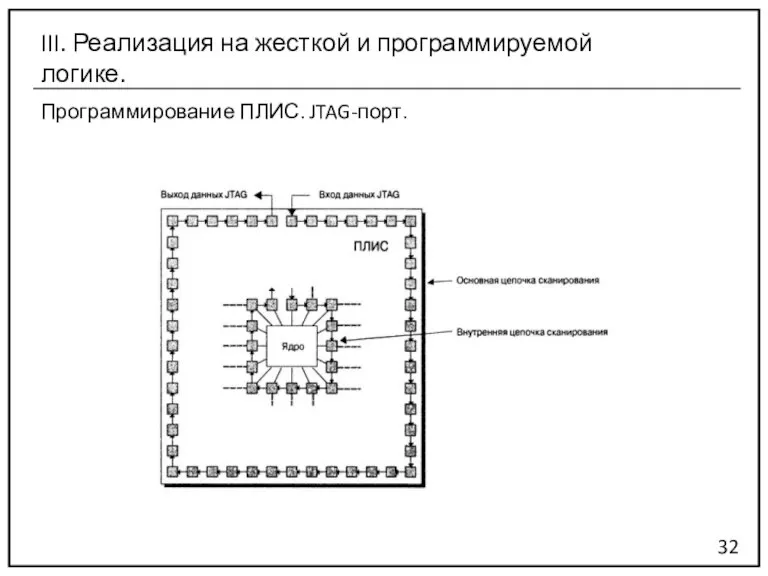

- 33. Программирование ПЛИС. JTAG-порт. 32 III. Реализация на жесткой и программируемой логике.

- 35. Скачать презентацию

TEO-STROY Система для управления строительной фирмой/студией ремонта

TEO-STROY Система для управления строительной фирмой/студией ремонта Программный комплекс Autocad

Программный комплекс Autocad Few words about clouds

Few words about clouds Одномерные массивы и работа со строками

Одномерные массивы и работа со строками Платформа Aliexpress

Платформа Aliexpress 7-1-2

7-1-2 Проецирование. Бинарный урок

Проецирование. Бинарный урок ALGA_CA-32

ALGA_CA-32 Создание формы для базы данных

Создание формы для базы данных Алгоритмы обработки данных при организации электронного архива предприятий радиоэлектронной промышленности на базе PLM-систем

Алгоритмы обработки данных при организации электронного архива предприятий радиоэлектронной промышленности на базе PLM-систем Создание электронного учебного пособия по помехоустойчивым кодам с разработкой справочника

Создание электронного учебного пособия по помехоустойчивым кодам с разработкой справочника Презентация на тему Применение систем счисления

Презентация на тему Применение систем счисления  Базіка - сервіс чат ботів

Базіка - сервіс чат ботів Программное обеспечение. Вводный урок. 8 класс

Программное обеспечение. Вводный урок. 8 класс Разработка АИС Советник для анализа и принятия решений при торговых операций на рынке Forex

Разработка АИС Советник для анализа и принятия решений при торговых операций на рынке Forex Составление и выполнение алгоритмов чертёжника

Составление и выполнение алгоритмов чертёжника Основы проектирования баз данных. Распределенная обработка данных

Основы проектирования баз данных. Распределенная обработка данных Курс Веб-разработка (01)

Курс Веб-разработка (01) Разработка подсистемы управления доступом инфрастуктуры безопасности распределительных информационно-вычислительных систем

Разработка подсистемы управления доступом инфрастуктуры безопасности распределительных информационно-вычислительных систем Олимпиада iSandBOX 2020 Воркшоп 1

Олимпиада iSandBOX 2020 Воркшоп 1 Электронные таблицы. Обработка числовой информации в электронных таблицах

Электронные таблицы. Обработка числовой информации в электронных таблицах Организация локальных и глобальных сетей

Организация локальных и глобальных сетей Создание в социальной сети В контакте группы о Перми с интересной подборкой фактов о городе и его жителях

Создание в социальной сети В контакте группы о Перми с интересной подборкой фактов о городе и его жителях Разработка программного продукта Угадай число на языке программирования C Sharp

Разработка программного продукта Угадай число на языке программирования C Sharp Презентация — это не слайды!

Презентация — это не слайды! Программное обеспечение

Программное обеспечение Информационная безопасность

Информационная безопасность