Основная терминология курса: шейдер, SM, ROP, TPC, SP. Типы параллельных архитектур: SISD, MISD, SIMD, MIMD, DSP

Содержание

- 2. Введение Схематическое изображение графического адаптера Классификация вычислительных систем по Флинну Схематическое устройство SMP Multithreading Bottleneck

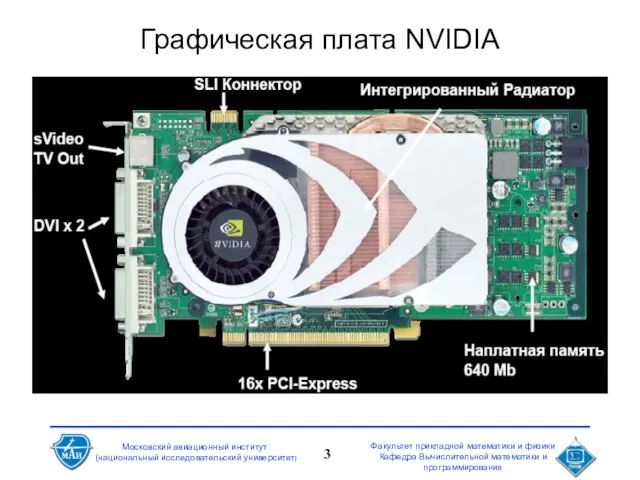

- 3. Графическая плата NVIDIA

- 4. Средства обмена данными в компьютере Обмен данными – важнейшая составляющая компьютера Примеры: многопроцессорные системы, FPGA etc.

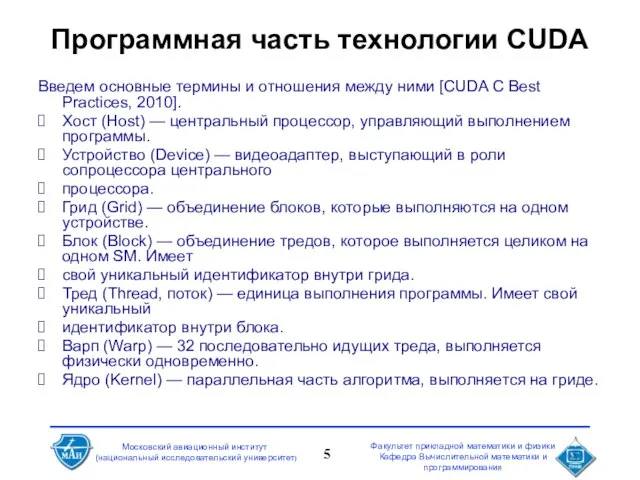

- 5. Программная часть технологии CUDA Введем основные термины и отношения между ними [CUDA C Best Practices, 2010].

- 6. Схематическое изображение графического адаптера

- 7. DSP Цифровой сигнальный процессор (англ. Digital signal processor, DSP; сигнальный микропроцессор, СМП; процессор цифровых сигналов, ПЦС)

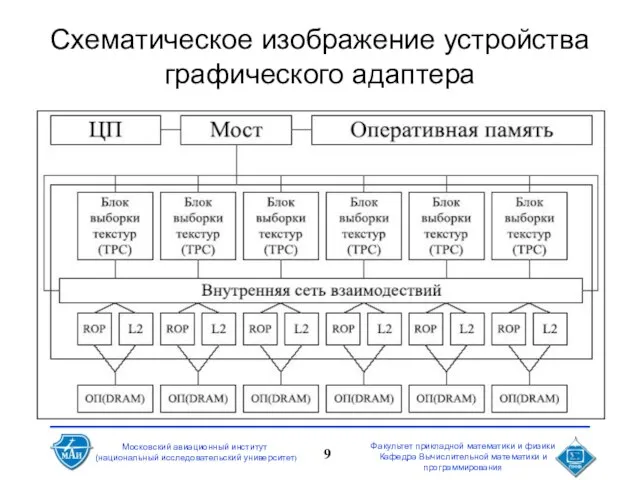

- 9. Схематическое изображение устройства графического адаптера

- 10. Схематические особенности видеочипа

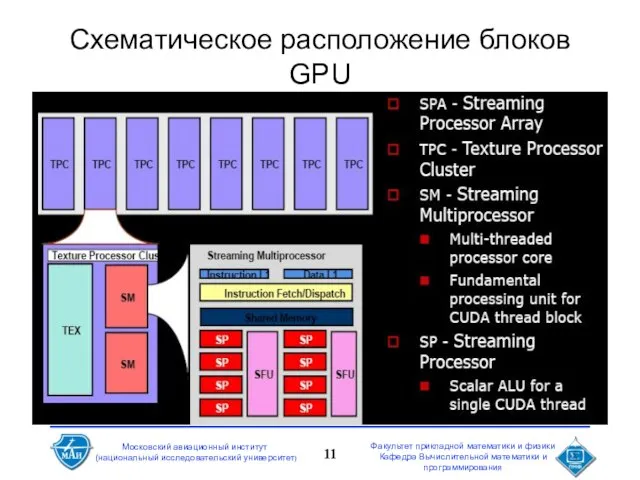

- 11. Схематическое расположение блоков GPU

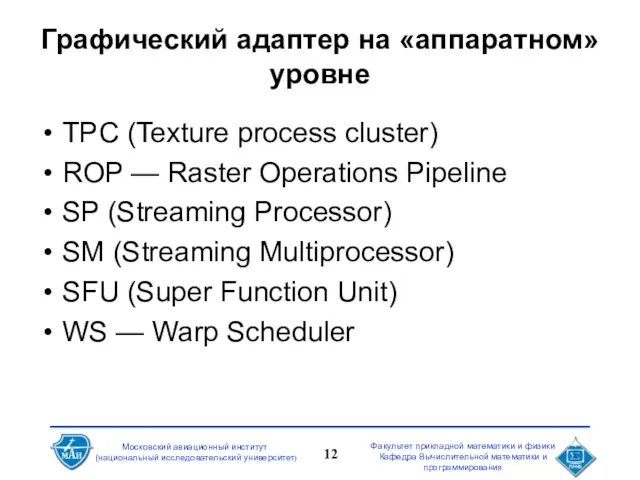

- 12. Графический адаптер на «аппаратном» уровне TPC (Texture process cluster) ROP — Raster Operations Pipeline SP (Streaming

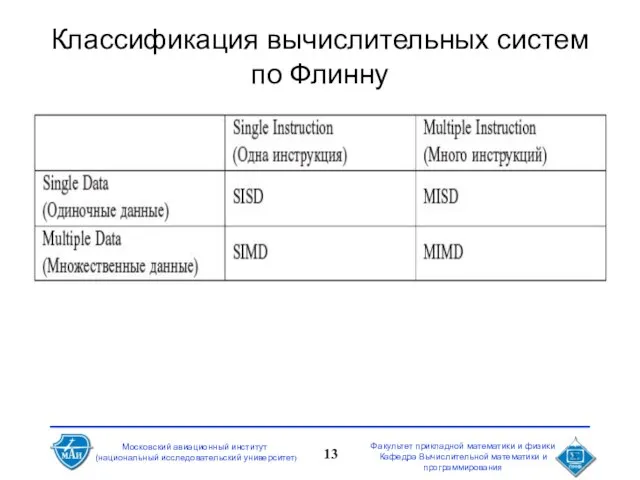

- 13. Классификация вычислительных систем по Флинну

- 14. Классы систем

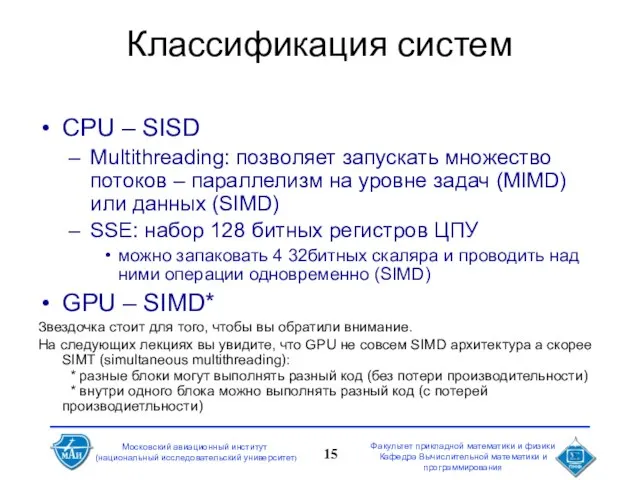

- 15. Классификация систем CPU – SISD Multithreading: позволяет запускать множество потоков – параллелизм на уровне задач (MIMD)

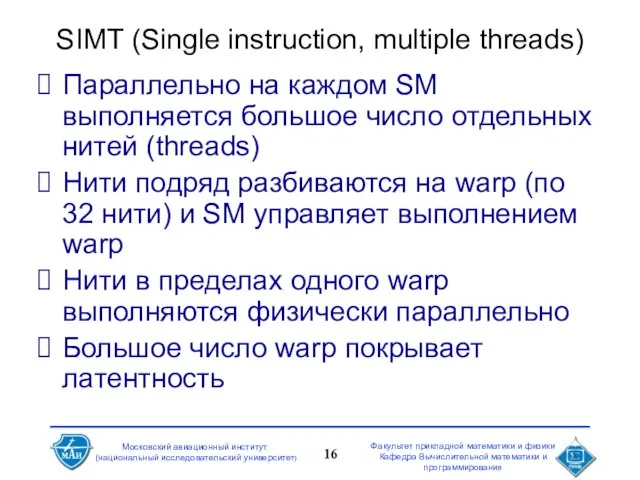

- 16. SIMT (Single instruction, multiple threads) Параллельно на каждом SM выполняется большое число отдельных нитей (threads) Нити

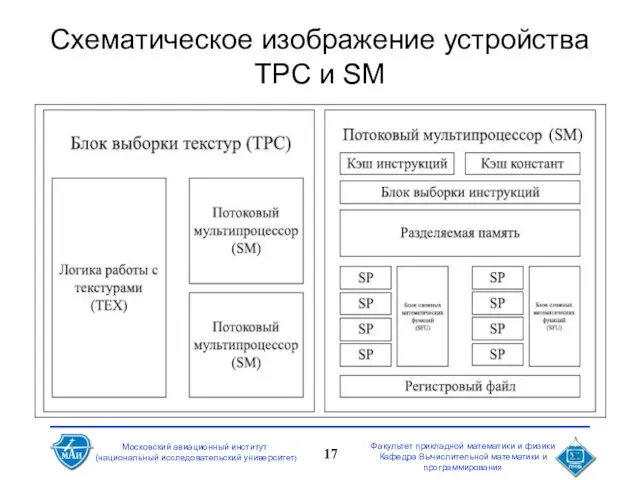

- 17. Схематическое изображение устройства TPC и SM

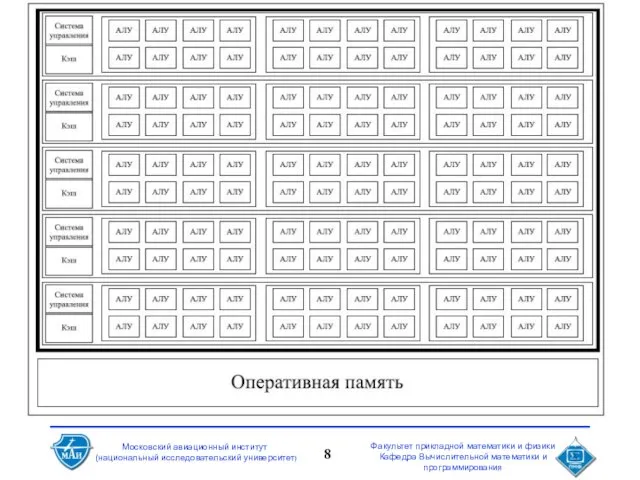

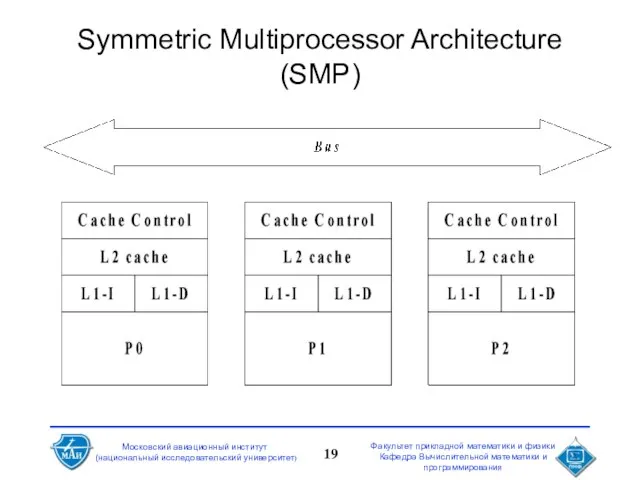

- 18. Symmetric Multiprocessor Architecture (SMP) Каждый процессор имеет свои L1 и L2 кэши подсоединен к общей шине

- 19. Symmetric Multiprocessor Architecture (SMP)

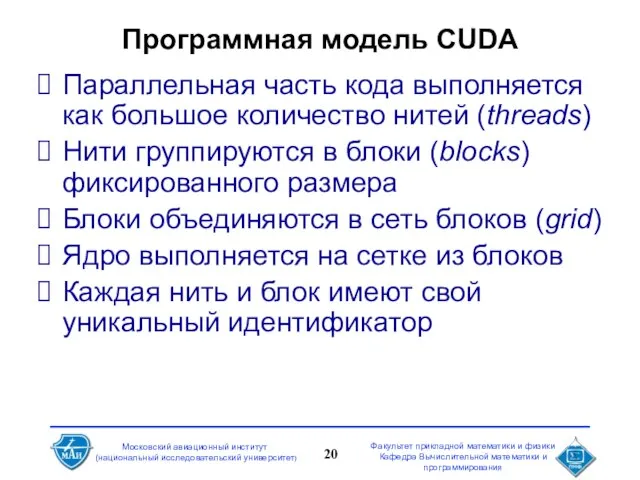

- 20. Программная модель CUDA Параллельная часть кода выполняется как большое количество нитей (threads) Нити группируются в блоки

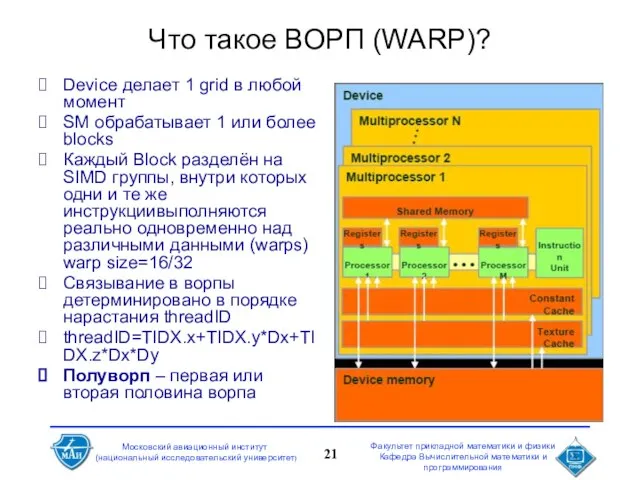

- 21. Что такое ВОРП (WARP)? Device делает 1 grid в любой момент SM обрабатывает 1 или более

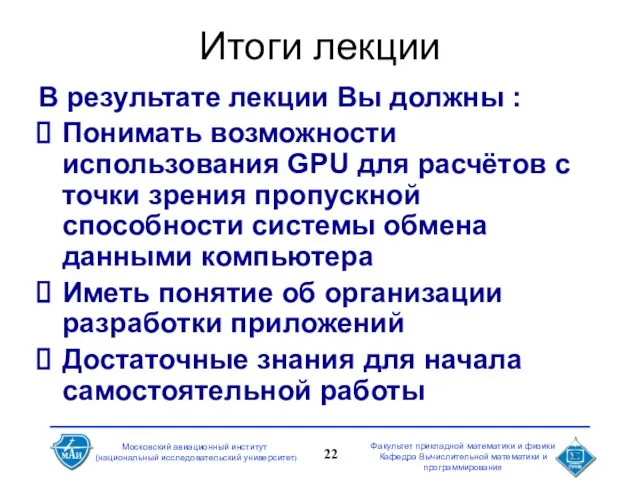

- 22. Итоги лекции В результате лекции Вы должны : Понимать возможности использования GPU для расчётов с точки

- 24. Скачать презентацию

Элементы теории фредгольмовых отображений

Элементы теории фредгольмовых отображений Многоугольники

Многоугольники Площадь треугольника

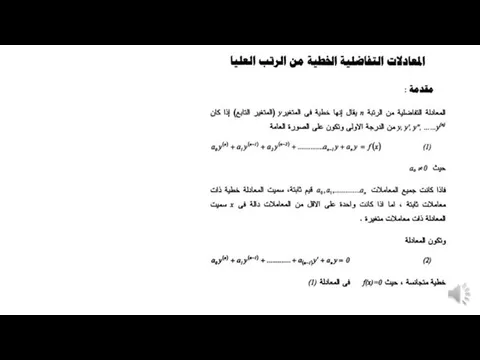

Площадь треугольника المعادلات التفاضلية ذات الرتبة الأعلى (المحاضرة رقم 6)

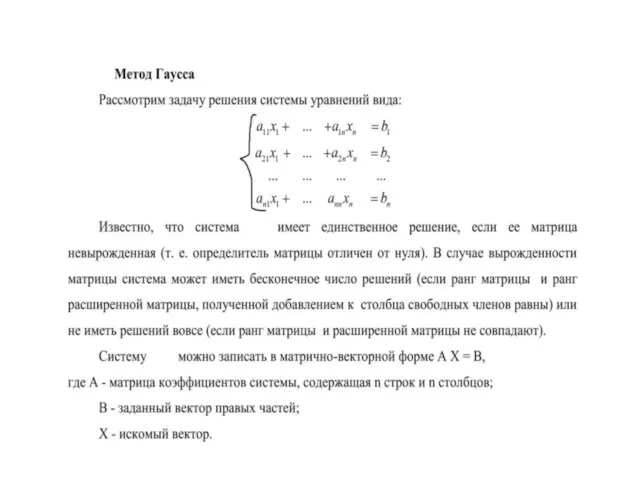

المعادلات التفاضلية ذات الرتبة الأعلى (المحاضرة رقم 6) Метод Гаусса

Метод Гаусса Векторный анализ -теория поля. Типы векторных полей. Лекция 18

Векторный анализ -теория поля. Типы векторных полей. Лекция 18 Разложение многочленов на множители с помощью комбинации различных приёмов

Разложение многочленов на множители с помощью комбинации различных приёмов Граница круга

Граница круга Дифференциальное уравнение движения поезда и его анализ

Дифференциальное уравнение движения поезда и его анализ Перестановки, размещения, сочетания без повторений

Перестановки, размещения, сочетания без повторений Производная функция

Производная функция Вписанные и описанные четырехугольники

Вписанные и описанные четырехугольники Математический маятник. Измерения

Математический маятник. Измерения Задача про комбинацию окружностей и квадрата и её обобщение от Тимофея Гаврикова

Задача про комбинацию окружностей и квадрата и её обобщение от Тимофея Гаврикова Формы графического изображения. (Лекция 3)

Формы графического изображения. (Лекция 3) Презентация на тему Задачи на движение для учителя

Презентация на тему Задачи на движение для учителя  Прямоугольник

Прямоугольник Параллельность плоскостей

Параллельность плоскостей Пирамиды

Пирамиды Уравнения и неравенства с одной переменной

Уравнения и неравенства с одной переменной Дроби. Десятичные дроби. Контрольный работа

Дроби. Десятичные дроби. Контрольный работа Презентация_по_математике_Высказывания_и_операции_над_ними_10_класс

Презентация_по_математике_Высказывания_и_операции_над_ними_10_класс Скалярное произведение векторов

Скалярное произведение векторов Лекция 2

Лекция 2 Основное свойство алгебраической дроби

Основное свойство алгебраической дроби Выражение в инфиксной форме. Выражение в постфиксной форме

Выражение в инфиксной форме. Выражение в постфиксной форме Число потоков в графе

Число потоков в графе Таблица умножения числа 2 и на число 2

Таблица умножения числа 2 и на число 2