Содержание

- 2. Содержание Основные понятия Полусумматор Сумматор Построение схемы последовательного сумматора Работа сумматора

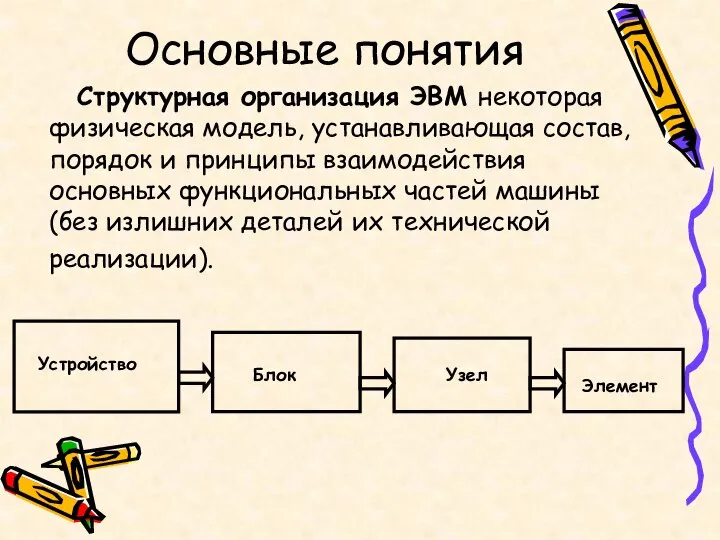

- 3. Основные понятия Структурная организация ЭВМ некоторая физическая модель, устанавливающая состав, порядок и принципы взаимодействия основных функциональных

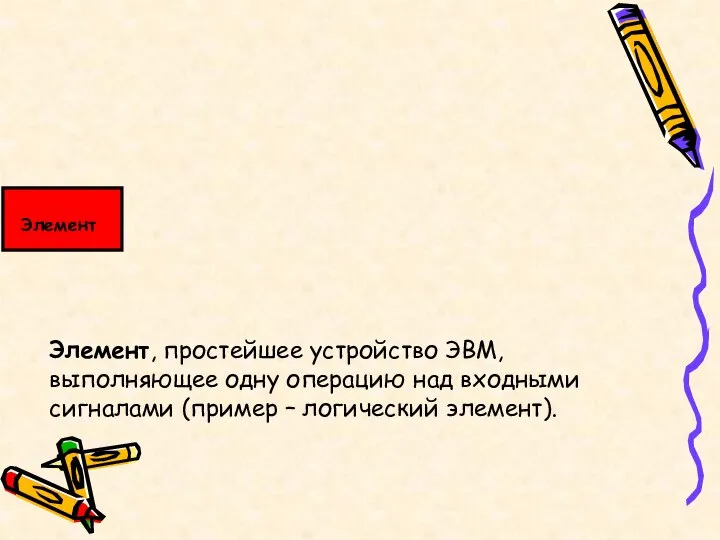

- 4. Элемент, простейшее устройство ЭВМ, выполняющее одну операцию над входными сигналами (пример – логический элемент).

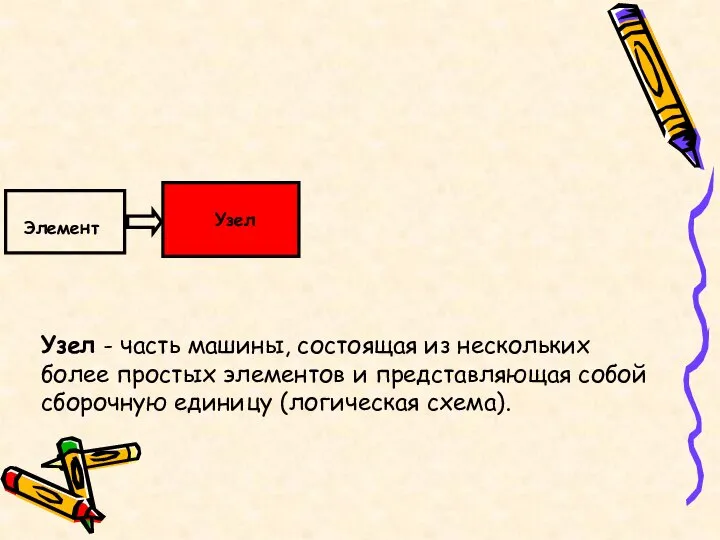

- 5. Узел - часть машины, состоящая из нескольких более простых элементов и представляющая собой сборочную единицу (логическая

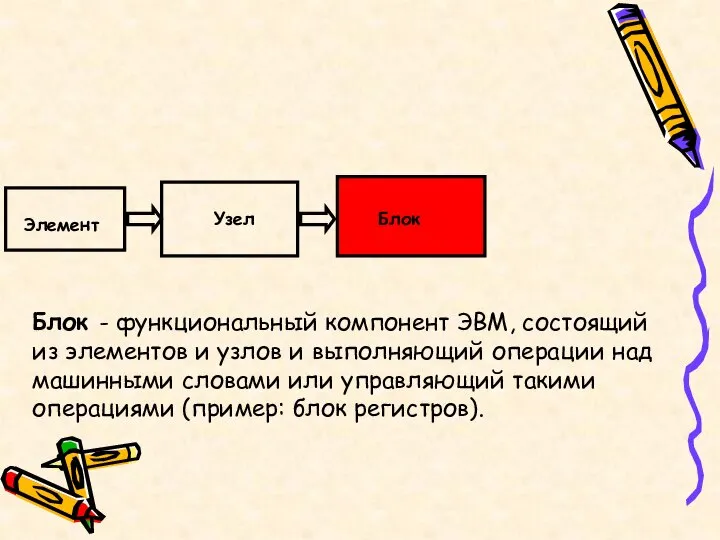

- 6. Блок - функциональный компонент ЭВМ, состоящий из элементов и узлов и выполняющий операции над машинными словами

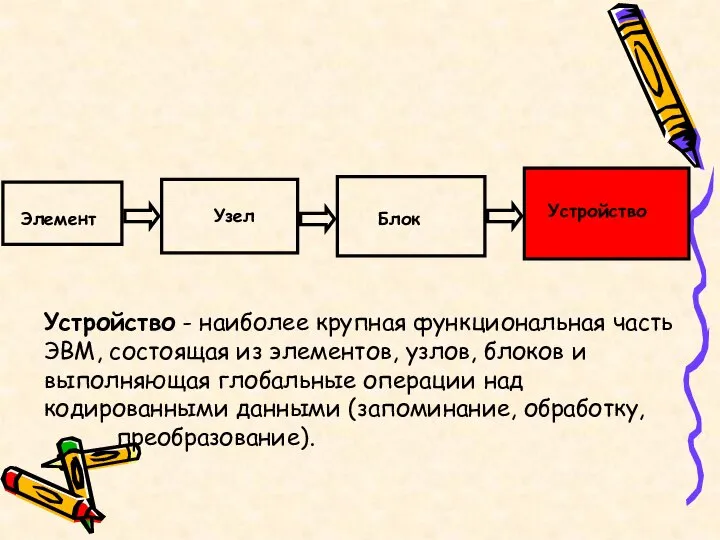

- 7. Устройство - наиболее крупная функциональная часть ЭВМ, состоящая из элементов, узлов, блоков и выполняющая глобальные операции

- 8. Узел ЭВМ выполняющий арифметическое суммирование кодов чисел, называется сумматором.

- 9. Операция суммирования осуществляется в сумматорах поразрядно с использованием одноразрядных суммирующих схем. При этом в каждом разряде

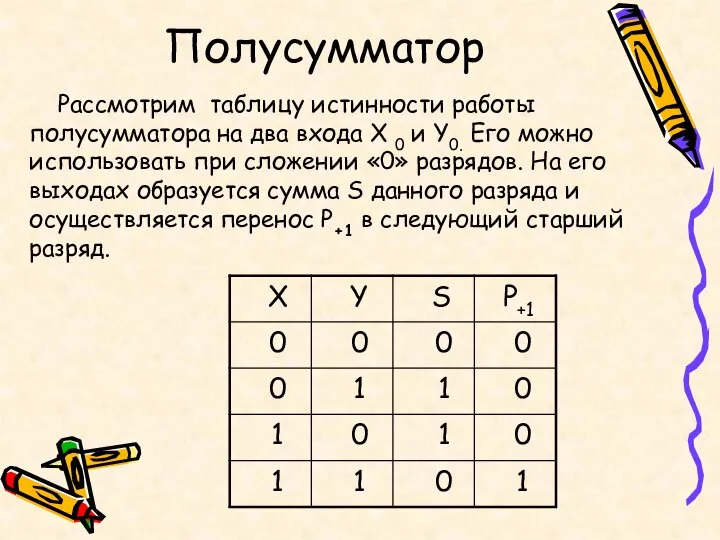

- 10. Полусумматор Рассмотрим таблицу истинности работы полусумматора на два входа X 0 и Y0. Его можно использовать

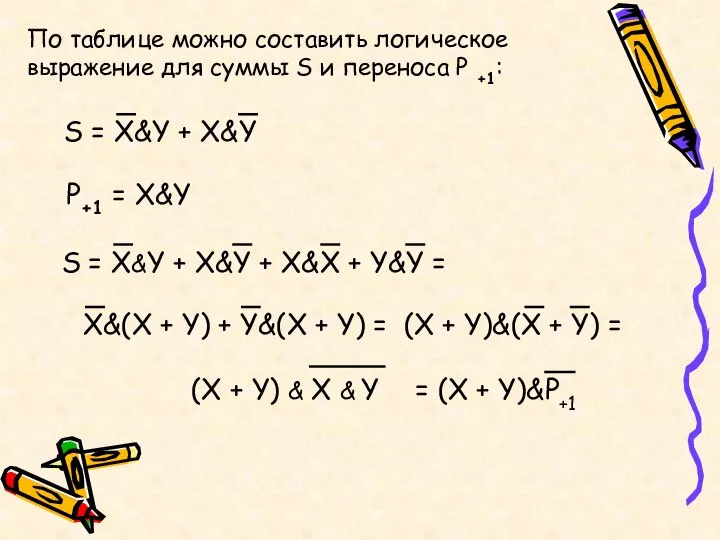

- 11. По таблице можно составить логическое выражение для суммы S и переноса Р +1: P+1 = X&Y

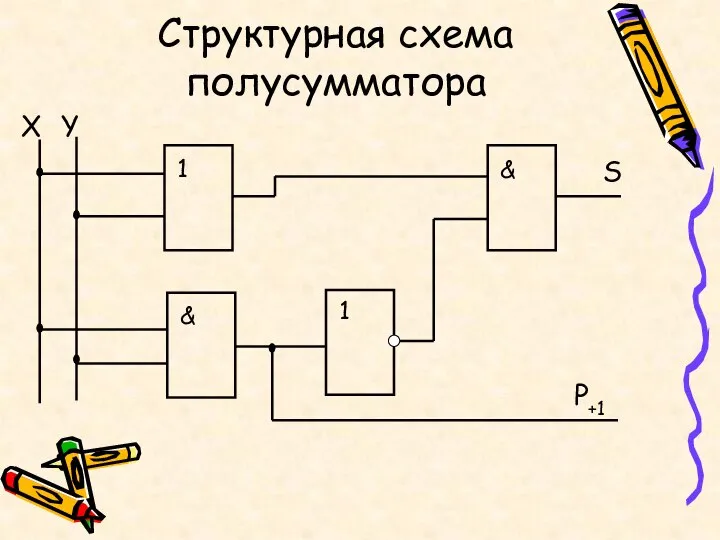

- 12. Структурная схема полусумматора

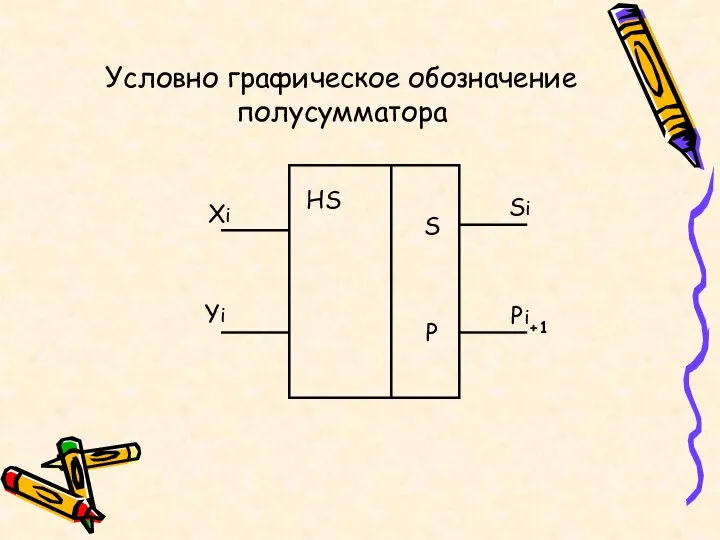

- 13. Условно графическое обозначение полусумматора HS S P Xi Yi Si Pi+1

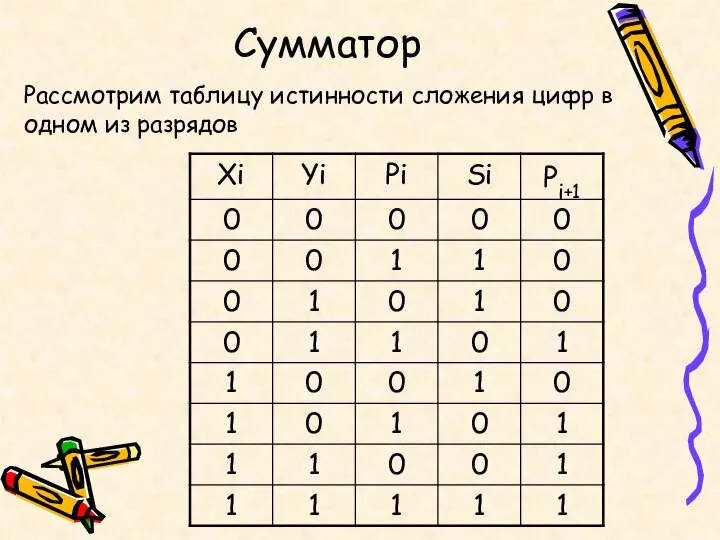

- 14. Сумматор Рассмотрим таблицу истинности сложения цифр в одном из разрядов

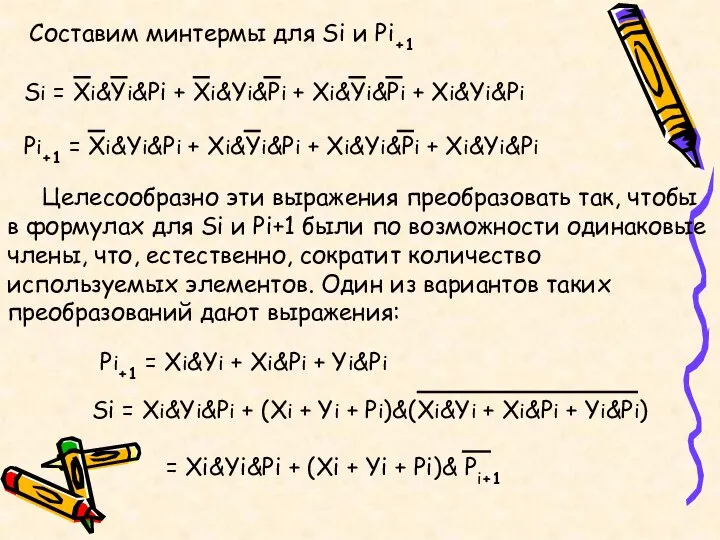

- 15. Составим минтермы для Si и Pi+1 Целесообразно эти выражения преобразовать так, чтобы в формулах для Si

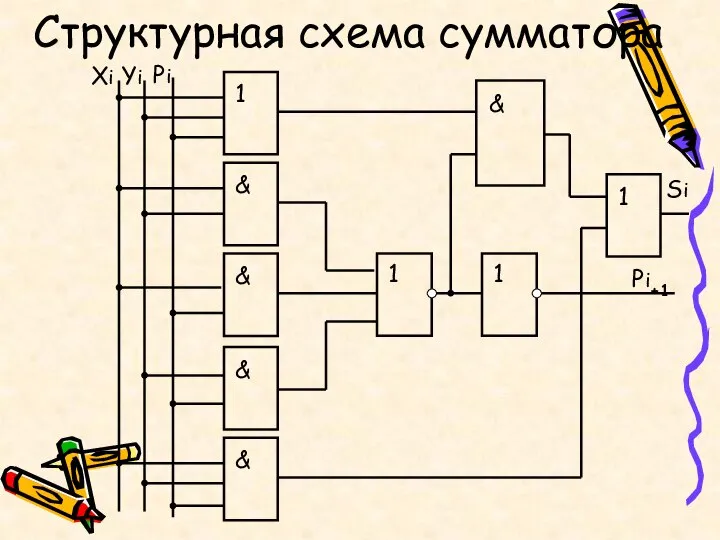

- 16. Структурная схема сумматора

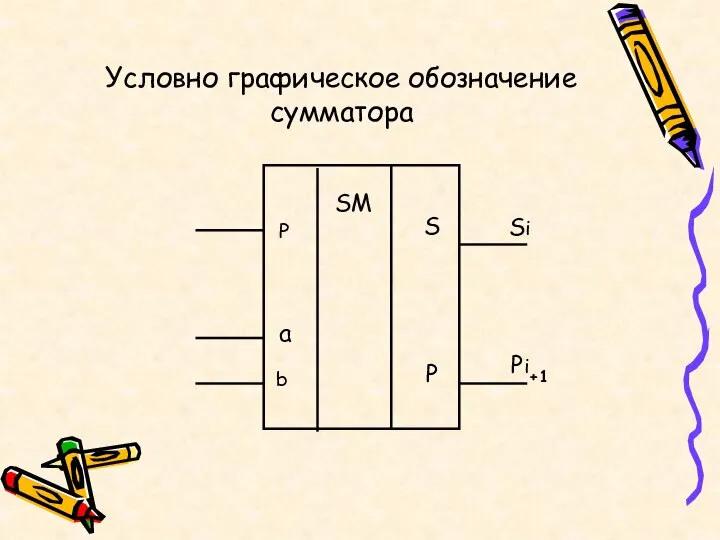

- 17. SM S P Si Pi+1 a b P Условно графическое обозначение сумматора

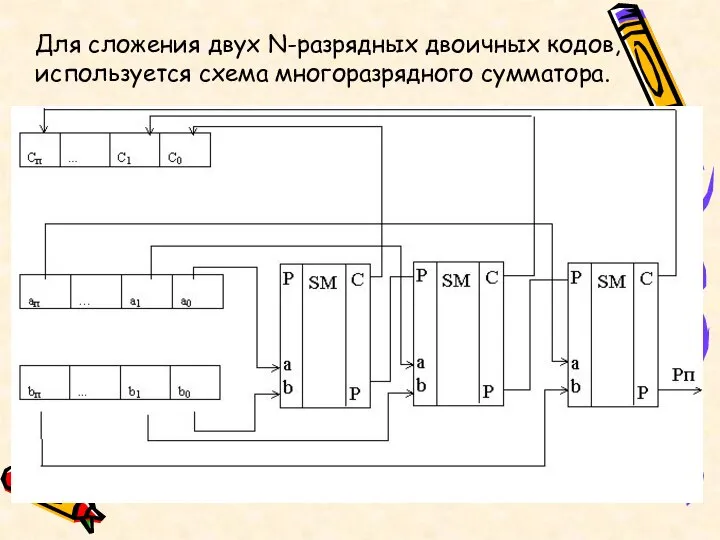

- 18. Для сложения двух N-разрядных двоичных кодов, используется схема многоразрядного сумматора.

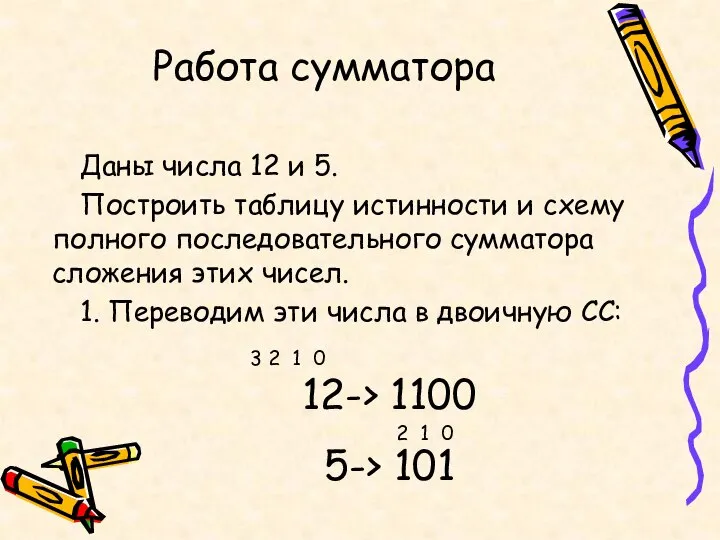

- 19. Работа сумматора Даны числа 12 и 5. Построить таблицу истинности и схему полного последовательного сумматора сложения

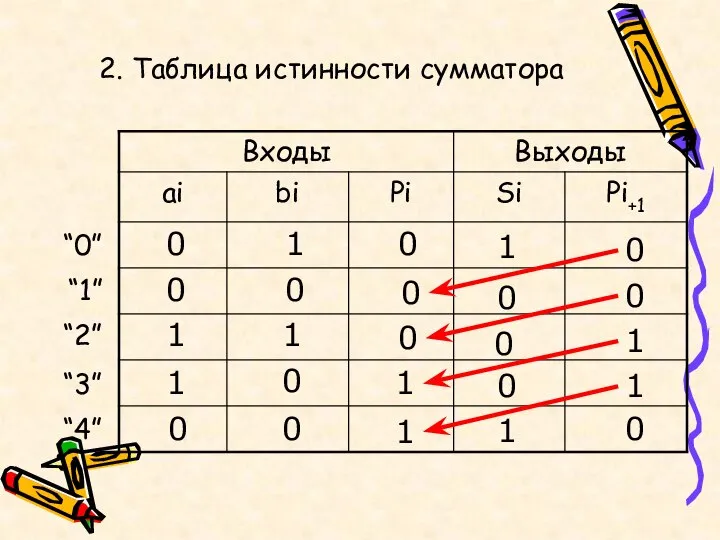

- 20. 2. Таблица истинности сумматора 0 1 1 0 0 0 0 0 0 0 1 1

- 21. Структурная схема сумматора 0

- 23. Скачать презентацию

Презентация на тему Приложение (8 класс)

Презентация на тему Приложение (8 класс) Роль христианства в становлении средневековой культуры

Роль христианства в становлении средневековой культуры Эффективные модели обновления систем повышения квалификации и аттестации педагогических кадров

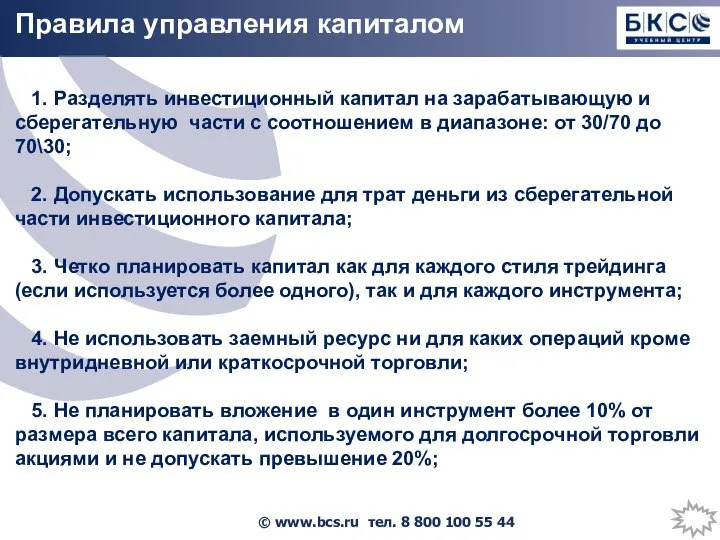

Эффективные модели обновления систем повышения квалификации и аттестации педагогических кадров Правила управления капиталом

Правила управления капиталом Субъект, объект и предмет науки

Субъект, объект и предмет науки Title

Title  Изменения слизистой оболочки полости рта при дерматозах с аутоиммунным компонентом

Изменения слизистой оболочки полости рта при дерматозах с аутоиммунным компонентом Функция арифметического квадратного корня

Функция арифметического квадратного корня Кислород. Получение кислорода и его физические свойства

Кислород. Получение кислорода и его физические свойства Химия и производство. 11 класс

Химия и производство. 11 класс Рейтинги устойчивого развития регионов Российской Федерации

Рейтинги устойчивого развития регионов Российской Федерации 10-11 класс

10-11 класс Презентация на тему Игра с интерактивной доской «Немецкая и венгерская школа»

Презентация на тему Игра с интерактивной доской «Немецкая и венгерская школа» Право на службе человека

Право на службе человека Производство, передача и использование электрической энергии

Производство, передача и использование электрической энергии Беседа о толерантности для учащихся 2 класса

Беседа о толерантности для учащихся 2 класса Авторское право

Авторское право Встречай Новый год с Essens (Чешская парфюмерно-косметическая фирма)

Встречай Новый год с Essens (Чешская парфюмерно-косметическая фирма) Млекопитающие

Млекопитающие Понятие и виды государственных служащих

Понятие и виды государственных служащих Цветы из ткани

Цветы из ткани Образование деепричастий совершенного и несовершенного вида

Образование деепричастий совершенного и несовершенного вида Соединение деталей из древесины на клею

Соединение деталей из древесины на клею Узнаваемое лицо. Как увеличить аудиторию в социальных сетях

Узнаваемое лицо. Как увеличить аудиторию в социальных сетях Выполнение финансового плана по дополнительному образованию на сентябрь-декабрь 2017 года

Выполнение финансового плана по дополнительному образованию на сентябрь-декабрь 2017 года Урок доброты по произведению В.Распутина«Уроки французского».

Урок доброты по произведению В.Распутина«Уроки французского». Business Letter Formats

Business Letter Formats  Презентация на тему Многонациональная Россия

Презентация на тему Многонациональная Россия