Содержание

- 2. Два основных режима: Real Address Mode (реальный режим); Protected Virtual Address Mode (защищенный режим). Новые возможности

- 3. Добавлены новые флаги: ID Flag (ID, 21 бит) – Если возможно программно устанавливать и сбрасывать этот

- 4. Расположение дескрипторных таблиц определяется регистрами процессора: GDTR (Global Descriptor Table Register), IDTR (Interrupt Descriptor Table Register),

- 5. Сегментная адресация в защищенном режиме

- 7. Скачать презентацию

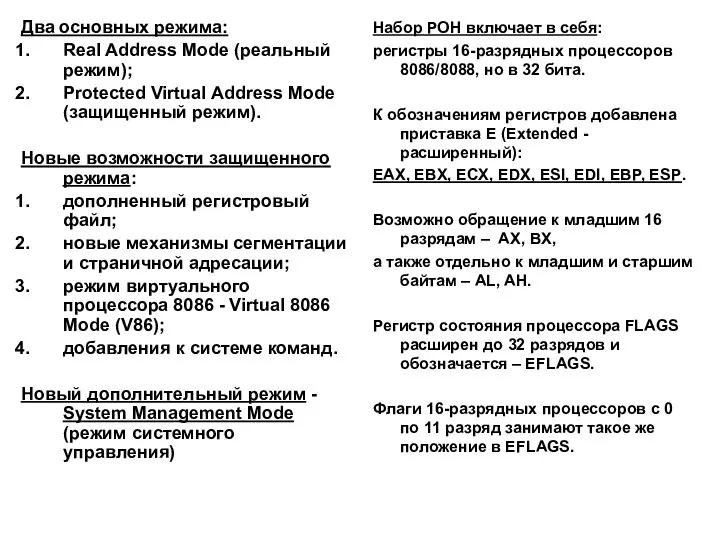

Слайд 2Два основных режима:

Real Address Mode (реальный режим);

Protected Virtual Address Mode (защищенный режим).

Новые

Два основных режима:

Real Address Mode (реальный режим);

Protected Virtual Address Mode (защищенный режим).

Новые

дополненный регистровый файл;

новые механизмы сегментации и страничной адресации;

режим виртуального процессора 8086 - Virtual 8086 Mode (V86);

добавления к системе команд.

Новый дополнительный режим - System Management Mode (режим системного управления)

Набор РОН включает в себя:

регистры 16-разрядных процессоров 8086/8088, но в 32 бита.

К обозначениям регистров добавлена приставка E (Extended - расширенный):

EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP.

Возможно обращение к младшим 16 разрядам – AX, BX,

а также отдельно к младшим и старшим байтам – AL, AH.

Регистр состояния процессора FLAGS расширен до 32 разрядов и обозначается – EFLAGS.

Флаги 16-разрядных процессоров с 0 по 11 разряд занимают такое же положение в EFLAGS.

Слайд 3Добавлены новые флаги:

ID Flag (ID, 21 бит) – Если возможно программно устанавливать

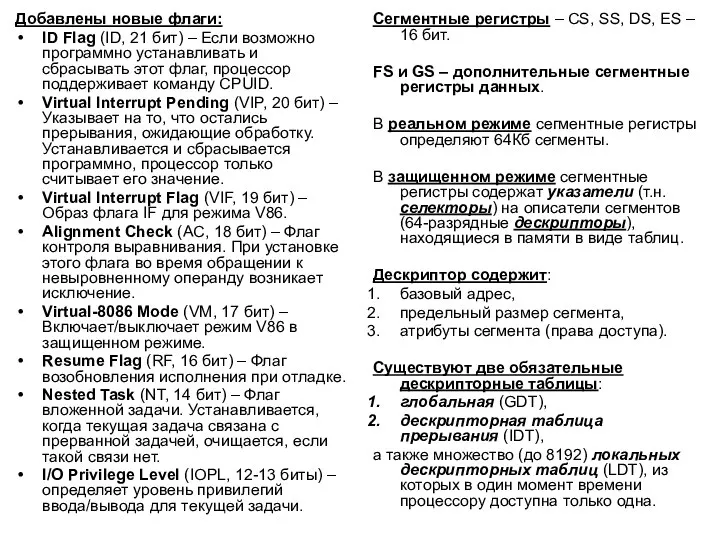

Добавлены новые флаги:

ID Flag (ID, 21 бит) – Если возможно программно устанавливать

Virtual Interrupt Pending (VIP, 20 бит) – Указывает на то, что остались прерывания, ожидающие обработку. Устанавливается и сбрасывается программно, процессор только считывает его значение.

Virtual Interrupt Flag (VIF, 19 бит) – Образ флага IF для режима V86.

Alignment Check (AC, 18 бит) – Флаг контроля выравнивания. При установке этого флага во время обращении к невыровненному операнду возникает исключение.

Virtual-8086 Mode (VM, 17 бит) – Включает/выключает режим V86 в защищенном режиме.

Resume Flag (RF, 16 бит) – Флаг возобновления исполнения при отладке.

Nested Task (NT, 14 бит) – Флаг вложенной задачи. Устанавливается, когда текущая задача связана с прерванной задачей, очищается, если такой связи нет.

I/O Privilege Level (IOPL, 12-13 биты) – определяет уровень привилегий ввода/вывода для текущей задачи.

Сегментные регистры – CS, SS, DS, ES – 16 бит.

FS и GS – дополнительные сегментные регистры данных.

В реальном режиме сегментные регистры определяют 64Кб сегменты.

В защищенном режиме сегментные регистры содержат указатели (т.н. селекторы) на описатели сегментов (64-разрядные дескрипторы), находящиеся в памяти в виде таблиц.

Дескриптор содержит:

базовый адрес,

предельный размер сегмента,

атрибуты сегмента (права доступа).

Существуют две обязательные дескрипторные таблицы:

глобальная (GDT),

дескрипторная таблица прерывания (IDT),

а также множество (до 8192) локальных дескрипторных таблиц (LDT), из которых в один момент времени процессору доступна только одна.

Слайд 4Расположение дескрипторных таблиц определяется регистрами процессора:

GDTR (Global Descriptor Table Register),

IDTR (Interrupt Descriptor

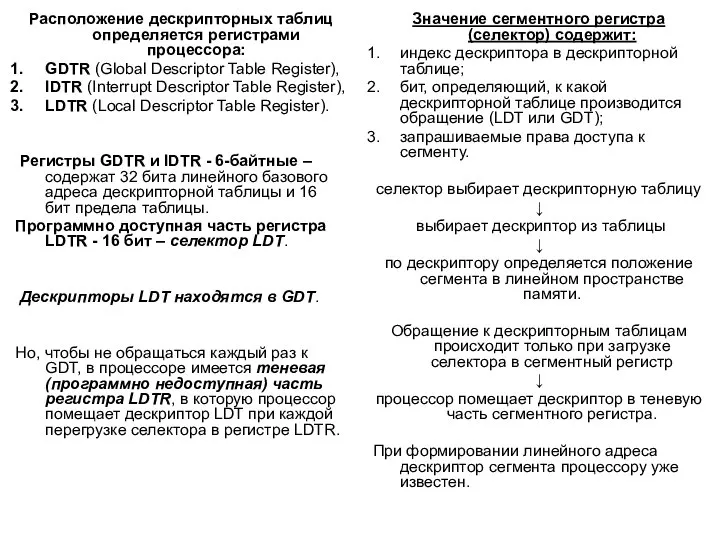

Расположение дескрипторных таблиц определяется регистрами процессора:

GDTR (Global Descriptor Table Register),

IDTR (Interrupt Descriptor

LDTR (Local Descriptor Table Register).

Регистры GDTR и IDTR - 6-байтные – содержат 32 бита линейного базового адреса дескрипторной таблицы и 16 бит предела таблицы.

Программно доступная часть регистра LDTR - 16 бит – селектор LDT.

Дескрипторы LDT находятся в GDT.

Но, чтобы не обращаться каждый раз к GDT, в процессоре имеется теневая (программно недоступная) часть регистра LDTR, в которую процессор помещает дескриптор LDT при каждой перегрузке селектора в регистре LDTR.

Значение сегментного регистра (селектор) содержит:

индекс дескриптора в дескрипторной таблице;

бит, определяющий, к какой дескрипторной таблице производится обращение (LDT или GDT);

запрашиваемые права доступа к сегменту.

селектор выбирает дескрипторную таблицу

↓

выбирает дескриптор из таблицы

↓

по дескриптору определяется положение сегмента в линейном пространстве памяти.

Обращение к дескрипторным таблицам происходит только при загрузке селектора в сегментный регистр

↓

процессор помещает дескриптор в теневую часть сегментного регистра.

При формировании линейного адреса дескриптор сегмента процессору уже известен.

Слайд 5Сегментная адресация в защищенном режиме

Сегментная адресация в защищенном режиме

Контроллер «АКД-СК»

Контроллер «АКД-СК» III Красноярский экономический форум «Развитие востока страны»Круглый «Региональная политика России и региональные стратегии к

III Красноярский экономический форум «Развитие востока страны»Круглый «Региональная политика России и региональные стратегии к Государственный санитарно-эпидемиологический надзор в области гигиены питания

Государственный санитарно-эпидемиологический надзор в области гигиены питания Модель проектно-ориентированной системы управления

Модель проектно-ориентированной системы управления Совершенствование правового положения государственных и муниципальных учреждений: организационные, финансовые, правовые аспект

Совершенствование правового положения государственных и муниципальных учреждений: организационные, финансовые, правовые аспект Курская антоновка – символ Курской области

Курская антоновка – символ Курской области Памятка о ложных вызовах об актах терроризма

Памятка о ложных вызовах об актах терроризма Изделия из слоеного теста

Изделия из слоеного теста Презентация на тему Верблюд

Презентация на тему Верблюд  Мой народ – американцы

Мой народ – американцы Презентация на тему Сергей Есенин Юность

Презентация на тему Сергей Есенин Юность  Информационные технологии в жилищно-коммунальном хозяйстве Финляндии

Информационные технологии в жилищно-коммунальном хозяйстве Финляндии Презентация на тему готовимся к ГИА, В3, В6

Презентация на тему готовимся к ГИА, В3, В6  Жанр портрета в культуре разных времён

Жанр портрета в культуре разных времён История аниме

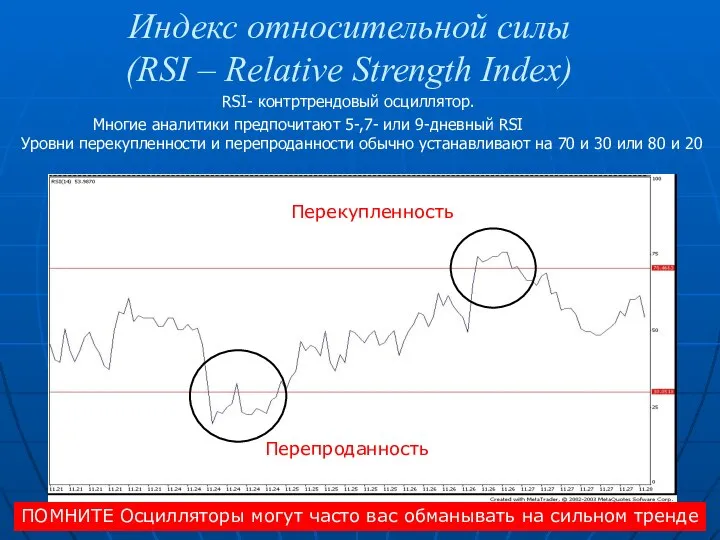

История аниме Индекс относительной силы

Индекс относительной силы Неживая и живая природа

Неживая и живая природа Реакторы, охлаждаемые водой сверхкритического давления при двухходовой схеме движения теплоносителя Ю.Д. Баранаев, А.П. Глебов, А.В

Реакторы, охлаждаемые водой сверхкритического давления при двухходовой схеме движения теплоносителя Ю.Д. Баранаев, А.П. Глебов, А.В speaking_club_yesno (2)

speaking_club_yesno (2) Мастер-класс Скрап-страницы моего лета

Мастер-класс Скрап-страницы моего лета Айларов Сослан Русланович

Айларов Сослан Русланович Елочные шарики из бумаги в технике квиллинг

Елочные шарики из бумаги в технике квиллинг Инновационная система и политика в РФ

Инновационная система и политика в РФ Семейный бюджет. Доходная и расходная части бюджета.

Семейный бюджет. Доходная и расходная части бюджета. Бухгалтерский учет, анализ и аудит

Бухгалтерский учет, анализ и аудит Праздник 1 мая

Праздник 1 мая мониторинг цен

мониторинг цен Анализ рынка детского питания на территории города Казани в одной из ключевых национальных сетей Пятерочка

Анализ рынка детского питания на территории города Казани в одной из ключевых национальных сетей Пятерочка