Содержание

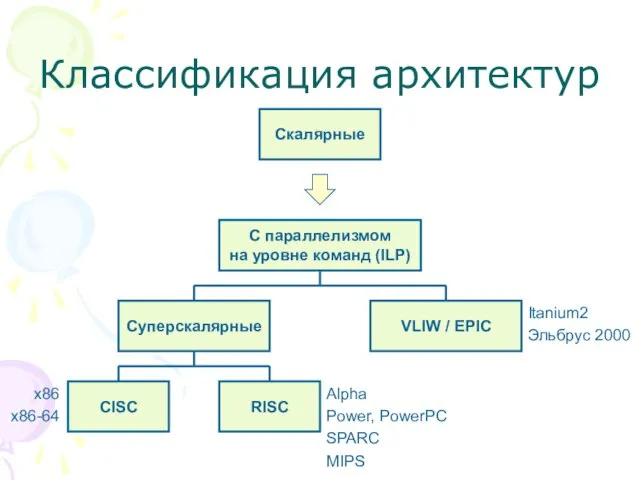

- 2. Классификация архитектур Скалярные С параллелизмом на уровне команд (ILP) Суперскалярные VLIW / EPIC RISC CISC Itanium2

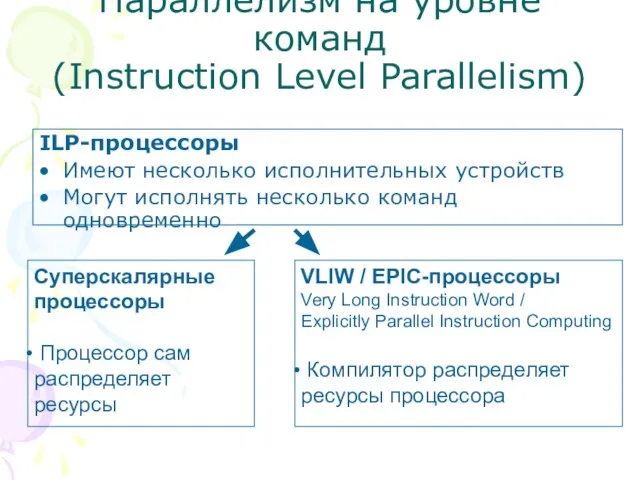

- 3. Параллелизм на уровне команд (Instruction Level Parallelism) ILP-процессоры Имеют несколько исполнительных устройств Могут исполнять несколько команд

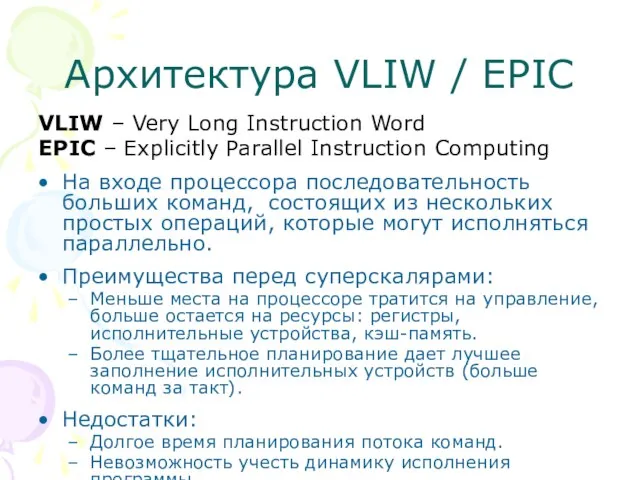

- 4. Архитектура VLIW / EPIC VLIW – Very Long Instruction Word EPIC – Explicitly Parallel Instruction Computing

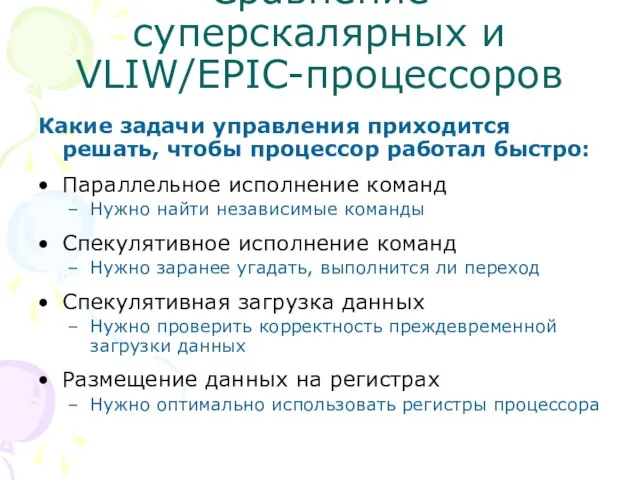

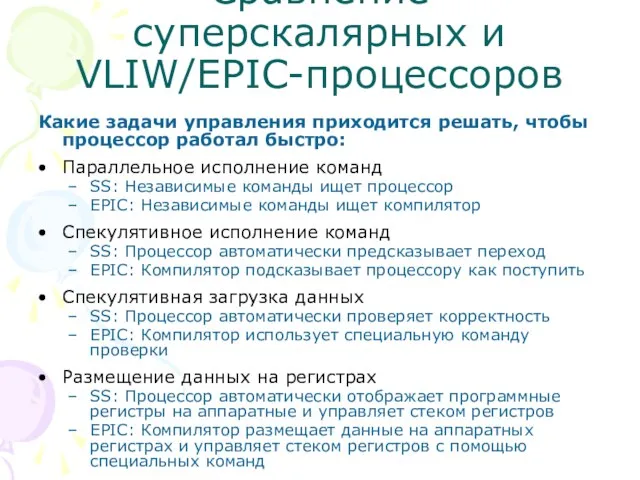

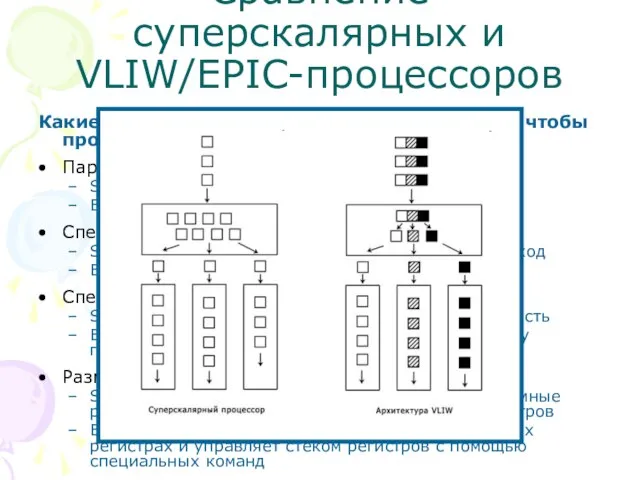

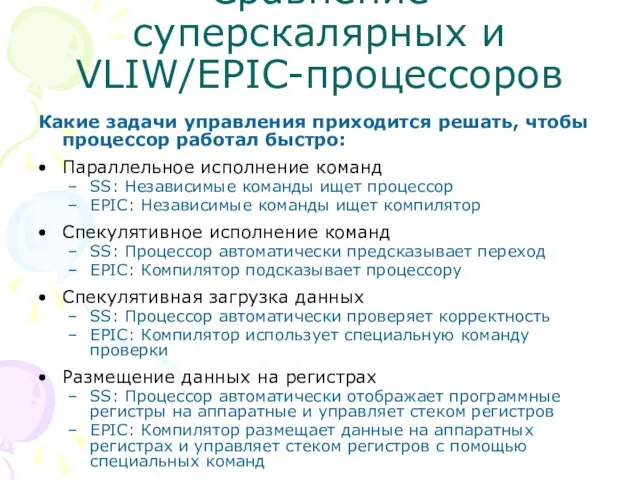

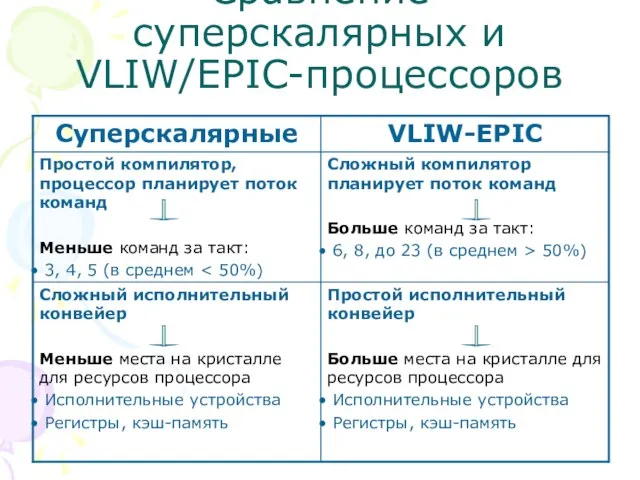

- 5. Сравнение суперскалярных и VLIW/EPIC-процессоров Какие задачи управления приходится решать, чтобы процессор работал быстро: Параллельное исполнение команд

- 6. Сравнение суперскалярных и VLIW/EPIC-процессоров Какие задачи управления приходится решать, чтобы процессор работал быстро: Параллельное исполнение команд

- 7. Сравнение суперскалярных и VLIW/EPIC-процессоров Какие задачи управления приходится решать, чтобы процессор работал быстро: Параллельное исполнение команд

- 8. Сравнение суперскалярных и VLIW/EPIC-процессоров Какие задачи управления приходится решать, чтобы процессор работал быстро: Параллельное исполнение команд

- 9. Сравнение суперскалярных и VLIW/EPIC-процессоров

- 10. Предсказание ветвлений Выборка Декодирование в RISC Переименование регистров Переупорядочение и распараллеливание Исполнение Завершение CISC RISC VLIW

- 11. Архитектура VLIW / EPIC История M-10 (1972) Cydrome (1984-1988) Cydra-5 256 bit VLIW (7 ops.), reg.

- 12. Архитектура Itanium

- 13. Семейство процессоров Itanium 2001 2002 2003 2006 Itanium (Merced) 800 MHz 4 MB L3 cache 180

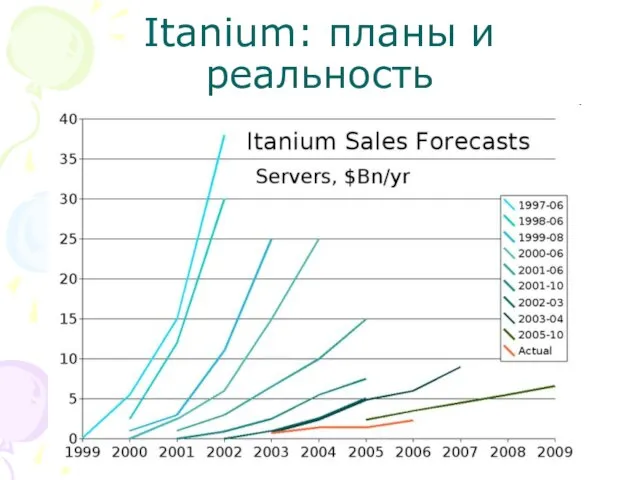

- 14. Itanium: планы и реальность

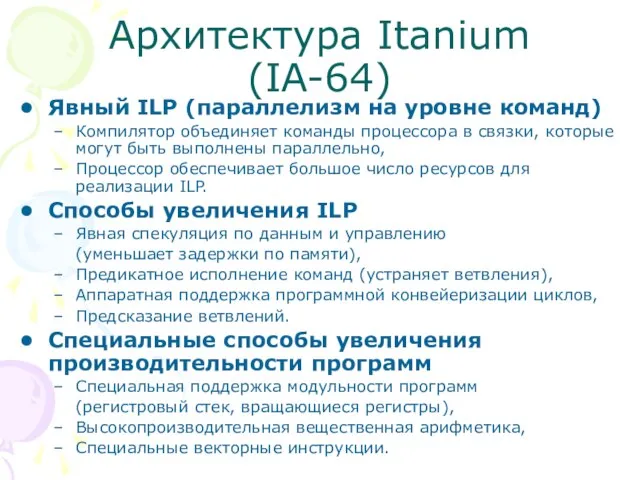

- 15. Архитектура Itanium (IA-64) Явный ILP (параллелизм на уровне команд) Компилятор объединяет команды процессора в связки, которые

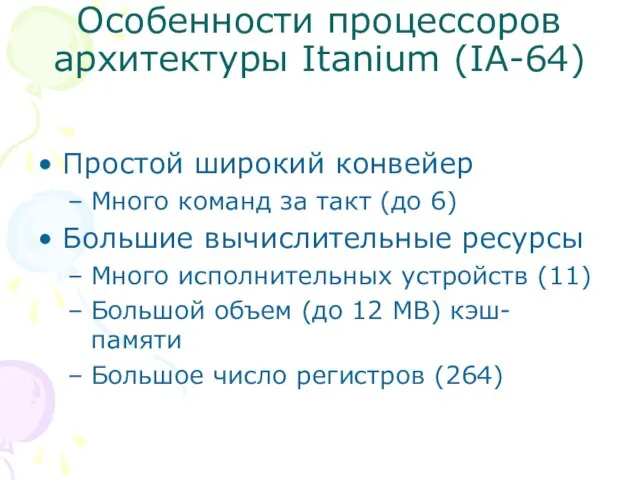

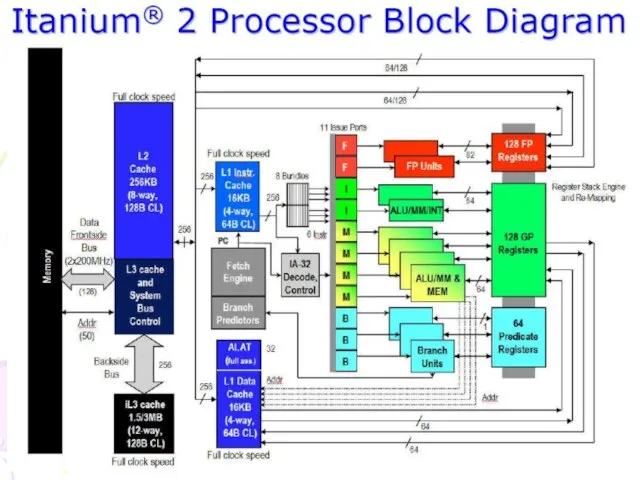

- 16. Особенности процессоров архитектуры Itanium (IA-64) Простой широкий конвейер Много команд за такт (до 6) Большие вычислительные

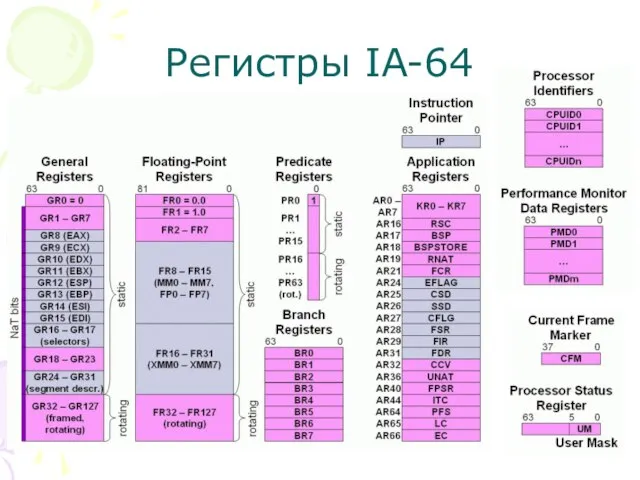

- 18. Регистры IA-64

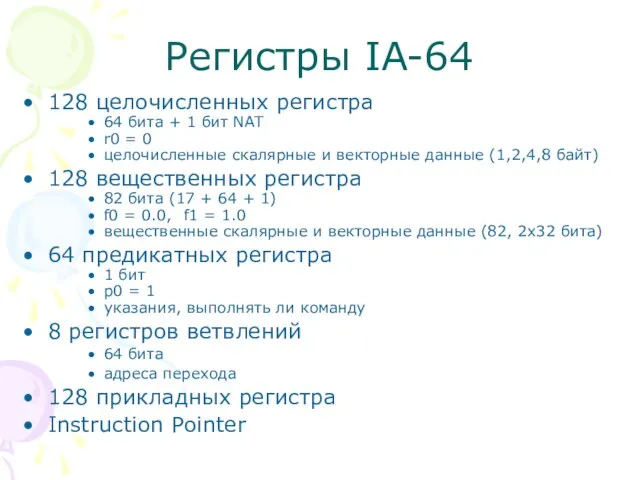

- 19. Регистры IA-64 128 целочисленных регистра 64 бита + 1 бит NAT r0 = 0 целочисленные скалярные

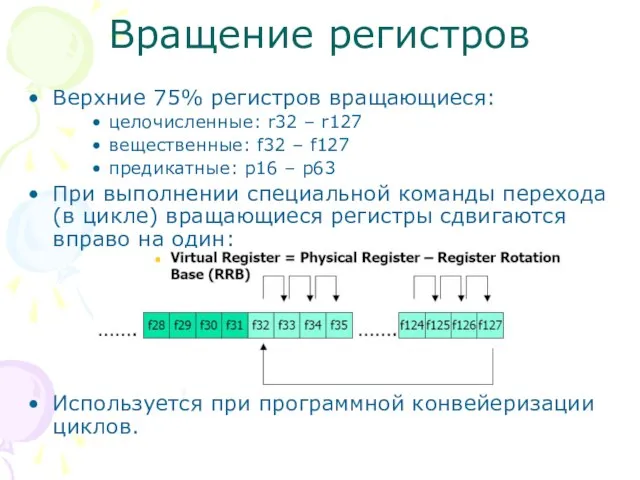

- 20. Вращение регистров Верхние 75% регистров вращающиеся: целочисленные: r32 – r127 вещественные: f32 – f127 предикатные: p16

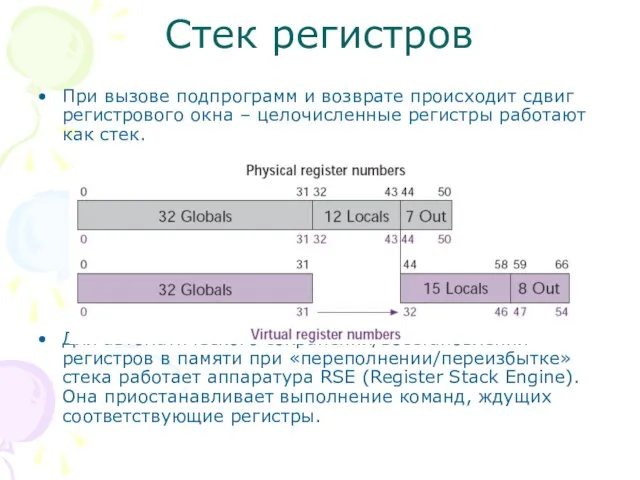

- 21. Стек регистров При вызове подпрограмм и возврате происходит сдвиг регистрового окна – целочисленные регистры работают как

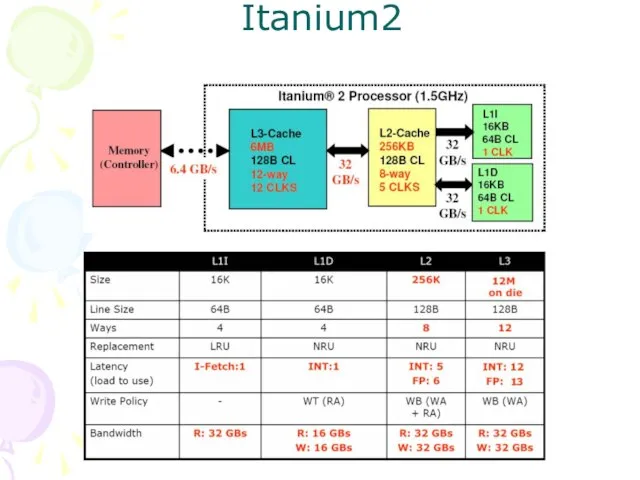

- 22. Иерархия кэш-памяти Itanium2

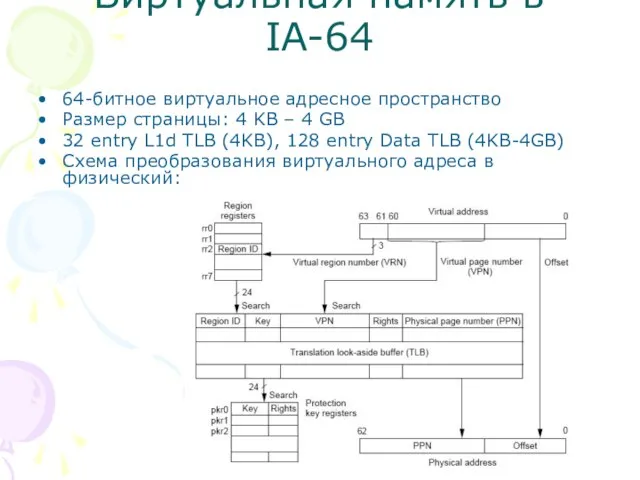

- 23. Виртуальная память в IA-64 64-битное виртуальное адресное пространство Размер страницы: 4 KB – 4 GB 32

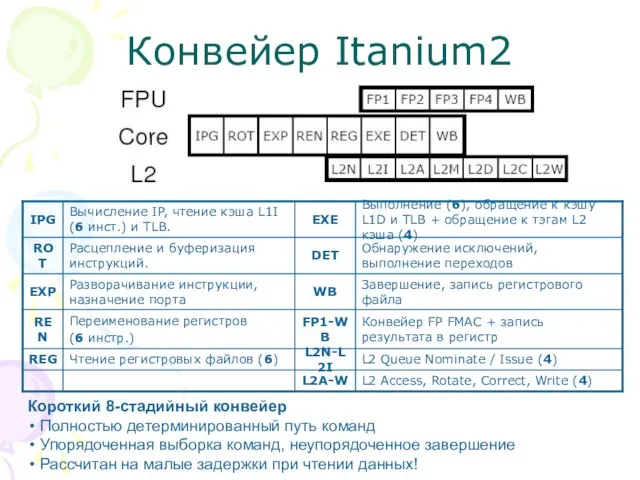

- 24. Конвейер Itanium2 Короткий 8-стадийный конвейер Полностью детерминированный путь команд Упорядоченная выборка команд, неупорядоченное завершение Рассчитан на

- 25. Исполнительные устройства Число операций за такт

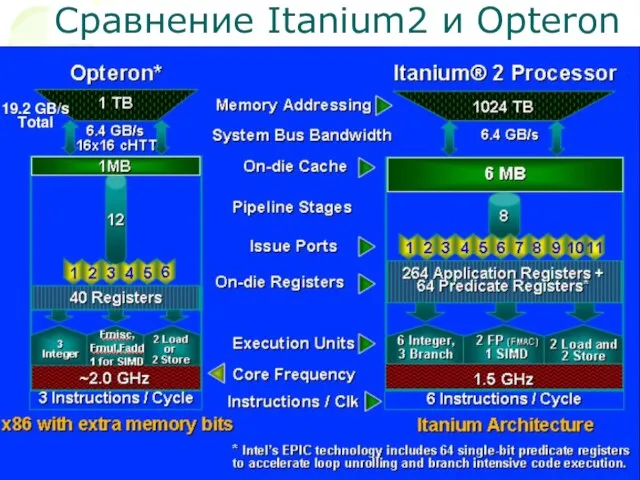

- 26. Сравнение Itanium2 и Opteron

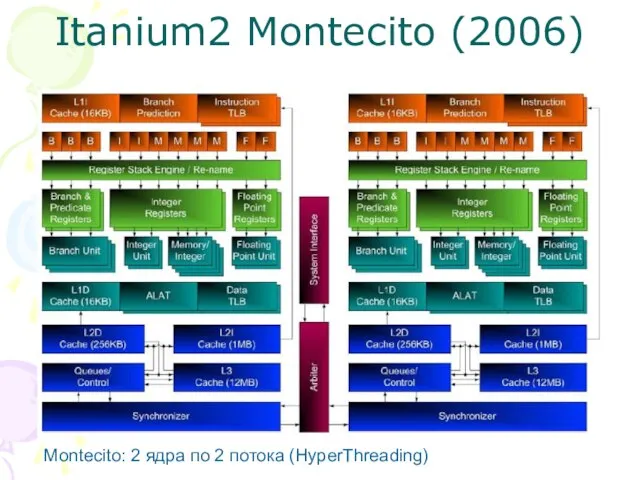

- 27. Itanium2 Montecito (2006) Montecito: 2 ядра по 2 потока (HyperThreading)

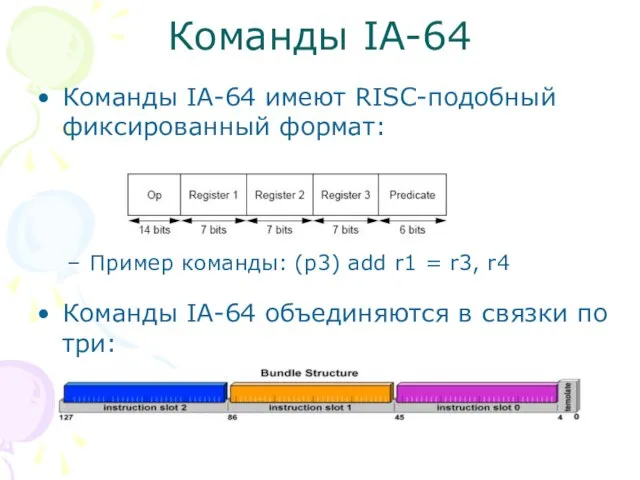

- 28. Команды IA-64 Команды IA-64 имеют RISC-подобный фиксированный формат: Пример команды: (p3) add r1 = r3, r4

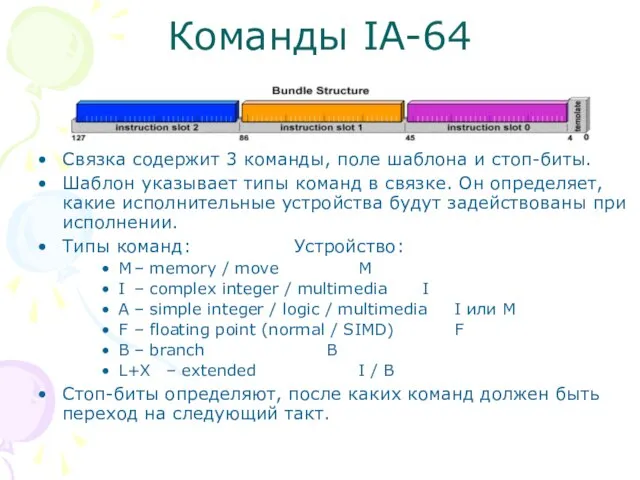

- 29. Команды IA-64 Связка содержит 3 команды, поле шаблона и стоп-биты. Шаблон указывает типы команд в связке.

- 30. Команды IA-64 Всего возможно 24 различных шаблона: Процессор загружает максимум по 2 связки за такт. Только

- 31. Команды IA-64 Логические (and, …) Арифметические (add, …) Команды сравнения (cmp, …) Команды сдвига (shl, …)

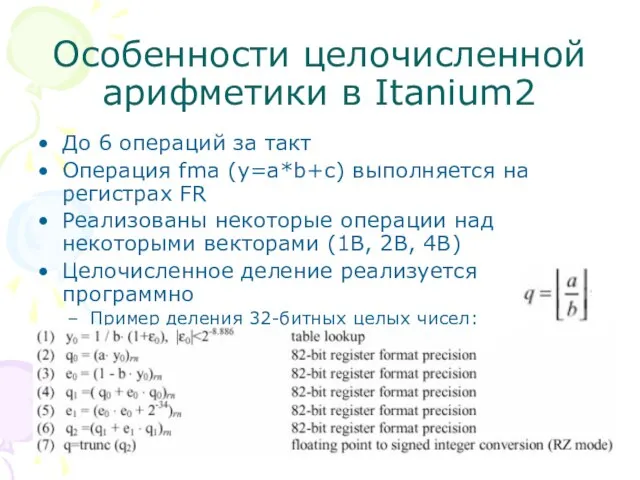

- 32. Особенности целочисленной арифметики в Itanium2 До 6 операций за такт Операция fma (y=a*b+c) выполняется на регистрах

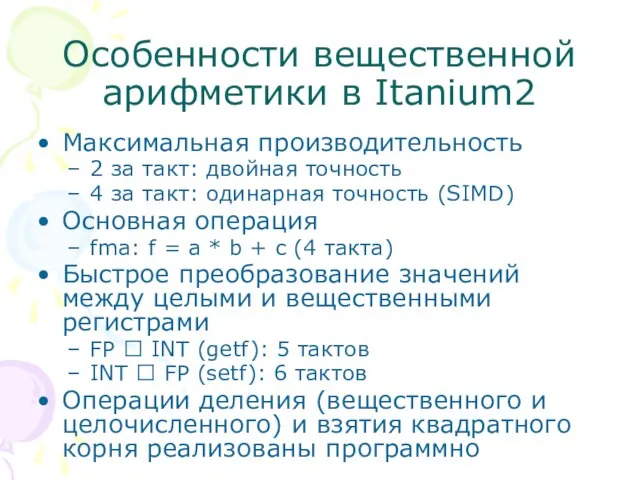

- 33. Особенности вещественной арифметики в Itanium2 Максимальная производительность 2 за такт: двойная точность 4 за такт: одинарная

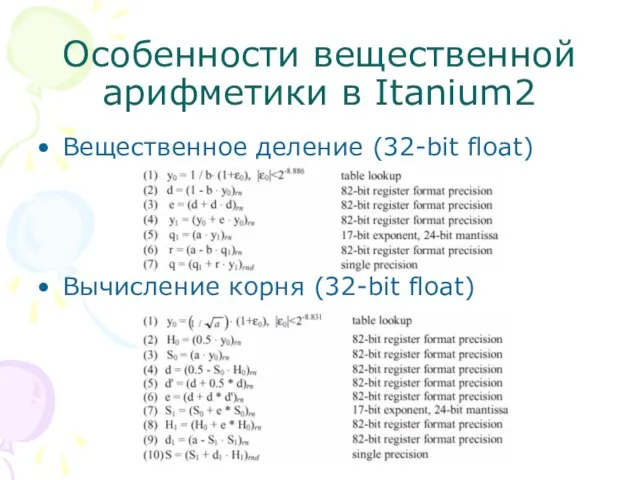

- 34. Особенности вещественной арифметики в Itanium2 Вещественное деление (32-bit float) Вычисление корня (32-bit float)

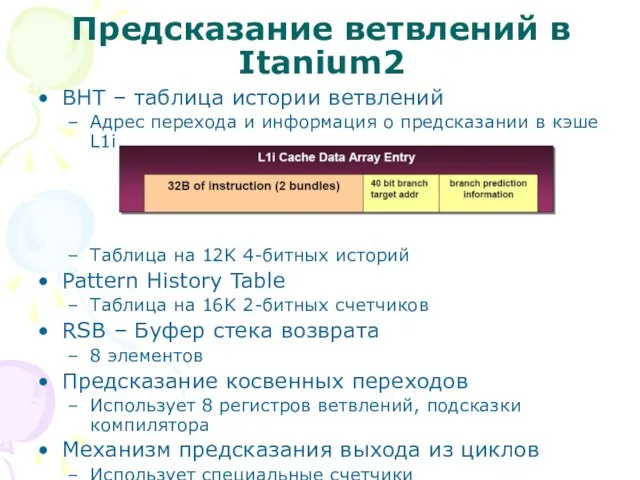

- 35. Предсказание ветвлений в Itanium2 BHT – таблица истории ветвлений Адрес перехода и информация о предсказании в

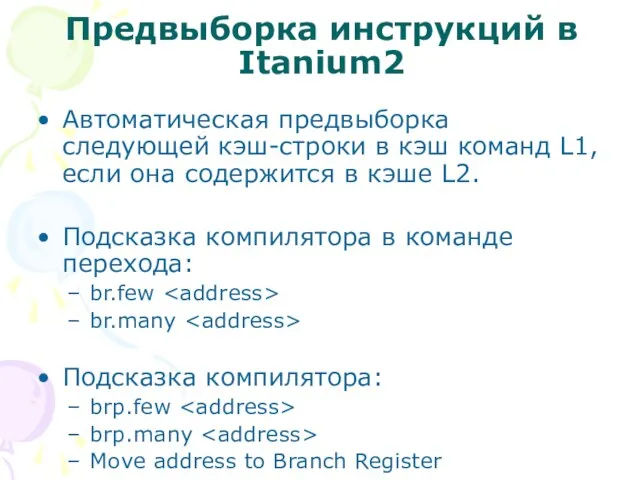

- 36. Предвыборка инструкций в Itanium2 Автоматическая предвыборка следующей кэш-строки в кэш команд L1, если она содержится в

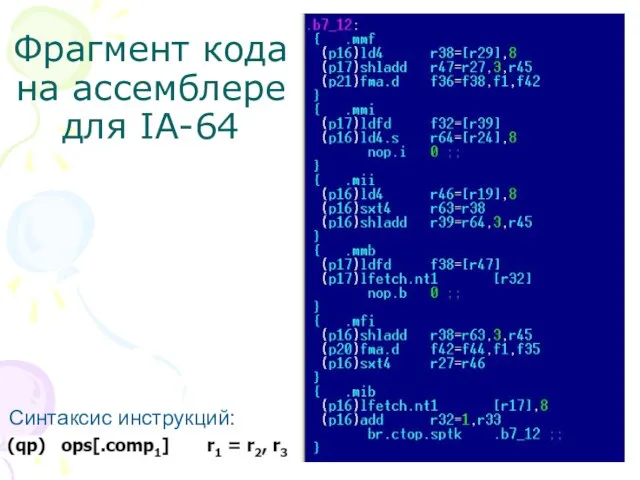

- 37. Фрагмент кода на ассемблере для IA-64 Синтаксис инструкций:

- 38. Средства повышения производительности в IA-64 Предикатное исполнение команд Аппаратные счетчики циклов Спекуляция по данным и управлению

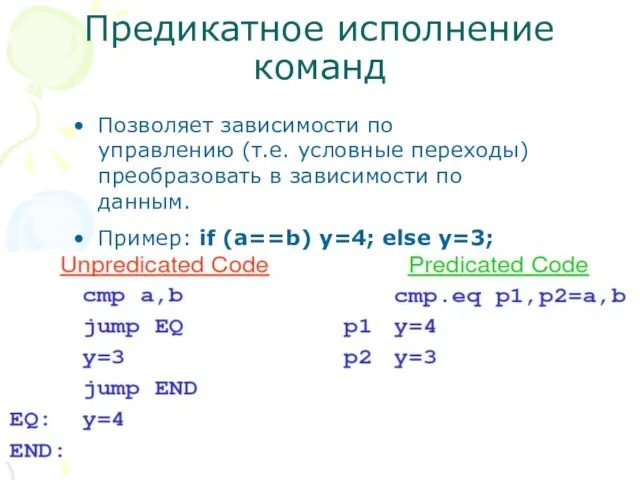

- 39. Предикатное исполнение команд Позволяет зависимости по управлению (т.е. условные переходы) преобразовать в зависимости по данным. Пример:

- 40. Аппаратные счетчики циклов Архитектурная поддержка циклов По специальной команде перехода счетчики автоматически уменьшаются и делается проверка

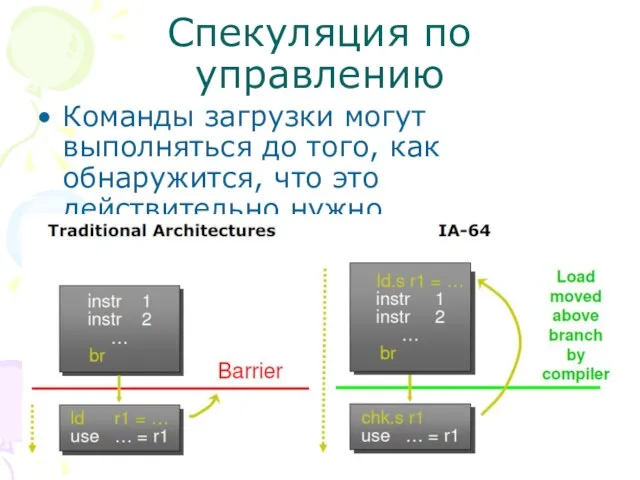

- 41. Спекуляция по управлению Команды загрузки могут выполняться до того, как обнаружится, что это действительно нужно.

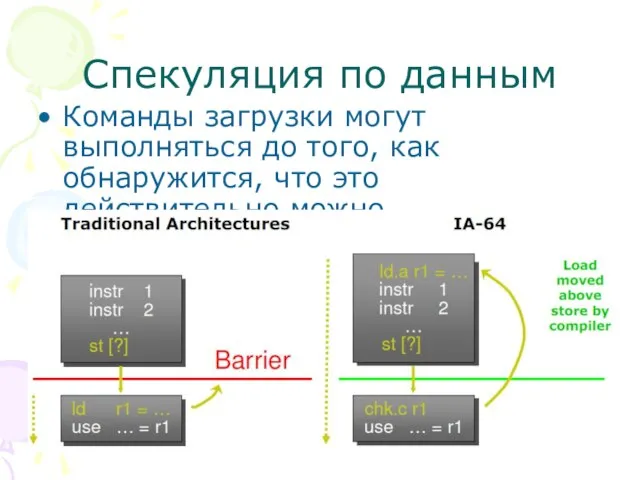

- 42. Спекуляция по данным Команды загрузки могут выполняться до того, как обнаружится, что это действительно можно.

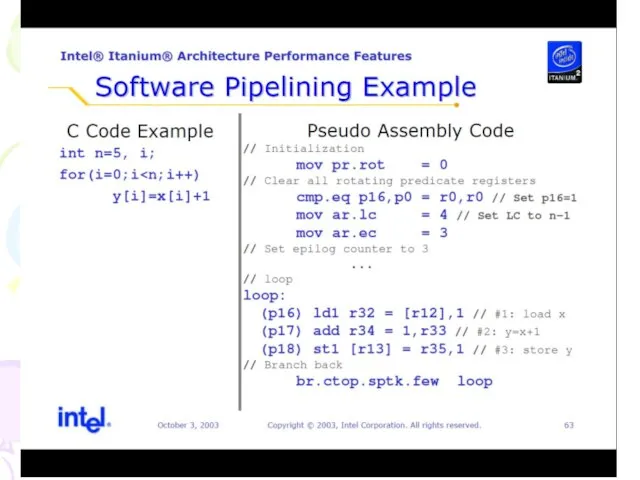

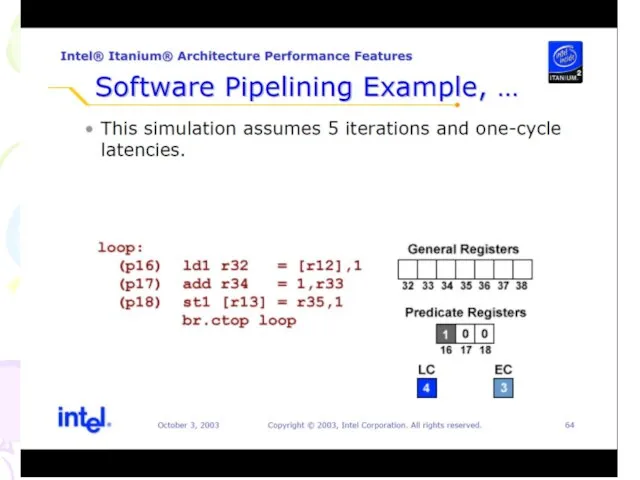

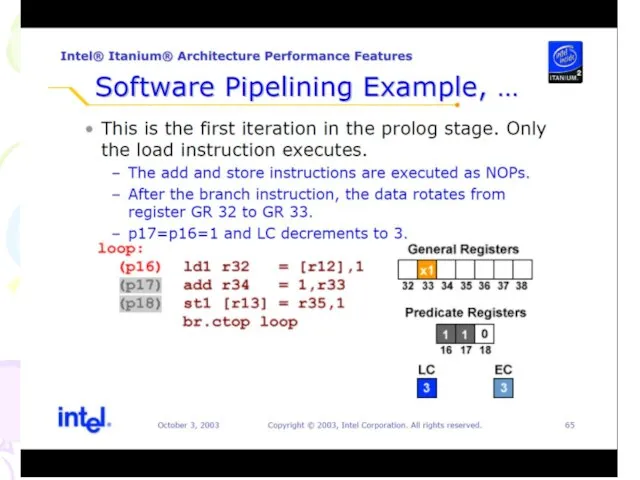

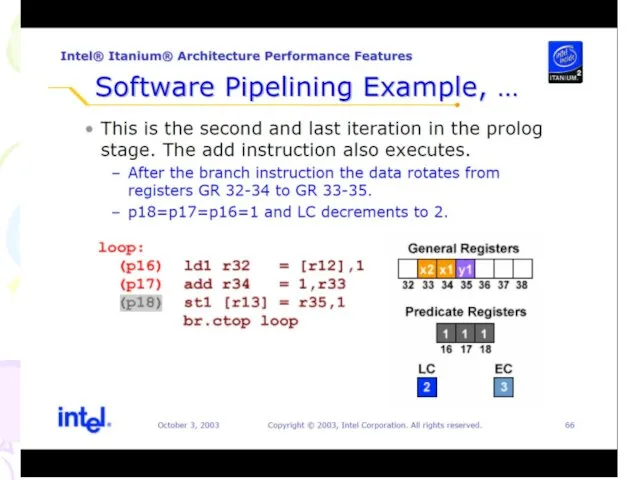

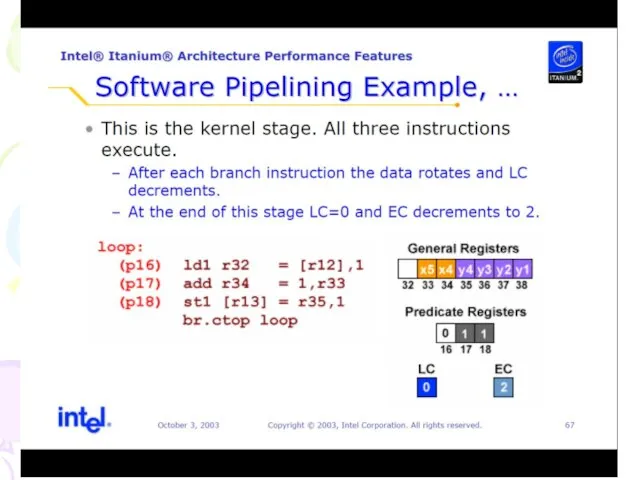

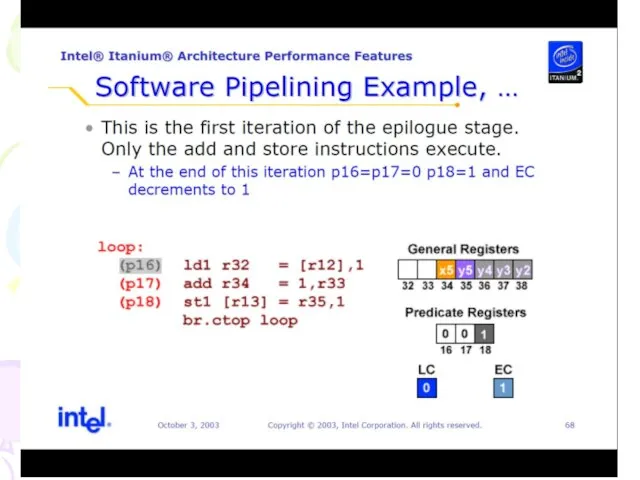

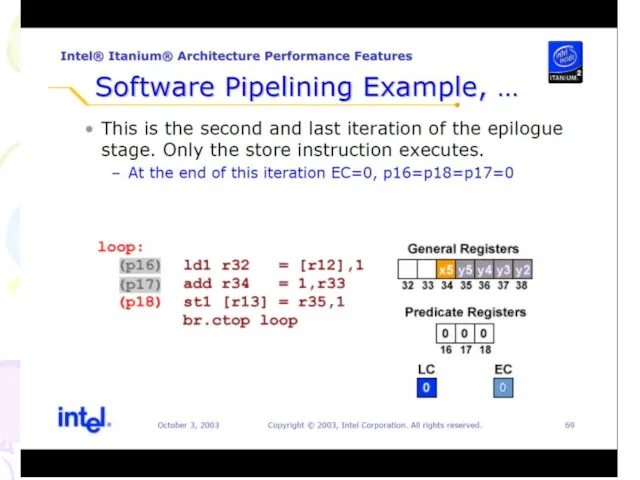

- 43. Программная конвейеризация цикла Архитектурная поддержка параллельного исполнения команд цикла. Выполняется с помощью: Предикатных регистров Аппаратных счетчиков

- 51. Процессоры Itanium 9300 (Tukwila) Особенности нового Itanium-а Частота: до 1.73 GHz Режим Turbo boost: до 1.86

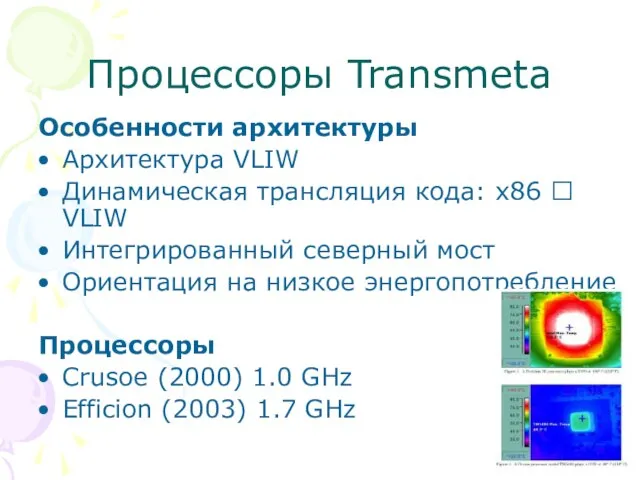

- 52. Процессоры Transmeta

- 53. Процессоры Transmeta Особенности архитектуры Архитектура VLIW Динамическая трансляция кода: x86 ? VLIW Интегрированный северный мост Ориентация

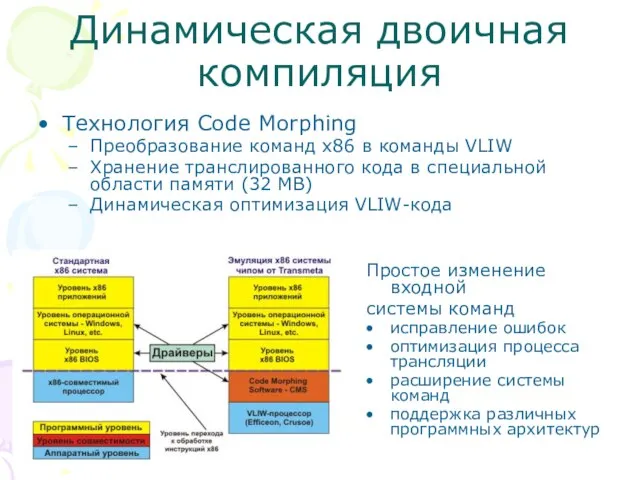

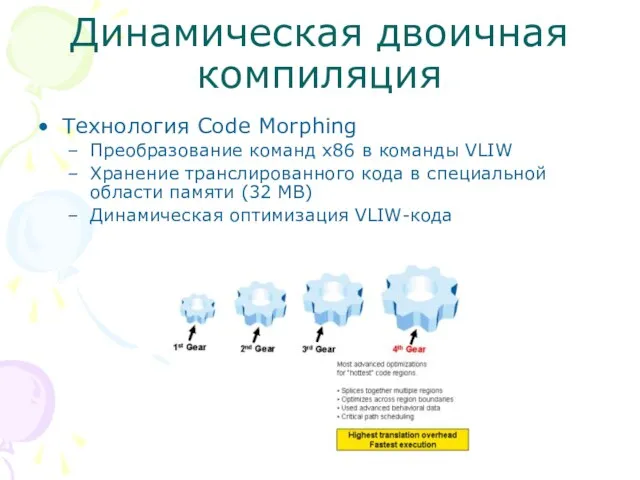

- 54. Динамическая двоичная компиляция Технология Code Morphing Преобразование команд x86 в команды VLIW Хранение транслированного кода в

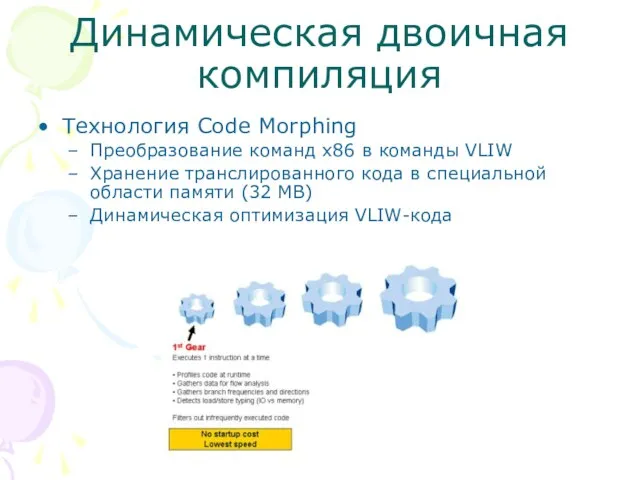

- 55. Динамическая двоичная компиляция Технология Code Morphing Преобразование команд x86 в команды VLIW Хранение транслированного кода в

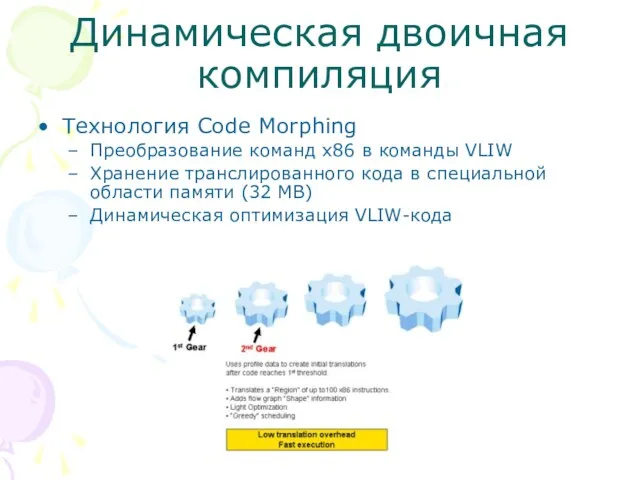

- 56. Динамическая двоичная компиляция Технология Code Morphing Преобразование команд x86 в команды VLIW Хранение транслированного кода в

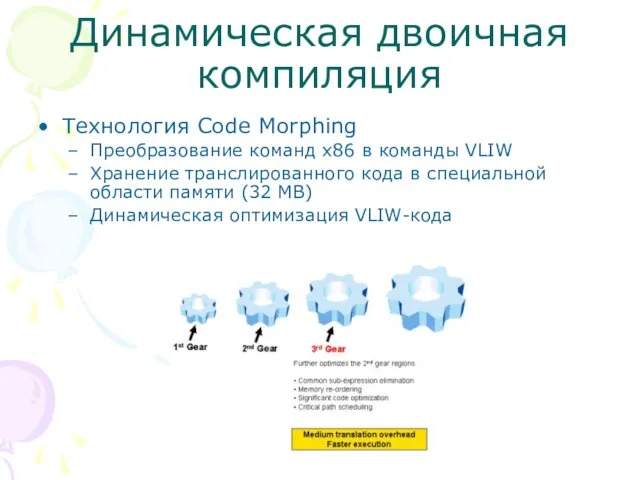

- 57. Динамическая двоичная компиляция Технология Code Morphing Преобразование команд x86 в команды VLIW Хранение транслированного кода в

- 58. Динамическая двоичная компиляция Технология Code Morphing Преобразование команд x86 в команды VLIW Хранение транслированного кода в

- 59. Динамическая двоичная компиляция Технология Code Morphing Преобразование команд x86 в команды VLIW Хранение транслированного кода в

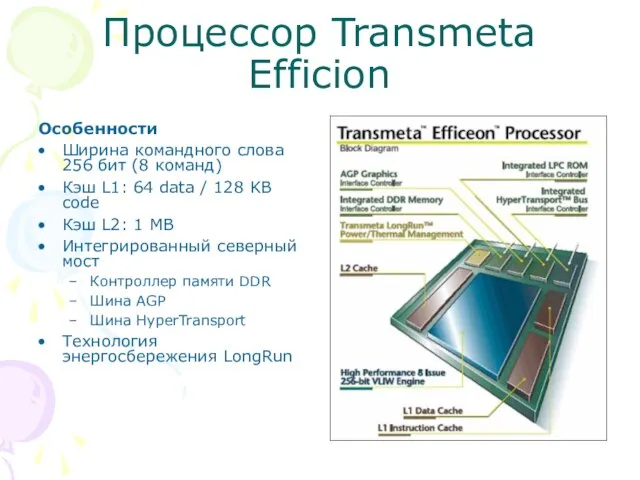

- 60. Процессор Transmeta Efficion Особенности Ширина командного слова 256 бит (8 команд) Кэш L1: 64 data /

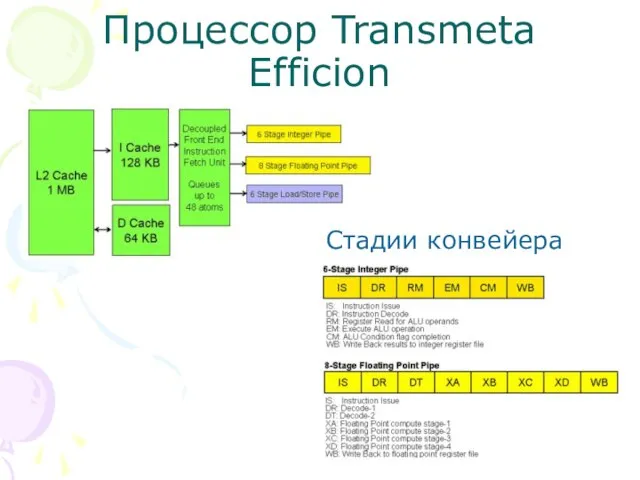

- 61. Процессор Transmeta Efficion Стадии конвейера

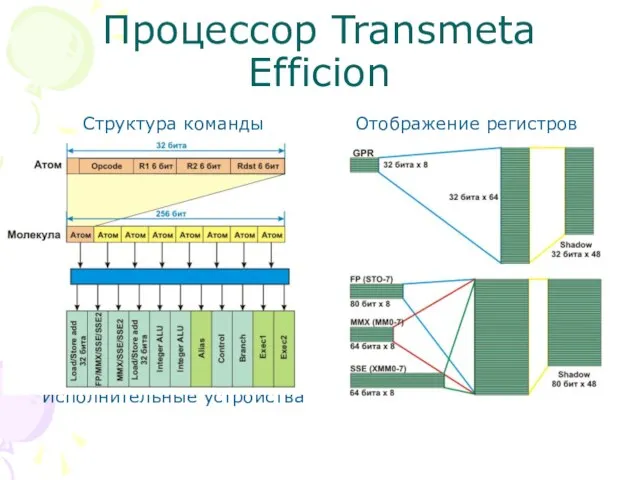

- 62. Процессор Transmeta Efficion Структура команды Исполнительные устройства Отображение регистров

- 63. Архитектура Эльбрус 2000 Бабаян Борис Арташесович чл.корр. РАН Intel Fellow

- 64. Эльбрус 2000 ELBRUS – ExpLicit Basic Resources Utilization Scheduling (явное планирование использования основных ресурсов) Особенности архитектуры

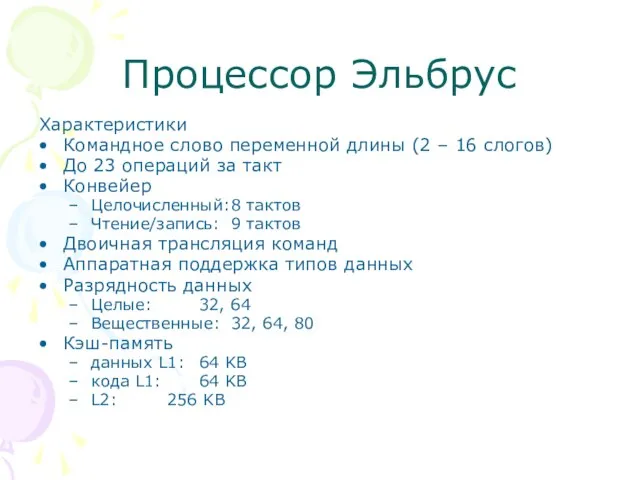

- 65. Процессор Эльбрус Характеристики Командное слово переменной длины (2 – 16 слогов) До 23 операций за такт

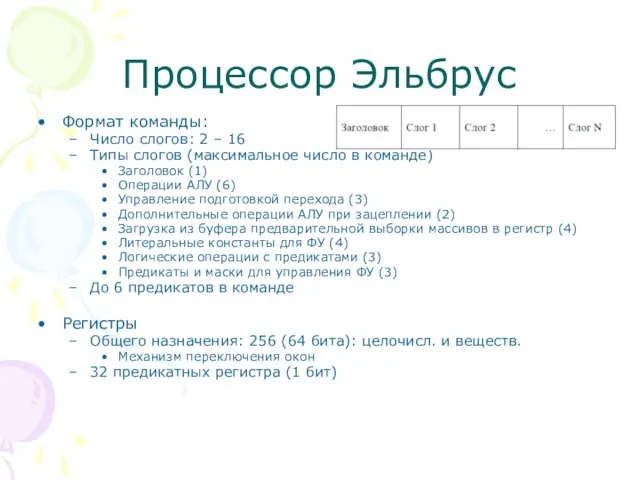

- 66. Процессор Эльбрус Формат команды: Число слогов: 2 – 16 Типы слогов (максимальное число в команде) Заголовок

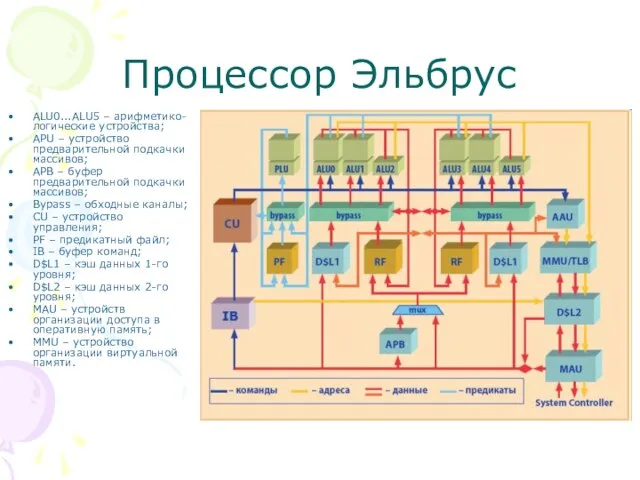

- 67. Процессор Эльбрус ALU0...ALU5 – арифметико-логические устройства; APU – устройство предварительной подкачки массивов; APB – буфер предварительной

- 68. Процессор Эльбрус Динамическая трансляция кода

- 70. Скачать презентацию

Социальный Форум России и Фестиваль «СоДействие» - всероссийские площадки общественно-государственного диалога

Социальный Форум России и Фестиваль «СоДействие» - всероссийские площадки общественно-государственного диалога Шаблон проекта

Шаблон проекта Викторина. Битва полов

Викторина. Битва полов Россия – многонациональная страна

Россия – многонациональная страна Искусство доколумбовой Америки

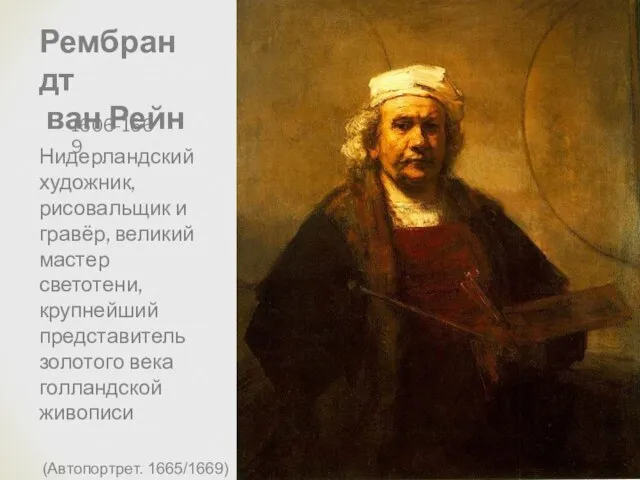

Искусство доколумбовой Америки Рембрандт ван Рейн 1606-1669

Рембрандт ван Рейн 1606-1669 Правила поведения для детей

Правила поведения для детей Teradata

Teradata 990 Рижский ночной ближний бомбардировочный авиаполк

990 Рижский ночной ближний бомбардировочный авиаполк Административная ответственность

Административная ответственность Товары для отопления

Товары для отопления Использование технологии критического мышления на уроках русского языка и литературы (из опыта работы учителя гимназии № 505 Кол

Использование технологии критического мышления на уроках русского языка и литературы (из опыта работы учителя гимназии № 505 Кол Презентация на тему Устный счёт

Презентация на тему Устный счёт  Действия с целыми числами

Действия с целыми числами Факультет фундаментальной и прикладной химии

Факультет фундаментальной и прикладной химии Будет в доме Домовой

Будет в доме Домовой Львова С.И., Львов В.В.

Львова С.И., Львов В.В. Операционная система

Операционная система История аниме

История аниме Презентация на тему Ситуация успеха на уроках математики как средство повышения качества образования

Презентация на тему Ситуация успеха на уроках математики как средство повышения качества образования  бжд Вагизова стресс и его профилактика

бжд Вагизова стресс и его профилактика Факультет готовит: специалистов с квалификацией «Учитель математики и информатики» для общеобразовательных школ, лицеев, колледж

Факультет готовит: специалистов с квалификацией «Учитель математики и информатики» для общеобразовательных школ, лицеев, колледж Презентация на тему Черные дыры

Презентация на тему Черные дыры Плавление

Плавление Разработка реконфигурируемого устройства на ПЛИС

Разработка реконфигурируемого устройства на ПЛИС СИСТЕМЫ ВОДЯНОГО ОТОПЛЕНИЯ

СИСТЕМЫ ВОДЯНОГО ОТОПЛЕНИЯ Правила ухода за новорожденным

Правила ухода за новорожденным Музыкальная культура

Музыкальная культура