Слайд 2Два класса

Суперскалярные процессоры

Процессоры с длинным командным словом

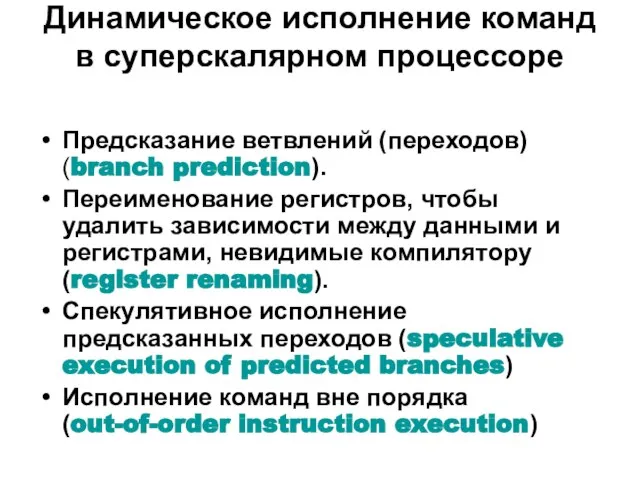

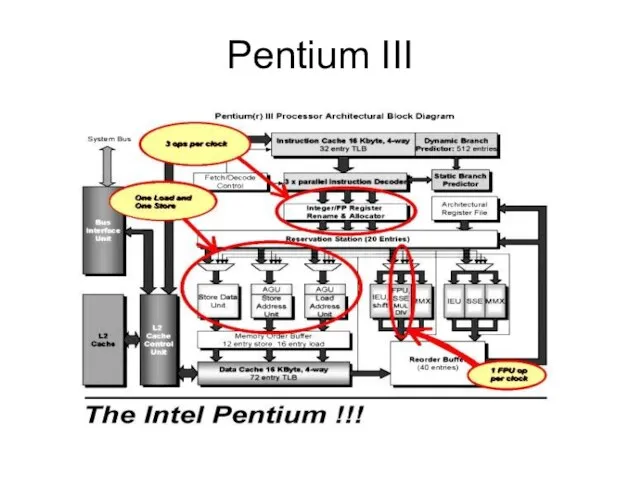

Слайд 4Динамическое исполнение команд в суперскалярном процессоре

Предсказание ветвлений (переходов) (branch prediction).

Переименование регистров, чтобы

удалить зависимости между данными и регистрами, невидимые компилятору (register renaming).

Спекулятивное исполнение предсказанных переходов (speculative execution of predicted branches)

Исполнение команд вне порядка (out-of-order instruction execution)

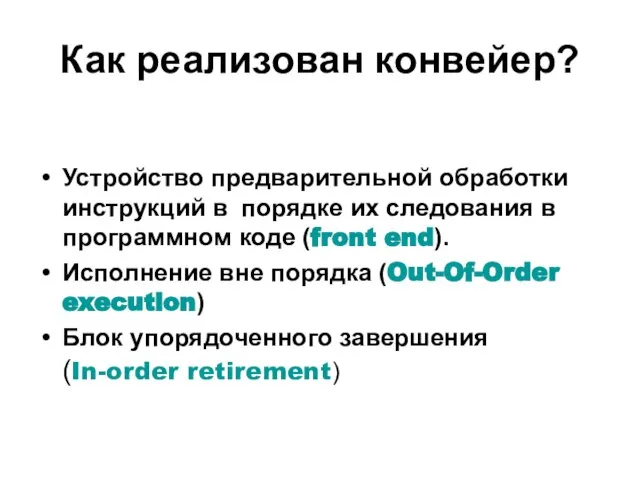

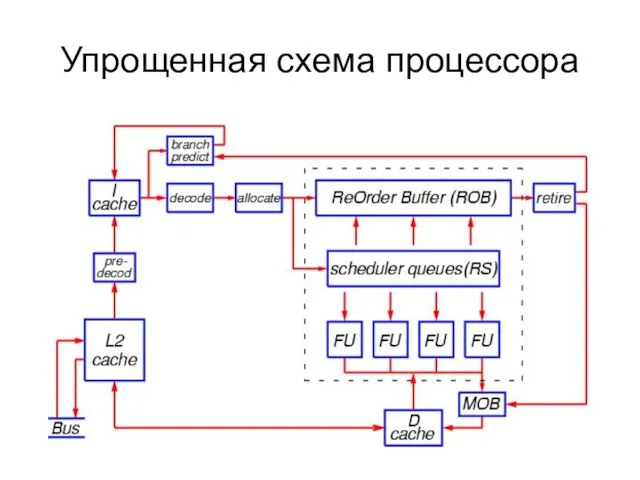

Слайд 5Как реализован конвейер?

Устройство предварительной обработки инструкций в порядке их следования в программном

коде (front end).

Исполнение вне порядка (Out-Of-Order execution)

Блок упорядоченного завершения (In-order retirement)

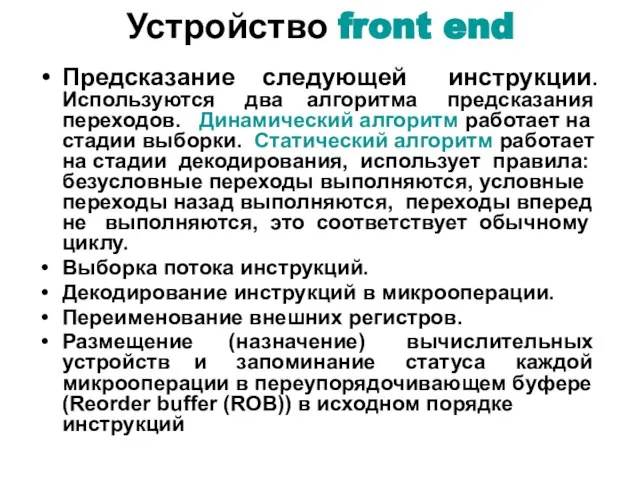

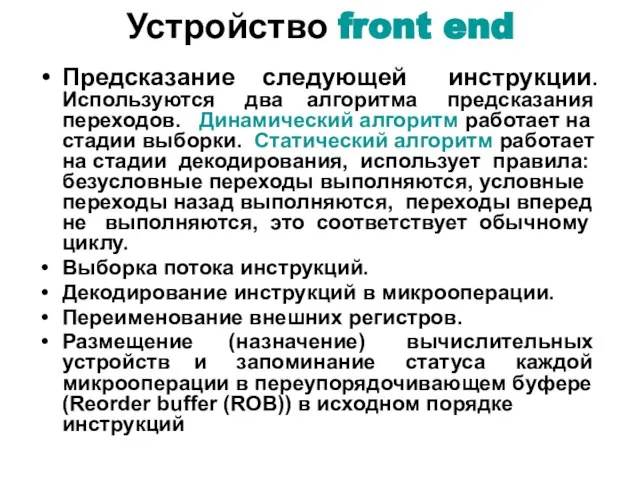

Слайд 6Устройство front end

Предсказание следующей инструкции. Используются два алгоритма предсказания переходов. Динамический

алгоритм работает на стадии выборки. Статический алгоритм работает на стадии декодирования, использует правила: безусловные переходы выполняются, условные переходы назад выполняются, переходы вперед не выполняются, это соответствует обычному циклу.

Выборка потока инструкций.

Декодирование инструкций в микрооперации.

Переименование внешних регистров.

Размещение (назначение) вычислительных устройств и запоминание статуса каждой микрооперации в переупорядочивающем буфере (Reorder buffer (ROB)) в исходном порядке инструкций

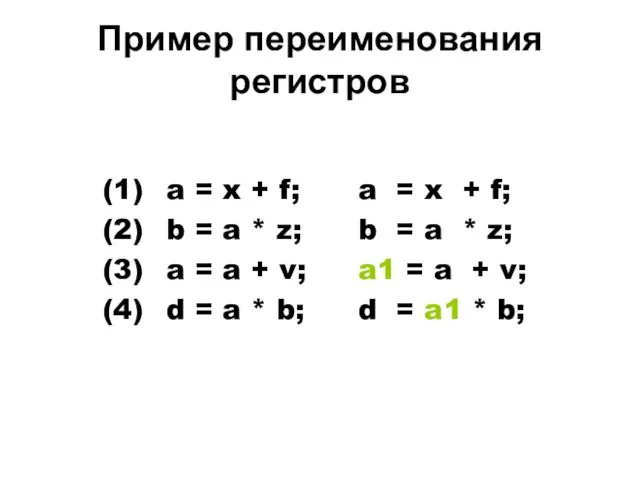

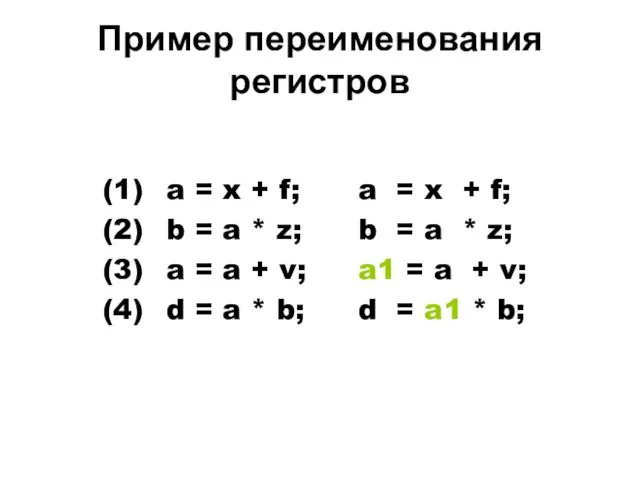

Слайд 7Пример переименования регистров

(1) a = x + f; a = x + f;

(2) b =

a * z; b = a * z;

(3) a = a + v; a1 = a + v;

(4) d = a * b; d = a1 * b;

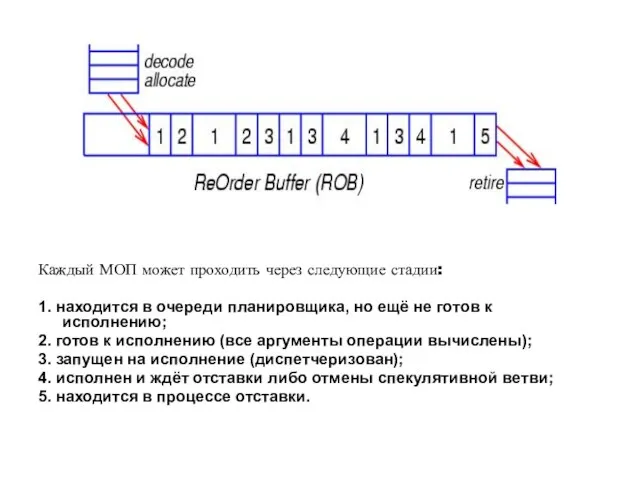

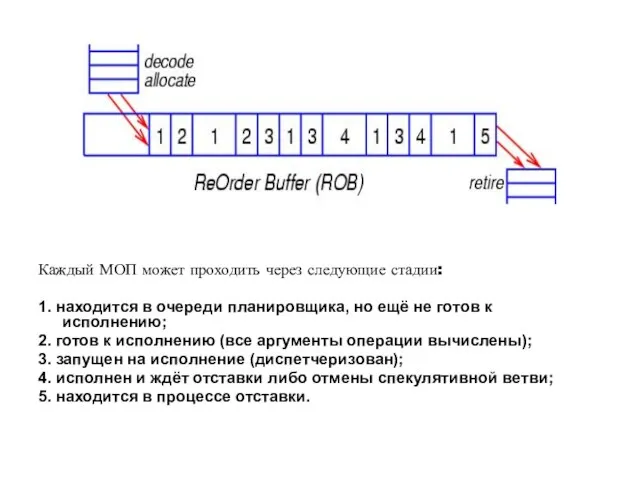

Слайд 8Каждый МОП может проходить через следующие стадии:

1. находится в очереди планировщика, но

ещё не готов к исполнению;

2. готов к исполнению (все аргументы операции вычислены);

3. запущен на исполнение (диспетчеризован);

4. исполнен и ждёт отставки либо отмены спекулятивной ветви;

5. находится в процессе отставки.

Слайд 9Устройство Out-Of-Order execution

Планирование и распределение микроопераций

Выполнение микроопераций и запоминание их результатов

временно в буфере ROB.

Слайд 10Блок упорядоченного завершения

Запись результатов обратно во внешние архитектурные регистры, постоянная запись

данных, если это необходимо.

Изъятие микроопераций из буфера ROB.

Презентация на тему Основные инфекционные заболевания и их профилактика

Презентация на тему Основные инфекционные заболевания и их профилактика Митральные пороки

Митральные пороки  Влияние компьютерных игр на здоровье младших школьников и определение компьютерной зависимости

Влияние компьютерных игр на здоровье младших школьников и определение компьютерной зависимости Презентация на тему Пальчиковая гимнастика

Презентация на тему Пальчиковая гимнастика  “Мастерская для инноваций”

“Мастерская для инноваций” В каких странах говорят на английском языке?

В каких странах говорят на английском языке? В ожидании Рождества. Фотоальбом

В ожидании Рождества. Фотоальбом В.Б. Тарасов МГТУ им. Н.Э.Баумана, Кафедра «Компьютерные системы автоматизации производства» e-mail:

В.Б. Тарасов МГТУ им. Н.Э.Баумана, Кафедра «Компьютерные системы автоматизации производства» e-mail:  Административная ответственность

Административная ответственность МЕХАНИЗМЫ ВЗАИМОДЕЙСТВИЯ ВЕРБАЛЬНЫХ И НЕВЕРБАЛЬНЫХ ЕДИНИЦ В ДИАЛОГЕ II Б. ДЕЙКТИЧЕСКИЕ ЖЕСТЫ И РЕЧЕВЫЕ АКТЫ Крейдлин Г. Е. (РГГУ,

МЕХАНИЗМЫ ВЗАИМОДЕЙСТВИЯ ВЕРБАЛЬНЫХ И НЕВЕРБАЛЬНЫХ ЕДИНИЦ В ДИАЛОГЕ II Б. ДЕЙКТИЧЕСКИЕ ЖЕСТЫ И РЕЧЕВЫЕ АКТЫ Крейдлин Г. Е. (РГГУ,  Технология как часть общечеловеческой культуры

Технология как часть общечеловеческой культуры Коммуникационные технологии

Коммуникационные технологии  Атмосфера: значение, строение, изучение

Атмосфера: значение, строение, изучение Презентация на тему Вода в природе 3 класс

Презентация на тему Вода в природе 3 класс  Презентация на тему Фалес Милетский

Презентация на тему Фалес Милетский Реки

Реки Блинчики-Мск. Проект

Блинчики-Мск. Проект Презентация на тему Чтобы путь был счастливым (3 класс)

Презентация на тему Чтобы путь был счастливым (3 класс) Развитие социальной психологии

Развитие социальной психологии проект ккт

проект ккт Установка коннектора компрессора на новых корейских компрессорах!

Установка коннектора компрессора на новых корейских компрессорах! Я РАДА ПРИВЕТСТВОВАТЬ ВАС НА УРОКЕ ФИЗИКИ

Я РАДА ПРИВЕТСТВОВАТЬ ВАС НА УРОКЕ ФИЗИКИ общая характеристика растений

общая характеристика растений Новогодний хороводНам очень веселоВозьмёмся за руки.. - презентация

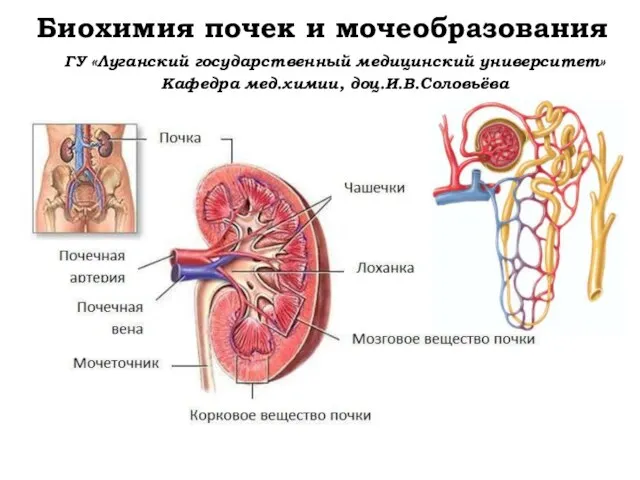

Новогодний хороводНам очень веселоВозьмёмся за руки.. - презентация Биохимия почек и мочеобразования

Биохимия почек и мочеобразования Сертификация систем качества

Сертификация систем качества Презентация на тему Экологические факторы. Антропогенное воздействие на экосистемы

Презентация на тему Экологические факторы. Антропогенное воздействие на экосистемы Птичья азбука

Птичья азбука