Содержание

- 2. История Начало исследований в области формальной логики было положено Аристотелем в IV в. до н.э. Однако

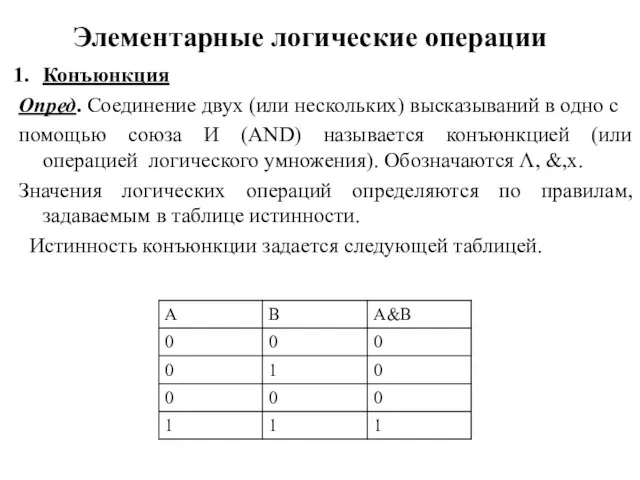

- 3. Элементарные логические операции Конъюнкция Опред. Соединение двух (или нескольких) высказываний в одно с помощью союза И

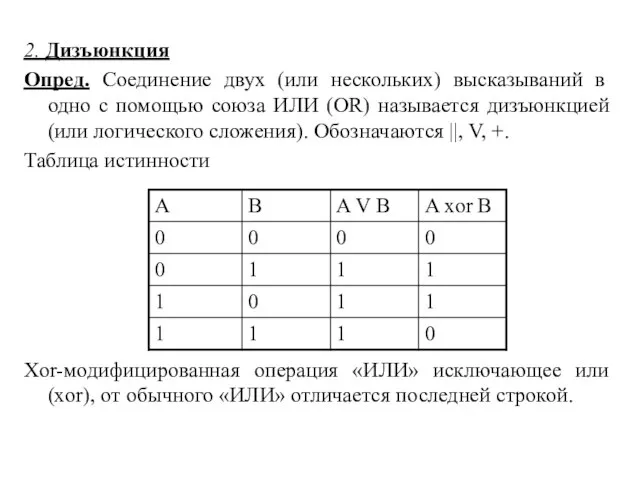

- 4. 2. Дизъюнкция Опред. Соединение двух (или нескольких) высказываний в одно с помощью союза ИЛИ (OR) называется

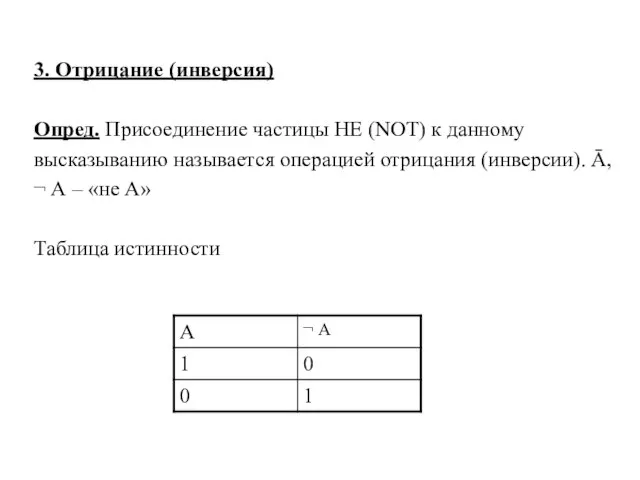

- 5. 3. Отрицание (инверсия) Опред. Присоединение частицы НЕ (NOT) к данному высказыванию называется операцией отрицания (инверсии). Ā,

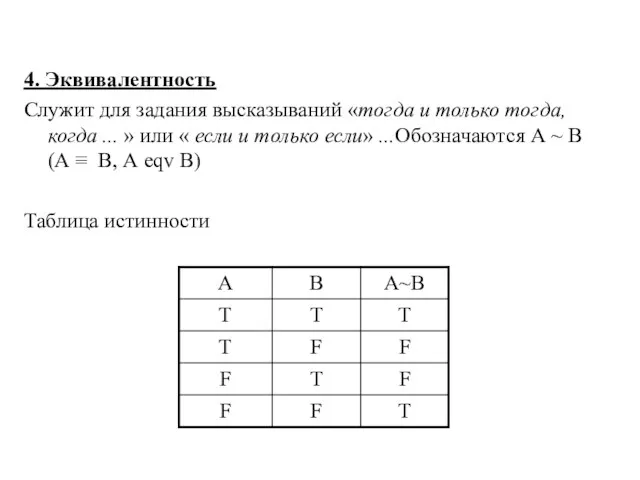

- 6. 4. Эквивалентность Служит для задания высказываний «тогда и только тогда, когда ... » или « если

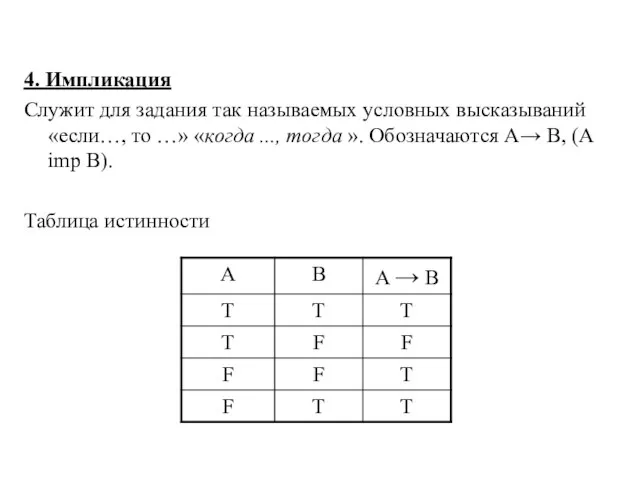

- 7. 4. Импликация Служит для задания так называемых условных высказываний «если…, то …» «когда ..., тогда ».

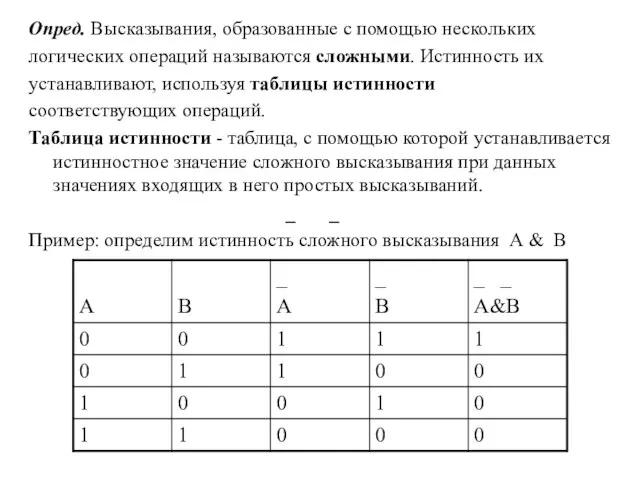

- 8. Опред. Высказывания, образованные с помощью нескольких логических операций называются сложными. Истинность их устанавливают, используя таблицы истинности

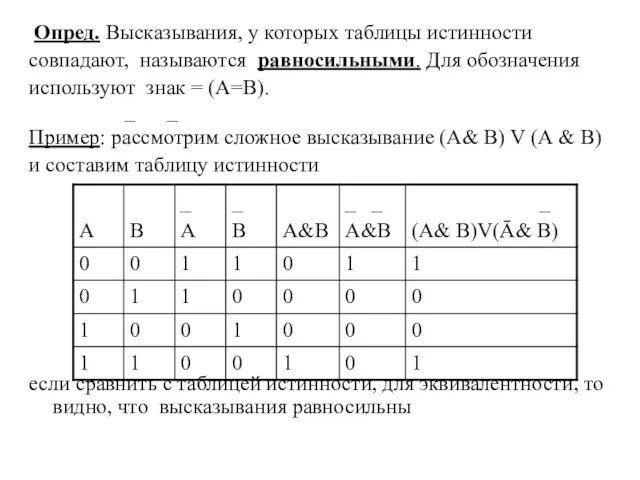

- 9. Опред. Высказывания, у которых таблицы истинности совпадают, называются равносильными. Для обозначения используют знак = (А=В). _

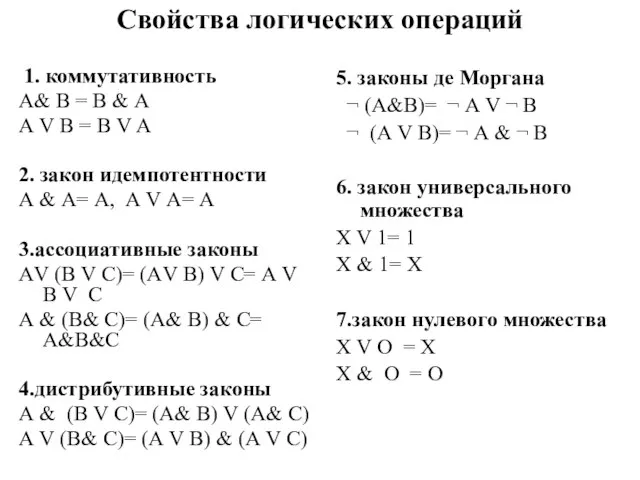

- 10. Свойства логических операций 1. коммутативность А& В = В & А А V В = В

- 11. Схемная реализация базовых логических элементов Логические элементы (ЛЭ) - это электронные схемы с одним или несколькими

- 12. Схемная реализация базовых логических элементов. Из логических элементов путем их комбинации строятся основные схемы компьютера. Триггер

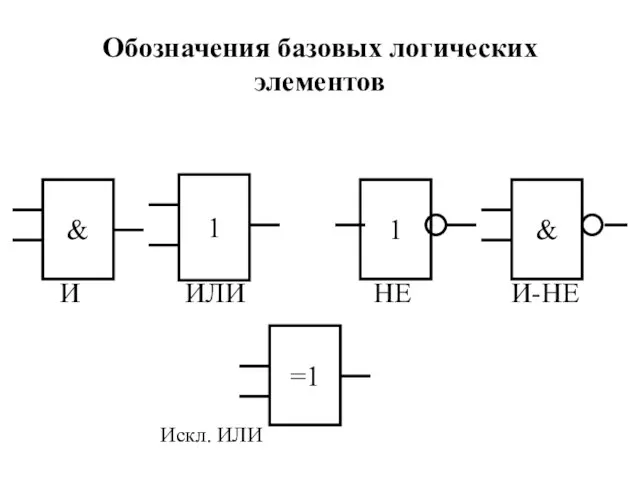

- 13. Обозначения базовых логических элементов И ИЛИ НЕ И-НЕ Искл. ИЛИ & 1 =1 1 &

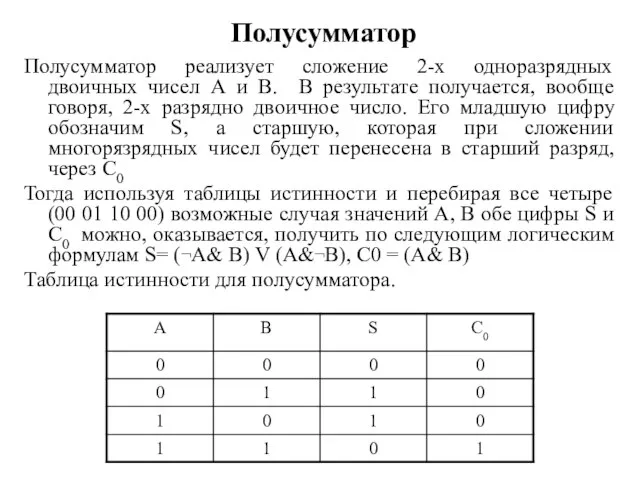

- 14. Полусумматор Полусумматор реализует сложение 2-х одноразрядных двоичных чисел А и В. В результате получается, вообще говоря,

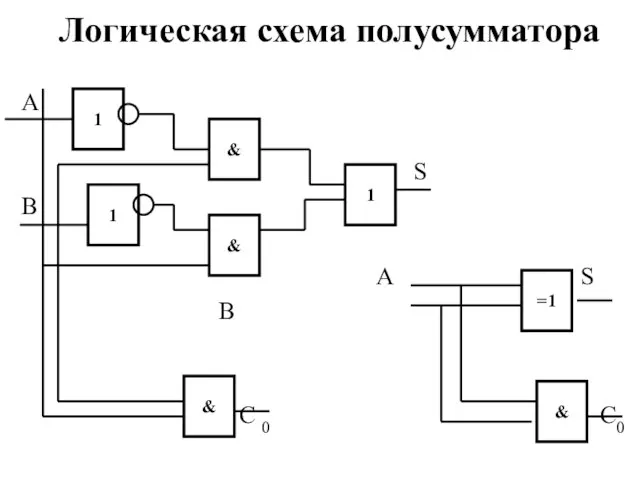

- 15. Логическая схема полусумматора А S В А S В C 0 C0 1 & 1 &

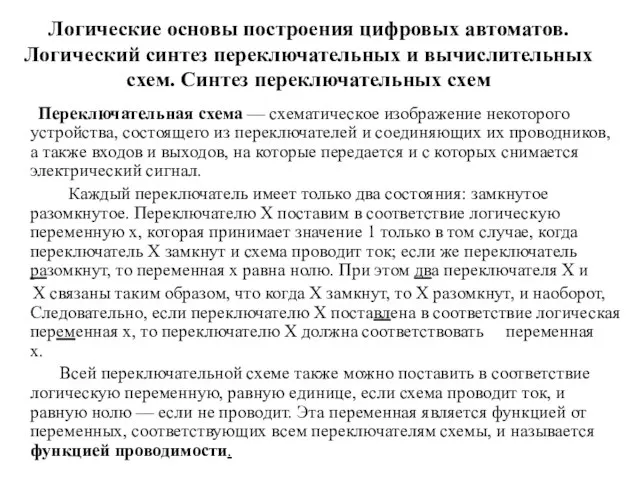

- 16. Логические основы построения цифровых автоматов. Логический синтез переключательных и вычислительных схем. Синтез переключательных схем Переключательная схема

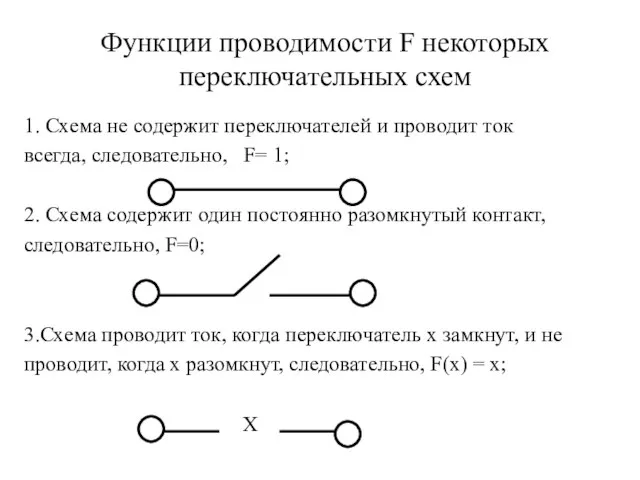

- 17. Функции проводимости F некоторых переключательных схем 1. Схема не содержит переключателей и проводит ток всегда, следовательно,

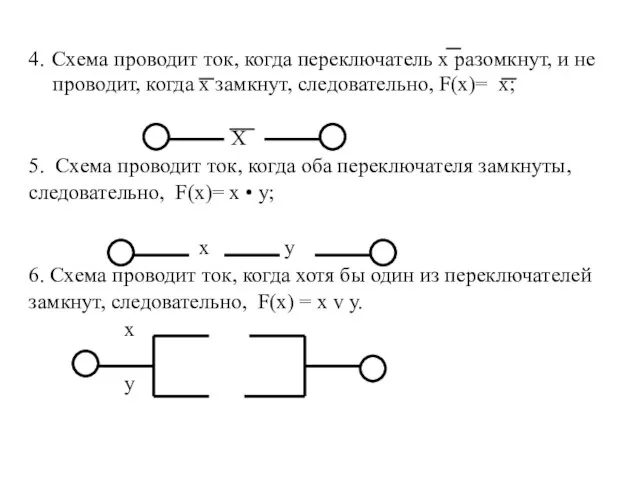

- 18. 4. Схема проводит ток, когда переключатель х разомкнут, и не проводит, когда х замкнут, следовательно, F(х)=

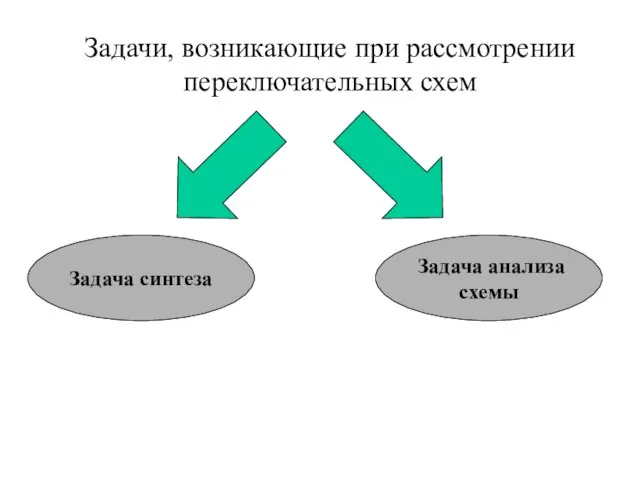

- 19. Задачи, возникающие при рассмотрении переключательных схем Задача синтеза Задача анализа схемы

- 20. Этапы синтеза переключательной схемы 1. Составление функции проводимости по заданным условиям 2. Упрощение этой функции. 3.

- 21. Этапы анализа схемы 1. Определение значений функции проводимости при всех возможных наборах, входящих в эту функцию

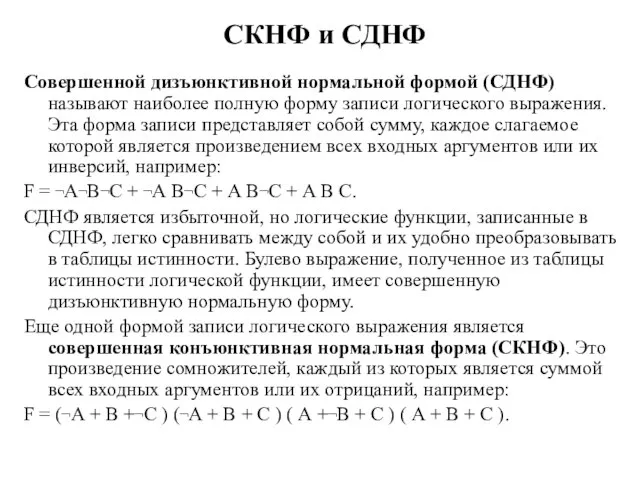

- 22. СКНФ и СДНФ Совершенной дизъюнктивной нормальной формой (СДНФ) называют наиболее полную форму записи логического выражения. Эта

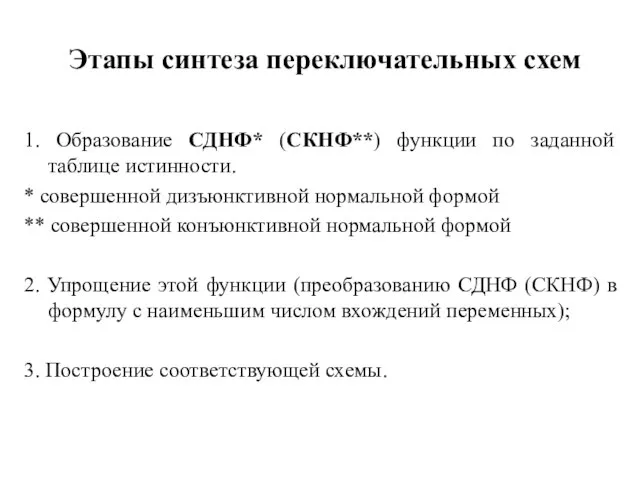

- 23. Этапы синтеза переключательных схем 1. Образование СДНФ* (СКНФ**) функции по заданной таблице истинности. * совершенной дизъюнктивной

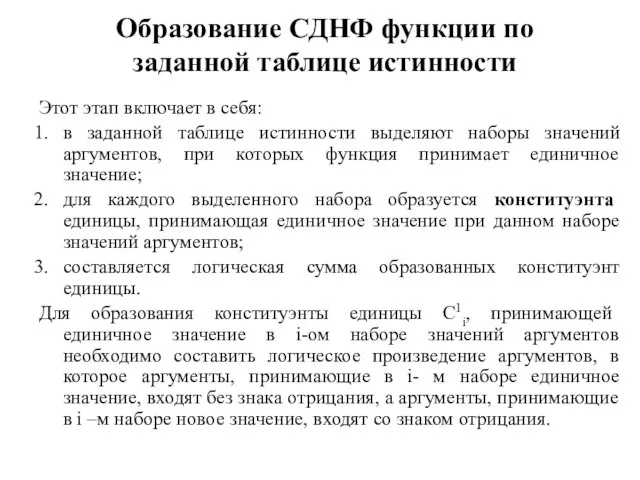

- 24. Образование СДНФ функции по заданной таблице истинности Этот этап включает в себя: в заданной таблице истинности

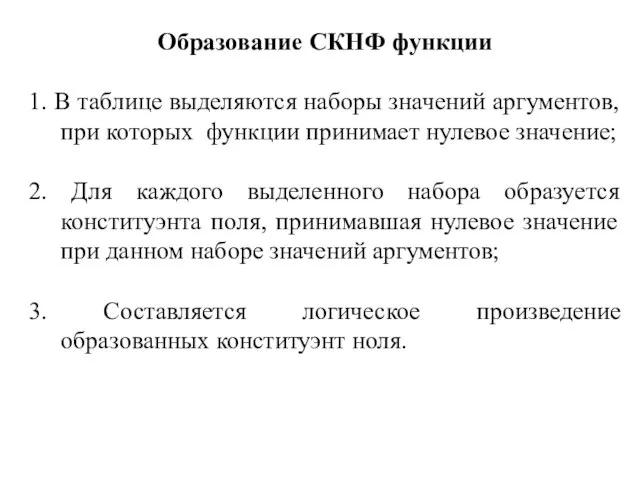

- 25. Образование СКНФ функции 1. В таблице выделяются наборы значений аргументов, при которых функции принимает нулевое значение;

- 26. Упрощение функции При преобразовании СДНФ (СКНФ) в формулу с наименьшим числом вхождений переменных (минимизация формулы) используют

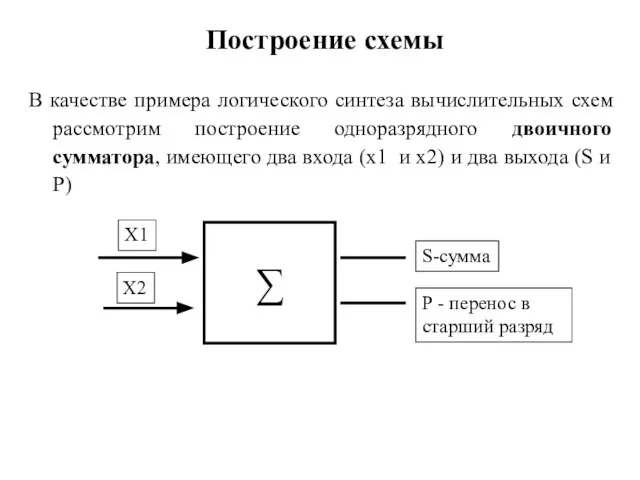

- 27. Построение схемы В качестве примера логического синтеза вычислительных схем рассмотрим построение одноразрядного двоичного сумматора, имеющего два

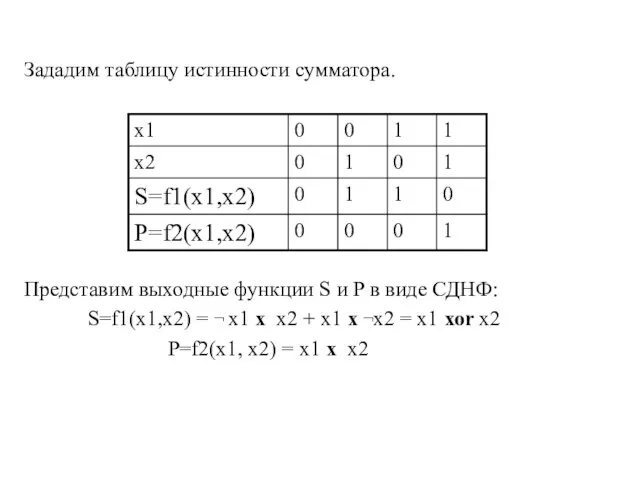

- 28. Зададим таблицу истинности сумматора. Представим выходные функции S и P в виде СДНФ: S=f1(x1,x2) = ¬

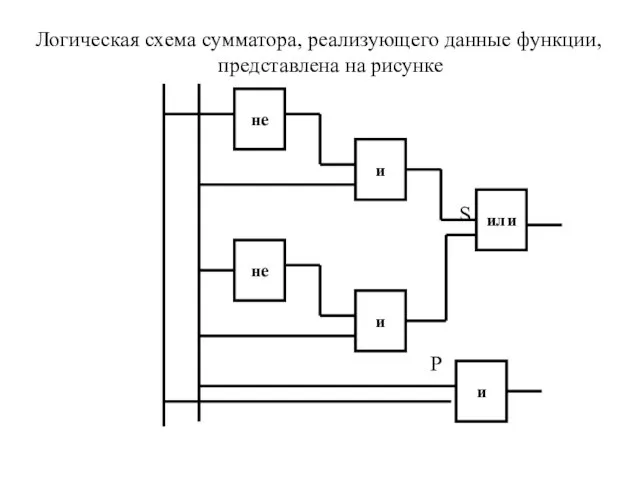

- 29. Логическая схема сумматора, реализующего данные функции, представлена на рисунке S P не и и или и

- 30. Для логических схем (И, ИЛИ, НЕ) существуют типовые технические схемы (логические элементы), реализующие их на полупроводниковых

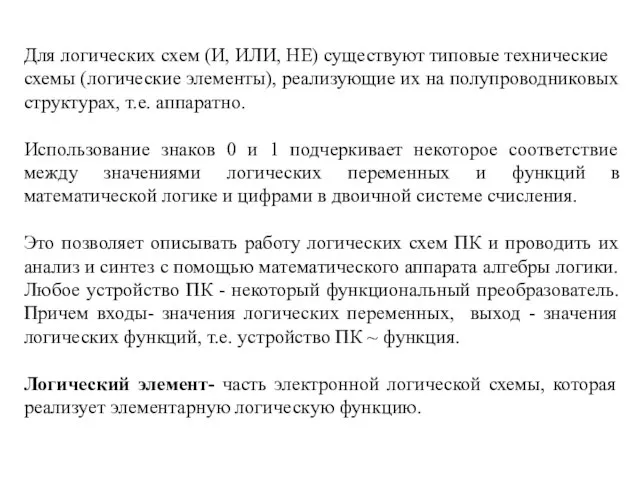

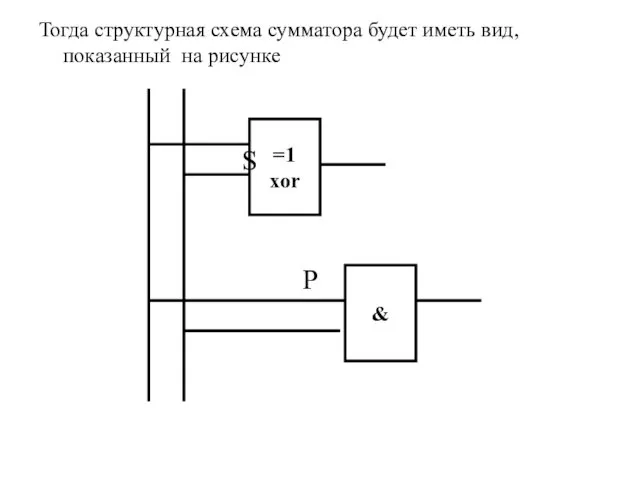

- 31. Тогда структурная схема сумматора будет иметь вид, показанный на рисунке S P =1 xor &

- 33. Скачать презентацию

Логистика

Логистика Времена года

Времена года The Rising of the moon

The Rising of the moon Мониторинг готовности первоклассников к обучению в школе

Мониторинг готовности первоклассников к обучению в школе Узоры, которые создали люди

Узоры, которые создали люди Приобретение жилья

Приобретение жилья Экологическое состояние Юбилейного микрорайона города Краснодара

Экологическое состояние Юбилейного микрорайона города Краснодара Искусство как феномен культуры

Искусство как феномен культуры Творчество художника Е. И. чарушина

Творчество художника Е. И. чарушина Понятие бизнес - процесса

Понятие бизнес - процесса От энергии до…

От энергии до… Михаил Дмитриевич Прохоров Генеральный директор

Михаил Дмитриевич Прохоров Генеральный директор Презентация на тему Тарифные льготы как инструмент привлечения иностранных инвестиций

Презентация на тему Тарифные льготы как инструмент привлечения иностранных инвестиций  Информационно-коммуникационные технологии при изучении явления электромагнитной индукции

Информационно-коммуникационные технологии при изучении явления электромагнитной индукции Браслет своими руками

Браслет своими руками презентация_210922

презентация_210922 МБОУ «Сорокинская СОШ»

МБОУ «Сорокинская СОШ» ПАЛОМНИЧЕСТВО БХАКТИ-ВРИКШ ЧЕТЫРЕ ДХАМЫ

ПАЛОМНИЧЕСТВО БХАКТИ-ВРИКШ ЧЕТЫРЕ ДХАМЫ Топчихинский район МОУ Топчихинская СОШ № 2 Федосеенко Н.Н. Урок английского языка в 3 классе “Colours. How Colourful the World IS”.

Топчихинский район МОУ Топчихинская СОШ № 2 Федосеенко Н.Н. Урок английского языка в 3 классе “Colours. How Colourful the World IS”. Рецидивная и профессиональная преступность

Рецидивная и профессиональная преступность Информационно-методический центр Адмиралтейского района Выпускная работа Проблема счастья в романе И.А.Гончарова «Обломов» П

Информационно-методический центр Адмиралтейского района Выпускная работа Проблема счастья в романе И.А.Гончарова «Обломов» П Чугун. Виды чугуна

Чугун. Виды чугуна КАФЕДРА ПРОГРАММНЫХ СИСТЕМ

КАФЕДРА ПРОГРАММНЫХ СИСТЕМ  ОСТРЫЙ ВЕНОЗНЫЙ ТРОМБОЗ И ТРОМБОЭМБОЛИЯ ЛЕГОЧНОЙ АРТЕРИИ:СОВРЕМЕННЫЕ СТАНДАРТЫ ДИАГНОСТИКИ, ЛЕЧЕНИЯ И ПРОФИЛАКТИКИ

ОСТРЫЙ ВЕНОЗНЫЙ ТРОМБОЗ И ТРОМБОЭМБОЛИЯ ЛЕГОЧНОЙ АРТЕРИИ:СОВРЕМЕННЫЕ СТАНДАРТЫ ДИАГНОСТИКИ, ЛЕЧЕНИЯ И ПРОФИЛАКТИКИ Фонетика

Фонетика Нормы делового этикета в современной онлайн коммуникации

Нормы делового этикета в современной онлайн коммуникации Школьная форма – стильно, удобно, модно…

Школьная форма – стильно, удобно, модно… Воздухоплавание

Воздухоплавание