Содержание

- 2. Мировые тенденции развития микропроцессоров Микропроцессорные линии МЦСТ-R и Эльбрус Маршрут проектирования микропроцессоров Вычислительные устройства на базе

- 3. «Закон Мура» продолжает действовать – количество транзисторов на кристалле удваивается каждые 18-24 месяцев за счет перехода

- 4. Пять главных проблем развития микропроцессоров в XXI веке* Параллельность - возможность использования десятков вычислительных ядер и

- 5. Основные черты современных микропроцессоров: Многоядерные и многопотоковые структуры Многоуровневая иерархия памяти Объединение системных и периферийных контроллеров

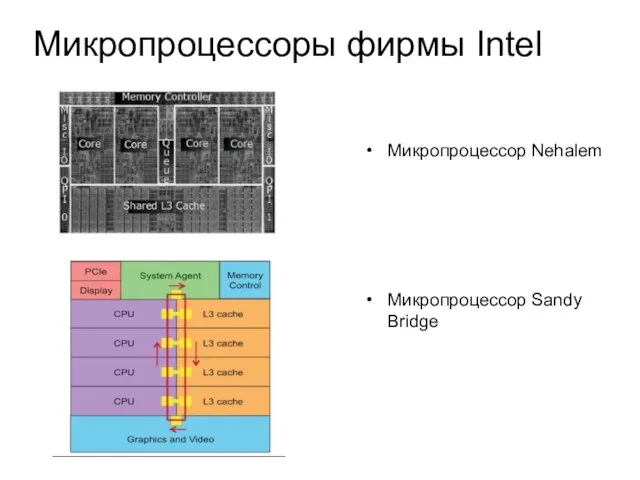

- 6. Микропроцессоры фирмы Intel Микропроцессор Nehalem Микропроцессор Sandy Bridge

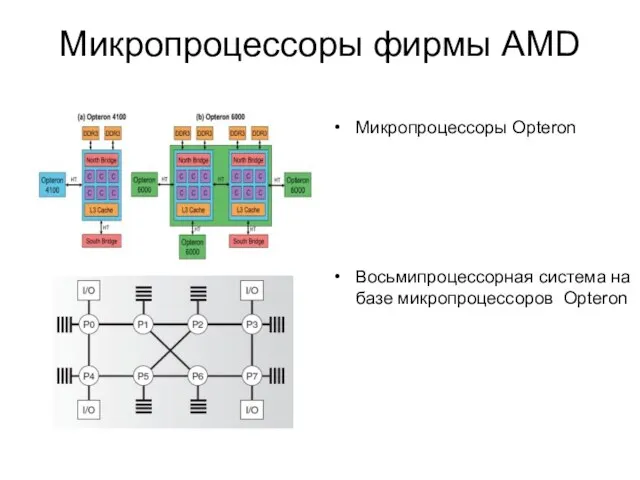

- 7. Микропроцессоры фирмы AMD Микропроцессоры Opteron Восьмипроцессорная система на базе микропроцессоров Opteron

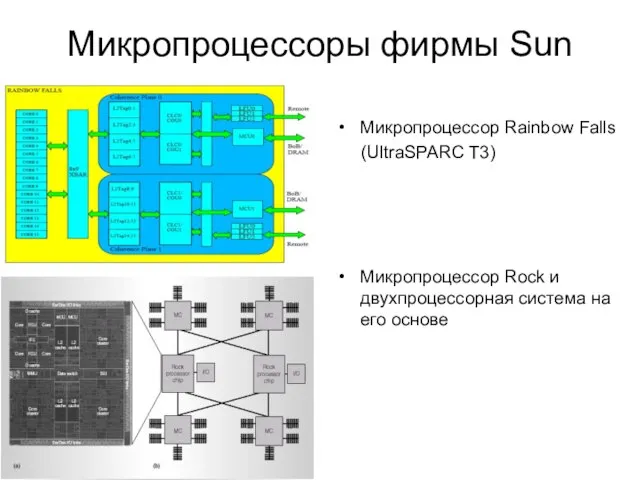

- 8. Микропроцессоры фирмы Sun Микропроцессор Rainbow Falls (UltraSPARC T3) Микропроцессор Rock и двухпроцессорная система на его основе

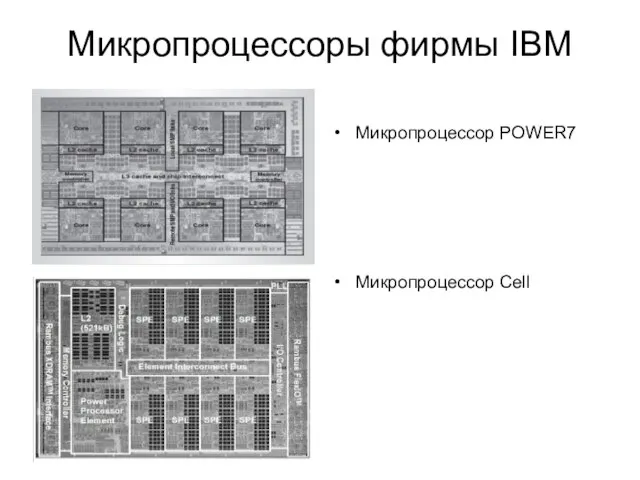

- 9. Микропроцессоры фирмы IBM Микропроцессор POWER7 Микропроцессор Cell

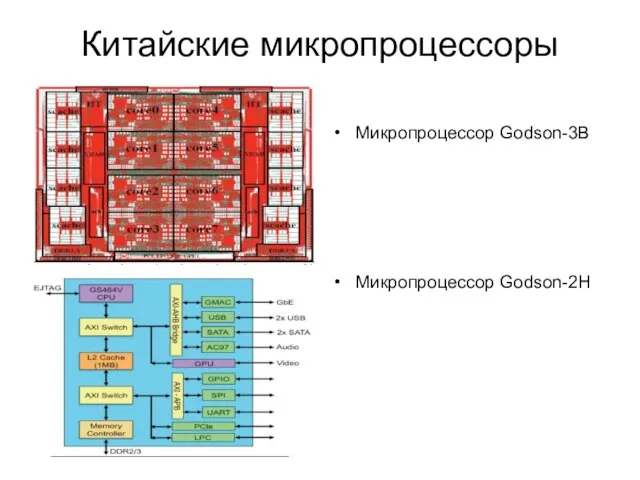

- 10. Китайские микропроцессоры Микропроцессор Godson-3B Микропроцессор Godson-2H

- 11. Китайские микропроцессоры Эволюция микропроцессоров Godson

- 12. Мировые тенденции развития микропроцессоров Микропроцессорные линии МЦСТ-R и Эльбрус Маршрут проектирования микропроцессоров Вычислительные устройства на базе

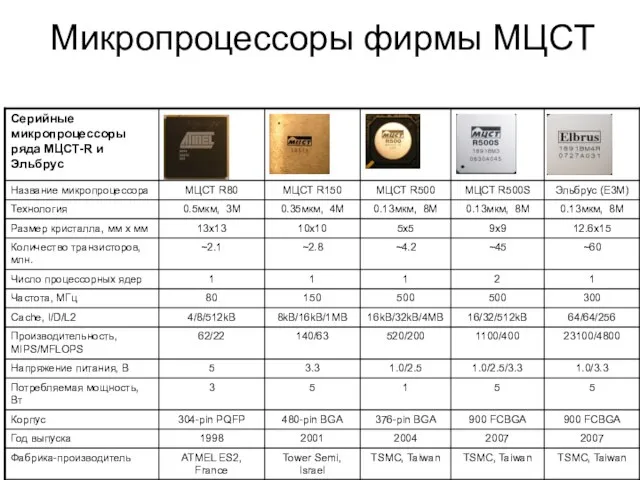

- 13. Микропроцессоры фирмы МЦСТ

- 14. Основные черты микропроцессора Эльбрус архитектура, ориентированная на получение высокой производительности совместимость с архитектурой Intel х86 с

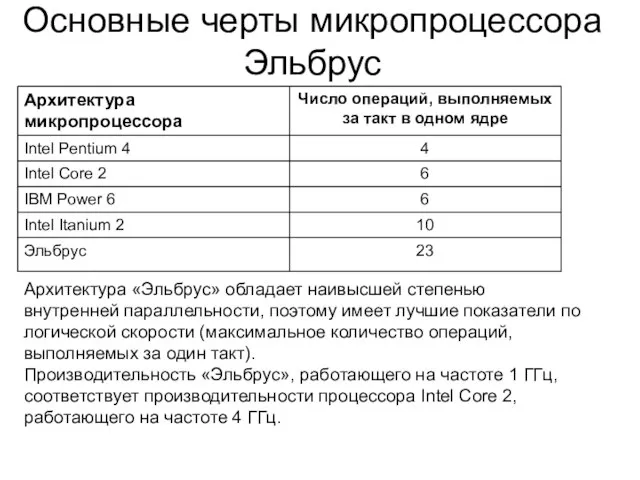

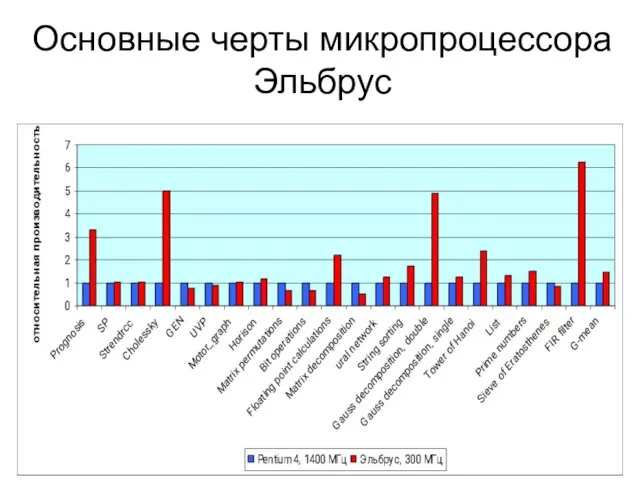

- 15. 1C 4C 2C 2C 4C 4C 8C Основные черты микропроцессора Эльбрус Архитектура «Эльбрус» обладает наивысшей степенью

- 16. Основные черты микропроцессора Эльбрус

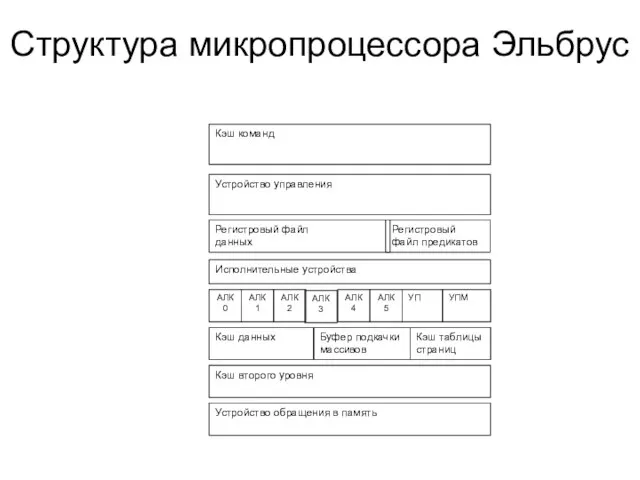

- 17. Кэш команд Устройство управления Регистровый файл данных Регистровый файл предикатов Исполнительные устройства АЛК1 АЛК2 АЛК3 АЛК4

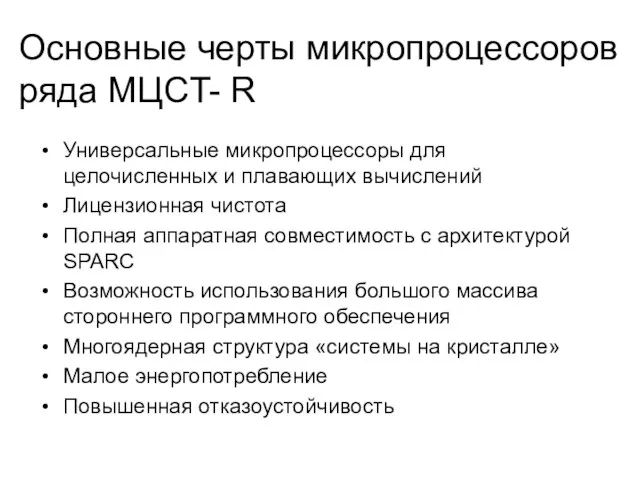

- 18. Основные черты микропроцессоров ряда MЦСT- R Универсальные микропроцессоры для целочисленных и плавающих вычислений Лицензионная чистота Полная

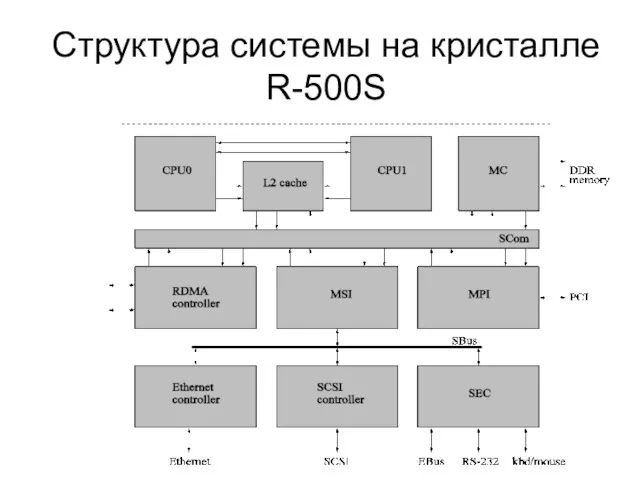

- 19. Структура системы на кристалле R-500S

- 20. Мировые тенденции развития микропроцессоров Микропроцессорные линии МЦСТ-R и Эльбрус Маршрут проектирования микропроцессоров Вычислительные устройства на базе

- 21. Основные этапы логического проектирования микропроцессоров Разработка спецификаций RTL-описание на языке Verilog Автономная верификация (САПР Model Sim)

- 22. Основные этапы топологического проектирования микропроцессоров Синтез устройств (САПР Design Compiler + PowerCompiler) Планирование кристалла - создание

- 23. Основные этапы топологического проектирования микропроцессора Оценка мощности, падения напряжения и электромиграции (САПР Astro-Rail) Экстракция паразитных RC

- 24. Особенности топологического проектирования микропроцессоров Наличие заказного регистрового файла Наличие заказного блока формирования синхросигналов Наличие заказного блока

- 25. Мировые тенденции развития микропроцессоров Микропроцессорные линии МЦСТ-R и Эльбрус Маршрут проектирования микропроцессоров Вычислительные устройства на базе

- 26. Вычислительные комплексы «Эльбрус-3М1» для АРМ и встроенных применений Количество процессоров – 2 Тактовая частота процессора –300

- 27. Вычислительный комплекс Эльбрус-90 в конструкции IBM РС для АРМ Два микропроцессора R-500 1000 MIPS/400MFlops 2X4 MB

- 28. Вычислительный комплекс Эльбрус-90 в индустриальном исполнении 4 микропроцессора R-500 2000 MIPS/800 MFlops 4X4 MB кэш-память второго

- 29. Вычислительный комплекс Эльбрус-90 в исполнении ноутбук и планшет микропроцессор R-500 процессорный модуль SOM ЕТХ 490 MIPS/200

- 30. Вычислительный многопроцессорный модуль CompactPCI 3U Количество микросхем 1891ВМ3 на модуле – 1 Общее количество процессоров –

- 31. Вычислительный многопроцессорный модуль CompactPCI 6U Количество микросхем 1891ВМ3 на модуле – 4 Общее количество процессоров –

- 32. Мировые тенденции развития микропроцессоров Микропроцессорные линии МЦСТ-R и Эльбрус Маршрут проектирования микропроцессоров Вычислительные устройства на базе

- 33. Операционные системы для микропроцессорных платформ Эльбрус и МЦСТ-R: ОС Эльбрус, МСВС, Solaris

- 34. Структура ОС Эльбрус Доработанное ядро ОС Linux Библиотеки, утилиты, конфигурационные файлы, связанные с произведенными доработками Специальные

- 35. Мировые тенденции развития микропроцессоров Микропроцессорные линии МЦСТ-R и Эльбрус Маршрут проектирования микропроцессоров Вычислительные устройства на базе

- 36. Оптимизирующий компилятор

- 37. Эффективная двоичная совместимость с Intel x86 Функциональность Полная совместимость с архитектурой Intel x86 Прямое исполнение 20+

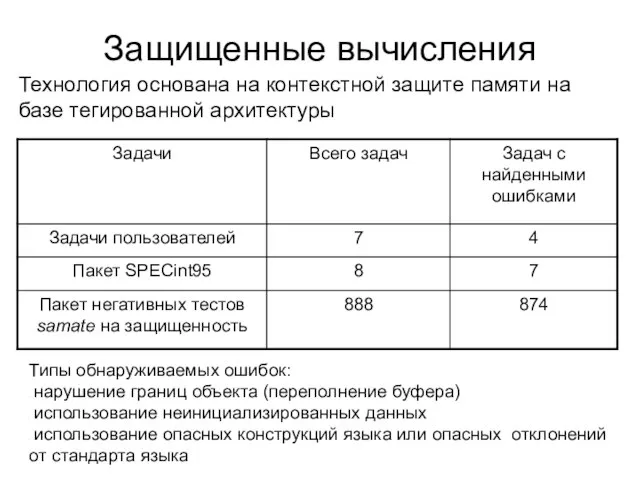

- 38. Защищенные вычисления Типы обнаруживаемых ошибок: нарушение границ объекта (переполнение буфера) использование неинициализированных данных использование опасных конструкций

- 39. Мировые тенденции развития микропроцессоров Микропроцессорные линии МЦСТ-R и Эльбрус Маршрут проектирования микропроцессоров Вычислительные устройства на базе

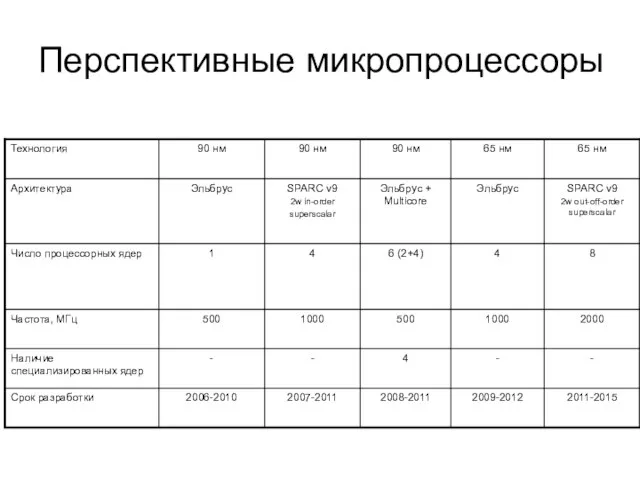

- 40. Перспективные микропроцессоры

- 41. Структура системы на кристалле Эльбрус-S

- 42. Структура системы на кристалле МЦСТ-4R

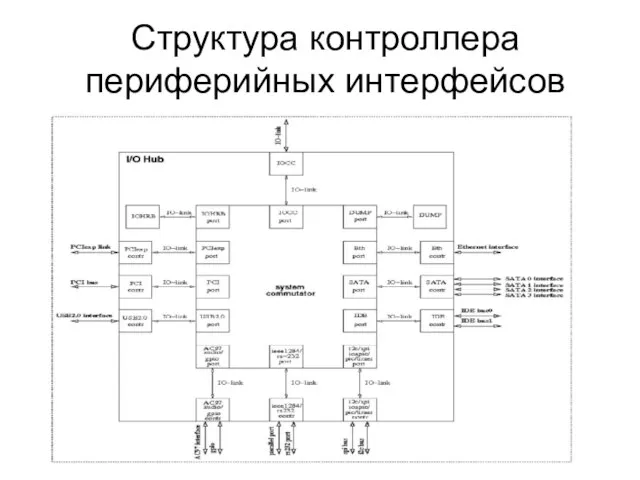

- 43. Структура контроллера периферийных интерфейсов

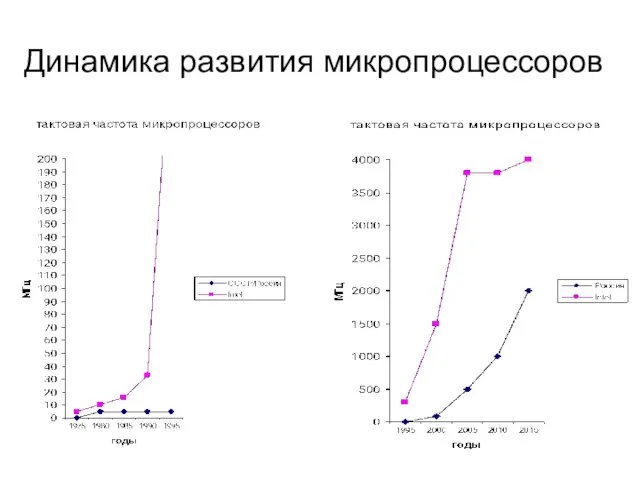

- 44. Динамика развития микропроцессоров

- 46. Скачать презентацию

Знание - сила

Знание - сила Воздух - наш невидимый друг

Воздух - наш невидимый друг 200200.68.01 Прикладная оптика

200200.68.01 Прикладная оптика Горные машины и оборудование. Курс лекций

Горные машины и оборудование. Курс лекций Занятия Мои друзья. Мое увлечение

Занятия Мои друзья. Мое увлечение Характеристики проекта

Характеристики проекта Простые вещества-неметаллы

Простые вещества-неметаллы Кордицепс НСПCordyceps NSP

Кордицепс НСПCordyceps NSP ОЗ 7 Попередження ризиків від вибухонебезпечних предметів

ОЗ 7 Попередження ризиків від вибухонебезпечних предметів Реабилитация детей с девиантно-криминальным поведением

Реабилитация детей с девиантно-криминальным поведением Программирование на языке С

Программирование на языке С  Презентація

Презентація Актуальные проблемы формирования регионального свода книжных памятников Из опыта работы Архангельской областной научной биб

Актуальные проблемы формирования регионального свода книжных памятников Из опыта работы Архангельской областной научной биб Лекция 12. Особенная часть финансово-банковского права

Лекция 12. Особенная часть финансово-банковского права Нанесение тонких пленок из жидких растворов прекурсоров

Нанесение тонких пленок из жидких растворов прекурсоров Неделя

Неделя Управление качеством образования: компетенции 21 века. Эмоциональный интеллект

Управление качеством образования: компетенции 21 века. Эмоциональный интеллект РЕГИСТР РИСКОВ ПО КИРОВСКОЙ ОБЛАСТИ ПРИ ПОСТАВКАХ КОНТРОЛИРУЕМОЙ ДРЕВЕСИНЫ СОГЛАСНО ТРЕБОВАНИЯМ FSC Проект для обсуждения Пров

РЕГИСТР РИСКОВ ПО КИРОВСКОЙ ОБЛАСТИ ПРИ ПОСТАВКАХ КОНТРОЛИРУЕМОЙ ДРЕВЕСИНЫ СОГЛАСНО ТРЕБОВАНИЯМ FSC Проект для обсуждения Пров Шаблон проекта # бери своё

Шаблон проекта # бери своё МОУ «Афанасовская СОШ Корочанского района Белгородской области»

МОУ «Афанасовская СОШ Корочанского района Белгородской области» Юридическая ответственность и ее виды

Юридическая ответственность и ее виды Предупреждение Дженни Джозеф

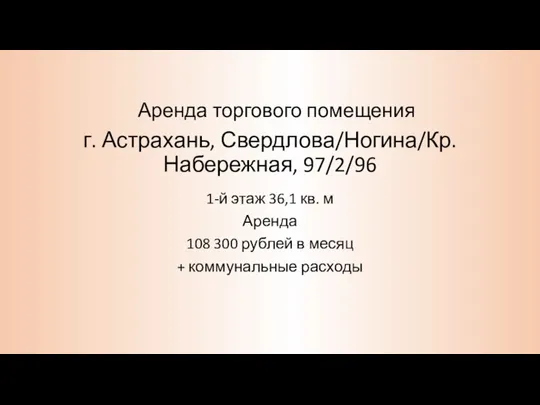

Предупреждение Дженни Джозеф Аренда торгового помещения г. Астрахань

Аренда торгового помещения г. Астрахань В.Гюго

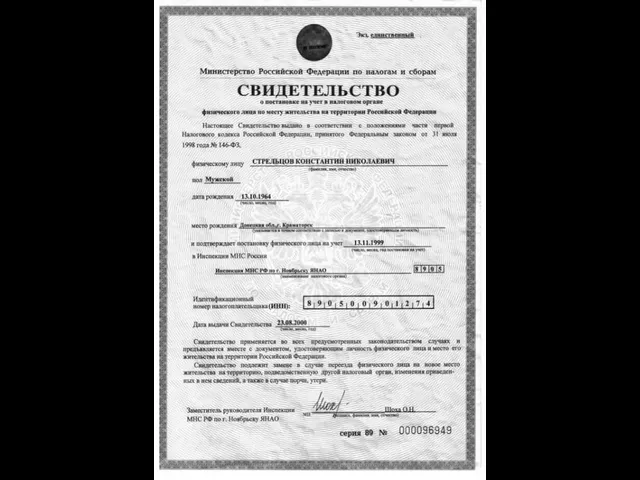

В.Гюго Тел. Офисный 8(3496)36-76-49 Галина.

Тел. Офисный 8(3496)36-76-49 Галина. Методическое письмо Об использовании результатов ЕГЭ 2009 года в преподавании математики в ОУ среднего (полного) общего образования

Методическое письмо Об использовании результатов ЕГЭ 2009 года в преподавании математики в ОУ среднего (полного) общего образования Презентация (1)

Презентация (1) Открытка ко дню пожилого человека

Открытка ко дню пожилого человека